Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Le58QL02/021/031

## Quad Low Voltage Subscriber Line Audio-Processing Circuit VE580 Series

### **APPLICATIONS**

■ Codec function on telephone switch line cards

#### **FEATURES**

- Low-power, 3.3 V CMOS technology with 5-V tolerant digital inputs

- Software and coefficient compatible to the Le79Q02/ 021/031 QSLAC™ device

- Performs the functions of four codec/filters

- Software programmable:

- SLIC device input impedance

- Transhybrid balance

- Transmit and receive gains

- Equalization (frequency response)

- Digital I/O pins

- Programmable debouncing on one input

- Time slot assigner

- Programmable clock slot and PCM transmit clock edge options

- Standard microprocessor interface

- A-law, μ-law, or linear coding

- Single or Dual PCM ports available

- Up to 128 channels (PCLK at 8.192 MHz) per PCM port

- Optional supervision on the PCM highway

- 1.536, 1.544, 2.048, 3.072, 3.088, 4.096, 6.144, 6.176, or

8.192 MHz master clock derived from MCLK or PCLK

- Built-in test modes with loopback, tone generation, and μP access to PCM data

- Mixed state (analog and digital) impedance scaling

- Performance guaranteed over a 12 dB gain range

- Real Time Data register with interrupt (open drain or TTL output)

- Supports multiplexed SLIC device outputs

- Broadcast state

- 256 kHz or 293 kHz chopper clock for Legerity SLIC devices with switching regulator

- Maximum channel bandwidth for V.90 modems

#### RELATED LITERATURE

- 080754 Le58QL061/063 QLSLAC<sup>™</sup> Device Data Sheet

- 080761 QSLAC<sup>™</sup> to QLSLAC<sup>™</sup> Device Design Conversion Guide

- 080758 QSLAC<sup>™</sup> to QLSLAC<sup>™</sup> Guide to New Designs

### ORDERING INFORMATION

| Device       | Package (Green) <sup>1</sup> | Packing <sup>2</sup> |

|--------------|------------------------------|----------------------|

| Le58QL02FJC  | 44-pin PLCC                  | Tube                 |

| Le58QL021FJC | 44-pin PLCC                  | Tube                 |

| Le58QL021BVC | 44-pin TQFP                  | Tray                 |

| Le58QL031DJC | 32-pin PLCC                  | Tube                 |

- The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

- 2. For delivery using a tape and reel packing system, add a "T" suffix to the OPN (Ordering Part Number) when placing an order.

### **DESCRIPTION**

The Le58QL02/021/031 Quad Low Voltage Subscriber Line Audio-Processing Circuit (QLSLAC™) devices integrate the key functions of analog line cards into high-performance, very-programmable, four-channel codec-filter devices. The QLSLAC devices are based on the proven design of Legerity's reliable SLAC™ device families. The advanced architecture of the QLSLAC devices implements four independent channels and employs digital filters to allow software control of transmission, thus providing a cost-effective solution for the audio-processing function of programmable line cards. The QLSLAC devices are software and coefficient compatible to the QSLAC devices.

Advanced submicron CMOS technology makes the Le58QL02/021/031 QLSLAC devices economical, with both the functionality and the low power consumption needed in line card designs to maximize line card density at minimum cost. When used with four Legerity SLIC devices, a QLSLAC device provides a complete software-configurable solution to the BORSCHT functions.

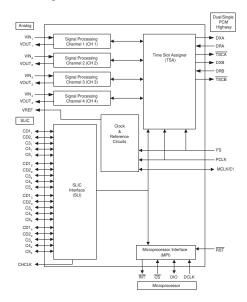

#### **BLOCK DIAGRAM**

Document ID# **080753** Date: **April 09, 2009** Version: **9**

Distribution: Public Document

## **TABLE OF CONTENTS**

| APPLICATIONS1                                          |

|--------------------------------------------------------|

| FEATURES1                                              |

| ORDERING INFORMATION1                                  |

| RELATED LITERATURE                                     |

| DESCRIPTION                                            |

| BLOCK DIAGRAM                                          |

| TABLE OF CONTENTS                                      |

| LIST OF FIGURES                                        |

| LIST OF TABLES                                         |

| PRODUCT DESCRIPTION                                    |

| BLOCK DESCRIPTIONS                                     |

| Clock and Reference Circuits                           |

| Microprocessor Interface (MPI)                         |

| Time Slot Assigner (TSA)                               |

| Signal Processing Channels (CHx)                       |

| SLIC Device Interface (SLI)                            |

| CONNECTION DIAGRAMS                                    |

| PIN DESCRIPTIONS10                                     |

| ABSOLUTE MAXIMUM RATINGS12                             |

| OPERATING RANGES12                                     |

| Environmental Ranges                                   |

| Electrical Ranges12                                    |

| ELECTRICAL CHARACTERISTICS                             |

| Transmission Characteristics                           |

| Group Delay Distortion                                 |

| Gain Linearity                                         |

| Total Distortion Including Quantizing Distortion18     |

| Discrimination Against Out-of-Band Input Signals       |

| Discrimination Against 12- and 16-kHz Metering Signals |

| Overload Compression                                   |

| SWITCHING CHARACTERISTICS                              |

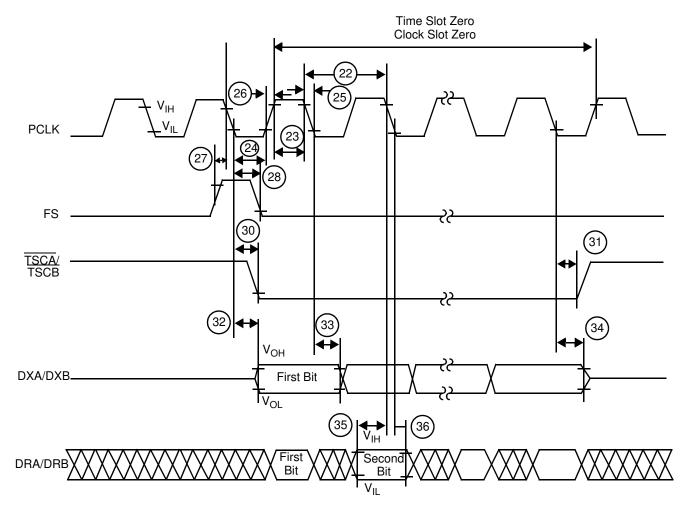

| SWITCHING WAVEFORMS                                    |

| OPERATING THE QLSLAC DEVICE                            |

| Power-Up Sequence                                      |

| Channel Enable (EC) Register                           |

| SLIC Device Control and Data Lines                     |

| Clock Mode Operation                                   |

| E1 Multiplex Operation                                 |

| Real-Time Data Register Operation                      |

| Interrupt                                              |

| Interrupt Mask Register                                |

| Active State                                           |

| Inactive State                                         |

| Reset States                                           |

| SIGNAL PROCESSING                                      |

| Overview of Digital Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Two-Wire Impedance Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Frequency Response Correction and Equalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33 |

| Transhybrid Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Gain Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Transmit Signal Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Transmit PCM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Receive Signal Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Receive PCM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Analog Impedance Scaling Network (AISN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| Speech Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| Signaling on the PCM Highway                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| Robbed-Bit Signaling Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Default Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| COMMAND DESCRIPTION AND FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Command Field Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Microprocessor Interface Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| SUMMARY OF MPI COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

| MPI COMMAND STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

| 00h Deactivate (Standby State)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41 |

| 02h Software Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 04h Hardware Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 06h No Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 0Eh Activate Channel (Operational State)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 40/41h Write/Read Transmit Time Slot and PCM Highway Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 42/43h Write/Read Receive Time Slot and PCM Highway Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 44/45h Write/Read Transmit Clock Slot, Receive Clock Slot, and Transmit Clock Edg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 46/4/n Write/Read Chip Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43 |

| 46/47h Write/Read Chip Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44 |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register.  4D/4Fh Read Real-Time Data Register.  50/51h Write/Read AISN and Analog Gains.  52/53h Write/Read SLIC Device Input/Output Register.  54/55h Write/Read SLIC Input/Output Direction, Read Status Bits.  60/61h Write/Read Operating Functions.  6C/6Dh Write/Read Interrupt Mask Register.  70/71h Write/Read Operating Conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register.  4D/4Fh Read Real-Time Data Register.  50/51h Write/Read AISN and Analog Gains.  52/53h Write/Read SLIC Device Input/Output Register.  54/55h Write/Read SLIC Input/Output Direction, Read Status Bits.  60/61h Write/Read Operating Functions.  6C/6Dh Write/Read Interrupt Mask Register.  70/71h Write/Read Operating Conditions.  73h Read Revision Code Number (RCN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register  4D/4Fh Read Real-Time Data Register  50/51h Write/Read AISN and Analog Gains  52/53h Write/Read SLIC Device Input/Output Register  54/55h Write/Read SLIC Input/Output Direction, Read Status Bits  60/61h Write/Read Operating Functions  6C/6Dh Write/Read Interrupt Mask Register  70/71h Write/Read Operating Conditions  73h Read Revision Code Number (RCN)  80/81h Write/Read GX Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 88/89h Write/Read R Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 88/89h Write/Read R Filter Coefficients 96/97h Write/Read B2 Filter Coefficients (IIR)                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register.  4D/4Fh Read Real-Time Data Register.  50/51h Write/Read AISN and Analog Gains.  52/53h Write/Read SLIC Device Input/Output Register.  54/55h Write/Read SLIC Input/Output Direction, Read Status Bits.  60/61h Write/Read Operating Functions.  6C/6Dh Write/Read Interrupt Mask Register.  70/71h Write/Read Operating Conditions.  73h Read Revision Code Number (RCN).  80/81h Write/Read GX Filter Coefficients.  82/83h Write/Read GR Filter Coefficients (FIR and IIR).  86/87h Write/Read B1 Filter Coefficients.  88/89h Write/Read X Filter Coefficients.  88/89h Write/Read R Filter Coefficients.  96/97h Write/Read B2 Filter Coefficients (IIR).  98/99h Write/Read FIR Z Filter Coefficients (FIR only).                                                                                                                                                                                                                                                                                                                    |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read R Filter Coefficients 96/97h Write/Read B2 Filter Coefficients (IIR) 98/99h Write/Read FIR Z Filter Coefficients (FIR only) 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR only)                                                                                                                                                                                                                                                                                            |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 96/97h Write/Read B2 Filter Coefficients (IIR) 98/99h Write/Read FIR Z Filter Coefficients (FIR only) 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR only) C8/C9h Write/Read Debounce Time Register                                                                                                                                                                                                                                                   |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read R Filter Coefficients 96/97h Write/Read R Filter Coefficients (IIR) 98/99h Write/Read B2 Filter Coefficients (FIR only) 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR only) C8/C9h Write/Read Debounce Time Register CDh Read Transmit PCM Data E8/E9h Write/Read Ground Key Filter                                                                                                                                                                                        |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 96/97h Write/Read R Filter Coefficients (IIR) 98/99h Write/Read FIR Z Filter Coefficients (FIR only) 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR only) C8/C9h Write/Read Debounce Time Register CDh Read Transmit PCM Data E8/E9h Write/Read Ground Key Filter                                                                                                                                                                                     |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 88/89h Write/Read R Filter Coefficients 96/97h Write/Read B2 Filter Coefficients (IIR) 98/99h Write/Read FIR Z Filter Coefficients (FIR only) 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR) C8/C9h Write/Read Debounce Time Register CDh Read Transmit PCM Data E8/E9h Write/Read Ground Key Filter  PROGRAMMABLE FILTERS General Description of CSD Coefficients                                                                                   |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 88/89h Write/Read R Filter Coefficients 96/97h Write/Read B2 Filter Coefficients (IIR) 98/99h Write/Read FIR Z Filter Coefficients (FIR only) 9A/9Bh Write/Read IIR Z Filter Coefficients (IIR only) C8/C9h Write/Read Debounce Time Register CDh Read Transmit PCM Data E8/E9h Write/Read Ground Key Filter  PROGRAMMABLE FILTERS General Description of CSD Coefficients User Test States and Operating Conditions                                    |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register. 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register. 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits. 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register. 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN). 80/81h Write/Read GX Filter Coefficients. 82/83h Write/Read GR Filter Coefficients (FIR and IIR). 86/87h Write/Read B1 Filter Coefficients. 88/89h Write/Read X Filter Coefficients. 88/89h Write/Read X Filter Coefficients. 88/89h Write/Read R Filter Coefficients. 96/97h Write/Read B2 Filter Coefficients (IIR). 98/99h Write/Read B1 Z Filter Coefficients (IIR). 98/99h Write/Read B1 Z Filter Coefficients (IIR). 98/99h Write/Read Debounce Time Register. CDh Read Transmit PCM Data. E8/E9h Write/Read Ground Key Filter.  PROGRAMMABLE FILTERS. General Description of CSD Coefficients. User Test States and Operating Conditions A-Law and μ-Law Companding. |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register. 4D/4Fh Read Real-Time Data Register. 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register. 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN) 80/81h Write/Read GX Filter Coefficients 82/83h Write/Read GR Filter Coefficients 84/85h Write/Read Z Filter Coefficients (FIR and IIR) 86/87h Write/Read B1 Filter Coefficients 88/89h Write/Read X Filter Coefficients 8A/8Bh Write/Read R Filter Coefficients 96/97h Write/Read B2 Filter Coefficients (IIR) 98/99h Write/Read B1 Filter Coefficients (FIR only) 9A/9Bh Write/Read Debounce Time Register CDh Read Transmit PCM Data E8/E9h Write/Read Ground Key Filter  PROGRAMMABLE FILTERS General Description of CSD Coefficients User Test States and Operating Conditions A-Law and μ-Law Companding  APPLICATIONS                                                  |    |

| 4A/4Bh Write/Read Channel Enable and Operating Mode Register 4D/4Fh Read Real-Time Data Register. 50/51h Write/Read AISN and Analog Gains 52/53h Write/Read SLIC Device Input/Output Register. 54/55h Write/Read SLIC Input/Output Direction, Read Status Bits. 60/61h Write/Read Operating Functions 6C/6Dh Write/Read Interrupt Mask Register. 70/71h Write/Read Operating Conditions 73h Read Revision Code Number (RCN). 80/81h Write/Read GX Filter Coefficients. 82/83h Write/Read GR Filter Coefficients (FIR and IIR). 86/87h Write/Read B1 Filter Coefficients. 88/89h Write/Read X Filter Coefficients. 88/89h Write/Read X Filter Coefficients. 88/89h Write/Read R Filter Coefficients. 96/97h Write/Read B2 Filter Coefficients (IIR). 98/99h Write/Read B1 Z Filter Coefficients (IIR). 98/99h Write/Read B1 Z Filter Coefficients (IIR). 98/99h Write/Read Debounce Time Register. CDh Read Transmit PCM Data. E8/E9h Write/Read Ground Key Filter.  PROGRAMMABLE FILTERS. General Description of CSD Coefficients. User Test States and Operating Conditions A-Law and μ-Law Companding. |    |

| APPLICATION CIRCUIT      | 61         |

|--------------------------|------------|

| LINE CARD PARTS LIST     | 61         |

| PHYSICAL DIMENSIONS      | 62         |

| 32-Pin PLCC              | 62         |

| 44-Pin PLCC              |            |

| 44-Pin TQFP              | 34         |

| REVISION HISTORY         | <b>6</b> 5 |

| Revision A1 to A2        | 35         |

| Revision A2 to B1        | 35         |

| Revision B1 to C1        |            |

| Revision C1 to D1        |            |

| Revision D1 to E1        |            |

| Revision E1 to F1        |            |

| Revision F1 to F2        | 35         |

| Revision F2 to Version 9 | 35         |

## **LIST OF FIGURES**

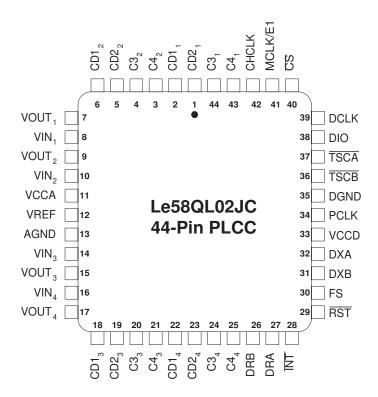

| Figure 1.  | Le58QL02JC 44-Pin PLCC                                                 | .7 |

|------------|------------------------------------------------------------------------|----|

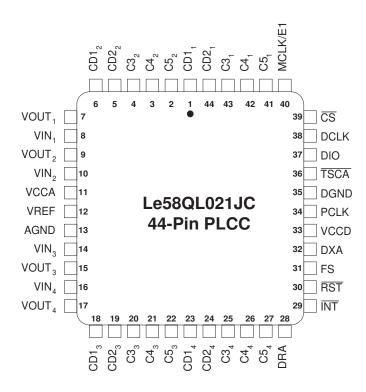

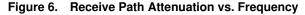

| Figure 2.  | Le58QL021JC 44-Pin PLCC                                                | .8 |

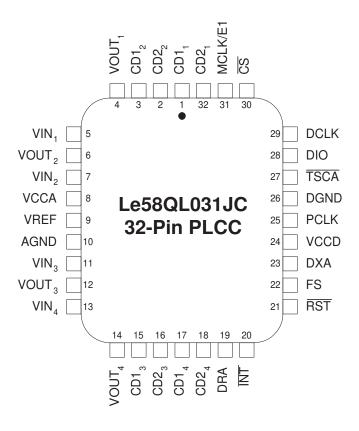

| Figure 3.  | Le58QL031JC 32-Pin PLCC                                                | .8 |

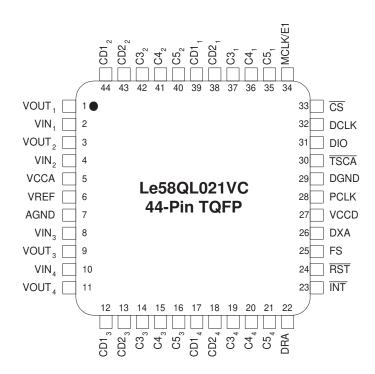

| Figure 4.  | Le58QL021VC 44-Pin PLCC                                                | .9 |

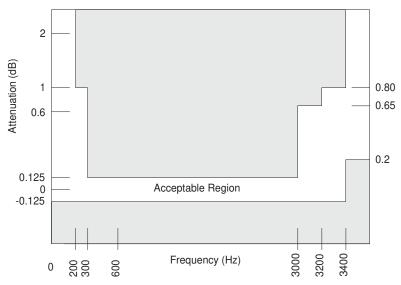

| Figure 5.  | Transmit Path Attenuation vs. Frequency                                | 15 |

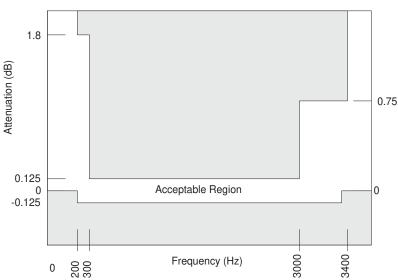

| Figure 6.  | Receive Path Attenuation vs. Frequency                                 | 15 |

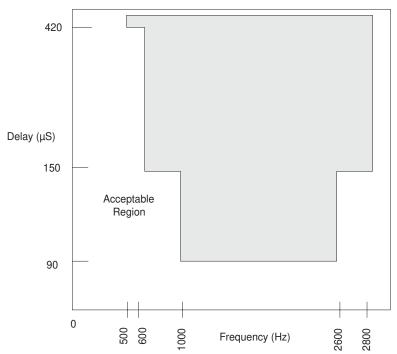

| Figure 7.  | Group Delay Distortion                                                 | 16 |

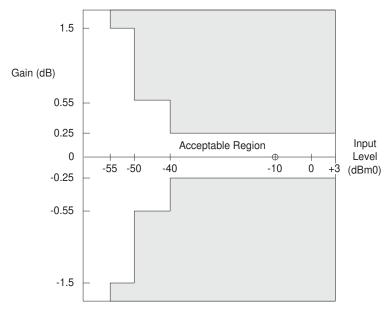

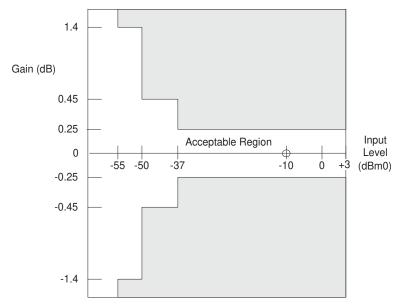

| Figure 8.  | A-law Gain Linearity with Tone Input (Both Paths)                      | 17 |

| Figure 9.  | μ-law Gain Linearity with Tone Input (Both Paths)                      | 17 |

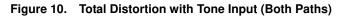

| Figure 10. | Total Distortion with Tone Input (Both Paths)                          | 18 |

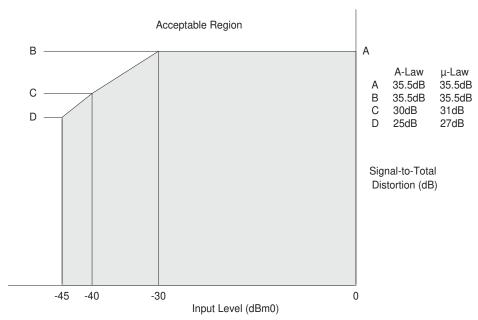

| Figure 11. | Discrimination Against Out-of-Band Signals                             | 19 |

| Figure 12. | Spurious Out-of-Band Signals                                           |    |

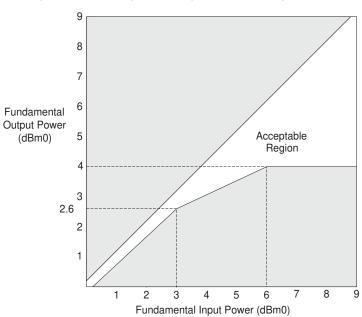

| Figure 13. | Analog-to-Analog Overload Compression                                  | 21 |

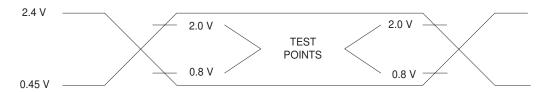

| Figure 14. | Input and Output Waveforms for AC Tests                                | 24 |

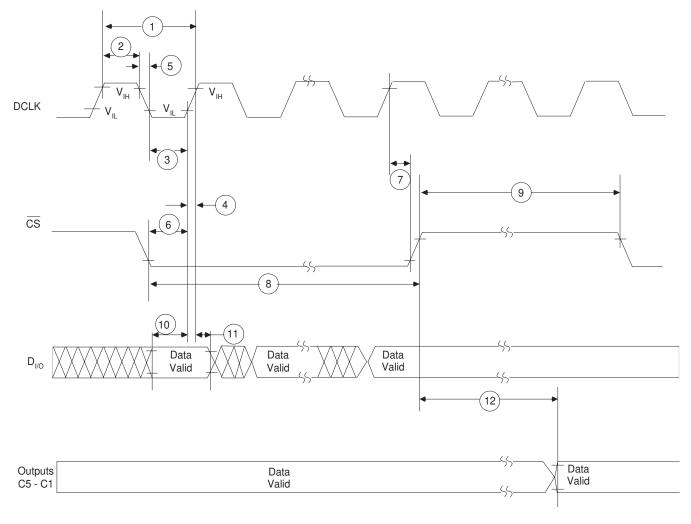

| Figure 15. | Microprocessor Interface (Input Mode)                                  |    |

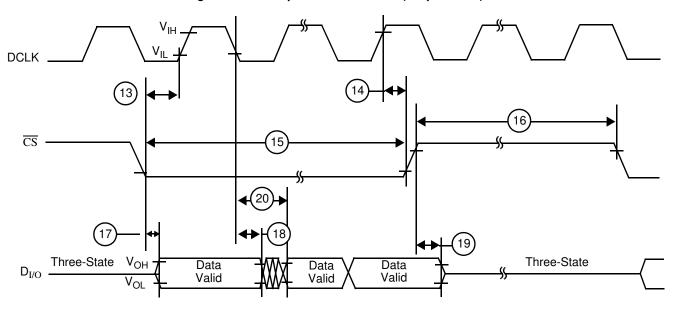

| Figure 16. | Microprocessor Interface (Output Mode)                                 |    |

| Figure 17. | PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge)         |    |

| Figure 18. | PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge)         |    |

| Figure 19. | Master Clock Timing                                                    |    |

| Figure 20. | Clock Mode Options                                                     |    |

| Figure 21. | SLIC Device I/O E1 Multiplex and Real-Time Data Register Operation     |    |

| Figure 22. | E1 Multiplex Internal Timing                                           |    |

| Figure 23. | MPI Real-Time Data Register                                            |    |

| Figure 24. | QLSLAC Device Transmission Block Diagram                               |    |

| Figure 25. | Robbed-Bit Frame                                                       |    |

| Figure 26. | Le7920 SLIC/QLSLAC Device Application Circuit                          | 31 |

| LIST OF    | TABLES                                                                 |    |

|            | QLSLAC Device Configurations                                           |    |

| Table 2.   | 0 dBm0 Voltage Definitions with Unity Gain in X, R, GX, GR, AX, and AR | 14 |

| Table 3.   | Channel Parameters                                                     | 38 |

|            | Channel Monitors                                                       |    |

|            | Global Chip Parameters                                                 |    |

|            | Global Chip Status Monitors                                            |    |

|            | A-Law: Positive Input Values                                           |    |

| Table 8.   | μ-Law: Positive Input Values                                           | 59 |

### PRODUCT DESCRIPTION

The QLSLAC device performs the codec/filter and two-to-four-wire conversion functions required of the subscriber line interface circuitry in telecommunications equipment. These functions involve converting audio signals into digital PCM samples and converting digital PCM samples back into audio signals. During conversion, digital filters are used to band limit the voice signals. All of the digital filtering is performed in digital signal processors operating from a master clock, which can be derived either from PCLK or MCLK.

Four independent channels allow the QLSLAC device to function as four SLAC<sup>TM</sup> devices. For programming information, each channel has its own enable bit (EC1, EC2, EC3, and EC4) to allow individual channel programming. If more than one Channel Enable bit is High or if all Channel Enable bits are High, all channels enabled will receive the programming information written; therefore, a Broadcast mode can be implemented by simply enabling all channels in the device to receive the information. The Channel Enable bits are contained in the Channel Enable (EC) register, which is written and read using Command 4A/4Bh. The Broadcast mode is useful in initializing QLSLAC devices in a large system.

The user-programmable filters set the receive and transmit gain, perform the transhybrid balancing function, permit adjustment of the two-wire termination impedance, and provide equalization of the receive and transmit paths. All programmable digital filter coefficients can be calculated using the WinSLAC™ software.

Data transmitted or received on the PCM highway can be 8-bit companded code (with an optional 8-bit signaling byte in the transmit direction) or 16-bit linear code. The 8-bit codes appear 1 byte per time slot, while the 16-bit code appears in two consecutive time slots. The compressed PCM codes can be either 8-bit companded A-law or  $\mu$ -law. The PCM data is read from and written to the PCM highway in user-programmable time slots at rates of 128 kHz to 8.192 MHz. The transmit clock edge and clock slot can be selected for compatibility with other devices that can be connected to the PCM highway.

Three configurations of the QLSLAC device are offered with single or dual PCM highways. The Le58QL02 and Le58QL021 QLSLAC devices with dual and single PCM highways respectively are available in the 44-pin packages. The Le58QL031JC QLSLAC device is a single PCM highway version in a 32-pin PLCC package.

|             | · ·                          |               |              |                     |

|-------------|------------------------------|---------------|--------------|---------------------|

| PCM Highway | Programmable I/O per Channel | Chopper Clock | Package      | Part Number         |

| Dual        | Four I/O                     | Yes           | 44 PLCC      | Le58QL02JC          |

| Single      | Five I/O                     | No            | 44 PLCC/TQFP | Le58QL021JC (or VC) |

| Single      | Two I/O                      | No            | 32 PLCC      | Le58QL031JC         |

Table 1. QLSLAC Device Configurations

### **BLOCK DESCRIPTIONS**

#### **Clock and Reference Circuits**

This block generates a master clock and a frame sync signal for the digital circuits. It also generates an analog reference voltage for the analog circuits.

### **Microprocessor Interface (MPI)**

This block communicates with the external control microprocessor over a serial interface. It passes user control information to the other blocks, and it passes status information from the blocks to the user. In addition, this block contains the reset circuitry.

### **Time Slot Assigner (TSA)**