Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## LPC11Cx2/Cx4

# 32-bit ARM Cortex-M0 microcontroller; 16/32 kB flash, 8 kB SRAM; C CAN

Rev. 3.2 — 4 January 2016

Product data sheet

## 1. General description

The LPC11Cx2/Cx4 are an ARM Cortex-M0 based, low-cost 32-bit MCU family, designed for 8/16-bit microcontroller applications, offering performance, low power, simple instruction set and memory addressing together with reduced code size compared to existing 8/16-bit architectures.

The LPC11Cx2/Cx4 operate at CPU frequencies of up to 50 MHz.

The peripheral complement of the LPC11Cx2/Cx4 includes 16/32 kB of flash memory, 8 kB of data memory, one C\_CAN controller, one Fast-mode Plus I<sup>2</sup>C-bus interface, one RS-485/EIA-485 UART, two SPI interfaces with SSP features, four general purpose counter/timers, a 10-bit ADC, and up to 40 general purpose I/O pins.

On-chip C\_CAN drivers and flash In-System Programming tools via C\_CAN are included. In addition, the LPC11C22 and LPC11C24 parts include an on-chip, high-speed CAN transceiver.

## 2. Features and benefits

- System:

- ◆ ARM Cortex-M0 processor, running at frequencies of up to 50 MHz.

- ◆ ARM Cortex-M0 built-in Nested Vectored Interrupt Controller (NVIC).

- Serial Wire Debug.

- System tick timer.

- Memory:

- ◆ 32 kB (LPC11Cx4) or 16 kB (LPC11Cx2) on-chip flash program memory.

- 8 kB SRAM data memory.

- In-System Programming (ISP) and In-Application Programming (IAP) via on-chip bootloader software.

- Flash ISP commands can be issued via UART or C CAN.

- Digital peripherals:

- General Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors.

- 40 GPIO pins on the LPC11C12/C14 parts; 36 GPIO pins on the LPC11C22/C24 parts.

- GPIO pins can be used as edge and level sensitive interrupt sources.

- High-current output driver (20 mA) on one pin.

- ◆ High-current sink drivers (20 mA) on two I<sup>2</sup>C-bus pins in Fast-mode Plus.

- ◆ Four general purpose counter/timers with a total of four capture inputs and 13 (LPC11C12/C14) or 12 (LPC11C22/C24) match outputs.

- ◆ Programmable WatchDog Timer (WDT).

- Analog peripherals:

- ◆ 10-bit ADC with input multiplexing among 8 pins.

- Serial interfaces:

- ◆ UART with fractional baud rate generation, internal FIFO, and RS-485 support.

- Two SPI controllers with SSP features and with FIFO and multi-protocol capabilities.

- ◆ I<sup>2</sup>C-bus interface supporting full I<sup>2</sup>C-bus specification and Fast-mode Plus with a data rate of 1 Mbit/s with multiple address recognition and monitor mode.

- C\_CAN controller. On-chip C\_CAN and CANopen drivers included.

- ◆ On-chip, high-speed CAN transceiver (parts LPC11C22/C24 only).

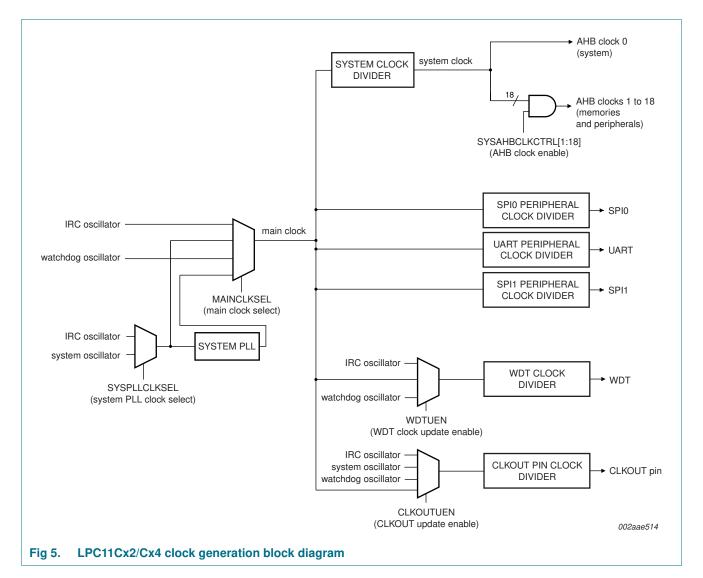

- Clock generation:

- ◆ 12 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock.

- ◆ Crystal oscillator with an operating range of 1 MHz to 25 MHz.

- ◆ Programmable watchdog oscillator with a frequency range of 7.8 kHz to 1.8 MHz.

- PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the system oscillator or the internal RC oscillator.

- Clock output function with divider that can reflect the system oscillator, IRC, CPU clock, or the Watchdog clock.

- Power control:

- Integrated PMU (Power Management Unit) to minimize power consumption during Sleep, Deep-sleep, and Deep power-down modes.

- ◆ Three reduced power modes: Sleep, Deep-sleep, and Deep power-down.

- Processor wake-up from Deep-sleep mode via a dedicated start logic using 13 of the GPIO pins.

- Power-On Reset (POR).

- Brownout detect with four separate thresholds for interrupt and forced reset.

- Unique device serial number for identification.

- Single 3.3 V power supply (1.8 V to 3.6 V).

- Available as 48-pin LQFP package.

## 3. Applications

- eMetering

- Elevator systems

- Industrial and sensor based networks

- White goods

## 4. Ordering information

Table 1. Ordering information

| Type number       | Package |                                                                                             |          |  |  |  |  |  |

|-------------------|---------|---------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

|                   | Name    | Description                                                                                 | Version  |  |  |  |  |  |

| LPC11C12FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7\times7\times1.4~\text{mm}$ | SOT313-2 |  |  |  |  |  |

| LPC11C14FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7\times7\times1.4~\text{mm}$ | SOT313-2 |  |  |  |  |  |

| LPC11C22FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body $7\times7\times1.4~\text{mm}$ | SOT313-2 |  |  |  |  |  |

| LPC11C24FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm  | SOT313-2 |  |  |  |  |  |

## 4.1 Ordering options

Table 2. Ordering options

| Type number       | Flash | Total<br>SRAM | UART<br>RS-485 | I <sup>2</sup> C/<br>Fast+ | SPI | C_CAN | C_CAN with<br>on-chip<br>CAN | GPIO<br>pins | ADC channels | Package |

|-------------------|-------|---------------|----------------|----------------------------|-----|-------|------------------------------|--------------|--------------|---------|

| LPC11C12FBD48/301 | 16 kB | 8 kB          | 1              | 1                          | 2   | 1     | no transceiver               | 40           | 8            | LQFP48  |

| LPC11C14FBD48/301 | 32 kB | 8 kB          | 1              | 1                          | 2   | 1     | no                           | 40           | 8            | LQFP48  |

| LPC11C22FBD48/301 | 16 kB | 8 kB          | 1              | 1                          | 2   | 1     | yes                          | 36           | 8            | LQFP48  |

| LPC11C24FBD48/301 | 32 kB | 8 kB          | 1              | 1                          | 2   | 1     | yes                          | 36           | 8            | LQFP48  |

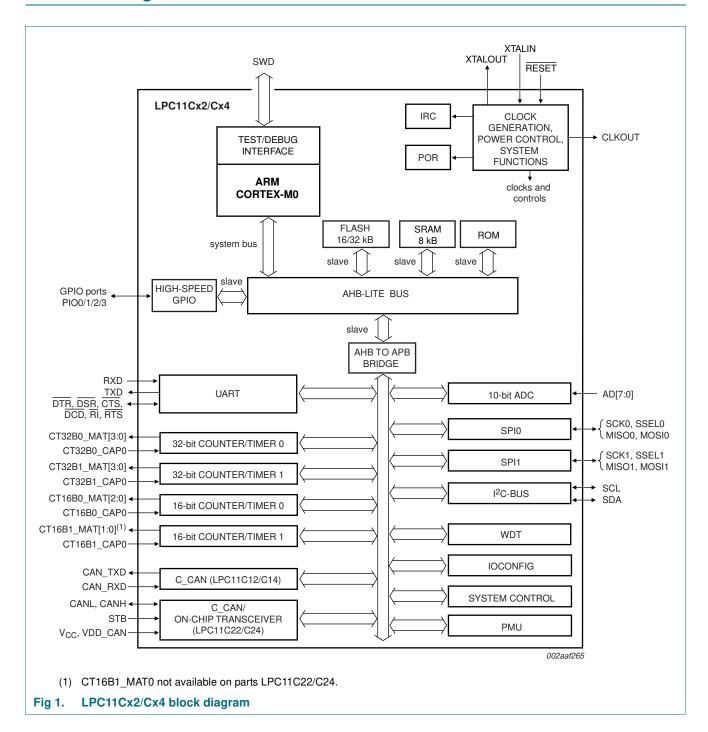

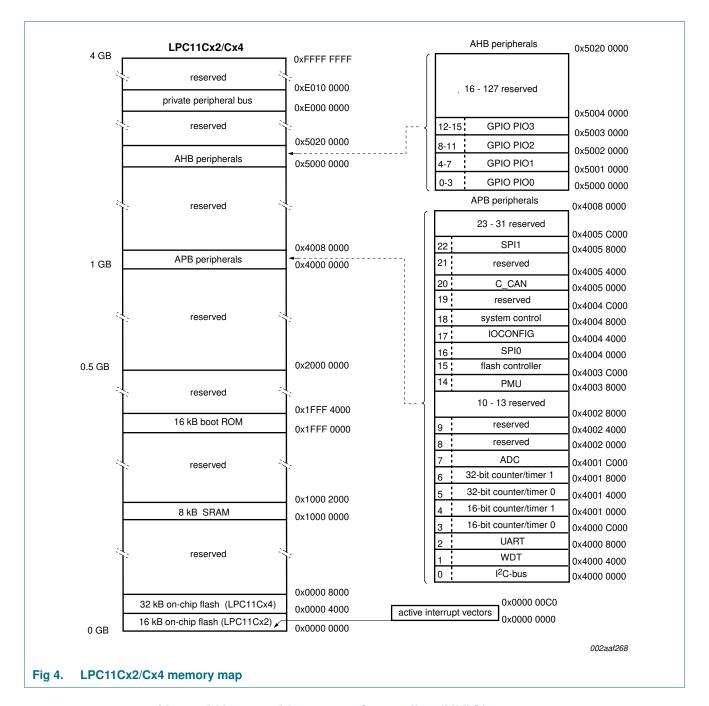

## 5. Block diagram

## 6. Pinning information

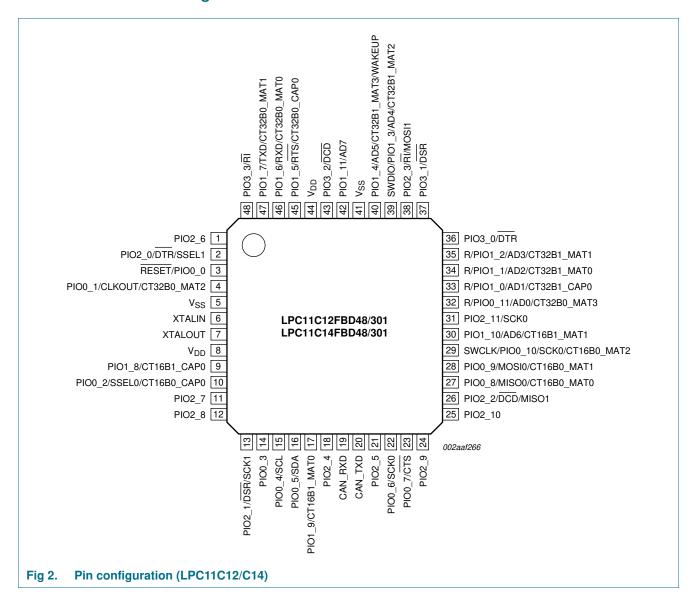

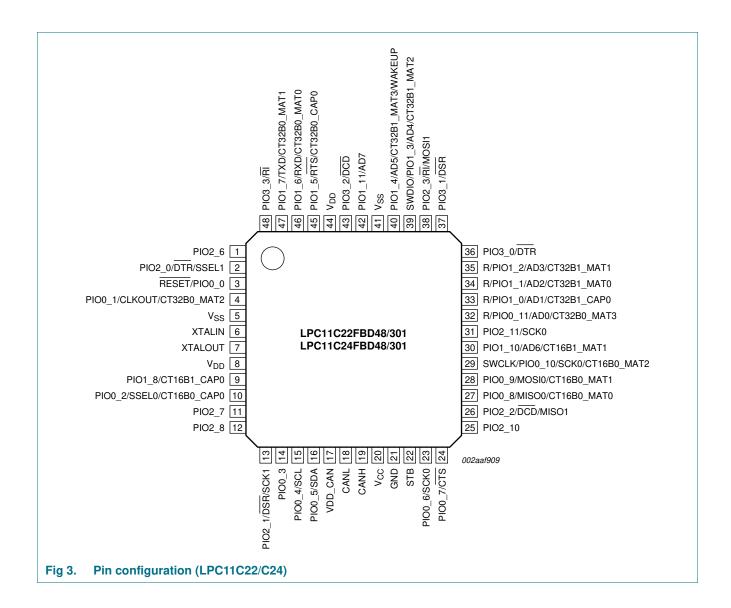

## 6.1 Pinning

## 6.2 Pin description

Table 3. LPC11C12/C14 pin description table

| Symbol                        | Pin                 | Start<br>logic<br>inputs | Туре   | Reset state      | Description                                                                                                                                                                                                                                                |

|-------------------------------|---------------------|--------------------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11             |                     |                          |        |                  | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                               |

| RESET/PIO0_0                  | 3[2]                | yes                      | I      | I; PU            | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0.         |

|                               |                     |                          | I/O    | -                | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                         |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 4[3]                | yes                      | I/O    | I; PU            | <b>PIOO_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the flash ISP command handler via UART (if PIOO_3 is HIGH) or via C_CAN (if PIOO_3 is LOW).                                                          |

|                               |                     |                          | 0      | -                | CLKOUT — Clockout pin.                                                                                                                                                                                                                                     |

|                               |                     |                          | 0      | -                | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                           |

| PIO0_2/SSEL0/                 | 10[3]               | yes                      | I/O    | I; PU            | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                         |

| CT16B0_CAP0                   |                     |                          | I/O    | -                | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                             |

|                               |                     |                          | I      | -                | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                          |

| PIO0_3                        | 14 <sup>[3]</sup>   | yes                      | I/O    | I; PU            | PIO0_3 — General purpose digital input/output pin. This pin is monitored during reset: Together with a LOW level on pin PIO0_1, a LOW level starts the flash ISP command handler via C_CAN and a HIGH level starts the flash ISP command handler via UART. |

| PIO0_4/SCL                    | 15 <mark>4</mark>   | yes                      | I/O    | I; IA            | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                            |

|                               |                     |                          | I/O    | -                | $ {\bf SCL-l^2C} - bus, open-drain clock input/output. High-current sink only if l^2C Fast-mode Plus is selected in the l/O configuration register. $                                                                                                      |

| PIO0_5/SDA                    | 16 <mark>4</mark>   | yes                      | I/O    | I; IA            | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                            |

|                               |                     |                          | I/O    | -                | <b>SDA</b> — $I^2$ C-bus, open-drain data input/output. High-current sink only if $I^2$ C Fast-mode Plus is selected in the I/O configuration register.                                                                                                    |

| PIO0_6/SCK0                   | 22[3]               | yes                      | I/O    | I; PU            | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                         |

|                               |                     |                          | I/O    | -                | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                              |

| PIO0_7/CTS                    | 23[3]               | yes                      | I/O    | I; PU            | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                     |

|                               |                     |                          | 1      | -                | CTS — Clear To Send input for UART.                                                                                                                                                                                                                        |

| PIO0_8/MISO0/                 | 27 <mark>3</mark>   | yes                      | I/O    | I; PU            | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                         |

| CT16B0_MAT0                   |                     |                          | I/O    | -                | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                                      |

|                               |                     |                          | 0      | -                | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                           |

| PIO0_9/MOSI0/                 | 28[3]               | yes                      | I/O    | I; PU            | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                         |

| CT16B0_MAT1                   |                     |                          | I/O    | -                | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                                      |

|                               |                     |                          | 0      | -                | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                           |

| SWCLK/PIO0_10/                | 29 <mark>[3]</mark> | yes                      | I      | I; PU            | SWCLK — Serial wire clock.                                                                                                                                                                                                                                 |

| SCK0/<br>CT16B0_MAT2          |                     |                          | I/O    | -                | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                        |

| OTTOBU_WATZ                   |                     |                          | I/O    | -                | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                              |

|                               |                     |                          | 0      | -                | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                           |

| LPC11CX2_CX4                  |                     |                          | All ir | nformation provi | ided in this document is subject to legal disclaimers.  © NXP B.V. 2016. All rights reserve                                                                                                                                                                |

Table 3. LPC11C12/C14 pin description table

| Symbol                       | Pin                 | Start<br>logic<br>inputs | Туре | Reset state | Description                                                                                                                                                                                                                                          |

|------------------------------|---------------------|--------------------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/PIO0_11/<br>AD0/           | 325                 | yes                      | -    | I; PU       | ${\bf R}$ — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                     |

| CT32B0_MAT3                  |                     |                          | I/O  | -           | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                  |

|                              |                     |                          | I    | -           | AD0 — A/D converter, input 0.                                                                                                                                                                                                                        |

|                              |                     |                          | 0    | -           | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                     |

| PIO1_0 to PIO1_11            |                     |                          |      |             | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                         |

| R/PIO1_0/AD1/<br>CT32B1_CAP0 | 33[5]               | yes                      | -    | I; PU       | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                              |                     |                          | I/O  | -           | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                   |

|                              |                     |                          | I    | -           | AD1 — A/D converter, input 1.                                                                                                                                                                                                                        |

|                              |                     |                          | I    | -           | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                    |

| R/PIO1_1/AD2/<br>CT32B1_MAT0 | 34[5]               | no                       | -    | I; PU       | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                              |                     |                          | I/O  | -           | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                   |

|                              |                     |                          | I    | -           | AD2 — A/D converter, input 2.                                                                                                                                                                                                                        |

|                              |                     |                          | 0    | -           | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                     |

| R/PIO1_2/AD3/<br>CT32B1_MAT1 | 35 <u>[5]</u>       | no                       | -    | I; PU       | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                              |                     |                          | I/O  | -           | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                   |

|                              |                     |                          | I    | -           | AD3 — A/D converter, input 3.                                                                                                                                                                                                                        |

|                              |                     |                          | 0    | -           | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                     |

| SWDIO/PIO1_3/                | 39 <u>[5]</u>       | no                       | I/O  | I; PU       | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                              |

| AD4/<br>CT32B1_MAT2          |                     |                          | I/O  | -           | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                   |

| 0132B1_WA12                  |                     |                          | I    | -           | AD4 — A/D converter, input 4.                                                                                                                                                                                                                        |

|                              |                     |                          | 0    | -           | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                     |

| PIO1_4/AD5/<br>CT32B1_MAT3/  | 405                 | no                       | I/O  | I; PU       | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                   |

| WAKEUP                       |                     |                          | I    | -           | AD5 — A/D converter, input 5.                                                                                                                                                                                                                        |

|                              |                     |                          | 0    | -           | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                     |

|                              |                     |                          | I    | -           | <b>WAKEUP</b> — Deep power-down mode wake-up pin with 20 ns glitch filter. This pin must be pulled HIGH externally to enter Deep power-down mode and pulled LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

| PIO1_5/RTS/                  | 45 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                   |

| CT32B0_CAP0                  |                     |                          | 0    | -           | RTS — Request To Send output for UART.                                                                                                                                                                                                               |

|                              |                     |                          | I    | -           | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                    |

| PIO1_6/RXD/                  | 46 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                                                                   |

| CT32B0_MAT0                  |                     |                          |      | -           | RXD — Receiver input for UART.                                                                                                                                                                                                                       |

|                              |                     |                          | 0    | -           | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                                                                     |

Table 3. LPC11C12/C14 pin description table

| Symbol            | Pin                 | Start<br>logic<br>inputs | Туре | Reset state | Description                                                                                                                                                                                                                                            |

|-------------------|---------------------|--------------------------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO1_7/TXD/       | 47 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO1_7 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| CT32B0_MAT1       |                     |                          | 0    | -           | TXD — Transmitter output for UART.                                                                                                                                                                                                                     |

|                   |                     |                          | 0    | -           | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                                                                                                                                                                       |

| PIO1_8/           | 9[3]                | no                       | I/O  | I; PU       | PIO1_8 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| CT16B1_CAP0       |                     |                          | I    | -           | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                                                                                                                                                                                                      |

| PIO1_9/           | 17 <mark>3</mark>   | no                       | I/O  | I; PU       | PIO1_9 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| CT16B1_MAT0       |                     |                          | 0    | -           | CT16B1_MAT0 — Match output 0 for 16-bit timer 1.                                                                                                                                                                                                       |

| PIO1_10/AD6/      | 30[5]               | no                       | I/O  | I; PU       | PIO1_10 — General purpose digital input/output pin.                                                                                                                                                                                                    |

| CT16B1_MAT1       |                     |                          | I    | -           | AD6 — A/D converter, input 6.                                                                                                                                                                                                                          |

|                   |                     |                          | 0    | -           | CT16B1_MAT1 — Match output 1 for 16-bit timer 1.                                                                                                                                                                                                       |

| PIO1_11/AD7       | 42[5]               | no                       | I/O  | I; PU       | PIO1_11 — General purpose digital input/output pin.                                                                                                                                                                                                    |

|                   |                     |                          | I    | -           | AD7 — A/D converter, input 7.                                                                                                                                                                                                                          |

| PIO2_0 to PIO2_11 |                     |                          |      |             | <b>Port 2</b> — Port 2 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 2 pins depends on the function selected through the IOCONFIG register block.                                           |

| PIO2_0/DTR/       |                     | no                       | I/O  | I; PU       | PIO2_0 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| SSEL1             |                     |                          | I/O  | -           | DTR — Data Terminal Ready output for UART.                                                                                                                                                                                                             |

|                   |                     |                          | I/O  | -           | SSEL1 — Slave Select for SPI1.                                                                                                                                                                                                                         |

| PIO2_1/DSR/SCK1   | 13 <mark>3</mark> r | no                       | I/O  | I; PU       | PIO2_1 — General purpose digital input/output pin.                                                                                                                                                                                                     |

|                   |                     |                          | I    | -           | DSR — Data Set Ready input for UART.                                                                                                                                                                                                                   |

|                   |                     |                          | I/O  | -           | SCK1 — Serial clock for SPI1.                                                                                                                                                                                                                          |

| PIO2_2/DCD/       | 26 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO2_2 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| MISO1             |                     |                          |      | -           | DCD — Data Carrier Detect input for UART.                                                                                                                                                                                                              |

|                   |                     |                          | I/O  | -           | MISO1 — Master In Slave Out for SPI1.                                                                                                                                                                                                                  |

| PIO2_3/RI/MOSI1   | 38 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO2_3 — General purpose digital input/output pin.                                                                                                                                                                                                     |

|                   |                     |                          |      | -           | RI — Ring Indicator input for UART.                                                                                                                                                                                                                    |

|                   |                     |                          | I/O  | -           | MOSI1 — Master Out Slave In for SPI1.                                                                                                                                                                                                                  |

| PIO2_4            | 18 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO2_4 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| PIO2_5            | 21 <u>[3]</u>       | no                       | I/O  | I; PU       | PIO2_5 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| PIO2_6            | 1 <u>[3]</u>        | no                       | I/O  | I; PU       | PIO2_6 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| PIO2_7            | 11 <u>[3]</u>       | no                       | I/O  | I; PU       | PIO2_7 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| PIO2_8            | 12 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO2_8 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| PIO2_9            | 24 <u>[3]</u>       | no                       | I/O  | I; PU       | PIO2_9 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| PIO2_10           | 25 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO2_10 — General purpose digital input/output pin.                                                                                                                                                                                                    |

| PIO2_11/SCK0      | 31 <u>[3]</u>       | no                       | I/O  | I; PU       | PIO2_11 — General purpose digital input/output pin.                                                                                                                                                                                                    |

|                   |                     |                          | I/O  | -           | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                          |

| PIO3_0 to PIO3_3  |                     |                          |      |             | <b>Port 3</b> — Port 3 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 3 pins depends on the function selected through the IOCONFIG register block. Pins PIO3_4 to PIO3_11 are not available. |

Table 3. LPC11C12/C14 pin description table

| Symbol     | Pin                 | Start<br>logic<br>inputs | Туре | Reset state | Description                                                                                                       |

|------------|---------------------|--------------------------|------|-------------|-------------------------------------------------------------------------------------------------------------------|

| PIO3_0/DTR | 36 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO3_0 — General purpose digital input/output pin.                                                                |

|            |                     |                          | 0    | -           | <b>DTR</b> — Data Terminal Ready output for UART.                                                                 |

| PIO3_1/DSR | 37 <mark>3</mark>   | no                       | I/O  | I; PU       | PIO3_1 — General purpose digital input/output pin.                                                                |

|            |                     |                          | I    | -           | DSR — Data Set Ready input for UART.                                                                              |

| PIO3_2/DCD | 43 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO3_2 — General purpose digital input/output pin.                                                                |

|            |                     |                          | I    |             | DCD — Data Carrier Detect input for UART.                                                                         |

| PIO3_3/RI  | 48 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO3_3 — General purpose digital input/output pin.                                                                |

|            |                     |                          | I    | -           | RI — Ring Indicator input for UART.                                                                               |

| CAN_RXD    | 19 <mark>6</mark> ] | no                       | I    | I; IA       | CAN_RXD — C_CAN receive data input.                                                                               |

| CAN_TXD    | 20[6]               | no                       | 0    | I; IA       | CAN_TXD — C_CAN transmit data output.                                                                             |

| $V_{DD}$   | 8; 44               | -                        | I    | -           | Supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage. |

| XTALIN     | 6[7]                | -                        | I    | -           | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V.       |

| XTALOUT    | 7 <u>[7]</u>        | -                        | 0    | -           | Output from the oscillator amplifier.                                                                             |

| $V_{SS}$   | 5; 41               | -                        | I    | -           | Ground.                                                                                                           |

- [1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level); IA = inactive, no pull-up/down enabled.

- [2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode. See Figure 27 for the reset pad configuration.

- [3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 26).

- [4]  $I^2C$ -bus pads compliant with the  $I^2C$ -bus specification for  $I^2C$  standard mode and  $I^2C$  Fast-mode Plus.

- [5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 26).

- [6] 5 V tolerant digital I/O pad without pull-up/pull-down resistors.

- [7] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

Table 4. LPC11C22/C24 pin description table

| Symbol            | Pin  | Start<br>logic<br>inputs | Туре | Reset state | Description                                                                                                                                                                                                                                        |

|-------------------|------|--------------------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11 |      |                          |      |             | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                       |

| RESET/PIO0_0      | 3[2] | yes                      | I    | I; PU       | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                   |      |                          | I/O  | -           | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

Table 4. LPC11C22/C24 pin description table

| Symbol                        | Pin                      | Start<br>logic<br>inputs | Туре     | Reset state | Description                                                                                                                                                                                                                                                |

|-------------------------------|--------------------------|--------------------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 4 <u>[3]</u>             | yes                      | I/O      | I; PU       | <b>PIOO_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the flash ISP command handler via UART (if PIOO_3 is HIGH) or via C_CAN (if PIOO_3 is LOW).                                                          |

|                               |                          |                          | 0        | -           | CLKOUT — Clockout pin.                                                                                                                                                                                                                                     |

|                               |                          |                          | 0        | -           | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                           |

| PIO0_2/SSEL0/                 | 10 <mark>[3]</mark>      | yes                      | I/O      | I; PU       | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                         |

| CT16B0_CAP0                   |                          |                          | I/O      | -           | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                             |

|                               |                          |                          | I        | -           | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                          |

| PIO0_3                        | 14 <u><sup>[3]</sup></u> | yes                      | I/O      | I; PU       | PIO0_3 — General purpose digital input/output pin. This pin is monitored during reset: Together with a LOW level on pin PIO0_1, a LOW level starts the flash ISP command handler via C_CAN and a HIGH level starts the flash ISP command handler via UART. |

| PIO0_4/SCL                    | 15 <mark>[4]</mark>      | yes                      | I/O      | I; IA       | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                            |

|                               |                          |                          | I/O      | -           | $ {\bf SCL-l}^2 {\bf C}\text{-bus, open-drain clock input/output. High-current sink only if l}^2 {\bf C} \ {\bf Fast-mode Plus is selected in the l/O configuration register.} $                                                                           |

| PIO0_5/SDA                    | 16 <mark>4</mark> ye     | yes                      | I/O      | I; IA       | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                            |

|                               |                          |                          | I/O      | -           | <b>SDA</b> — $I^2$ C-bus, open-drain data input/output. High-current sink only if $I^2$ C Fast-mode Plus is selected in the I/O configuration register.                                                                                                    |

| PIO0_6/SCK0                   | 23 <mark>[3]</mark>      | yes                      | I/O      | I; PU       | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                         |

|                               |                          |                          | I/O      | -           | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                              |

| PIO0_7/CTS                    | 24[3]                    | yes                      | I/O      | I; PU       | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                                     |

|                               |                          |                          | I        | -           | CTS — Clear To Send input for UART.                                                                                                                                                                                                                        |

| PIO0_8/MISO0/                 | 27 <mark>[3]</mark>      | yes                      | I/O      | I; PU       | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                         |

| CT16B0_MAT0                   |                          |                          | I/O      | -           | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                                      |

|                               |                          |                          | 0        | -           | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                           |

| PIO0_9/MOSI0/                 | 28 <mark>[3]</mark>      | yes                      | I/O      | I; PU       | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                         |

| CT16B0_MAT1                   |                          |                          | I/O      | -           | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                                      |

|                               |                          |                          | 0        | -           | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                           |

| SWCLK/PIO0_10/                | 29 <mark>[3]</mark>      | yes                      | <u> </u> | I; PU       | SWCLK — Serial wire clock.                                                                                                                                                                                                                                 |

| SCK0/<br>CT16B0_MAT2          |                          |                          | I/O      | -           | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                        |

| 011000_1111112                |                          |                          | I/O      | -           | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                              |

|                               |                          |                          | 0        | -           | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                           |

| R/PIO0_11/<br>AD0/            |                          | yes                      | -        | I; PU       | ${\bf R}$ — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                           |

| CT32B0_MAT3                   |                          |                          | I/O      | -           | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                        |

|                               |                          |                          | I        | -           | AD0 — A/D converter, input 0.                                                                                                                                                                                                                              |

|                               |                          |                          | 0        | -           | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                           |

| PIO1_0 to PIO1_11             |                          |                          |          |             | <b>Port 1</b> — Port 1 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 1 pins depends on the function selected through the IOCONFIG register block.                                               |

Table 4. LPC11C22/C24 pin description table

| Table 4. LPC11C22/C24 pin description table |                     |                          |      |             |                                                                                                                                                                                                                                                      |  |  |

|---------------------------------------------|---------------------|--------------------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                                      | Pin                 | Start<br>logic<br>inputs | Туре | Reset state | Description                                                                                                                                                                                                                                          |  |  |

| R/PIO1_0/AD1/<br>CT32B1_CAP0                | 33[5]               | yes                      | -    | I; PU       | ${\bf R}$ — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                     |  |  |

|                                             |                     |                          | I/O  | -           | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

|                                             |                     |                          | 1    | -           | AD1 — A/D converter, input 1.                                                                                                                                                                                                                        |  |  |

|                                             |                     |                          | 1    | -           | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                    |  |  |

| R/PIO1_1/AD2/<br>CT32B1_MAT0                | 34[5]               | no                       | -    | I; PU       | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |  |  |

|                                             |                     |                          | I/O  | -           | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

|                                             |                     |                          | 1    | -           | AD2 — A/D converter, input 2.                                                                                                                                                                                                                        |  |  |

|                                             |                     |                          | 0    | -           | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                     |  |  |

| R/PIO1_2/AD3/<br>CT32B1_MAT1                | 35 <u>[5]</u>       | no                       | -    | I; PU       | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |  |  |

|                                             |                     |                          | I/O  | -           | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

|                                             |                     |                          | I    | -           | AD3 — A/D converter, input 3.                                                                                                                                                                                                                        |  |  |

|                                             |                     |                          | 0    | -           | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                     |  |  |

| SWDIO/PIO1_3/                               | 39 <mark>[5]</mark> | no                       | I/O  | I; PU       | <b>SWDIO</b> — Serial wire debug input/output.                                                                                                                                                                                                       |  |  |

| AD4/                                        |                     |                          | I/O  | -           | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

| CT32B1_MAT2                                 |                     |                          | I    | -           | AD4 — A/D converter, input 4.                                                                                                                                                                                                                        |  |  |

|                                             |                     |                          | 0    | -           | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                     |  |  |

| PIO1_4/AD5/<br>CT32B1_MAT3/                 | 40[5]               | no                       | I/O  | I; PU       | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                   |  |  |

| WAKEUP                                      |                     |                          | 1    | -           | AD5 — A/D converter, input 5.                                                                                                                                                                                                                        |  |  |

|                                             |                     |                          | 0    | -           | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                     |  |  |

|                                             |                     |                          | I    | -           | <b>WAKEUP</b> — Deep power-down mode wake-up pin with 20 ns glitch filter. This pin must be pulled HIGH externally to enter Deep power-down mode and pulled LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |  |  |

| PIO1_5/RTS/                                 | 45 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

| CT32B0_CAP0                                 |                     |                          | 0    | -           | RTS — Request To Send output for UART.                                                                                                                                                                                                               |  |  |

|                                             |                     |                          | I    | -           | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                    |  |  |

| PIO1_6/RXD/                                 | 46 <mark>[3]</mark> | no                       | I/O  | I; PU       | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

| CT32B0_MAT0                                 |                     |                          | I    | -           | RXD — Receiver input for UART.                                                                                                                                                                                                                       |  |  |

|                                             |                     |                          | 0    | -           | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                                                                     |  |  |

| PIO1_7/TXD/                                 | 47 <mark>3</mark>   | no                       | I/O  | I; PU       | PIO1_7 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

| CT32B0_MAT1                                 |                     |                          | 0    | -           | TXD — Transmitter output for UART.                                                                                                                                                                                                                   |  |  |

|                                             |                     |                          | 0    | -           | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                                                                                                                                                                     |  |  |

| PIO1_8/                                     | 9 <mark>[3]</mark>  | no                       | I/O  | I; PU       | PIO1_8 — General purpose digital input/output pin.                                                                                                                                                                                                   |  |  |

| CT16B1_CAP0                                 |                     |                          | I    | -           | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                                                                                                                                                                                                    |  |  |

| PIO1_10/AD6/                                | 30[5]               | no                       | I/O  | I; PU       | PIO1_10 — General purpose digital input/output pin.                                                                                                                                                                                                  |  |  |

| CT16B1_MAT1                                 |                     |                          | I    | -           | AD6 — A/D converter, input 6.                                                                                                                                                                                                                        |  |  |

|                                             |                     |                          | 0    | -           | CT16B1_MAT1 — Match output 1 for 16-bit timer 1.                                                                                                                                                                                                     |  |  |

Table 4. LPC11C22/C24 pin description table

| Symbol            | Pin                 | Start<br>logic<br>inputs | Type | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                            |

|-------------------|---------------------|--------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO1_11/AD7       | 42[5]               | no                       | I/O  | I; PU                 | PIO1_11 — General purpose digital input/output pin.                                                                                                                                                                                                    |

|                   |                     |                          | I    | -                     | AD7 — A/D converter, input 7.                                                                                                                                                                                                                          |

| PIO2_0 to PIO2_11 |                     |                          |      |                       | <b>Port 2</b> — Port 2 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 2 pins depends on the function selected through the IOCONFIG register block.                                           |

| PIO2_0/DTR/       | 2[3]                | no                       | I/O  | I; PU                 | PIO2_0 — General purpose digital input/output pin.                                                                                                                                                                                                     |

| SSEL1             |                     |                          | I/O  | -                     | DTR — Data Terminal Ready output for UART.                                                                                                                                                                                                             |

|                   |                     |                          | I/O  | -                     | SSEL1 — Slave Select for SPI1.                                                                                                                                                                                                                         |

| PIO2_1/DSR/SCK1   | 13 <mark>[3]</mark> | no                       | I/O  | I; PU                 | PIO2_1 — General purpose digital input/output pin.                                                                                                                                                                                                     |

|                   |                     |                          | I    | -                     | DSR — Data Set Ready input for UART.                                                                                                                                                                                                                   |