# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **LPC804**

32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ microcontroller; up to 32 KB flash and 4 KB SRAM; 12-bit ADC; Comparator; 10-bit DAC; Capacitive Touch Interface; Programmable Logic Unit

Rev. 1.4 — 12 July 2018

Product data sheet

## 1. General description

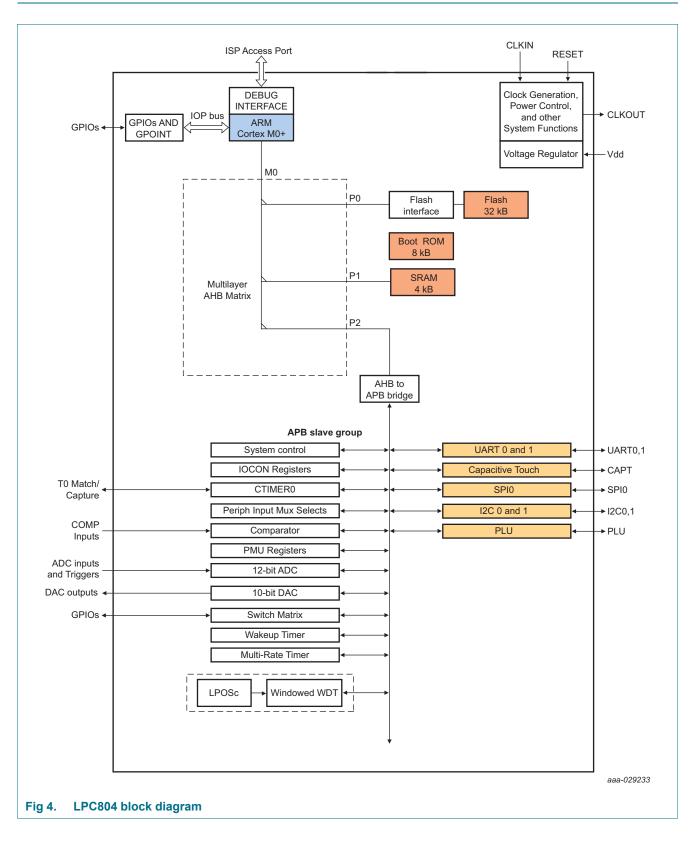

The LPC804 are an Arm Cortex-M0+ based, low-cost 32-bit MCU family operating at CPU frequencies of up to 15 MHz. The LPC804 supports 32 KB of flash memory and 4 KB of SRAM.

The peripheral complement of the LPC804 includes a CRC engine, two I<sup>2</sup>C-bus interfaces, up to two USARTs, one SPI interface, Capacitive Touch Interface (Cap Touch), one multi-rate timer, self-wake-up timer, one general purpose 32-bit counter/timer, one 12-bit ADC, one 10-bit DAC, one analog comparator, function-configurable I/O ports through a switch matrix, an input pattern match engine, Programmable Logic Unit (PLU), and up to 30 general-purpose I/O pins.

For additional documentation related to the LPC804 parts, see Section 19.

## 2. Features and benefits

- System:

- Arm Cortex-M0+ processor (revision r0p1), running at frequencies of up to 15 MHz with single-cycle multiplier and fast single-cycle I/O port.

- Arm Cortex-M0+ built-in Nested Vectored Interrupt Controller (NVIC).

- System tick timer.

- AHB multilayer matrix.

- Serial Wire Debug (SWD) with four break points and two watch points. JTAG boundary scan (BSDL) supported.

- Memory:

- Up to 32 KB on-chip EEPROM based flash programming memory.

- Code Read Protection (CRP).

- ◆ 4 KB SRAM.

- Dual I/O power (LPC804M111JDH24):

- Independent supplies on each package side permitting level-shifting signals from one off-chip voltage domain to another and/or interfacing directly to off-chip peripherals operating at different supply levels.

- The switch matrix provides level shifter functionality to allow up to two selected signals to be routed from user-selected pins in one voltage domain to selected pins in the alternate domain. This feature can also be used on a single supply device if voltage level shifting is not required.

- ROM API support:

- Boot loader.

PC804

- Supports Flash In-Application Programming (IAP).

- Supports In-System Programming (ISP) through USART.

- On-chip ROM APIs for integer divide.

- Free Running Oscillator (FRO) API.

- Digital peripherals:

- High-speed GPIO interface connected to the Arm Cortex-M0+ I/O bus with up to 30 General-Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors, programmable open-drain mode, and input inverter. GPIO direction control supports independent set/clear/toggle of individual bits.

- High-current source output driver (20 mA) on five pins.

- GPIO interrupt generation capability with boolean pattern-matching feature on eight GPIO inputs.

- Switch matrix for flexible configuration of each I/O pin function.

- CRC engine.

- Capacitive Touch Interface.

- Programmable Logic Unit (PLU) to create small combinatorial and/or sequential logic networks including simple state machines.

- Timers:

- One 32-bit general purpose counter/timer, with four match outputs and three capture inputs. Supports PWM mode, and external count

- Four channel Multi-Rate Timer (MRT) for repetitive interrupt generation at up to four programmable, fixed rates.

- Self-Wake-up Timer (WKT) clocked from either Free Running Oscillator (FRO), a low-power, low-frequency internal oscillator, or an external clock input.

- Windowed Watchdog timer (WWDT).

- Analog peripherals:

- One 12-bit ADC with up to 12 input channels with multiple internal and external trigger inputs and with sample rates of up to 480 Ksamples/s. The ADC supports two independent conversion sequences.

- Comparator with five input pins and external or internal reference voltage.

- One 10-bit DAC.

- Serial peripherals:

- Two USART interfaces with pin functions assigned through the switch matrix and one fractional baud rate generators.

- One SPI controllers with pin functions assigned through the switch matrix.

- Two I<sup>2</sup>C-bus interface. It supports data rates up to 400 kbit/s on standard digital pins.

- Clock generation:

- Free Running Oscillator (FRO). This oscillator provides a selectable 9 MHz, 12 MHz and 15 MHz outputs that can be used as a system clock. The FRO is trimmed to ±1 % accuracy over the entire voltage and temperature range of 0 C to 70 C.

- 1 MHz low power oscillator can be used as a clock source.

- Clock output function with divider that can reflect all internal clock sources.

- Power control:

- Reduced power modes: sleep mode, deep-sleep mode, power-down mode, and deep power-down mode.

- Wake-up from deep-sleep and power-down modes on activity on USART, SPI, and I<sup>2</sup>C peripherals.

- Wake-up from deep power-down mode on multiple pins.

- ◆ Timer-controlled self wake-up from sleep, deep-sleep, and power-down modes.

- Power-On Reset (POR).

- Brownout detect (BOD).

- Unique device serial number for identification.

- Single power supply (1.71 V to 3.6 V).

- Operating temperature range -40 °C to +105 °C.

- Available in WLCSP20, TSSOP20, TSSOP24, and HVQFN33 packages.

## 3. Applications

- Sensor gateways

- Industrial

- Gaming controllers

- 8/16-bit applications

- Consumer

- Climate control

- Simple motor control

- Portables and wearables

- Lighting

- Motor control

- Fire and security applications

| 4. Ordering information | Or | dering | information |

|-------------------------|----|--------|-------------|

|-------------------------|----|--------|-------------|

#### Table 1.Ordering information

| Type number     | Package | Package                                                                                                                 |           |  |  |  |  |  |  |  |  |

|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|--|

|                 | Name    | Description                                                                                                             | Version   |  |  |  |  |  |  |  |  |

| LPC804M101JDH20 | TSSOP20 | plastic thin shrink small outline package; 20 leads; body width 4.4 mm                                                  | SOT360-1  |  |  |  |  |  |  |  |  |

| LPC804M101JDH24 | TSSOP24 | plastic thin shrink small outline package; 24 leads; body width 4.4 mm                                                  | SOT355-1  |  |  |  |  |  |  |  |  |

| LPC804M111JDH24 | TSSOP24 | plastic thin shrink small outline package; 24 leads; body width 4.4 mm                                                  | SOT355-1  |  |  |  |  |  |  |  |  |

| LPC804M101JHI33 | HVQFN33 | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 5 $\times$ 5 $\times$ 0.85 mm | SOT617-11 |  |  |  |  |  |  |  |  |

| LPC804UK        | WLCSP20 | wafer level chip-size package; 20 (5 $\times$ 4) bumps; 2.50 $\times 1.84 \times 0.5$ mm                                | SOT1397-8 |  |  |  |  |  |  |  |  |

### 4.1 Ordering options

#### Table 2. Ordering options

| Type number     | Flash/KB | SRAM/KB | USART | <sup>12</sup> C | SPI | DAC | Capacitive Touch | PLU | GPIO | Dual I/O power supply | Package |

|-----------------|----------|---------|-------|-----------------|-----|-----|------------------|-----|------|-----------------------|---------|

| LPC804M101JDH20 | 32       | 4       | 2     | 2               | 1   | -   | yes              | yes | 17   | -                     | TSSOP20 |

| LPC804M101JDH24 | 32       | 4       | 2     | 2               | 1   | 1   | yes              | yes | 21   | -                     | TSSOP24 |

| LPC804M111JDH24 | 32       | 4       | 2     | 2               | 1   | 1   | yes              | yes | 20   | yes                   | TSSOP24 |

| LPC804M101JHI33 | 32       | 4       | 2     | 2               | 1   | 1   | yes              | yes | 30   | -                     | HVQFN33 |

| LPC804UK        | 32       | 4       | 2     | 2               | 1   | -   | yes              | yes | 17   | -                     | WLCSP20 |

PC804

## 5. Marking

Fig 1. TSSOP20 and TSSOP24 package markings

Fig 2. HVQFN33 package marking

The LPC804 HVQFN33 packages have the following top-side marking::

- First line: LPC804M1

- Second line: xxxx

- Third line: yywwx[R]

- yyww: Date code with yy = year and ww = week.

- xR = Boot code version and device revision.

The LPC804 TSSOP20 packages typically have the following top-side marking:

- First line: LPC804

- Second line: M101

- Third line: xxxx

- Fourth line: xxywwx[R]

- yww: Date code with y = year and ww = week.

- xR = Boot code version and device revision.

The LPC804 TSSOP24 packages have the following top-side marking:

- First line: LPC804

- Second line: xxxx

- Third line: ywwx[R]

- yww: Date code with y = year and ww = week.

- xR = Boot code version and device revision.

- Fourth line: M1y1J

- y: 0 or 1

The LPC804 WLCSP20 packages have the following top-side marking:

- First line: LPC804

- Second line: xxxxx

- Third line: xyywwx[R]

- yyww: Date code with ww = week and yy = year.

- xR = Boot code version and device revision.

- Fourth line: xxx yyy

#### Table 3.Device revision table

| Revision identifier (R) | Revision description                               |

|-------------------------|----------------------------------------------------|

| 1A                      | Initial device revision with Boot ROM version 13.1 |

| 1B                      | Initial device revision with Boot ROM version 13.1 |

**Product data sheet**

## 6. Block diagram

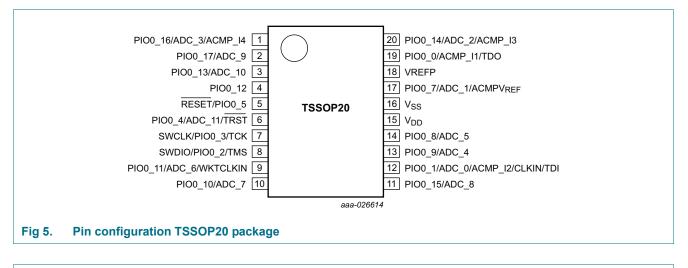

## 7. Pinning information

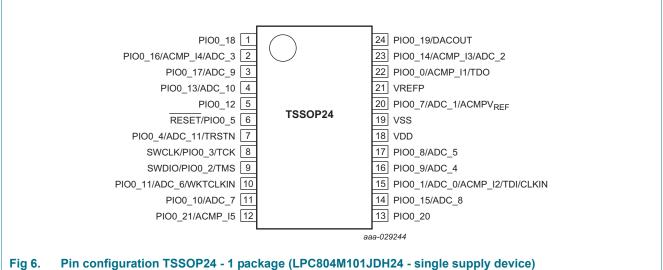

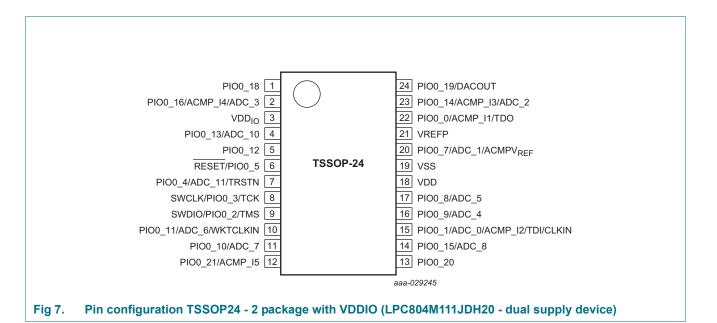

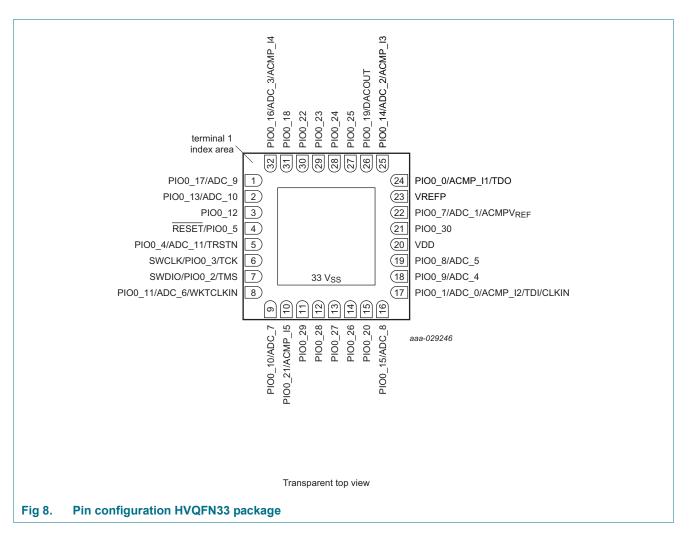

### 7.1 Pinning

**Product data sheet**

#### 7.2 Pin description

<u>Table 4</u> shows the pin functions that are fixed to specific pins on each package. These fixed-pin functions are selectable through the switch matrix between GPIO and the comparator, ADC, SWD, and RESET pins. By default, the GPIO function is selected except on pins PIO0\_2, PIO0\_3, and PIO0\_5. JTAG functions are available in boundary scan mode only.

Movable functions for the I2C, USART, SPI, CTimer pins, Capacitive Touch, and other peripherals can be assigned through the switch matrix to any pin that is not power or ground in place of the pin's fixed functions.

The following exceptions apply:

Do not assign more than one output to any pin. However, an output and/or one or more inputs can be assigned to a pin. Once any function is assigned to a pin, the pin's GPIO functionality is disabled.

Eight GPIO pins trigger a wake-up from deep power-down mode. If the part must wake up from deep power-down mode via an external pin, do not assign any movable function to this pin. The GPIO pins should be pulled HIGH externally before entering deep power-down mode. A LOW-going pulse as short as 50 ns causes the chip to exit deep power-down mode and wakes up the part.

The JTAG functions TDO, TDI, TCK, TMS, and TRST are selected on pins PIO0\_0 to PIO0\_4 by hardware when the part is in boundary scan mode.

PIO0\_2, PIO0\_3, PIO0\_12, PIO0\_18, and PIO0\_20 are the high drive output pins. <u>PIO0\_4</u>, PIO0\_8, PIO0\_9, PIO0\_10, PIO0\_11, PIO0\_13, PIO0\_15, and PIO0\_17 are the WAKEUP pins.

#### Table 4. Pin description

| Symbol                             | TSSOP24-1 | TSSOP24-2 | TSSOP20 | HVQFN33 | WLCSP20 |            | Reset<br>state <u>[1]</u> | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|-----------|-----------|---------|---------|---------|------------|---------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0/ACMP_I1/TDO                 | 22        | 22        | 19      | 24      | D3      | [2]        | I; PU                     | 10      | <b>PIO0_0</b> — General-purpose port 0<br>input/output 0.<br>In ISP mode, this is the U0_RXD pin (for<br>single supply devices).<br>In boundary scan mode: TDO (Test Data<br>Out).                                                                                                                                                                                                       |

| PIO0_1/ADC_0/ACMP_I2/<br>TDI/CLKIN | 15        | 15        | 12      | 17      | A4      | [2]        | I; PU                     | A<br>IO | <ul> <li>ACMP_I1 — Analog comparator input 1.</li> <li>PIO0_1 — General-purpose port 0 input/output 1.</li> <li>In boundary scan mode: TDI (Test Data In).</li> </ul>                                                                                                                                                                                                                    |

|                                    |           |           |         |         |         |            |                           | A<br>I  | ACMP_I2 — Analog comparator input 2.                                                                                                                                                                                                                                                                                                                                                     |

| SWDIO/PIO0_2/<br>TMS               | 9         | 9         | 8       | 7       | B2      | [3]        | I; PU                     | IO      | CLKIN — External clock input.<br>SWDIO — Serial Wire Debug I/O. SWDIO<br>is enabled by default on this pin. In<br>boundary scan mode: TMS (Test Mode<br>Select).                                                                                                                                                                                                                         |

|                                    |           |           |         |         |         |            |                           | I/O     | <b>PIO0_2</b> — General-purpose port 0 input/output 2.                                                                                                                                                                                                                                                                                                                                   |

| SWCLK/PIO0_3/<br>TCK               |           |           | 7       | 6       | B1      | <u>[3]</u> | I; PU                     | I       | <b>SWCLK</b> — Serial Wire Clock. SWCLK is<br>enabled by default on this pin.<br>In boundary scan mode: TCK (Test Clock).                                                                                                                                                                                                                                                                |

|                                    |           |           |         |         |         |            |                           | Ю       | <b>PIO0_3</b> — General-purpose port 0 input/output 3.                                                                                                                                                                                                                                                                                                                                   |

| PIO0_4/ADC_11/<br>TRSTN            | 7         | 7         | 6       | 5       | C2      | [2]        | I; PU                     | Ю       | <b>PIO0_4</b> — General-purpose port 0<br>input/output 4.<br>In ISP mode, this pin is the U0_TXD pin (for<br>single supply devices).<br>In boundary scan mode: TRST (Test<br>Reset).                                                                                                                                                                                                     |

|                                    |           |           |         |         |         |            |                           | A       | ADC_11 — ADC input 11.                                                                                                                                                                                                                                                                                                                                                                   |

| RESET/PIO0_5                       | 6         | 6         | 5       | 4       | C1      | [5]        | I; PU                     | IO      | <b>RESET</b> — External reset input: A<br>LOW-going pulse as short as 50 ns on this<br>pin resets the device, causing I/O ports and<br>peripherals to take on their default states,<br>and processor execution to begin at<br>address 0.<br>The RESET pin can be left unconnected or<br>be used as a GPIO or for any movable<br>function if an external RESET function is<br>not needed. |

|                                    |           |           |         |         |         |            |                           | I       | <b>PIO0_5</b> — General-purpose port 0 input/output 5.                                                                                                                                                                                                                                                                                                                                   |

#### Table 4. Pin description

| Symbol                                | TSSOP24-1 | TSSOP24-2 | TSSOP20 | HVQFN33                                                  | WLCSP20 |            | Reset<br>state <sup>[1]</sup> | Туре | Description                                                                                                                                                                                                                                                                                    |

|---------------------------------------|-----------|-----------|---------|----------------------------------------------------------|---------|------------|-------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_7/ADC_1/<br>ACMPV <sub>REF</sub> | 20        | 20        | 17      | 22                                                       | D4      | [2]        | I; PU                         | Ю    | <b>PIO0_7</b> — General-purpose port 0 input/output 7.                                                                                                                                                                                                                                         |

|                                       |           |           |         |                                                          |         |            |                               | А    | ADC_1 — ADC input 1.                                                                                                                                                                                                                                                                           |

|                                       |           |           |         |                                                          |         |            |                               |      | <b>ACMPV<sub>REF</sub></b> — Alternate reference voltage for the analog comparator.                                                                                                                                                                                                            |

| PIO0_8/ADC_5                          | 17        | 17        | 14      | 19                                                       | C3      | [2]        | I; PU                         | Ю    | <b>PIO0_8</b> — General-purpose port 0<br>input/output 8. In ISP mode, this is the<br>U0_RXD pin (for dual supply devices).                                                                                                                                                                    |

|                                       |           |           |         |                                                          |         |            |                               | А    | ADC_5 — ADC input 5.                                                                                                                                                                                                                                                                           |

| PIO0_9/ADC_4                          | 16        | 16        | 13      | 18                                                       | В3      | [2]        | I; PU                         | Ю    | <b>PIO0_9</b> — General-purpose port 0<br>input/output 9. In ISP mode, this is the<br>U0_TXD pin (for dual supply devices).                                                                                                                                                                    |

|                                       |           |           |         |                                                          |         |            |                               | А    | ADC_4 — ADC input 4.                                                                                                                                                                                                                                                                           |

| PIO0_10/ADC_7                         | 11        | 11        | 10      | 9                                                        | A2      | [2]        | Inactive                      | l; F | <b>PIO0_10</b> — General-purpose port 0 input/output 10.                                                                                                                                                                                                                                       |

|                                       |           |           |         |                                                          |         |            |                               |      | ADC_7 — ADC input 7.                                                                                                                                                                                                                                                                           |

| PIO0_11/ADC_6/<br>WKTCLKIN            |           |           | l; F    | <b>PIO0_11</b> — General-purpose port 0 input/output 11. |         |            |                               |      |                                                                                                                                                                                                                                                                                                |

|                                       |           |           |         |                                                          |         |            |                               |      | ADC_6 — ADC input 6.                                                                                                                                                                                                                                                                           |

|                                       |           |           |         |                                                          |         |            |                               |      | WKTCKLKIN — This pin can host an<br>external clock for the self-wake-up timer. To<br>use the pin as a self-wake-up timer clock<br>input, select the external clock in the<br>wake-up timer CTRL register. The external<br>clock input is active in sleep, deep-sleep,<br>and power-down modes. |

| PIO0_12                               | 5         | 5         | 4       | 3                                                        | D1      | <u>[3]</u> | I; PU                         | Ю    | <b>PIO0_12</b> — General-purpose port 0<br>input/output 12. ISP entry pin. A LOW level<br>on this pin during reset starts the ISP<br>command handler.                                                                                                                                          |

| PIO0_13/ADC_10                        | 4         | 4         | 3       | 2                                                        | D2      | <u>[2]</u> | I; PU                         | IO   | <b>PIO0_13</b> — General-purpose port 0 input/output 13.                                                                                                                                                                                                                                       |

|                                       |           |           |         |                                                          |         |            |                               | A    | ADC_10 — ADC input 10.                                                                                                                                                                                                                                                                         |

| PIO0_14/ACMP_3/<br>ADC_2              | 23        | 23        | 20      | 25                                                       | E3      | [2]        | I; PU                         | Ю    | <b>PIO0_14</b> — General-purpose port 0 input/output 14.                                                                                                                                                                                                                                       |

|                                       |           |           |         |                                                          |         |            |                               | A    | <b>ACMP_I3</b> — Analog comparator common input 3.                                                                                                                                                                                                                                             |

|                                       |           |           |         |                                                          |         |            |                               | A    | ADC_2 — ADC input 2.                                                                                                                                                                                                                                                                           |

| PIO0_15/ADC_8                         | 14        | 14        | 11      | 16                                                       | A3      | <u>[4]</u> | I; PU                         | IO   | <b>PIO0_15</b> — General-purpose port 0 input/output 15.                                                                                                                                                                                                                                       |

|                                       |           |           |         |                                                          |         |            |                               |      | ADC_8 — ADC input 8.                                                                                                                                                                                                                                                                           |

**LPC804**

#### Table 4. Pin description

| Symbol                    | TSSOP24-1 | TSSOP24-2 | TSSOP20 | HVQFN33 | WLCSP20 |              | Reset<br>state <sup>[1]</sup> | Туре | Description                                                                              |

|---------------------------|-----------|-----------|---------|---------|---------|--------------|-------------------------------|------|------------------------------------------------------------------------------------------|

| PIO0_16/ACMP_I4/<br>ADC_3 | 2         | 2         | 1       | 32      | E2      | [3]          | I; PU                         | Ю    | <b>PIO0_16</b> — General-purpose port 0 input/output 16.                                 |

|                           |           |           |         |         |         |              |                               |      | <b>ACMP_I4</b> — Analog comparator common input 4.                                       |

|                           |           |           |         |         |         |              |                               |      | ADC_3 — ADC input 3.                                                                     |

| PIO0_17/ADC_9             | 3         | -         | 2       | 1       | E1      | [2]          | I; PU                         | Ю    | <b>PIO0_17</b> — General-purpose port 0 input/output 17.                                 |

|                           |           |           |         |         |         |              |                               | А    | ADC_9 — ADC input 9.                                                                     |

| PIO0_18                   | 1         | 1         | -       | 31      | -       | [3]          | I; PU                         | Ю    | <b>PIO0_18</b> — General-purpose port 0 input/output 18.                                 |

| PIO0_19/DACOUT            | 24        | 24        | -       | 26      | -       | [2]          | I; PU                         | Ю    | <b>PIO0_19</b> — General-purpose port 0 input/output 19.                                 |

|                           |           |           |         |         |         |              |                               | А    | DACOUT — DAC output.                                                                     |

| PIO0_20                   | 13        | 13        | -       | 15      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_20</b> — General-purpose port 0 input/output 20.                                 |

| PIO0_21/ACMP_I5           | 12        | 12        | -       | 10      | -       | [3] I; PU IC |                               | Ю    | <b>PIO0_21</b> — General-purpose port 0 input/output 21.                                 |

|                           |           |           |         |         |         |              |                               |      | <b>ACMP_15</b> — Analog comparator common input 5.                                       |

| PIO0_22                   | -         | -         | -       | 30      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_22</b> — General-purpose port 0 input/output 22.                                 |

| PIO0_23                   | -         | -         | -       | 29      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_23</b> — General-purpose port 0 input/output 23.                                 |

| PIO0_24                   | -         | -         | -       | 28      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_24</b> — General-purpose port 0 input/output 24.                                 |

| PIO0_25                   | -         | -         | -       | 27      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_25</b> — General-purpose port 0 input/output 25.                                 |

| PIO0_26                   | -         | -         | -       | 14      | -       | [3]          | I; PU                         | Ю    | <b>PIO0_26</b> — General-purpose port 0 input/output 26.                                 |

| PIO0_27                   | -         | -         | -       | 13      | -       | [3]          | I; PU                         | Ю    | <b>PIO0_27</b> — General-purpose port 0 input/output 27.                                 |

| PIO0_28                   | -         | -         | -       | 12      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_28</b> — General-purpose port 0 input/output 28.                                 |

| PIO0_29                   | -         | -         | -       | 11      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_29</b> — General-purpose port 0 input/output 29.                                 |

| PIO0_30                   | -         | -         | -       | 21      | -       | <u>[3]</u>   | I; PU                         | Ю    | <b>PIO0_30</b> — General-purpose port 0 input/output 30.                                 |

| VREFP                     | 21        | 21        | 18      | 23      | E4      |              |                               | A    | <b>VREFP</b> — ADC positive reference voltage.<br>Must be equal or lower than $V_{DD}$ . |

| Symbol            | TSSOP24-1 | TSSOP24-2 | TSSOP20 | HVQFN33           | WLCSP20 | Reset<br>state <sup>[1]</sup> | Туре | Description                                                                                                                                                                                                                                 |

|-------------------|-----------|-----------|---------|-------------------|---------|-------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>   | 18        | 18        | 15      | 20                | B4      | -                             | -    | If VDDIO is present, VDD is the supply<br>voltage for the I/Os on the right side of the<br>package and the core voltage regulator. If<br>VDDIO is not present, VDD also supplies<br>voltage to the I/Os on the left side of the<br>package. |

| VDD <sub>IO</sub> | -         | 3         | -       | -                 | -       | -                             | -    | If present, it is the supply voltage for the I/Os on the left side of the package.                                                                                                                                                          |

| V <sub>SS</sub>   | 19        |           | 16      | 33 <mark>8</mark> | C4      | -                             | -    | Ground.                                                                                                                                                                                                                                     |

#### Table 4.Pin description

[1] Pin state at reset for default function: I = Input; AI = Analog Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level); IA = inactive, no pull-up/down enabled; F = floating. For pin states in the different power modes, see Section 15.5 "Pin states in different power modes". For termination on unused pins, see Section 15.4 "Termination of unused pins".

[2] 5 V tolerant pin providing standard digital I/O functions with configurable modes, configurable hysteresis, and analog input. When configured as an analog input, the digital section of the pin is disabled, and the pin is not 5 V tolerant.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis; includes high-current output driver.

[4] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis.

[5] See Figure 16 for the reset pad configuration. This pin includes a 20 ns glitch filter (active in all power modes). RESET functionality is not available in deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from deep power-down mode.

[6] The WKTCLKIN function is enabled in the PINENABLE0 register in the PMU. See the LPC804 user manual.

[7] The digital part of this pin is 3 V tolerant pin due to special analog functionality. Pin provides standard digital I/O functions with configurable modes, configurable hysteresis, and an analog input. When configured as an analog input, the digital section of the pin is disabled.

[8] Thermal pad for HVQFN33.

## 8. Movable functions

Movable functions for the I2C, USART, SPI, CTimer pins, Capacitive Touch, and other peripherals can be assigned through the switch matrix to any pin that is not power or ground in place of the fixed functions of the pin.

## Table 5. Movable functions (assign to pins PIO0\_0 to PIO0\_5, PIO0\_7 to PIO0\_30 through switch matrix)

| switch        |      | <b>*)</b>                                                           |

|---------------|------|---------------------------------------------------------------------|

| Function name | Туре | Description                                                         |

| Ux_TXD        | 0    | Transmitter output for USART0 to USART1.                            |

| Ux_RXD        | I    | Receiver input for USART0 to USART1.                                |

| Ux_RTS        | 0    | Request To Send output for USART0.                                  |

| Ux_CTS        | I    | Clear To Send input for USART0.                                     |

| Ux_SCLK       | I/O  | Serial clock input/output for USART0 to USART1 in synchronous mode. |

| SPIx_SCK      | I/O  | Serial clock for SPI0.                                              |

| SPIx_MOSI     | I/O  | Master Out Slave In for SPI0.                                       |

| SPIx_MISO     | I/O  | Master In Slave Out for SPI0.                                       |

| SPIx_SSEL0    | I/O  | Slave select 0 for SPI0.                                            |

| SPIx_SSEL1    | I/O  | Slave select 1 for SPI0.                                            |

| I2Cx_SDA      | I/O  | I <sup>2</sup> C0 and I <sup>2</sup> C1 bus data input/output.      |

| I2Cx_SCL      | I/O  | I <sup>2</sup> C0 and I <sup>2</sup> C1 bus clock input/output.     |

| ACMP_O        | 0    | Analog comparator output.                                           |

| CLKOUT        | 0    | Clock output.                                                       |

| GPIO_INT_BMAT | 0    | Output of the pattern match engine.                                 |

| T0_MAT0       | 0    | Timer Match channel 0.                                              |

| T0_MAT1       | 0    | Timer Match channel 1.                                              |

| T0_MAT2       | 0    | Timer Match channel 2.                                              |

| T0_MAT3       | 0    | Timer Match channel 3.                                              |

| T0_CAP0       | I    | Timer Capture channel 0.                                            |

| T0_CAP1       | I    | Timer Capture channel 1.                                            |

| T0_CAP2       | I    | Timer Capture channel 2.                                            |

| CAPT_X0       | 0    | CAPT_X0 function.                                                   |

| CAPT_X1       | 0    | CAPT_X1 function.                                                   |

| CAPT_X2       | 0    | CAPT_X2 function.                                                   |

| CAPT_X3       | 0    | CAPT_X3 function.                                                   |

| CAPT_X4       | 0    | CAPT_X4 function.                                                   |

| CAPT_YL       | 0    | CAPT_YL function.                                                   |

| CAPT_YH       | 0    | CAPT_YH function.                                                   |

| LVLSHFT_IN0   | I    | Level shift input 0.                                                |

| LVLSHFT_IN1   | I    | Level shift input 1.                                                |

| LVLSHFT_OUT0  | 0    | Level shift output 0.                                               |

| LVLSHFT_OUT1  | 0    | Level shift output 1.                                               |

### 9. Functional description

#### 9.1 Arm Cortex-M0+ core

The Arm Cortex-M0+ core runs at an operating frequency of up to 15 MHz using a two-stage pipeline. The core revision is r0p1.

Integrated in the core are the NVIC and Serial Wire Debug with four breakpoints and two watchpoints. The Arm Cortex-M0+ core supports a single-cycle I/O enabled port for fast GPIO access.

The core includes a single-cycle multiplier and a system tick timer.

#### 9.2 On-chip flash program memory

The LPC804 contain up to 32 KB of on-chip EEPROM based flash program memory.

#### 9.3 On-chip SRAM

The LPC804 contain a total of 4 KB on-chip static RAM data memory.

#### 9.4 On-chip ROM

The on-chip ROM contains the bootloader:

- Boot loader.

- Supports Flash In-Application Programming (IAP).

- Supports In-System Programming (ISP) through USART.

- On-chip ROM APIs for integer divide.

- Free Running Oscillator (FRO) API.

#### 9.5 Memory map

The LPC804 incorporates several distinct memory regions. <u>Figure 9</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The Arm private peripheral bus includes the Arm core registers for controlling the NVIC, the system tick timer (SysTick), and the reduced power modes.

| Memory space               |                           |           | AHB perpherals    |             |

|----------------------------|---------------------------|-----------|-------------------|-------------|

| (reserved)                 | 0xFFFF FFFF               |           |                   |             |

| private peripheral bus     | 0xE010 0000               | ſ         | (reserved)        | 0x5001 4000 |

| (reserved)                 | 0xE000 0000               | ────┤┣─── | CRC engine        | 0x5000 4000 |

| GPIO interrupts            | 0xA000 8000               | ί 📖       | onto engine       | 0x5000 0000 |

| GPIO                       | 0xA000 4000               |           |                   |             |

| (reserved)                 | 0xA000 0000               |           |                   |             |

| AHB                        | 0x5001 4000               |           |                   |             |

| peripherals                | 0                         |           | APB perpherals    |             |

| (reserved)                 | 0x5000 0000               | 31-30     | (reserved)        | 0x4007 FFFF |

| АРВ                        | 0x4008 0000               | 29        | (reserved)        | 0x4007 8000 |

| peripherals                | •                         | 28        | (reserved)        | 0x4007 4000 |

|                            | 0x4000 0000               | 27        | (reserved)        | 0x4007 0000 |

| (reserved)                 |                           | 26        | USART1            | 0x4006 C000 |

| RAM                        | 0x1000 1000               | 25        | USART0            | 0x4006 8000 |

| (reserved)                 | 0x1000 0000               | 24        | CAPTouch          | 0x4006 4000 |

| Boot ROM                   | 0x0F00 2000               | 23        | (reserved)        | 0x4006 0000 |

| (reserved)                 | 0x0F00 0000               | 22        | SPI               | 0x4005 C000 |

| Flash memory               | 0x0000 8000               | 21        | I2C1              | 0x4005 8000 |

| (up to 32 KB)              |                           | 20        | I2C0              | 0x4005 4000 |

| 1                          | → 0x0000 0000             | 19        | (reserved)        | 0x4005 0000 |

|                            |                           | 18        | Syscon            | 0x4004 C000 |

| active in                  | terrupt vectors 0x0000 00 | 17        | IOCON             | 0x4004 8000 |

|                            | 0x0000 00                 | 16        | (reserved)        | 0x4004 4000 |

|                            |                           | 15        | (reserved)        | 0x4004 0000 |

|                            |                           | 14        | CTIMER 0          | 0x4003 C000 |

|                            |                           | 13        | (reserved)        | 0x4003 8000 |

|                            |                           | 12        | (reserved)        | 0x4003 4000 |

|                            |                           | 11        | (reserved)        | 0x4003 0000 |

|                            |                           | 10        | PLU               | 0x4002 C000 |

|                            |                           | 9         | Analog Comparator | 0x4002 8000 |

|                            |                           | 8         | PMU               | 0x4002 4000 |

|                            |                           | 7         | ADC               | 0x4002 0000 |

|                            |                           | 6         | (reserved)        | 0x4001 C000 |

|                            |                           | 5         | DAC0              | 0x4001 8000 |

|                            |                           | 4         | (reserved)        | 0x4001 4000 |

|                            |                           | 3         | Switch Matrix     | 0x4001 0000 |

|                            |                           | 2         | Wake-up Timer     | 0x4000 C000 |

|                            |                           |           | Multi-Rate Timer  | 0x4000 8000 |

|                            |                           | 0         | Watchdog timer    | 0x4000 4000 |

|                            |                           |           |                   | 0x4000 0000 |

|                            |                           |           |                   | aaa-029247  |

| Fig 9. LPC804 Memory mappi | na                        |           |                   |             |

|                            |                           |           |                   |             |

### 9.6 Nested Vectored Interrupt Controller (NVIC)

The Nested Vectored Interrupt Controller (NVIC) is part of the Cortex-M0+. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

#### 9.6.1 Features

- Nested Vectored Interrupt Controller is a part of the Arm Cortex-M0+.

- Tightly coupled interrupt controller provides low interrupt latency.

- Controls system exceptions and peripheral interrupts.

- Supports 32 vectored interrupts.

- In the LPC804, the NVIC supports vectored interrupts for each of the peripherals and the eight pin interrupts.

- Four programmable interrupt priority levels with hardware priority level masking.

- Software interrupt generation using the Arm exceptions SVCall and PendSV.

- Supports NMI.

#### 9.6.2 Interrupt sources

Each peripheral device has at least one interrupt line connected to the NVIC but can have several interrupt flags. Individual interrupt flags can also represent more than one interrupt source.

#### 9.7 System tick timer

The Arm Cortex-M0+ includes a 24-bit system tick timer (SysTick) that is intended to generate a dedicated SysTick exception at a fixed time interval (typically 10 ms).

#### 9.8 I/O configuration

The IOCON block controls the configuration of the I/O pins. Each digital or mixed digital/analog pin with the PIO0\_n designator in Table 4 can be configured as follows:

- Enable or disable the weak internal pull-up and pull-down resistors.

- Select a pseudo open-drain mode. The input cannot be pulled up above V<sub>DD</sub>. The pins are not 5 V tolerant when V<sub>DD</sub> is grounded.

- Program the input glitch filter with different filter constants using one of the IOCON divided clock signals (IOCONCLKCDIV, see <u>Figure 12 "LPC804 clock generation</u>"). You can also bypass the glitch filter.

- Invert the input signal.

- Hysteresis can be enabled or disabled.

- The switch matrix setting enables the analog input mode on pins with analog and digital functions. Enabling the analog mode disconnects the digital functionality.

- The LPC804 uses a dual voltage I/O feature. The pins on one side of the package are supplied by VDDIO and the pins on the other side are supplied by VDD. Each of these two supplies can be connected to different voltages within the allowed Vdd range. This feature allows the device to level-shift signals from one off-chip voltage domain to another.

PC804

• The switch matrix provides level shifter functionality to allow up to two selected signals to be routed from user-selected pins in one voltage domain to selected pins in the alternate domain. This feature can also be used on a single supply device if voltage level shifting is not required.

**Remark:** The functionality of each I/O pin is flexible and is determined entirely through the switch matrix. See Section 9.9 for details.

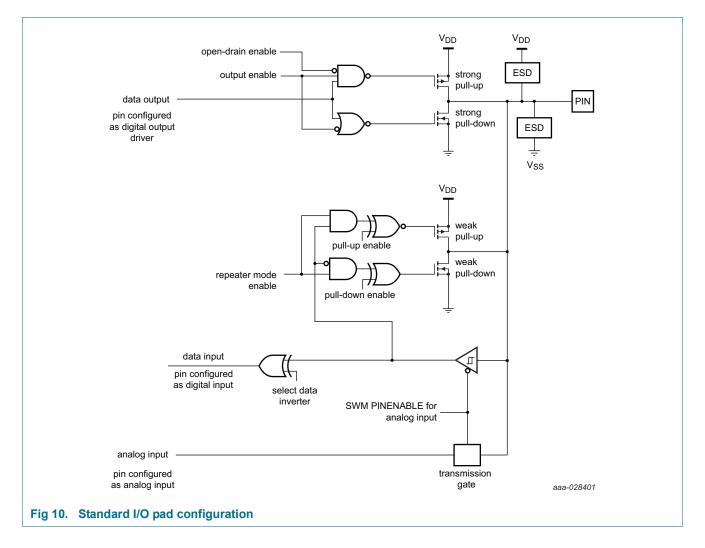

#### 9.8.1 Standard I/O pad configuration

Figure 10 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver with configurable open-drain output.

- Digital input: Weak pull-up resistor (PMOS device) enabled/disabled.

- Digital input: Weak pull-down resistor (NMOS device) enabled/disabled.

- Digital input: Repeater mode enabled/disabled.

- Digital input: Programmable input digital filter selectable on all pins.

- · Analog input: Selected through the switch matrix.

#### 9.9 Switch Matrix (SWM)

The switch matrix controls the function of each digital or mixed analog/digital pin in a highly flexible way by allowing to connect many functions like the USART, SPI, CTimer, Capacitive Touch, and I2C functions to any pin that is not power or ground. These functions are called movable functions and are listed in Table 5.

Functions that need specialized pads can be enabled or disabled through the switch matrix. These functions are called fixed-pin functions and cannot move to other pins. The fixed-pin functions are listed in <u>Section 7.2 "Pin description"</u>. If a fixed-pin function is disabled, any other movable function can be assigned to this pin.

#### 9.10 Fast General-Purpose parallel I/O (GPIO)

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Multiple outputs can be set or cleared in one write operation.

LPC804 use accelerated GPIO functions:

- GPIO registers are on the Arm Cortex-M0+ IO bus for fastest possible single-cycle I/O timing, allowing GPIO toggling with rates of up to 7 MHz.

- An entire port value can be written in one instruction.

- Mask, set, and clear operations are supported for the entire port.

All GPIO port pins are fixed-pin functions that are enabled or disabled on the pins by the switch matrix. Therefore each GPIO port pin is assigned to one specific pin and cannot be moved to another pin. Except for pins SWDIO/PIO0\_2, SWCLK/PIO0\_3, and RESET/PIO0\_5, the switch matrix enables the GPIO port pin function by default.

#### 9.10.1 Features

- Bit level port registers allow a single instruction to set and clear any number of bits in one write operation.

- Direction control of individual bits.

- All I/O default to GPIO inputs with internal pull-up resistors enabled after reset.

- Pull-up/pull-down configuration, repeater, and open-drain modes can be programmed through the IOCON block for each GPIO pin (see Figure 10).

- Direction (input/output) can be set and cleared individually.

- Pin direction bits can be toggled.

#### 9.11 Pin interrupt

The pin interrupt block configures up to eight pins from all digital pins for providing eight external interrupts connected to the NVIC.

Any digital pin, independently of the function selected through the switch matrix, can be configured through the SYSCON block as input to the pin interrupt. The registers that control the pin interrupt are on the IO+ bus for fast single-cycle access.

#### 9.11.1 Features

- Pin interrupts

- Up to eight pins can be selected from all digital pins as edge- or level-sensitive interrupt requests. Each request creates a separate interrupt in the NVIC.

- Edge-sensitive interrupt pins can interrupt on rising or falling edges or both.

- Level-sensitive interrupt pins can be HIGH- or LOW-active.

- Pin interrupts can wake up the LPC804 from sleep mode, deep-sleep mode, and power-down mode.

#### 9.12 USART0/1

All USART functions are movable functions and are assigned to pins through the switch matrix.

#### 9.12.1 Features

- Maximum bit rates of 1.875 Mbit/s in asynchronous mode and 10 Mbit/s in synchronous mode for USART functions connected to all digital pins.

- 7, 8, or 9 data bits and 1 or 2 stop bits

- Synchronous mode with master or slave operation. Includes data phase selection and continuous clock option.

- Multiprocessor/multidrop (9-bit) mode with software address compare. (RS-485 possible with software address detection and transceiver direction control.)

- Parity generation and checking: odd, even, or none.

- One transmit and one receive data buffer.

- RTS/CTS for hardware signaling for automatic flow control. Software flow control can be performed using Delta CTS detect, Transmit Disable control, and any GPIO as an RTS output.

- Received data and status can optionally be read from a single register

- Break generation and detection.

- Receive data is 2 of 3 sample "voting". Status flag set when one sample differs.

- Built-in Baud Rate Generator.

- A fractional rate divider is shared among all UARTs.

- Interrupts available for Receiver Ready, Transmitter Ready, Receiver Idle, change in receiver break detect, Framing error, Parity error, Overrun, Underrun, Delta CTS detect, and receiver sample noise detected.

- · Separate data and flow control loopback modes for testing.

- Baud rate clock can also be output in asynchronous mode.

#### 9.13 SPI0

All SPI functions are movable functions and are assigned to pins through the switch matrix.

PC804

#### 9.13.1 Features

- Maximum data rates of up to 15 Mbit/s in master mode and up to 20 Mbit/s in slave mode for SPI functions connected to all digital pins.

- Data frames of 1 to 16 bits supported directly. Larger frames supported by software.

- Master and slave operation.

- Data can be transmitted to a slave without the need to read incoming data, which can be useful while setting up an SPI memory.

- Control information can optionally be written along with data, which allows very versatile operation, including "any length" frames.

- One Slave Select input/output with selectable polarity and flexible usage.

Remark: Texas Instruments SSI and National Microwire modes are not supported.

#### 9.14 I<sup>2</sup>C-bus interface (I<sup>2</sup>C0 and I<sup>2</sup>C1)

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a serial clock line (SCL) and a serial data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master.

#### 9.14.1 Features

- I<sup>2</sup>C0 and I<sup>2</sup>C1 support standard and fast mode with data rates of up to 400 kbit/s.

- Independent Master, Slave, and Monitor functions.

- Supports both Multi-master and Multi-master with Slave functions.

- Multiple I<sup>2</sup>C slave addresses supported in hardware.

- One slave address can be selectively qualified with a bit mask or an address range in order to respond to multiple I<sup>2</sup>C bus addresses.

- 10-bit addressing supported with software assist.

- Supports SMBus.

#### 9.15 Capacitive Touch Interface

The Capacitive Touch interface is designed to handle up to five capacitive buttons in different sensor configurations, such as slider, and button matrix. It operates in sleep, deep sleep, and power-down modes, allowing very low power performance.

The Capacitive Touch module measures the change in capacitance of an electrode plate when an earth-ground connected object (for example, finger) is brought within close proximity.

#### 9.16 CTimer

#### 9.16.1 General-purpose 32-bit timers/external event counter

The LPC804 has one general-purpose 32-bit timer/counter.

**Product data sheet**

The timer/counter is designed to count cycles of the system derived clock or an externally-supplied clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. The timer/counter also includes three capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

#### 9.16.1.1 Features

- A 32-bit timer/counter with a programmable 32-bit prescaler.

- Counter or timer operation.

- Up to three 32-bit captures can take a snapshot of the timer value when an input signal transitions. A capture event may also optionally generate an interrupt. The number of capture inputs for each timer that are actually available on device pins can vary by device.

- Four 32-bit match registers that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Shadow registers are added for glitch-free PWM output.

- For each timer, up to 4 external outputs corresponding to match registers with the following capabilities (the number of match outputs for each timer that are actually available on device pins can vary by device):

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- The timer and prescaler may be configured to be cleared on a designated capture event. This feature permits easy pulse width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

- Up to 4 match registers can be configured for PWM operation, allowing up to 3 single edged controlled PWM outputs. (The number of match outputs for each timer that are actually available on device pins can vary by device.)

#### 9.17 Multi-Rate Timer (MRT)

The Multi-Rate Timer (MRT) provides a repetitive interrupt timer with two channels. Each channel can be programmed with an independent time interval, and each channel operates independently from the other channels.

#### 9.17.1 Features

- 31-bit interrupt timer

- Two channels independently counting down from individually set values

- · Bus stall, repeat and one-shot interrupt modes

### 9.18 Windowed WatchDog Timer (WWDT)

The watchdog timer resets the controller if software fails to service the watchdog timer periodically within a programmable time window.

#### 9.18.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The WatchDog Clock (WDCLK) is generated by the dedicated watchdog oscillator (WDOSC).

#### 9.19 Self-Wake-up Timer (WKT)

The self-wake-up timer is a 32-bit, loadable down counter. Writing any non-zero value to this timer automatically enables the counter and launches a count-down sequence. When the counter is used as a wake-up timer, this write can occur prior to entering a reduced power mode.

#### 9.19.1 Features

- 32-bit loadable down counter. Counter starts automatically when a count value is loaded. Time-out generates an interrupt/wake up request.

- The WKT supports three clock sources: an external clock on the WKTCLKIN pin, the low-power oscillator, and the FRO. The low-power oscillator can be used as the clock source in sleep, deep-sleep, and power-down modes.

- The WKT can be used for waking up the part from any reduced power mode or for general-purpose timing.

#### 9.20 Programmable Logic Unit (PLU)

The PLU is comprised of 26 5-input LUT elements. Each LUT element contains a 32-bit truth table (look-up table) register and a 32:1 multiplexer. During operation, the five LUT inputs control the select lines of the multiplexer. This structure allows any desired logical combination of the five LUT inputs.

PC804

#### 9.20.1 Features

- The PLU is used to create small combinatorial and/or sequential logic networks including simple state machines.

- The PLU is comprised of an array of 26 inter-connectable, 5-input Look-up Table (LUT) elements, and four flip-flops.

- Eight primary outputs can be selected using a multiplexer from among all of the LUT outputs and the four flip-flops.

- An external clock to drive the four flip-flops must be applied to the PLU\_CLKIN pin if a sequential network is implemented.

- Programmable logic can be used to drive on-chip inputs/triggers through external pin-to-pin connections.

- A tool suite is provided to facilitate programming of the PLU to implement the logic network described in a Verilog RTL design.

**Remark:** PLU cannot be used to wake-up from sleep, deep-sleep, power-down, and deep power-down modes.

#### 9.21 Analog comparator (ACMP)

The analog comparator with selectable hysteresis can compare voltage levels on external pins and internal voltages.

After power-up and after switching the input channels of the comparator, the output of the voltage ladder must be allowed to settle to its stable value before it can be used as a comparator reference input. Settling times are given in Table 27.

The analog comparator output is a movable function and is assigned to a pin through the switch matrix. The comparator inputs and the voltage reference are enabled through the switch matrix.