# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **OMAP-L138 SOM-M1 Hardware Specification**

Hardware Documentation

Logic PD // Products Published: August 2009 Last revised: November 2010

This document contains valuable proprietary and confidential information and the attached file contains source code, ideas, and techniques that are owned by Logic Product Development Company (collectively "Logic PD's Proprietary Information"). Logic PD's Proprietary Information may not be used by or disclosed to any third party except under written license from Logic Product Development Company.

Logic Product Development Company makes no representation or warranties of any nature or kind regarding Logic PD's Proprietary Information or any products offered by Logic Product Development Company. Logic PD's Proprietary Information is disclosed herein pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipment. The only warranties made by Logic Product Development Company, if any, with respect to any products described in this document are set forth in such license or agreement. Logic Product Development Company shall have no liability of any kind, express or implied, arising out of the use of the Information in this document, including direct, indirect, special or consequential damages.

Logic Product Development Company may have patents, patent applications, trademarks, copyrights, trade secrets, or other intellectual property rights pertaining to Logic PD's Proprietary Information and products described in this document (collectively "Logic PD's Intellectual Property"). Except as expressly provided in any written license or agreement from Logic PD's Intellectual Property, this document and the information contained therein does not create any license to Logic PD's Intellectual Property.

The Information contained herein is subject to change without notice. Revisions may be issued regarding changes and/or additions.

© Copyright 2010, Logic Product Development Company. All Rights Reserved.

| REV | EDITOR   | REVISION DESCRIPTION                                                                                                                                                                                       | Schematic<br>PN & REV          | APPROVAL | DATE     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------|----------|

| 1   | RS & JCA | Internal release                                                                                                                                                                                           | —                              | —        | 07/24/09 |

| 2   | RS & JCA | Initial Beta release                                                                                                                                                                                       | 1013536 Rev 3<br>1013253 Rev 3 | JCA      | 08/21/09 |

| 3   | RS       | -Section 3.2: Added typical active current numbers to table                                                                                                                                                | 1013536 Rev 3<br>1013253 Rev 3 | RS       | 10/05/09 |

| 4   | JCA      | -Added Section 2.3.4 and referenced drawings in Appendix B<br>-Appendix A: corrected J2 and J3 connector locations on drawing                                                                              | 1013536 Rev 3<br>1013253 Rev 3 | JCA      | 11/03/09 |

| 5   | JCA      | -Section 2.3.1: Corrected height of SOM;<br>-Section 2.4: Added Industrial temperature range; Added Caution<br>about system temperatures when enabling SATA;<br>-Updated mechanical drawings in Appendices | 1014647 Rev A<br>1014576 Rev A | KTL      | 11/05/10 |

# **Revision History**

Please check <u>www.logicpd.com</u> for the latest revision of this document, product change notifications, and additional documentation.

# **Table of Contents**

| 1 |                | duction                                    |   |

|---|----------------|--------------------------------------------|---|

|   |                | roduct Overview                            |   |

|   | 1.2 A          | bbreviations, Acronyms, & Definitions      | 1 |

|   | 1.3 N          | lomenclature                               | 2 |

|   |                | cope of Document                           |   |

|   |                | dditional Documentation Resources          |   |

| 2 |                | tional Specification                       |   |

|   | 2.1 P          | rocessor                                   |   |

|   | 2.1.1          | OMAP-L138 Processor                        |   |

|   | 2.1.2          |                                            |   |

|   |                | OM Interface                               |   |

|   | 2.2.1          | OMAP-L138 SOM-M1 Block Diagram             |   |

|   |                | lechanical Specifications                  | 6 |

|   | 2.3.1          | Mechanical Characteristics of SOM          |   |

|   | 2.3.2          | Interface Connectors                       |   |

|   | 2.3.3          | OMAP-L138 SOM-M1 Mechanical Drawings       | 7 |

|   | 2.3.4          | Example OMAP-L138 SOM-M1 Retention Methods | 7 |

| ~ | 2.4 T          | emperature Specifications                  | 7 |

| 3 | Elect          | rical Specification                        | 8 |

|   |                | bsolute Power Maximum Ratings              |   |

|   | 3.2 R          | ecommended Power Operating Conditions      | 8 |

| 4 |                | heral Specification                        |   |

|   |                |                                            |   |

|   |                |                                            |   |

|   | 4.2.1<br>4.2.2 | Mobile DDR                                 |   |

|   |                |                                            |   |

|   |                | 0/100 Ethernet PHY                         |   |

|   |                | isplay Interface                           |   |

|   | 4.5 5          | UART0-21                                   |   |

|   | 4.5.1          | SPI0/1                                     |   |

|   | 4.5.2          | I2C0/1                                     |   |

|   | 4.5.4          | McBSP0/1                                   |   |

|   | 4.5.5          | McDSF 0/1                                  |   |

|   |                | ISB Interface                              |   |

|   |                | DC/Touch Interface                         |   |

|   |                | General Purpose I/O (GPIO)                 |   |

|   |                | xpansion/Feature Options                   |   |

| 5 |                | em Integration                             |   |

|   |                | ustom Čonfiguration1                       |   |

|   |                | lesets                                     |   |

|   | 5.2.1          | Master Reset (MSTR nRST)—Reset Input1      |   |

|   | 5.2.2          | SOM Reset (RESETOUTn)-Reset output1        |   |

|   | 5.3 In         | nterrupts                                  |   |

|   | 5.4 J          | TAG Debugger Interface                     | 4 |

|   | 5.5 P          | ower Management1                           |   |

|   | 5.5.1          | System Power Supplies1                     |   |

|   | 5.5.           |                                            |   |

|   | 5.5.           |                                            | 4 |

|   | 5.5.           |                                            |   |

|   | 5.5.           | -                                          |   |

|   | 5.5.2          | Dual Voltage I/O1                          | 5 |

|   | 5.5.3          | System Power Management1                   | 5 |

| 5.5.4 Microcontroller                                  |    |

|--------------------------------------------------------|----|

| 5.6 ESD Considerations                                 |    |

| 6 Memory & I/O Mapping                                 | 17 |

| 7 Pin Descriptions & Functions                         |    |

| 7.1 J1 Connector 100-Pin Descriptions                  |    |

| 7.2 J2 Connector 100-Pin Descriptions                  | 24 |

| 7.3 J3 Connector 100-Pin Descriptions                  |    |

| Appendix A: OMAP-L138 SOM-M1 Mechanical Drawing        |    |

| Appendix B: Example OMAP-L138 SOM-M1 Retention Methods |    |

# **Table of Figures**

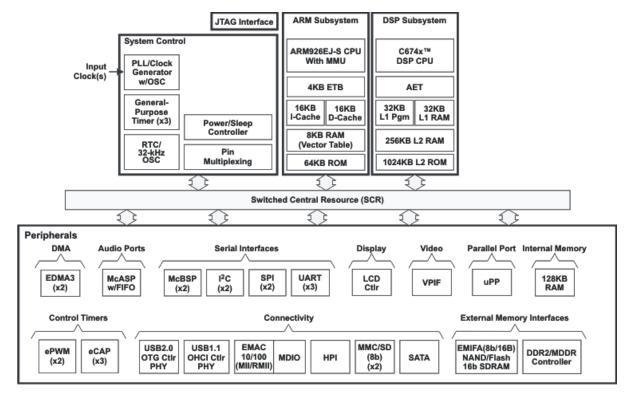

| Figure 2.1: OMAP-L138 Processor Block Diagram | 5 |

|-----------------------------------------------|---|

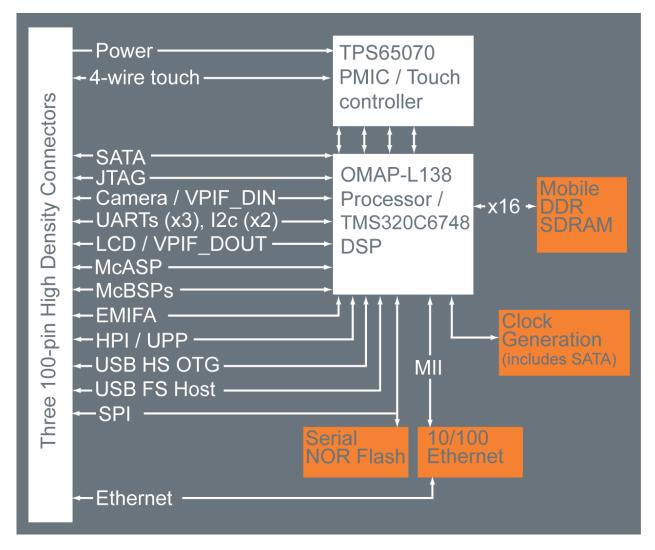

| Figure 2.2: OMAP-L138 SOM-M1 Block Diagram    | 6 |

### 1 Introduction

#### 1.1 **Product Overview**

The OMAP-L138 System on Module (SOM) is a compact, product-ready hardware and software solution that fast forwards embedded designs while reducing risk and controlling cost.

Based on Texas Instruments' OMAP-L138 processor and designed in the SOM-M1 form factor, the OMAP-L138 module offers essential features for handheld and embedded networking applications. The OMAP-L138 SOM-M1 features the superset OMAP-L138 processor, but also supports the TMS320C6748 digital signal processor (DSP).

The OMAP-L138 SOM-M1 brings the industry leading low power ARM926 core to a small, off-theshelf solution. The standard SOM-M1 form factor allows developers to reuse existing baseboard designs when upgrading to new OMAP processors, which extends roadmap possibilities for their end-product.

Two Zoom<sup>™</sup> Development Kit options allow developers to choose the platform best suited to their application needs. By starting with the corresponding Zoom Development Kit, engineers can write application software on the same hardware that will be used in their final product.

The compact size of the OMAP-L138 SOM-M1 is ideal for medical patient monitoring wearables and other portable instrumentation applications; the built-in Serial ATA (SATA) controller provides fast access to large capacity storage devices. For medical, industrial, audio, and communication products, the OMAP-L138 SOM-M1 allows for powerful versatility, long-life, and greener products.

#### 1.2 Abbreviations, Acronyms, & Definitions

| ADC<br>BOM<br>BSP<br>BTB<br>DAC<br>DMA<br>DSP<br>EDMA<br>EMIFA<br>ESD<br>FIFO<br>HPI<br>GPIO<br>GPMC<br>Hi-Z<br>I2C<br>I2S<br>IC<br>I/O<br>IRQ<br>LCD<br>LDO | Analog to Digital Converter<br>Bill of Materials<br>Board Support Package<br>Board-to-Board<br>Digital to Analog Converter<br>Direct Memory Access<br>Digital Signal Processor<br>Enhanced Direct Memory Access<br>External Memory Interface<br>Electrostatic Discharge<br>First In First Out<br>Host Port Interface<br>General Purpose Input Output<br>General Purpose Memory Controller<br>High Impedance<br>Inter-Integrated Circuit<br>Inter-Integrated Circuit<br>Inter-Integrated Circuit<br>Interrupt Request<br>Liquid Crystal Display<br>Low Dropout (Regulator) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| McASP<br>McBSP                                                                                                                                               | Multi-channel Audio Serial Port<br>Multi-channel Buffered Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| mDDR                                                                                                                                                         | Mobile Double Data Rate (RAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| mDDR                                                                                                                                                         | Mobile Double Data Rate (RAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| .=•                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| · ·· =                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BSP                                                                                                                                                          | Board Support Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BOM                                                                                                                                                          | Bill of Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADC                                                                                                                                                          | Analog to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### 1.3 Nomenclature

- The terms "SOM" and "SOM-M1" are used interchangeably throughout this document and can be assumed to mean the same thing within this text. The SOM-M1 is a specific form factor type of Logic's SOM.

- TMS320C6748, C6748, and C674x can be assumed to all represent the TMS320C6748 DSP core.

#### 1.4 Scope of Document

- This Hardware Specification is unique to the design and use of the OMAP-L138 SOM-M1 as designed by Logic and does not intend to include information outside of that scope. Detailed information about the Texas Instruments (TI) OMAP-L138 processor or any other device component on the SOM can be found in their respective manuals and specification documents; please see Section 1.5 for additional resources.

- This Hardware Specification applies to both the OMAP-L138 SOM-M1 and TMS320C6748 SOM-M1. The OMAP-L138 processor and TMS320C6758 DSP are identical, with the exception that the OMAP-L138 is a dual-core processor with an ARM9 core and a C674x core. Both processors—and therefore both SOMs—have the same peripheral set and the same pin functions.

#### 1.5 Additional Documentation Resources

The following documents or documentation resources are referenced within this Hardware Specification.

TI's OMAP-L138 Low-Power Applications Processor Datasheet, User Guides, Application Notes, White Papers, and Errata http://www.ti.com/omap-I138-prprod1

- TI's TPS65070 Datasheet http://focus.ti.com/docs/prod/folders/print/tps65070.html

- USB 2.0 Specification, available from USB.org <u>http://www.usb.org/developers/docs/</u>

- U-Boot documentation <u>http://www.denx.de/wiki/U-Boot/WebHome</u>

- Logic OMAP-L138 Baseboard BOM, Schematic, and Layout <u>http://support.logicpd.com/downloads/1216/</u>

- Logic OMAP-L138 SOM-M1 BOM, Schematic, and Layout (128 MB mDDR configuration included with the EVM Development Kit) <u>http://support.logicpd.com/downloads/1215/</u>

- Logic OMAP-L138 SOM-M1 BOM, Schematic, and Layout (64 MB mDDR configuration included with the eXperimenter Kit) <u>http://support.logicpd.com/downloads/1227/</u>

- Logic TMS320C6748 SOM-M1 BOM, Schematic, and Layout (included with the EVM Development Kit) http://support.logicpd.com/downloads/1228/

### 2 Functional Specification

#### 2.1 Processor

#### 2.1.1 OMAP-L138 Processor

The OMAP-L138 SOM-M1 uses TI's high-performance OMAP-L138 processor. This device contains two cores: an ARM926EJ-S MPU core and a C674x VLIW DSP core. The OMAP-L138 provides many integrated on-chip peripherals, including:

- ARM® ARM926EJ-S<sup>™</sup> RISC core

- C674x VLIW DSP core

- Integrated LCD Controller

- □ Up to 1024 x 1024 x 16 bit color

- Three UARTs

- I2S codec interface

- Universal Serial Bus (USB)

- One high-speed USB 2.0 On-the-Go (OTG) interface

- One full-speed USB 1.1 host interface

- Serial ATA Controller

- □ SATA I (1.5Gb/s) or SATA II (3Gb/s)

- Many general purpose I/O (GPIO) signals

- Programmable timers

- Real time clock (RTC)

- Low power modes

**IMPORTANT NOTE:** The OMAP-L138 processor is heavily multiplexed; using one peripheral may preclude the use of another. Users should carefully review the processor pinout, SOM pinout, and OMAP-L138 multiplexing table. See TI's *OMAP-L138 Low-Power Applications Processor Datasheet*, User Guides, and Application Notes for additional information.

IMPORTANT NOTE: Please visit TI's website for errata on the OMAP-L138.

#### 2.1.2 OMAP-L138 Processor Block Diagram

Figure 2.1: OMAP-L138 Processor Block Diagram

**Note:** The block diagram pictured above comes from TI's *OMAP-L138 Low-Power Applications Processor Data Sheet* (document number SPRS586–June 2009). Available from TI's website: <u>http://www.ti.com/lit/gpn/omap-I138</u>.

#### 2.2 SOM Interface

Logic's common SOM interface allows for easy migration to new processors and technology. Logic is constantly researching and developing new technologies to improve performance, lower cost, and increase feature capabilities. By using the common SOM footprint, it is possible to take advantage of Logic's work without having to re-spin the old design in certain cases dependent upon peripheral usage. Contact Logic sales for more information (<u>product.sales@logicpd.com</u>).

In fact, encapsulating a significant amount of your design onto the SOM reduces any long-term risk of obsolescence. If a component on the SOM design becomes obsolete, Logic will simply design for an alternative part that is transparent to your product. Furthermore, Logic tests all SOMs prior to delivery, decreasing time-to-market and ensuring a simpler and less costly manufacturing process.

#### 2.2.1 OMAP-L138 SOM-M1 Block Diagram

Figure 2.2: OMAP-L138 SOM-M1 Block Diagram

#### 2.3 Mechanical Specifications

#### 2.3.1 Mechanical Characteristics of SOM

| Parameter                   | Min | Typical       | Max | Unit   | Notes |

|-----------------------------|-----|---------------|-----|--------|-------|

| Dimensions                  | —   | 30 x 40 x 4.1 | —   | mm     | 1     |

| Weight                      | —   | 7             | —   | Grams  | 2     |

| Connector Insertion/Removal | —   | 30            | —   | Cycles | _     |

#### Notes:

- 1. The OMAP-L138 SOM-M1 in the Zoom OMAP-L138 EVM Development Kit includes power measurement circuitry along one edge of the SOM. This additional circuitry increases the PCB size to 33.7 x 40 x 4.1 mm. All other OMAP-L138 SOM-M1 modules, including those available in production volumes, are the typical size listed above.

- 2. May vary depending on SOM configuration.

| ΡN | 101375 | 55 Rev 5 |

|----|--------|----------|

|----|--------|----------|

#### 2.3.2 Interface Connectors

The OMAP-L138 SOM-M1 connects to a PCB baseboard through three 100-pin board-to-board (BTB) socket connectors.

| Ref Designator Manufacturer |        | SOM Connector P/N    | Mating Connector P/N |  |

|-----------------------------|--------|----------------------|----------------------|--|

| J1, J2, J3                  | Hirose | DF40C-100DP-0.4V(51) | DF40C-100DS-0.4V(51) |  |

#### 2.3.3 OMAP-L138 SOM-M1 Mechanical Drawings

Please see Appendix A for mechanical drawings of the OMAP-L138 SOM-M1 and recommended baseboard footprint layout.

#### 2.3.4 Example OMAP-L138 SOM-M1 Retention Methods

Please see Appendix B for mechanical drawings demonstrating three possible retention methods for the OMAP-L138 SOM-M1. These drawings are only meant to serve as possible solutions and should not be considered final designs for retention.

#### 2.4 Temperature Specifications

| Parameter                        | Min | Typical | Max | Unit | Notes |

|----------------------------------|-----|---------|-----|------|-------|

| Commercial Operating Temperature | 0   | 25      | 70  | °C   | _     |

| Industrial Operating Temperature | -40 | 25      | 85  | °C   | _     |

| Storage Temperature              | -40 | 25      | 85  | °C   | _     |

**CAUTION:** Systems using the SATA interface on the OMAP-L138 SOM-M1 may require additional heat dissipation techniques in order to comply with the high end of the system temperature limitation. It is the responsibility of the engineer to ensure the OMAP-L138 SOM-M1 maintains a safe operating temperature within the system.

### 3 Electrical Specification

#### 3.1 Absolute Power Maximum Ratings

| Parameter                     | Symbol       | Rating     | Unit |

|-------------------------------|--------------|------------|------|

| DC 5 V Supply Voltage         | 5V           | 0.0 to 7.0 | V    |

| DC Main Battery Input Voltage | MAIN_BATT_IN | 0.0 to 7.0 | V    |

| RTC Backup Battery Voltage    | BACKUP_BATT  | 0.0 to 7.0 | V    |

**NOTE:** These stress ratings are only for transient conditions. Operation at, or beyond, absolute maximum rating conditions may affect reliability and cause permanent damage to the SOM and its components.

#### 3.2 Recommended Power Operating Conditions

| Parameter                     | Min              | Typical | Max              | Unit | Notes |

|-------------------------------|------------------|---------|------------------|------|-------|

| DC Main Battery Input Voltage | 3.3              | 3.6     | 4.2              | V    | 4     |

| DC 5V Voltage                 | 3.6              | 5.0     | 5.8              | V    | 3     |

| DC 5V Active Current          | —                | 220     | —                | mA   | 5     |

| DC 5V Active Current, no SATA | —                | 130     | —                | mA   | 6     |

| DC RTC Backup Battery Voltage | 1.8              | 3.3     | 3.6              | V    |       |

|                               | 0.65*VREF (1.8V) |         |                  |      |       |

| Input Signal High Voltage     | 2 (3.3V)         | ]       | VREF             | V    | 2     |

|                               |                  |         | 0.35*VREF (1.8V) |      |       |

| Input Signal Low Voltage      | GND              | _       | 0.8 (3.3V)       | V    | 2     |

|                               | 2.40 (3.3V)      |         |                  |      |       |

| Output Signal High Voltage    | VREF-0.45 (1.8V) | ]       | VREF             | V    | 2     |

|                               |                  |         | 0.40 (3.3V)      |      |       |

| Output Signal Low Voltage     | GND              | _       | 0.45 (1.8V)      | V    | 2     |

#### Notes:

- 1. General note: CPU power rails are sequenced on the module.

- 2. VREF represents the peripheral I/O supply reference for the specific CPU voltage rail. For  $V_{I/OH}$  and  $V_{I/OL}$ , different values are provided for VREF = 1.8V and 3.3V.

- 3. Please see Section 5.5.1.1 for detailed information about 5V usage on the OMAP-L138 SOM-M1.

- Please see Section 5.5.1.3 for detailed information about MAIN\_BATT\_IN usage on the OMAP-L138 SOM-M1.

- 5. Measurement was taken with a system consisting of SOM, baseboard, and UI board. The SOM was running the standard U-Boot software image. This power measurement represents current consumption on the SOM only (baseboard and UI board were excluded).

- 6. Same setup as Note 5 with the exception that the SATA clock generator was disabled by populating R146.

### 4 Peripheral Specification

#### 4.1 Clocks

The OMAP-L138 SOM-M1 contains two crystals. One crystal is used to generate clocks for the processor core(s) and peripherals. The second crystal is dedicated to the RTC module.

The OMAP-L138 processor includes on-chip Phase Locked Loops (PLLs) and signal dividers which generate all core/peripheral clocks from a single external 24.000 MHz crystal. The maximum core processor operating frequency is 300 MHz. Optionally, on-chip module PLL0 provides an output:

| SOM Pin# | SOM Net Name | OMAP-L138 Processor Pin    |  |  |

|----------|--------------|----------------------------|--|--|

| J3.18    | uP_OBSCLK    | CLKOUT/ UHPI_HDS2/ GP6[14] |  |  |

**IMPORTANT NOTE:** Please see TI's *OMAP-L138 Low-Power Applications Processor Datasheet* and User Guides for additional information about processor clocking.

The OMAP-L138 processor also contains an on-chip Real Time Clock (RTC) module which is driven by an external 32.768 kHz crystal. The highly configurable RTC module provides a time reference to applications running on the OMAP-L138. The SOM contains a dedicated power input pin (J2.64, "VRTC\_IN") and low dropout (LDO) which supplies the processor's dedicated RTC power rail (RTC\_CVDD)

**IMPORTANT NOTE:** For more information on RTC power, see Section 5.5.1.4. For more information about software configuration of the RTC, see TI's *OMAP-L138 Low-Power Applications Processor Datasheet* and User Guides.

#### 4.2 Memory

#### 4.2.1 Mobile DDR

The OMAP-L138 SOM-M1 provides volatile memory via a single mDDR chip. Please refer to the *OMAP-L138 SOM-M1 Bill of Materials (BOM)* for the memory density of your specific SOM.

Other memory densities may be available for SOMs in production volumes. Please contact Logic Sales about custom configurations if your design requires different memory densities from Logic's standard SOM configurations: product.sales@logicpd.com.

#### 4.2.2 SPI Flash

The OMAP-L138 SOM-M1 provides non-volatile memory via an 8 MB SPI flash chip. This is also the default boot device.

Other memory densities may be available for SOMs in production volumes. Please contact Logic Sales about custom configurations if your design requires different memory densities from Logic's standard SOM configurations: product.sales@logicpd.com.

#### 4.3 10/100 Ethernet PHY

The OMAP-L138 SOM-M1 uses an SMSC LAN8710 Ethernet PHY to provide an easy-to-use networking interface. The four analog PHY interface signals (transmit/receive) each require an

#### PN 1013755 Rev 5 Logic Product Development Company, All Rights Reserved PRELIMINARY DOCUMENT—SUBJECT TO CHANGE

external impedance matching circuit to operate properly. Logic provides an example circuit schematic in the *OMAP-L138 Baseboard Schematics*. Please note the TX+/- and RX+/- pairs must be routed as differential pairs on the baseboard PCB.

#### 4.4 Display Interface

The OMAP-L138 has a built-in LCD controller supporting both synchronous (raster-type) and asynchronous (memory-mapped) panels.

The synchronous (raster) module supports STN, color STN, and TFT panels at a resolution of up to 1024 x 1024 x 16-bit color.

The asynchronous (memory-mapped) module supports a broad range of displays from monochrome character displays to TFT smart LCD panels. Displays driven by this module must contain their own memory and timing circuitry.

The signals from the OMAP-L138 LCD controller can be interfaced through the expansion connectors. See TI's *OMAP-L138 Low-Power Applications Processor Datasheet* for further information on the integrated LCD controller. Logic has written drivers for panels of different types and sizes. Please contact Logic before selecting a panel for your application.

**IMPORTANT NOTE:** Using the internal graphics controller will affect processor performance. Selecting display resolutions and color bits per pixel will vary processor busload.

#### 4.5 Serial Interfaces

The OMAP-L138 SOM-M1 comes with the following serial channels: UART0-2, SPI0/1, I2C0/1, McBSP0/1, and McASP. If additional serial channels are required, please contact Logic for reference designs. Please see TI's OMAP-L138 User Guides for further information regarding serial communications.

#### 4.5.1 UART0-2

The OMAP-L138 SOM-M1 provides three UART ports. UART0, UART1, and UART2 are asynchronous 16C550-compatible UARTs. These UARTs are high-speed serial interfaces that use 16-byte TX and RX FIFO registers; they are capable of sending and receiving serial data simultaneously. The signals from the SOM are not RS232 level signals. The end-product design must provide an external transceiver for RS232 applications. Logic has provided an example reference design with the Zoom OMAP-L138 Development Kits. When choosing an RS232 transceiver, the designer should keep in mind cost, availability, ESD protection, and data rates.

UART2 has been configured as the main SOM serial port. The UART2 baud rate is set to a default 115.2 Kbits/sec, though it supports most common serial baud rates.

#### 4.5.2 SPI0/1

The OMAP-L138 SOM-M1 provides two SPI ports with multiple chip selects.

SPI1 is the default boot source for the OMAP-L138 SOM-M1. A serial flash chip is attached to SPI1 CS0.

#### 4.5.3 I2C0/1

The OMAP-L138 SOM-M1 provides two I2C ports. The clock and data signals for both ports have 4.7K pull-up resistors to their respective power rails on the SOM. Please see TI's OMAP-L138 User Guides for further information.

I2C0 has been configured as the main SOM I2C port. I2C0 is used to control/configure many ICs on the SOM as well as the OMAP-L138 Development Kits.

#### 4.5.4 McBSP0/1

The OMAP-L138 SOM-M1 supports two Multi-channel Buffered Serial Port (McBSP) interfaces. These interfaces are primarily designed to support AC97 and IIS modes, but they can also be configured for other serial formats. However, The McBSPs are not intended to be used as high-speed interfaces.

#### 4.5.5 McASP

The OMAP-L138 SOM-M1 supports one Multi-channel Audio Serial Port (McASP). The McASP interface supports TDM streams, I2S protocols, and DIT.

Logic has provided an example reference design with the Zoom OMAP-L138 Development Kits; this reference design interfaces the OMAP-L138 McASP to a TLV320AIC3106 audio codec.

#### 4.6 USB Interface

The OMAP-L138 SOM-M1 supports one USB 1.1 full-speed host port and one USB 2.0 OTG port, which can function as a host or device/client. The USB 2.0 port can operate at up to 480 Mbit/sec, and the USB 1.1 port can operate at up to 12 Mbit/sec. Both the USB 1.1 and USB 2.0 controllers are internal to the OMAP-L138 processor. For more information on using both the USB host and OTG interfaces, please see TI's OMAP-L138 User Guides.

**IMPORTANT NOTE:** In order to correctly implement USB on the SOM, additional impedance matching circuitry may be required on the USBx\_D+ and USBx\_D- signals before they can be used. USB 2.0 requirements specify the signals must be routed as differential pairs with a 90 ohm differential impedance. Refer to the USB 2.0 Specification for detailed information.

#### 4.7 ADC/Touch Interface

The touch screen controller (TSC) on the OMAP-L138 SOM-M1 is an integrated feature of the TPS65070 PMIC. This TSC is used to support standard 4-wire resistive touch panels. The TPS65070 is connected to the OMAP-L138 by the I2C0 interface. Please see TI's *TPS65070 Datasheet* for more information.

#### 4.8 General Purpose I/O (GPIO)

Logic designed the OMAP-L138 SOM-M1 to be flexible and provide multiple options for analog and digital GPIO. There are numerous digital GPIO pins on the SOM that interface to the OMAP-L138. See Section 7 of this document for more information. If certain peripherals are not desired, such as the LCD controller, chip selects, IRQs, or UARTs, then more GPIO pins become available.

#### 4.9 Expansion/Feature Options

The OMAP-L138 SOM-M1 was designed for expansion and a variable feature set, providing all the necessary control signals and bus signals to expand the user's design. Some of these signals are buffered before reaching the expansion connectors. See TI's *OMAP-L138 Low-Power Applications Processor Datasheet* and User Guides and Logic's *OMAP-L138 SOM-M1 Schematics* for more details. Logic has experience implementing additional options, including: audio codecs, Ethernet ICs, co-processors, and components on SOMs. Please contact Logic for potential reference designs before selecting your peripherals.

### 5 System Integration

#### 5.1 Custom Configuration

The OMAP-L138 SOM-M1 was designed to meet multiple applications for users with specific design and budget requirements. As a result, this SOM supports a variety of embedded operating systems, flexible mDDR and SPI flash memory footprints, and other hardware configurations. If your application needs require unique hardware or software configurations, please contact Logic Sales about custom SOMs available in production volumes: product.sales@logicpd.com.

#### 5.2 Resets

The OMAP-L138 SOM-M1 has a reset input (MSTR\_nRST) and a reset output (RESETOUTn). External devices use MSTR\_nRST to assert reset to the product. The OMAP-L138 SOM-M1 uses RESETOUTn to indicate to other devices that the SOM is in reset.

#### 5.2.1 Master Reset (MSTR\_nRST)—Reset Input

Logic suggests that custom designs implementing the OMAP-L138 SOM-M1 use the MSTR\_nRST signal as the "pin-hole" reset used in commercial embedded systems. The MSTR\_nRST triggers a power-on-reset event to the OMAP-L138 processor and resets the entire CPU.

**IMPORTANT NOTE:** Any custom reset circuit design should guard the assertion of the reset lines during a low power state so as to prevent power-up in a low or bad power condition. (Powering up in a low or bad power condition will cause data corruption and, possibly, temporary system lockup). See the "Power Management" section of this document for further details. A low pulse on the MSTR\_nRST signal will cause a system-wide reset.

#### Low Pulse on MSTR\_nRST Signal:

A low pulse on the MSTR\_nRST signal, asserted by an external source (for example, the reset button on the custom design application) will bring MSTR\_nRST low until the assertion source is de-asserted. There is no delay beyond the de-assertion of the external MSTR\_nRST signal source, so the custom design must ensure that the assertion time is sufficient for all related peripherals.

Logic suggests that for any external assertion source that triggers the MSTR\_nRST signal, analog or digital, de-bouncing should be used to generate a clean, one-shot reset signal.

#### 5.2.2 SOM Reset (RESETOUTn)—Reset output

All hardware peripherals should connect their hardware-reset pin to the RESETOUTn signal on the expansion connector. Internally, all OMAP-L138 SOM-M1 peripheral hardware reset pins are connected to the RESET\_nOUT net.

If the output of the onboard voltage-monitoring circuit is asserted (active low), the user can expect to lose information stored in RAM. The data loss occurs because the CPU is reset to its reset defaults.

#### 5.3 Interrupts

The OMAP-L138 interrupt controller allows either the ARM or DSP core to enable, disable, trigger, or service all interrupts. Most external GPIO signals can also be configured as interrupt inputs by configuring their pin control registers. Logic BSPs setup and process all onboard system and external SOM interrupt sources. Refer to TI's *OMAP-L138 Low-Power Applications Processor Datasheet* and User Guides for further information on using interrupts.

#### 5.4 JTAG Debugger Interface

The JTAG connection on the OMAP-L138 allows recovery of corrupted flash memory, real-time application debug, and DSP development. There are several third-party JTAG debuggers available for TI microcontrollers. The following signals make up the JTAG interface to the OMAP-L138 processor: TDI, TMS, TCK, TDO, nTRST, RTCK, EMU0, EMU1, and MSTR\_nRST (MSTR\_nRST is only required for some JTAG tools; see the JTAG tool documentation for exact pinout). These signals should interface directly to a 14 or 20-pin 0.1" through-hole connector, as shown on Logic's *OMAP-L138 Baseboard Schematic*.

**IMPORTANT NOTE:** When laying out the JTAG connector, realize that it may not be numbered as a standard 14 or 20-pin 0.1" insulation displacement connector (IDC) through-hole connector. See the *OMAP-L138 Baseboard Schematic* for further details. Each JTAG tool vendor may define the IDC connector pin-out differently.

#### 5.5 Power Management

#### 5.5.1 System Power Supplies

In order to ensure a flexible design, the OMAP-L138 SOM-M1 has the following power areas: MAIN\_BATT\_IN, 5V, RTC\_BATT. All power areas are inputs to the SOM. The module also provides output reference voltage 3.3V\_or\_1.8V. 3.3V\_or\_1.8V is an output from the SOM, and should only be used as a reference voltage input to level shifting devices on baseboard designs.

**IMPORTANT NOTE:** If USB0\_VBUS is powered externally it will power the SOM, even if MAIN\_BATT\_IN and 5V are disconnected. Additionally, USB0\_VBUS can charge MAIN\_BATT\_IN. Please refer to the *TPS65070 Datasheet* for more information.

#### 5.5.1.1 5V

The 5V input is the main source of power for the OMAP-L138 SOM-M1. If power is present at the 5V input, the TPS65070 PMIC will preferentially select this power source over all other sources. If appropriate voltage is applied to the 5V input, the TPS65070 PMIC and OMAP-L138 processor will immediately start up and run. 5V input is capable of charging MAIN\_BATT\_IN.

For startup, acceptable 5V input range is: 3.6V < 5V input < 5.8V

At runtime, 5V range is: UVLO < 5V input < 5.8V

UVLO = UnderVoltage LockOut

UVLO = 3.0V (default), 2.8V < UVLO < 3.25V (programmable)

#### 5.5.1.2 USB0\_VBUS

USB0\_VBUS is an optional power source for the OMAP-L138 SOM-M1. If power is present at the USB0\_VBUS input, the TPS65070 PMIC will preferentially select this source over

#### PN 1013755 Rev 5 Logic Product Development Company, All Rights Reserved PRELIMINARY DOCUMENT—SUBJECT TO CHANGE

MAIN\_BATT\_IN. If appropriate voltage is applied to the USB0\_VBUS input, the TPS65070 PMIC and OMAP-L138 processor will immediately start up and run. The USB0\_VBUS input is capable of charging MAIN\_BATT\_IN.

#### 5.5.1.3 MAIN\_BATT\_IN

The MAIN\_BATT\_IN input is designed to be connected to a typical single lithium-ion battery. The TPS65070 PMIC will only power the SOM from MAIN\_BATT\_IN if power is not present at 5V or USB0\_VBUS inputs. If appropriate voltage is applied to the MAIN\_BATT\_IN input, the TPS65070 PMIC and OMAP-L138 processor will NOT immediately start up and run; a momentary low signal is also required on the PMIC\_PB\_IN pin. The TPS65070 PMIC is capable of charging MAIN\_BATT\_IN from either the 5V input or the USB0\_VBUS input.

For startup, MAIN\_BATT\_IN range is: 3.6V < MAIN\_BATT\_IN < 4.2V

At runtime, MAIN\_BATT\_IN range is: UVLO < MAIN\_BATT\_IN < 4.2V

UVLO = UnderVoltage LockOut

UVLO = 3.0V (default), 2.8V < UVLO < 3.25V (programmable)

#### **IMPORTANT NOTES:**

Though UVLO may be set as low as 2.8V, not all OMAP-L138 SOM-M1 circuits are capable of 2.8V operation. The SOM contains an internal 3.3V power rail, and devices connected to this rail may have dropout voltages much greater than UVLO. See Section 3.2 for the recommended range of input voltages.

Before designing a system which powers the OMAP-L138 SOM-M1 from MAIN\_BATT\_IN, the user should first review the following documents: *TPS65070 Datasheet*, *OMAP-L138 SOM-M1 Schematic*, and *OMAP-L138 Baseboard Schematic*.

#### 5.5.1.4 VRTC\_IN

The VRTC\_IN power rail is used to power the onboard RTC module. Always power this rail to maintain the clock of the product. A lithium-ion coin cell typically supplies power to this rail.

#### 5.5.2 Dual Voltage I/O

The OMAP-L138 processor and OMAP-L138 SOM-M1 uniquely support dual-voltage I/O. The user may select an operating voltage of either 1.8V or 3.3V through "IO\_VOLTAGE\_SEL" J1.37. For 3.3V operation, J1.37 should be left unconnected. For 1.8V operation, J1.37 should be tied directly to GND.

#### 5.5.3 System Power Management

Good power management design is important in any system development and embedded system design is no exception. In embedded system design, power management is typically one of the most complicated areas due to the dramatic effect it has on product cost, performance, usability, and overall customer satisfaction. Many factors affect a power-efficient hardware design: power supply selection (efficiency), clocking design, IC and component selection, etc. The OMAP-L138 SOM-M1 was designed with these aspects in mind while also providing maximum flexibility in software and system integration.

On the OMAP-L138 there are many different software configurations that drastically affect power consumption: microcontroller core clock frequency, bus clock frequency, peripheral clocks, bus

modes, power management states; peripheral power states and modes; product user scenarios; interrupt handling; and display settings (resolution, backlight, refresh, bits per pixel, etc). These settings are typically initialized in the startup software routines and may be modified later in the operating system and application software. Information for these items can be found in the appropriate documents such as the *U-Boot User's Manual*, TI's *OMAP-L138 Low-Power Applications Processor Datasheet* and User Guides, *TPS65070 Datasheet*, and Logic's *OMAP-L138 SOM-M1 Schematic*.

#### 5.5.4 Microcontroller

The OMAP-L138 processor's power management scheme was designed for ultra-low power, so naturally the static and dynamic power consumption has very flexible controls allowing designers to configure the processor to minimize end-product power consumption. Most peripheral modules can be powered on/off individually, and the core(s) can enter various levels of standby/sleep. To implement a low-power system, users should review TI's *OMAP-L138 Low-Power Applications Processor Datasheet* and User Guides, *TPS65070 Datasheet*, and Logic's *OMAP-L138 SOM-M1 Schematic*.

#### 5.6 ESD Considerations

The OMAP-L138 SOM-M1 was designed to interface to a customer's peripheral board, while remaining low cost and adaptable to many different applications. The SOM does not provide any onboard ESD protection circuitry—this must be provided by the product it is used in. Logic has extensive experience in designing products with ESD requirements. Please contact Logic if you need any assistance in ESD design considerations.

# 6 Memory & I/O Mapping

| Chip Select   | Device/Feature   | Notes                                                                              |

|---------------|------------------|------------------------------------------------------------------------------------|

| SPI0_SCS[0:5] | Not Available    | MDIO/MII comm. interfaces on SOM                                                   |

| SPI1_SCS[0]   | SPI Flash (boot) | LCD Backlight PWM on dev kit                                                       |

| SPI1_SCS[1]   |                  | LCD Backlight Power on dev kit                                                     |

| SPI1_SCS[2:3] |                  | Available for use by an off-board external device                                  |

| SPI1_SCS[4]   |                  | UART TXD on dev kit                                                                |

| SPI1_SCS[5]   |                  | UART RXD on dev kit                                                                |

| SPI1_SCS[6]   | Not Available    | I2C0 is used extensively for configuration/control<br>on both the SOM and dev. kit |

| SPI1_SCS[7]   | Not Available    | I2C0 is used extensively for configuration/control<br>on both the SOM and dev. kit |

| EMA_CS[0]     |                  | Available for use by an off-board external device                                  |

| EMA_CS[2:5]   |                  | Available for use by an off-board external device                                  |

| UHPI_HCS      |                  | Available for use by an off-board external device                                  |

OMAP-L138 chip select signals are described listed below:

## 7 Pin Descriptions & Functions

SOM Net Name: This is the name used in Logic's OMAP-L138 SOM-M1 Schematics.

**Processor Name:** This is the name used TI's *OMAP-L138 Low-Power Applications Processor Datasheet*.

**I/O:** This indicates the default pin configuration after booting U-Boot. Most pins can be reconfigured as either input or output. Consult Logic's *OMAP-L138 SOM-M1 Schematics* and TI's *OMAP-L138 Low-Power Applications Processor Datasheet* for more information.

**Description:** If a pull-up or pull-down resistor is present on the OMAP-L138 SOM-M1, it will be noted here. Special usage tips and cautions will be noted here. Consult Logic's *OMAP-L138 SOM-M1 Schematics* and TI's *OMAP-L138 Low-Power Applications Processor Datasheet* for more information.

#### 7.1 J1 Connector 100-Pin Descriptions

| J1 Pin# | SOM Net Name   | Processor Name                                              | I/O  | Voltage                      | Description                                                                                                                                           |

|---------|----------------|-------------------------------------------------------------|------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | uP_VPIF_DOUT8  | VP_DOUT[8]/<br>LCD_D[8]/<br>UPP_XD[0]/<br>GP7[0]/ BOOT[0]   |      | 3.3V or 1.8V<br>(see Note 1) | LCD G3 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-down on SOM.<br>Used to latch boot mode at startup (see<br>Note 2). |

| 2       | uP_VPIF_DOUT0  | VP_DOUT[0]/<br>LCD_D[0]/<br>UPP_XD[8]/<br>GP7[8]            | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD B1 data bit when outputting RGB565<br>data to an RGB666 display.                                                                                  |

| 3       | uP_VPIF_DOUT9  | VP_DOUT[9]/<br>LCD_D[9]/<br>UPP_XD[1]/<br>GP7[1]/ BOOT[1]   |      | 3.3V or 1.8V<br>(see Note 1) | LCD_G4 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-down on SOM.<br>Used to latch boot mode at startup (see<br>Note 2). |

| 4       | uP_VPIF_DOUT1  | VP_DOUT[1]/<br>LCD_D[1]/<br>UPP_XD[9]/<br>GP7[9]            | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_B2 data bit when outputting RGB565 data to an RGB666 display.                                                                                     |

| 5       | uP_VPIF_DOUT10 | VP_DOUT[10]/<br>LCD_D[10]/<br>UPP_XD[2]/<br>GP7[2]/ BOOT[2] |      | 3.3V or 1.8V<br>(see Note 1) | LCD_G5 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-up on SOM.<br>Used to latch boot mode at startup (see<br>Note 2).   |

| 6       | uP_VPIF_DOUT2  | VP_DOUT[2]/<br>LCD_D[2]/<br>UPP_XD[10]/<br>GP7[10]          |      | 3.3V or 1.8V<br>(see Note 1) | LCD_B3 data bit when outputting RGB565 data to an RGB666 display.                                                                                     |

| 7       | uP_VPIF_DOUT11 | VP_DOUT[11]/<br>LCD_D[11]/<br>UPP_XD[3]/<br>GP7[3]/ BOOT[3] |      | 3.3V or 1.8V<br>(see Note 1) | LCD_R1 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-up on SOM.<br>Used to latch boot mode at startup (see<br>Note 2).   |

| 8       | uP_VPIF_DOUT3  | VP_DOUT[3]/<br>LCD_D[3]/<br>UPP_XD[11]/<br>GP7[11]          | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_B4 data bit when outputting RGB565 data to an RGB666 display.                                                                                     |

| J1 Pin# | SOM Net Name          | Processor Name                                              | I/O  | Voltage                      | Description                                                                                                                                                                                                                                                                                       |

|---------|-----------------------|-------------------------------------------------------------|------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | uP_VPIF_DOUT12        | VP_DOUT[12]/<br>LCD_D[12]/<br>UPP_XD[4]/<br>GP7[4]/ BOOT[4] | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_R2 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-down on SOM.<br>Used to latch boot mode at startup (see<br>Note 2).                                                                                                                                             |

| 10      | uP_VPIF_DOUT4         | VP_DOUT[4]/<br>LCD_D[4]/<br>UPP_XD[12]/<br>GP7[12]          | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_B5 data bit when outputting RGB565<br>data to an RGB666 display. Notice that<br>LCD_B0 is omitted; LCD_B5 (Blue MSB) is<br>also connected to LCD_B0 (Blue LSB)<br>when driving an 18 bit display with 16 bits.                                                                                |

| 11      | uP_VPIF_DOUT13        | VP_DOUT[13]/<br>LCD_D[13]/<br>UPP_XD[5]/<br>GP7[5]/ BOOT[5] | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_R3 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-down on SOM.<br>Used to latch boot mode at startup (see<br>Note 2).                                                                                                                                             |

| 12      | uP_VPIF_DOUT5         | VP_DOUT[5]/<br>LCD_D[5]/<br>UPP_XD[13]/<br>GP7[13]          | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_G0 data bit when outputting RGB565 data to an RGB666 display.                                                                                                                                                                                                                                 |

| 13      | uP_VPIF_DOUT14        | VP_DOUT[14]/<br>LCD_D[14]/<br>UPP_XD[6]/<br>GP7[6]/ BOOT[6] | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_R4 data bit when outputting RGB565<br>data to an RGB666 display.<br>4.7k pull-down on SOM.<br>Used to latch boot mode at startup (see<br>Note 2).                                                                                                                                             |

| 14      | uP_VPIF_DOUT6         | VP_DOUT[6]/<br>LCD_D[6]/<br>UPP_XD[14]/<br>GP7[14]          | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_G1 data bit when outputting RGB565 data to an RGB666 display.                                                                                                                                                                                                                                 |

| 15      | uP_VPIF_DOUT15        | VP_DOUT[15]/<br>LCD_D[15]/<br>UPP_XD[7]/<br>GP7[7]/ BOOT[7] | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | LCD_R5 data bit when outputting RGB565<br>data to an RGB666 display. Notice that<br>LCD_R0 is omitted; LCD_R5 (Red MSB) is<br>also connected to LCD_R0 (Red LSB)<br>when driving an 18 bit display with 16 bits.<br>4.7k pull-down on SOM.<br>Used to latch boot mode at startup (see<br>Note 2). |

| 16      | uP_VPIF_DOUT7         | VP_DOUT[7]/<br>LCD_D[7]/<br>UPP_XD[15]/<br>GP7[15]          | Hi-Z |                              | LCD_G2 data bit when outputting RGB565 data to an RGB666 display.                                                                                                                                                                                                                                 |

| 17      | uP_LCD_HSYNC          | MMCSD1_DAT[5]/<br>LCD_HSYNC/<br>GP8[9]                      | Hi-Z | 3.3V or 1.8V<br>(see Note 1) |                                                                                                                                                                                                                                                                                                   |

| 18      | uP_LCD_PCLK           | MMCSD1_DAT[7]/<br>LCD_PCLK/<br>GP8[11]                      | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | 22 ohm series R on SOM.                                                                                                                                                                                                                                                                           |

| 19      | DGND                  | <u> </u>                                                    | Ι    | GND                          | Ground. Connect to digital ground.                                                                                                                                                                                                                                                                |

| 20      | DGND                  | <u> </u>                                                    | Ι    | GND                          | Ground. Connect to digital ground.                                                                                                                                                                                                                                                                |

| 21      | uP_LCD_VSYNC          | MMCSD1_DAT[4]/<br>LCD_VSYNC/<br>GP8[8]                      | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | _                                                                                                                                                                                                                                                                                                 |

| 22      | uP_LCD_MCLK           | MMCSD1_DAT[6]/<br>LCD_MCLK/<br>GP8[10]                      | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | 22 ohm series R on SOM.                                                                                                                                                                                                                                                                           |

| 23      | uP_LCD_AC_ENB_C<br>Sn | LCD_AC_ENB_C<br>S/ GP6[0]                                   | Hi-Z | 3.3V or 1.8V<br>(see Note 1) | _                                                                                                                                                                                                                                                                                                 |

| J1 Pin# | SOM Net Name    | Processor Name                                       | I/O    | Voltage                      | Description                                                                                                  |

|---------|-----------------|------------------------------------------------------|--------|------------------------------|--------------------------------------------------------------------------------------------------------------|

|         |                 | VP_CLKIN0/<br>UHPI_HCS/                              |        |                              |                                                                                                              |

|         |                 | GP6[7]/                                              |        | 3.3V or 1.8V                 |                                                                                                              |

|         | uP_VPIF_CLKIN0  | UPP_2xTXCLK                                          |        | (see Note 1)                 | —                                                                                                            |

| 25      | uP_USB0_DRVVBUS | — —                                                  | 0      |                              | —                                                                                                            |

|         |                 | VP_DIN[14]_<br>HSYNC/<br>UHPI_HD[6]/                 |        | 3.3V or 1.8V                 |                                                                                                              |

| 26      | uP_VPIF_DIN14   | UPP_CHA_D[6]                                         | Hi-Z   | (see Note 1)                 | —                                                                                                            |

| 27      | uP_VPIF_CLKO3   | VP_CLKOUT3/<br>GP6[1]                                | Hi-Z   | 3.3V or 1.8V<br>(see Note 1) | 22 ohm series R on SOM.                                                                                      |

| 28      | uP_VPIF_DIN15   | VP_DIN[15]_<br>VSYNC/<br>UHPI_HD[7]/<br>UPP_CHA_D[7] | Hi-7   | 3.3V or 1.8V<br>(see Note 1) |                                                                                                              |

|         |                 |                                                      |        |                              | 4.7k pull-up on SOM.                                                                                         |

| 29      | uP_RESETn       | RESET                                                | Ι      |                              | Also connected to PGOOD on TPS65070<br>PMIC. PGOOD is an open drain output.                                  |

| 30      | RFU             | —                                                    | NA     | NA                           | Reserved for future use. Do not connect.                                                                     |

| 31      | uP NMIn         | NMI                                                  |        |                              | 4.7k pull-up on SOM.<br>Also connected to INTn on TPS65070<br>PMIC. INTn is an open drain output.            |

| 32      | uP VPIF DIN13   | VP_DIN[13]_<br>FIELD/<br>UHPI_HD[5]/<br>UPP_CHA_D[5] |        | 3.3V or 1.8V<br>(see Note 1) |                                                                                                              |

|         |                 |                                                      |        |                              | Input to TPS65070 PMIC, not OMAP-L138.<br>See Section 5.5.1.3.<br>Buffered version of this input can be read |

| 33      | PMIC_PB_IN      | <u> </u>                                             | I/O    |                              | on OMAP-L138 pin EMA_RAS / GPIO2[5]                                                                          |

| 34      | uP_VPIF_DIN12   | VP_DIN[12]/<br>UHPI_HD[4]/<br>UPP_CHA_D[4]           | Hi-Z   | 3.3V or 1.8V<br>(see Note 1) |                                                                                                              |

| 35      | RFU             | —                                                    | NA     | NA                           | Reserved for future use. Do not connect.                                                                     |

| 36      | uP_VPIF_DIN11   | VP_DIN[11]/<br>UHPI_HD[3]/<br>UPP_CHA_D[3]           | Hi-Z   | 3.3V or 1.8V<br>(see Note 1) |                                                                                                              |