# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Platform Manager**

In-System Programmable Power and Digital Board Management

#### February 2012

#### Data Sheet DS1036

#### **Features**

- Precision Voltage Monitoring Increases Reliability

- 12 independent analog monitor inputs

- Differential inputs for remote ground sense

- Two programmable threshold comparators per analog input

- Hardware window comparison

- 10-bit ADC for I<sup>2</sup>C monitoring

- High-Voltage FET Drivers Enable Integration

- Power supply ramp up/down control

- Programmable current and voltage output

- Independently configurable for FET control or digital output

- **Power Supply Margin and Trim Functions**

- Trim and margin up to eight power supplies

- Dynamic voltage control through I<sup>2</sup>C

- Independent Digital Closed-Loop Trim function for each output

- Programmable Timers Increase Control Flexibility

- Four independent timers

- + 32  $\mu s$  to 2 second intervals for timing sequences

- PLD Resources Integrate Power and Digital Functions

- 48-macrocell CPLD

- 640 LUT4s FPGA

- Up to 107 digital I/Os

- Up to 6.1 Kbits distributed RAM

- Programmable sysIO<sup>™</sup> Buffer Supports a Range of Interfaces

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- System-Level Support

- Single 3.3V supply operation

- Industrial temperature range: -40°C to +85°C

- In-System Programmability Reduces Risk

- Integrated non-volatile configuration memory

JTAG programming interface

- Package Options

- 128-pin TQFP

- 208-ball ftBGA

- · RoHS compliant and halogen-free

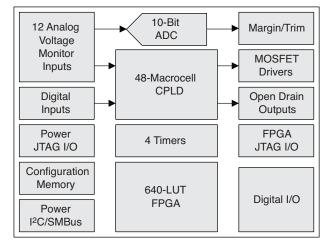

## **Block Diagram**

# Description

The Lattice Platform Manager integrates board power management (hot-swap, sequencing, monitoring, reset generation, trimming and margining) and digital board management functions (reset tree, non-volatile error logging, glue logic, board digital signal monitoring and control, system bus interface, etc.) into a single integrated solution.

The Platform Manager device provides 12 independent analog input channels to monitor up to 12 power supply test points. Up to 12 of these input channels can be monitored through differential inputs to support remote ground sensing. Each of the analog input channels is monitored through two independently programmable comparators to support both high/low and in-bounds/ out-of-bounds (window-compare) monitor functions. Up to six general purpose 5V tolerant digital inputs are also provided for miscellaneous control functions.

There are 16 open-drain digital outputs that can be used for controlling DC-DC converters, low-drop-out regulators (LDOs) and opto-couplers, as well as for supervisory and general purpose logic interface functions. Four of these outputs (HVOUT1-HVOUT4) may be configured as high-voltage MOSFET drivers. In highvoltage mode these outputs can provide up to 12V for driving the gates of n-channel MOSFETs so that they can be used as high-side power switches controlling the supplies with a programmable ramp rate for both ramp up and ramp down.

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

The board power management function can be implemented using an internal 48-macrocell CPLD. The status of all of the comparators on the analog input channels as well as the general purpose digital inputs are used as inputs by the CPLD array, and all digital outputs (open-drain as well as HVOUT) may be controlled by the CPLD.

Four independently programmable timers can create delays and time-outs ranging from 32  $\mu$ s to 2 seconds.

The Platform Manager device incorporates up to eight DACs for generating trimming voltage to control the output voltage of a DC-DC converter. Additionally, each power supply output voltage can be maintained typically within 0.5% tolerance across various load conditions using the Digital Closed Loop Control mode.

The internal 10-bit A/D converter can both be used to monitor the VMON voltage through the I<sup>2</sup>C bus as well as for implementing digital closed loop mode for maintaining the output voltage of all power supplies controlled by the monitoring and trimming section of the Platform Manager device.

The FPGA section of the Platform Manager is optimized to meet the requirements of board management functions including reset distribution, boundary scan management, fault logging, FPGA load control, and system bus interface. The FPGA section uses look-up tables (LUTs) and distributed memories for flexible and efficient logic implementation. This instant-on capability enables the Platform Manager devices to integrate control functions that are required as soon as power is applied to the board.

Power management functions can be integrated into the CPLD and digital board management functions can be integrated into the FPGA using the LogiBuilder tool provided by PAC-Designer<sup>®</sup> software. In addition, the FPGA designs can also be implemented in VHDL or Verilog HDL through the ispLEVER<sup>®</sup> software design tool.

The Platform Manager IC supports a hardware I<sup>2</sup>C/SMBus slave interface that can be used to measure voltages through the Analog to Digital Converter or is used for trimming and margining using a microcontroller.

There are two JTAG ports integrated into the Platform Manager device: Power JTAG and FPGA JTAG. The Power JTAG interface is used to program the power section of the Platform Manager and the FPGA JTAG is used to configure the FPGA portion of the device. The FPGA configuration memory can be changed in-system without interrupting the operation of the board management section. However, the Power Management section of the platform Manager cannot be changed without interrupting the power management operation.

| Parameter       | LPTM10-1247  | LPTM10-12107   |

|-----------------|--------------|----------------|

| Analog Inputs   | 12           | 12             |

| Margin and Trim | 6            | 8              |

| Total I/O       | 47           | 107            |

| CPLD Macrocells | 48           | 48             |

| FPGA LUTs       | 640          | 640            |

| Package         | 128-pin TQFP | 208-ball ftBGA |

#### Table 1. Platform Manager Family Selection Table

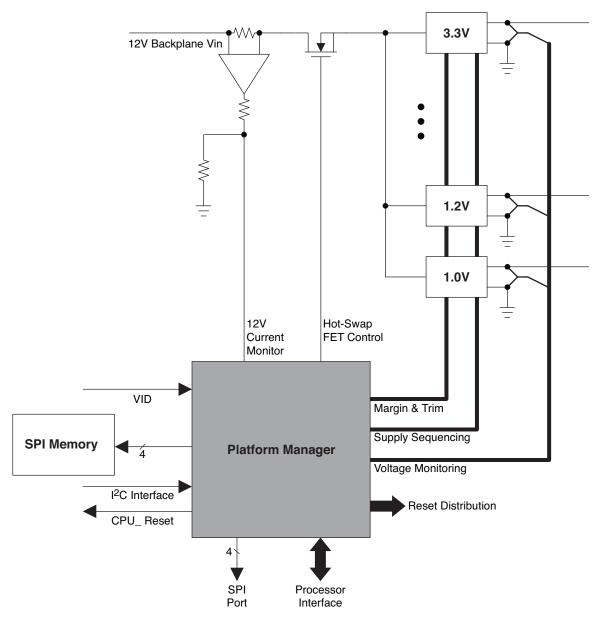

Figure 1. Typical Platform Manager Application

Note: See reference design, IP documentation and application notes for more information on implementation of individual functions called out above.

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Power Management Core Supply P <sub>VCCD</sub> 0.5 to 4.5V                            |

|---------------------------------------------------------------------------------------|

| Power Management Analog Supply P <sub>VCCA</sub> 0.5 to 4.5V                          |

| Power Management Digital Input Supply P <sub>VCCA</sub> (IN[1:4]) P <sub>VCCINP</sub> |

| Power Management JTAG Logic Supply P <sub>VCCJ</sub>                                  |

| Power Management Alternate $E^2$ programming supply APS <sup>4</sup>                  |

| Power Management Digital Input Voltage (All Digital I/O Pins) V $_{\rm IN}$           |

| VMON Input Voltage                                                                    |

| VMON Input Voltage Ground Sense                                                       |

| Voltage Applied to Power Management Tri-stated Pins (HVOUT[1:4])                      |

| Voltage Applied to Power Management Tri-stated Pins (OUT[5:16])                       |

| Maximum Sink Current on Any Power Management Output                                   |

| FPGA Supply Voltage V <sub>CC</sub>                                                   |

| FPGA Supply Voltage V <sub>CCAUX</sub> 0.5 to 3.75V                                   |

| FPGA Output Supply Voltage V <sub>CCIO</sub> 0.5 to 3.75V                             |

| FPGA I/O Tri-state Voltage Applied <sup>5</sup>                                       |

| FPGA Dedicated Input Voltage Applied <sup>5</sup>                                     |

| Device Storage Temperature                                                            |

| Junction Temperature T <sub>J</sub> +125°C                                            |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND (FPGA section) or GNDA/D (Power sections).

4. The APS pin MUST be left floating when PVCCD and PVCCA are powered.

5. Overshoot and undershoot of -2V to ( $V_{IHMAX}$  + 2) volts is permitted for a duration of <20 ns.

## **Recommended Operating Conditions**

| Symbol                                             | Parameter                                              | Conditions                                                   | Min.  | Max.                   | Units |

|----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|-------|------------------------|-------|

| P <sub>VCCD</sub> , P <sub>VCCA</sub> <sup>1</sup> | Core supply voltage at pin                             |                                                              | 2.8   | 3.96                   | V     |

| P <sub>VCCINP</sub>                                | Digital input supply for IN[1:4] at pin                |                                                              | 2.25  | 5.5                    | V     |

| P <sub>VCCJ</sub>                                  | JTAG logic supply voltage at pin                       |                                                              | 2.25  | 3.6                    | V     |

| APS                                                | Alternate E <sup>2</sup> programming supply at pin     | P <sub>VCCD</sub> and P <sub>VCCA</sub> powered              |       | onnect<br>eft Floating |       |

|                                                    |                                                        | P <sub>VCCD</sub> and P <sub>VCCA</sub> not powered          | 3.0   | 3.6                    | V     |

| V <sub>IN</sub>                                    | Input voltage at digital input pins                    |                                                              | -0.3  | 5.5                    | V     |

| V <sub>MON</sub>                                   | Input voltage at V <sub>MON</sub> pins                 |                                                              | -0.3  | 5.9                    | V     |

| V <sub>MONGS</sub>                                 | Input voltage at V <sub>MONGS</sub> pins               |                                                              | -0.2  | 0.3                    | V     |

| V <sub>OUT</sub>                                   |                                                        | OUT[5:16] pins                                               | -0.3  | 5.5                    | V     |

|                                                    |                                                        | HVOUT[1:4] pins in open-drain mode                           | -0.3  | 13.0                   | V     |

| V <sub>CC</sub> <sup>2</sup>                       | FPGA Core Supply Voltage                               |                                                              | 3.135 | 3.465                  | V     |

| V <sub>CCAUX</sub> <sup>2</sup>                    | FPGA Auxiliary Supply Voltage                          |                                                              | 3.135 | 3.465                  | V     |

| V 3                                                | FRCA 1/O Driver Supply Veltage                         | V <sub>CCIO0</sub> , V <sub>CCIO1</sub> , V <sub>CCIO3</sub> | 1.14  | 3.465                  | V     |

| V <sub>CCIO</sub> <sup>3</sup>                     | FPGA I/O Driver Supply Voltage                         | V <sub>CCIO2</sub>                                           | 2.25  | 3.6                    | V     |

| t <sub>JCOM</sub>                                  | Junction Temperature Commercial<br>Operation           | Power applied                                                | 0     | +85                    | °C    |

| t <sub>JIND</sub>                                  | Junction Temperature Industrial<br>Operation           | Power applied                                                | -40   | +100                   | °C    |

| t <sub>JFLASHCOM</sub>                             | Junction Temperature, Flash<br>Programming, Commercial |                                                              | 0     | +85                    | °C    |

| t <sub>JFLASHIND</sub>                             | Junction Temperature, Flash<br>Programming, Industrial |                                                              | -40   | +100                   | °C    |

1. P<sub>VCCD</sub> and P<sub>VCCA</sub> must always be tied together.

2. V<sub>CC</sub> and V<sub>CCAUX</sub> must always be tied together. Also, like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both 3.3V, they must also be the same supply.

3. See recommended voltages by I/O standard in subsequent table.

# Digital I/O Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Condition                                 | Min. | Тур. | Max     | Units |

|-----------------|------------------------------|-------------------------------------------|------|------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 \leq V_{IN} \leq V_{IH} \text{ (MAX)}$ |      |      | +/-1000 | μΑ    |

$\begin{array}{l} 1. \mbox{ Assumes monotonic rise/fall rates for } V_{CC,} \ V_{CCAUX,} \ \mbox{and } V_{CCIO.} \\ 2. \ 0 \leq V_{CC} \leq V_{CC} \ \mbox{(MAX)}, \ 0 \leq V_{CCIO} \leq V_{CCIO} \ \mbox{(MAX)} \ \mbox{and } 0 \leq V_{CCAUX} \leq V_{CCAUX} \ \mbox{(MAX)}. \end{array}$

3.I<sub>DK</sub> is additive to I<sub>PU.</sub> I<sub>PD</sub> or I<sub>BH</sub>.

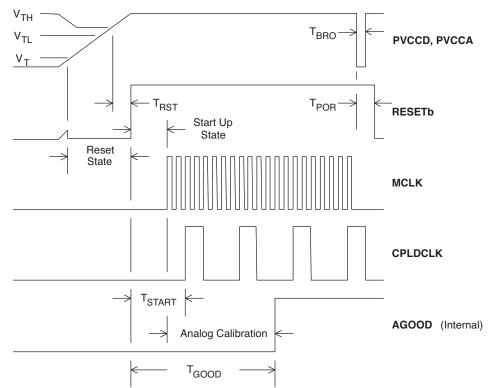

# **Power-On Reset – Power Management Section**

| Symbol             | Parameter                                                           | Conditions | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------------------------------------------|------------|------|------|------|-------|

| T <sub>RST</sub>   | Delay from V <sub>TH</sub> to start-up state                        |            |      |      | 100  | μs    |

| T <sub>START</sub> | Delay from RESETb HIGH to CPLDCLK<br>rising edge                    |            |      | 5    | 10   | μs    |

| T <sub>GOOD</sub>  | Power-on reset to valid VMON comparator<br>output and AGOOD is true |            |      |      | 2.5  | ms    |

| T <sub>BRO</sub>   | Minimum duration brown out required to trigger RESETb               |            | 1    |      | 5    | μs    |

| T <sub>POR</sub>   | Delay from brown out to reset state.                                |            |      |      | 13   | μs    |

| V <sub>TL</sub>    | Threshold below which RESETb is LOW <sup>1</sup>                    |            |      |      | 2.3  | V     |

| V <sub>TH</sub>    | Threshold above which RESETb is HIGH <sup>1</sup>                   |            | 2.7  |      |      | V     |

| V <sub>T</sub>     | Threshold above which RESETb is valid <sup>1</sup>                  |            | 0.8  |      |      | V     |

| CL                 | Capacitive load on RESETb for master/slave operation                |            |      |      | 200  | pF    |

1. Corresponds to PVCCA and PVCCD supply voltages.

#### Figure 2. Power Management Section Power-On Reset

## **ESD** Performance

| Pin Group | ESD Stress | Min. | Units |

|-----------|------------|------|-------|

| All pins  | HBM        | 1500 | V     |

|           | CDM        | 1000 | V     |

# DC Electrical Characteristics<sup>1, 2, 3, 4</sup>

| Symbol                       | Parameter                                                | Conditions                   | Typ.⁵ | Max. | Units |

|------------------------------|----------------------------------------------------------|------------------------------|-------|------|-------|

| P <sub>ICC</sub>             | Power Management section supply current                  | Normal operation             |       | 40   | mA    |

| PICCINP                      | Power Management section supply current                  | Normal operation             |       | 5    | mA    |

| P <sub>ICCJ</sub>            | Power Management section supply current                  | Normal operation             |       | 1    | mA    |

| I <sub>CC</sub> <sup>1</sup> | FPGA Core Power Supply                                   |                              | 8.7   |      | mA    |

| I <sub>CCAUX</sub>           | FPGA Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V | During initialization (0MHz) | 7     |      | mA    |

| I <sub>CCIO</sub>            | FPGA Bank Power Supply <sup>6</sup>                      | During initialization (0MHz) | 2.4   |      | mA    |

1. For further information on FPGA section supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all FPGA section I/O pins are held at  $V_{CCIO}$  or GND.

3. FPGA Frequency = 0 MHz.

4. Typical FPGA user pattern.

5.  $TJ = 25^{\circ}C$ , power supplies at nominal voltage.

6. Per bank,  $V_{CCIO}$  = 2.5V. Does not include pull-up/pull-down.

# FPGA Supply Current (Sleep Mode)<sup>1, 2</sup>

| Symbol                       | Parameter                      | Conditions | Typ. <sup>3</sup> | Max. | Units |

|------------------------------|--------------------------------|------------|-------------------|------|-------|

| I <sub>CC</sub> <sup>1</sup> | FPGA Core Power Supply         | Sleep Mode | 12                | 25   | μΑ    |

| I <sub>CCAUX</sub>           | FPGA Auxiliary Power Supply    |            | 1                 | 25   | μΑ    |

| I <sub>CCIO</sub>            | Bank Power Supply <sup>4</sup> |            | 2                 | 30   | μΑ    |

1. Assumes all inputs are configured as LVCMOS and held at the VCCIO or GND.

2. Frequency = 0MHz.

3.  $T_A = 25^{\circ}C$ , power supplies at nominal voltage.

4. Per bank.

# DC Electrical Characteristics – FPGA General Purpose I/O

| Symbol                              | Parameter                                | Condition                                                                                     | Min.                  | Тур. | Max.                  | Units |

|-------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I., I., 1, 4                        | Input or I/O Leakage                     | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                          | —                     | _    | 10                    | μA    |

| $I_{IL}$ , $I_{IH}$ <sup>1, 4</sup> | Input of I/O Leakage                     | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$                                                         | —                     | _    | 40                    | μA    |

| I <sub>PU</sub>                     | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                               | -30                   | _    | -150                  | μΑ    |

| I <sub>PD</sub>                     | I/O Active Pull-down Current             | $V_{IL} (MAX) \le V_{IN} \le V_{IH} (MAX)$                                                    | 30                    | _    | 150                   | μA    |

| I <sub>BHLS</sub>                   | Bus Hold Low sustaining current          | $V_{IN} = V_{IL}$ (MAX)                                                                       | 30                    | _    | —                     | μΑ    |

| I <sub>BHHS</sub>                   | Bus Hold High sustaining current         | $V_{IN} = 0.7 V_{CCIO}$                                                                       | -30                   | _    | —                     | μΑ    |

| I <sub>BHLO</sub>                   | Bus Hold Low Overdrive current           | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                               |                       | _    | 150                   | μA    |

| I <sub>BHHO</sub>                   | Bus Hold High Overdrive current          | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                               | —                     | _    | -150                  | μΑ    |

| V <sub>BHT</sub> <sup>3</sup>       | Bus Hold trip Points                     | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                               | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                  | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{IH} (MAX)$ | —                     | 8    | —                     | pf    |

| C2                                  | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{IH} (MAX)$ | —                     | 8    | —                     | pf    |

#### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25°C, f = 1.0MHz

Please refer to V<sub>IL</sub> and V<sub>IH</sub> in the sysIO Single-Ended DC Electrical Characteristics table of this document.

When V<sub>IH</sub> is higher than V<sub>CCIO</sub>, a transient current typically of 30ns in duration or less with a peak current of 6mA can occur on the high-tolow transition.

# Programming and Erase Supply Current<sup>1, 2, 3, 4</sup>

| Symbol             | Parameter                                                   | Typ.⁵ | Max. | Units |

|--------------------|-------------------------------------------------------------|-------|------|-------|

| I <sub>APS</sub>   | Power Management P <sub>VCCA/D</sub><br>Programming Current |       | 40   | mA    |

| I <sub>CC</sub>    | FPGA Core Power Supply                                      | 11    |      | mA    |

| I <sub>CCAUX</sub> | FPGA Auxiliary Power Supply<br>V <sub>CCAUX</sub> = 3.3V    | 10    |      | mA    |

| I <sub>CCIO</sub>  | FPGA Bank Power Supply <sup>6</sup>                         | 2     |      | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all I/O pins are held at V<sub>CCIO</sub> or GND.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

6. Per bank.  $V_{CCIO} = 2.5V$ . Does not include pull-up/pull-down.

## **Voltage Monitors**

| Symbol                    | Parameter                                           | Conditions | Min.  | Тур. | Max.  | Units |

|---------------------------|-----------------------------------------------------|------------|-------|------|-------|-------|

| R <sub>IN</sub>           | Input resistance                                    |            | 55    | 65   | 75    | kΩ    |

| C <sub>IN</sub>           | Input capacitance                                   |            |       | 8    |       | pF    |

| V <sub>MON</sub> Range    | Programmable trip-point range                       |            | 0.075 |      | 5.734 | V     |

| V <sub>Z</sub> Sense      | Near-ground sense threshold                         |            | 70    | 75   | 80    | mV    |

|                           | Absolute accuracy of any trip-point <sup>1</sup>    |            |       | 0.2  | 0.7   | %     |

| V <sub>MON</sub> Accuracy | Single-ended V <sub>MON</sub> pins <sup>2, 3</sup>  |            |       | 0.3  | 0.9   | %     |

| HYST                      | Hysteresis of any trip-point (relative to setting)  |            |       | 1    |       | %     |

| CMR                       | Common mode rejection                               |            |       | 60   |       | dB    |

| t <sub>PD16</sub>         | Propagation delay input to output glitch filter OFF |            |       | 16   |       | μs    |

| t <sub>PD64</sub>         | Propagation delay input to output glitch filter ON  |            |       | 64   |       | μs    |

1. Guaranteed by characterization across  $P_{VCCA}$  range, operating temperature, process.

Single-ended V<sub>MON</sub> inputs in 128-pin TQFP package only. Single-ended V<sub>MON</sub> input pins include: 59 (V<sub>MON1</sub>), 83 (V<sub>MON9</sub>), 84 (V<sub>MON10</sub>), 86 (V<sub>MON11</sub>), 88 (V<sub>MON12</sub>).

3. No adjacent digital I/O pin switching noise as described in the following table for single-ended V<sub>MON</sub> trip point error.

# Single-Ended Voltage Monitor Trip Point Error<sup>1</sup>

| Symbol                    | Parameter                                                                  | Conditions                                                                     | Min. | Тур. | Max. | Units |

|---------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|------|-------|

|                           | Single-ended trip point error (with adjacent switching noise) <sup>2</sup> | Pins 85, 87, 89<br>F <sub>SWITCH</sub> = 10MHz                                 |      | 2    |      | mV    |

| V <sub>MON</sub> Error SE | Single-ended trip point error (no adjacent switching noise) <sup>2</sup>   | Pins 85, 87, 89<br>F <sub>SWITCH</sub> = 0Hz;<br>All other digital I/O = 10MHz |      | 1    |      | mV    |

Single-ended V<sub>MON</sub> inputs in 128-pin TQFP package only. Affected single-ended V<sub>MON</sub> input pins only include: 83 (V<sub>MON9</sub>), 84 (V<sub>MON10</sub>), 86 (V<sub>MON11</sub>), and 88 (V<sub>MON12</sub>). Single-ended Vmon input pin 59 (V<sub>MON1</sub>) is not affected by adjacent switching noise.

Defined as TQFP package option adjacent digital I/O pins 85 (PR4B), 87 (PR3D) and 89 (PR2D) configured as outputs switching (F<sub>SWITCH</sub>) at 10MHz into a 33pF load capacitance.

# High Voltage FET Drivers

| Symbol               | Parameter                                  | Conditions                  | Min. | Тур. | Max. | Units |

|----------------------|--------------------------------------------|-----------------------------|------|------|------|-------|

|                      |                                            | 12V setting                 | 11.5 | 12   | 12.5 |       |

|                      | Cata driver eutout veltage                 | 10V setting                 | 9.6  | 10   | 10.4 | v     |

| V <sub>PP</sub>      | Gate driver output voltage                 | 8V setting                  | 7.7  | 8    | 8.3  | v     |

|                      |                                            | 6V setting                  | 5.8  | 6    | 6.2  | 1     |

|                      | Gate driver source current<br>(HIGH state) | Four settings in software   |      | 12.5 |      |       |

|                      |                                            |                             |      | 25   |      |       |

| OUTSRC               |                                            |                             |      | 50   |      | μΑ    |

|                      |                                            |                             |      | 100  |      |       |

|                      |                                            | FAST OFF mode               | 2000 | 3000 |      |       |

| I <sub>OUTSINK</sub> | Gate driver sink current                   |                             |      | 100  |      |       |

|                      | (LOW state)                                | Controlled ramp<br>settings |      | 250  |      | μΑ    |

|                      |                                            |                             |      | 500  |      | 1     |

# Margin/Trim DAC Output Characteristics

| Symbol           | Parameter                                              | Conditions                                                         | Min. | Тур.       | Max. | Units |

|------------------|--------------------------------------------------------|--------------------------------------------------------------------|------|------------|------|-------|

|                  | Resolution                                             |                                                                    |      | 8 (7+sign) |      | Bits  |

| FSR              | Full scale range                                       |                                                                    |      | +/-320     |      | mV    |

| LSB              | LSB step size                                          |                                                                    |      | 2.5        |      | mV    |

| I <sub>OUT</sub> | Output source/sink current                             |                                                                    | -200 |            | 200  | μA    |

|                  |                                                        | Offset 1                                                           |      | 0.6        |      |       |

| BPZ              | Bipolar zero output voltage<br>(code=80h)              | Offset 2                                                           |      | 0.8        |      | v     |

|                  |                                                        | Offset 3                                                           |      | 1.0        |      | v     |

|                  |                                                        | Offset 4                                                           |      | 1.25       |      |       |

| TS               | TrimCell output voltage settling                       | DAC code changed<br>from 80H to FFH or<br>80H to 00H               |      |            | 2.5  | ms    |

|                  | time <sup>1</sup>                                      | Single DAC code change                                             |      | 256        |      | μs    |

| C_LOAD           | Maximum load capacitance                               |                                                                    |      |            | 50   | pF    |

| TUPDATEM         | Update time through I <sup>2</sup> C port <sup>2</sup> | MCLK = 8 MHz                                                       |      | 260        |      | μs    |

| TOSE             | Total open loop supply voltage error <sup>3</sup>      | Full scale DAC corre-<br>sponds to ±5% supply<br>voltage variation | -1%  |            | +1%  | V/V   |

1. To 1% of set value with 50pf load connected to trim pins.

2. Total time required to update a single TRIMx output value by setting the associated DAC through the  $I^{2}C$  port.

This is the total resultant error in the trimmed power supply output voltage referred to any DAC code due to the DAC's INL, DNL, gain, output impedance, offset error and bipolar offset error across the industrial temperature range and the Platform Manager operating P<sub>VCCA</sub> and P<sub>VCCD</sub> ranges.

## **ADC Characteristics**

| Symbol               | Parameter               | Conditions                         | Min. | Тур.    | Max.             | Units |

|----------------------|-------------------------|------------------------------------|------|---------|------------------|-------|

|                      | ADC Resolution          |                                    |      | 10      |                  | Bits  |

| T <sub>CONVERT</sub> | Conversion Time         | Time from I <sup>2</sup> C Request |      |         | 200              | μs    |

|                      | Input range Full Scale  | Programmable Attenuator = 1        | 0    |         | 2.048            | V     |

| V <sub>IN</sub>      |                         | Programmable Attenuator = 3        | 0    |         | 5.9 <sup>1</sup> | V     |

| ADC Step Size        | LSB                     | Programmable Attenuator = 1        |      | 2       |                  | mV    |

| ADC Step Size        | LSB                     | Programmable Attenuator = 3        |      | 6       |                  | mV    |

| Eattenuator          | Error Due to Attenuator | Programmable Attenuator = 3        |      | +/- 0.1 |                  | %     |

1. Maximum voltage is limited by V<sub>MONX</sub> pin (theoretical maximum is 6.144V).

## ADC Error Budget Across Entire Operating Temperature Range

| Symbol     | Parameter                                                                                | Conditions                                                            | Min. | Тур.  | Max. | Units |

|------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|-------|------|-------|

|            |                                                                                          | Measurement Range 600 mV - 2.048V,<br>VMONxGS > -100mV, Attenuator =1 | -8   | +/-4  | 8    | mV    |

|            | Total Measurement Error at<br>Any Voltage (Differential Ana-<br>log Inputs) <sup>1</sup> | Measurement Range 600 mV - 2.048V,<br>VMONxGS > -200mV, Attenuator =1 |      | +/-6  |      | mV    |

| TADC Error |                                                                                          | Measurement Range 0 - 2.048V,<br>VMONxGS > -200mV, Attenuator =1      |      | +/-10 |      | mV    |

|            | Total Measurement Error at<br>Any Voltage (Single-Ended<br>Analog Inputs) <sup>2</sup>   | Measurement Range 600 mV - 2.048V,<br>Attenuator =1                   | -8   | +/-4  | 8    | mV    |

1. Total error, guaranteed by characterization, includes INL, DNL, Gain, Offset, and PSR specifications of the ADC.

Single-ended V<sub>MON</sub> inputs in 128-pin TQFP package only. Single-ended Vmon input pins include: 59 (VMON1), 83 (VMON9), 84 (VMON10), 86 (VMON11), 88 (VMON12).

# **Digital Specifications – Power Management Section Dedicated Inputs**

| Symbol                                                | Parameter                                                   | Conditions                                 | Min.                    | Тур. | Max.                    | Units |

|-------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------|-------------------------|------|-------------------------|-------|

| I <sub>IL</sub> ,I <sub>IH</sub>                      | Input leakage, no pull-up/pull-down                         |                                            |                         |      | +/-10                   | μA    |

| I <sub>PU</sub>                                       | Input pull-up current (PTMS, PTDI,<br>PTDISEL, PATDI, MCLK) |                                            |                         | 70   |                         | μΑ    |

| V <sub>IL</sub> Voltage input, logic low <sup>1</sup> | PTDI, PTMS, PATDI,<br>PTDISEL, 3.3V supply                  |                                            |                         | 0.8  |                         |       |

|                                                       | Voltage input, logic low <sup>1</sup>                       | PTDI, PTMS, PATDI,<br>PTDISEL, 2.5V supply |                         |      | 0.7                     | v     |

|                                                       |                                                             | SCL, SDA                                   |                         |      | 30% P <sub>VCCD</sub>   |       |

|                                                       |                                                             | IN[1:4]                                    |                         |      | 30% P <sub>VCCINP</sub> |       |

|                                                       |                                                             | PTDI, PTMS, PATDI,<br>PTDISEL, 3.3V supply | 2.0                     |      |                         |       |

| V <sub>IH</sub> Voltage inpu                          | Voltage input, logic high <sup>1</sup>                      | PTDI,P TMS, PATDI,<br>PTDISEL, 2.5V supply | 1.7                     |      |                         | V     |

|                                                       |                                                             | SCL, SDA                                   | 70% P <sub>VCCD</sub>   |      | P <sub>VCCD</sub>       |       |

|                                                       |                                                             | IN[1:4]                                    | 70% P <sub>VCCINP</sub> |      | P <sub>VCCINP</sub>     |       |

**Over Recommended Operating Conditions**

1. SCL, SDA referenced to P<sub>VCCD</sub>; IN[1:4] referenced to P<sub>VCCINP</sub>; PTDO, PTDI, PTMS, PATDI, PTDISEL referenced to P<sub>VCCJ</sub>.

### **Digital Specifications – Power Management Section Dedicated Outputs**

| Symbol                | Parameter                     | Conditions                                               | Min. | Тур. | Max.                    | Units |

|-----------------------|-------------------------------|----------------------------------------------------------|------|------|-------------------------|-------|

| I <sub>OH-HVOUT</sub> | Output leakage current        | HVOUT[1:4] in open<br>drain mode and pulled<br>up to 12V |      | 35   | 100                     | μΑ    |

| V <sub>OL</sub>       | HVOUT[1:4] (open drain mode), | I <sub>SINK</sub> = 10mA                                 |      |      | 0.8                     | V     |

|                       | OUT[5:16]                     | I <sub>SINK</sub> = 20mA                                 |      |      | 0.8                     |       |

|                       | PTDO, MCLK, CPLDCLK, SDA      | I <sub>SINK</sub> = 4mA                                  |      |      | 0.4                     |       |

| V <sub>OH</sub>       | PTDO, MCLK, CPLDCLK           | I <sub>SRC</sub> = 4mA                                   |      |      | P <sub>VCCD</sub> - 0.4 | V     |

| ISINKTOTAL            | All digital outputs           |                                                          |      |      | 130                     | mA    |

#### **Over Recommended Operating Conditions**

## sysIO Recommended Operating Conditions

|            | V <sub>CCIO</sub> (V) |      |       |  |  |  |

|------------|-----------------------|------|-------|--|--|--|

| Standard   | Min.                  | Тур. | Max.  |  |  |  |

| LVCMOS 3.3 | 3.135                 | 3.3  | 3.465 |  |  |  |

| LVCMOS 2.5 | 2.375                 | 2.5  | 2.625 |  |  |  |

| LVCMOS 1.8 | 1.71                  | 1.8  | 1.89  |  |  |  |

| LVCMOS 1.5 | 1.425                 | 1.5  | 1.575 |  |  |  |

| LVCMOS 1.2 | 1.14                  | 1.2  | 1.26  |  |  |  |

| LVTTL      | 3.135                 | 3.3  | 3.465 |  |  |  |

## sysIO Single-Ended DC Electrical Characteristics

| Input/Output            |          | V <sub>IL</sub>       | V <sub>IH</sub>       |          | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.    |              | I <sub>OH</sub> <sup>1</sup> |

|-------------------------|----------|-----------------------|-----------------------|----------|----------------------|-------------------------|--------------|------------------------------|

| Standard                | Min. (V) | Max. (V)              | Min. (V)              | Max. (V) | (V)                  | (V)                     | (mĂ)         | (mÅ)                         |

| LVCMOS 3.3              | -0.3     | 0.8                   | 2.0                   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 16, 12, 8, 4 | -14, -12, -8, -4             |

| 2000000.0               | -0.0     | 0.0                   | 2.0                   | 0.0      | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

|                         |          |                       |                       |          | 0.4                  | 2.4                     | 16           | -16                          |

| LVTTL                   | -0.3     | 0.8                   | 2.0                   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 12, 8, 4     | -12, -8, -4                  |

|                         |          |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 2.5              | -0.3     | 0.7                   | 1.7                   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 16, 12, 8, 4 | -14, -12, -8, -4             |

| 2001003 2.5             | -0.5     | 0.7                   | 1.7                   | 5.0      | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.8 <sup>2</sup> | -0.3     | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 16, 12, 8, 4 | -14, -12, -8, -4             |

|                         | -0.5     | 0.00 0.00             | 0.03 4 CCIO           | 0.0      | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.5 <sup>2</sup> | -0.3     | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 8, 4         | -8, -4                       |

|                         | -0.5     | 0.32 A CCIO           | 0.03 v CCIO           | 5.0      | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.2 <sup>2</sup> | -0.3     | 0.42                  | 0.78                  | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 6, 2         | -6, -2                       |

|                         | -0.3     | 0.42                  | 0.70                  | 5.0      | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

1. The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

2. Lower voltage operation not supported for VCCIO2 bank pins.

## sysIO Differential Electrical Characteristics

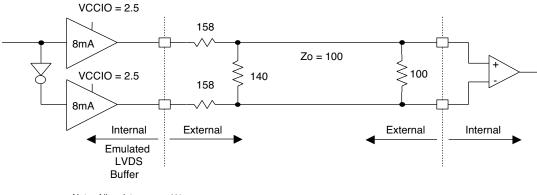

## **LVDS Emulation**

FPGA section outputs can support LVDS outputs via emulation (LVDS25E), in addition to the LVDS support that is available. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3 is one possible solution for LVDS standard implementation. Resistor values in Figure 3 are industry standard values for 1% resistors.

#### Figure 3. LVDS Using External Resistors (LVDS25E)

Note: All resistors are ±1%.

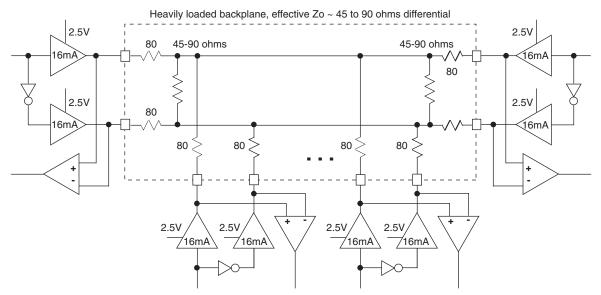

### **BLVDS Emulation**

FPGA outputs support the BLVDS standard through emulation. The output is emulated using complementary LVC-MOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 4 is one possible solution for bi-directional multi-point differential signals.

#### Figure 4. BLVDS Multi-point Output Example

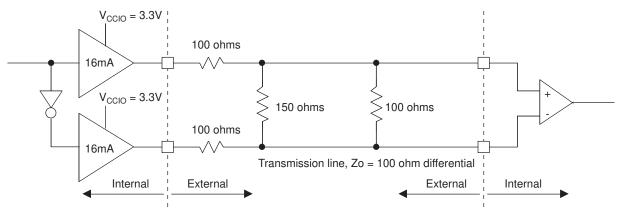

### LVPECL Emulation

FPGA outputs support the differential LVPECL standard through emulation. This output standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs on all the devices. The scheme shown in Figure 5 is one possible solution for point-to-point signals.

#### Figure 5. Differential LVPECL

For further information on LVPECL, BLVDS and other differential interfaces please see details of additional technical documentation at the end of the data sheet.

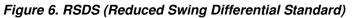

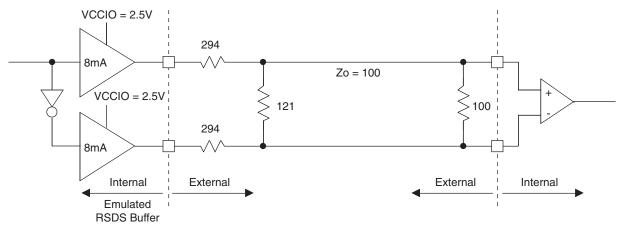

#### **RSDS Emulation**

FPGA outputs support the differential RSDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs on all the devices. The scheme shown in Figure 6 is one possible solution for RSDS standard implementation. Use LVDS25E mode with suggested resistors for RSDS operation. Resistor values in Figure 6 are industry standard values for 1% resistors.

## **Oscillator Transient Characteristics**

**Over Recommended Operating Conditions**

| Symbol               | Parameter                                                       | Conditions              | Min. | Тур. | Max. | Units |

|----------------------|-----------------------------------------------------------------|-------------------------|------|------|------|-------|

| f <sub>CLK</sub>     | Power Management inter-<br>nal master clock frequency<br>(MCLK) |                         | 7.6  | 8    | 8.4  | MHz   |

| fclkext              | Power Management exter-<br>nally applied master clock<br>(MCLK) |                         | 7.2  |      | 8.8  | MHz   |

| f <sub>PLDCLK</sub>  | CPLDCLK output frequency                                        | f <sub>CLK</sub> = 8MHz |      | 250  |      | kHz   |

| f <sub>FPGACLK</sub> | FPGA internal master clock<br>frequency                         |                         | 18   |      | 26   | MHz   |

## **Power Management CPLD Timer Transient Characteristics**

| Symbol        | Parameter                                          | Conditions              | Min.  | Тур. | Max.  | Units |

|---------------|----------------------------------------------------|-------------------------|-------|------|-------|-------|

| Timeout Range | Range of programmable timers (128 steps)           | f <sub>CLK</sub> = 8MHz | 0.032 |      | 1966  | ms    |

| Resolution    | Spacing between available adjacent timer intervals |                         |       |      | 13    | %     |

| Accuracy      | Timer accuracy                                     | f <sub>CLK</sub> = 8MHz | -6.67 |      | -12.5 | %     |

## Power Management I<sup>2</sup>C Port Characteristics

|                             |                                                 | 100  | KHz              | 400  | KHz              |       |

|-----------------------------|-------------------------------------------------|------|------------------|------|------------------|-------|

| Symbol                      | Definition                                      | Min. | Max.             | Min. | Max.             | Units |

| F <sub>I<sup>2</sup>C</sub> | I <sup>2</sup> C clock/data rate                |      | 100 <sup>1</sup> |      | 400 <sup>1</sup> | KHz   |

| T <sub>SU;STA</sub>         | After start                                     | 4.7  |                  | 0.6  |                  | us    |

| T <sub>HD;STA</sub>         | After start                                     | 4    |                  | 0.6  |                  | us    |

| T <sub>SU;DAT</sub>         | Data setup                                      | 250  |                  | 100  |                  | ns    |

| T <sub>SU;STO</sub>         | Stop setup                                      | 4    |                  | 0.6  |                  | us    |

| T <sub>HD;DAT</sub>         | Data hold; SCL= Vih_min = 2.1V                  | 0.3  | 3.45             | 0.3  | 0.9              | us    |

| T <sub>LOW</sub>            | Clock low period                                | 4.7  |                  | 1.3  |                  | us    |

| T <sub>HIGH</sub>           | Clock high period                               | 4    |                  | 0.6  |                  | us    |

| Τ <sub>F</sub>              | Fall time; 2.25V to 0.65V                       |      | 300              |      | 300              | ns    |

| T <sub>R</sub>              | Rise time; 0.65V to 2.25V                       |      | 1000             |      | 300              | ns    |

| T <sub>TIMEOUT</sub>        | Detect clock low timeout                        | 25   | 35               | 25   | 35               | ms    |

| T <sub>POR</sub>            | Device must be operational after power-on reset | 500  |                  | 500  |                  | ms    |

| T <sub>BUF</sub>            | Bus free time between stop and start condition  | 4.7  |                  | 1.3  |                  | us    |

If F<sub>I<sup>2</sup>C</sub> is less than 50kHz, then the ADC DONE status bit is not guaranteed to be set after a valid conversion request is completed. In this case, waiting for the T<sub>CONVERT</sub> minimum time after a convert request is made is the only way to guarantee a valid conversion is ready for readout. When F<sub>I2C</sub> is greater than 50kHz, ADC conversion complete is ensured by waiting for the DONE status bit.

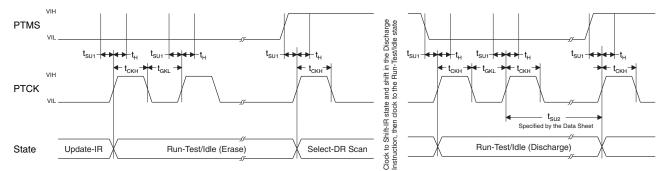

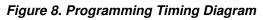

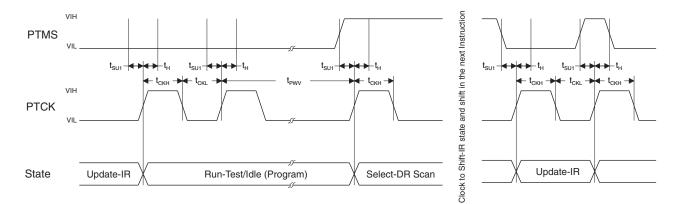

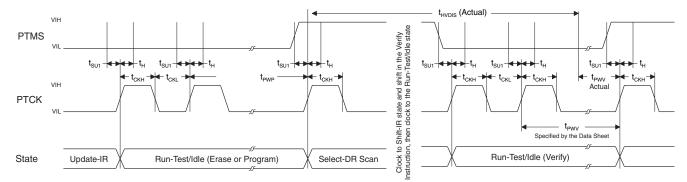

# **Timing for Power Management JTAG Operations**

| Symbol              | Parameter                            | Conditions | Min. | Тур. | Max. | Units |

|---------------------|--------------------------------------|------------|------|------|------|-------|

| t <sub>ISPEN</sub>  | Program enable delay time            |            | 10   | —    | —    | μs    |

| t <sub>ISPDIS</sub> | Program disable delay time           |            | 30   | —    | —    | μs    |

| t <sub>HVDIS</sub>  | High voltage discharge time, program |            | 30   | —    | _    | μs    |

| t <sub>HVDIS</sub>  | High voltage discharge time, erase   |            | 200  | —    | —    | μs    |

| t <sub>CEN</sub>    | Falling edge of PTCK to PTDO active  |            | —    | —    | 15   | ns    |

| t <sub>CDIS</sub>   | Falling edge of PTCK to PTDO disable |            | —    | —    | 15   | ns    |

| t <sub>SU1</sub>    | Setup time                           |            | 5    | —    | —    | ns    |

| t <sub>H</sub>      | Hold time                            |            | 10   | —    | —    | ns    |

| t <sub>СКН</sub>    | PTCK clock pulse width, high         |            | 20   | —    | —    | ns    |

| t <sub>CKL</sub>    | PTCK clock pulse width, low          |            | 20   | —    | —    | ns    |

| f <sub>MAX</sub>    | Maximum PTCK clock frequency         |            | —    | —    | 25   | MHz   |

| t <sub>CO</sub>     | Falling edge of PTCK to valid output |            | —    | —    | 15   | ns    |

| t <sub>PWV</sub>    | Verify pulse width                   |            | 30   | —    | —    | μs    |

| t <sub>PWP</sub>    | Programming pulse width              |            | 20   | —    | —    | ms    |

Figure 7. Erase (User Erase or Erase All) Timing Diagram

### Figure 9. Verify Timing Diagram

#### Figure 10. Discharge Timing Diagram

## **Typical FPGA Building Block Function Performance**<sup>1</sup>

### Pin-to-Pin Performance (LVCMOS25 12mA Drive)

| Function        | Timing | Units |

|-----------------|--------|-------|

| Basic Functions |        |       |

| 16-bit decoder  | 6.7    | ns    |

| 4:1 MUX         | 4.5    | ns    |

| 16:1 MUX        | 5.1    | ns    |

#### **Register-to-Register Performance**

| Function                     | Timing | Units |

|------------------------------|--------|-------|

| Basic Functions              |        |       |

| 16:1 MUX                     | 487    | MHz   |

| 16-bit adder                 | 292    | MHz   |

| 16-bit counter               | 388    | MHz   |

| 64-bit counter               | 200    | MHz   |

| Distributed Memory Functions |        |       |

| 16x2 Single Port RAM         | 434    | MHz   |

| 64x2 Single Port RAM         | 320    | MHz   |

| 128x4 Single Port RAM        | 261    | MHz   |

| 32x2 Pseudo-Dual Port RAM    | 314    | MHz   |

| 64x4 Pseudo-Dual Port RAM    | 271    | MHz   |

1. The above timing numbers are generated using the Platform Manager design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

Rev. A 0.19

# **Derating Logic Timing**

Logic Timing provided in the following sections of the data sheet and the Platform Manager design tool are worst case numbers in the operating range. Actual delays may be much faster. The Platform Manager design tool from Lattice can provide FPGA logic timing numbers at a particular temperature and voltage.

# **FPGA Section External Switching Characteristics**<sup>1</sup>

#### **Over Recommended Operating Conditions**

| Parameter             | Description                                                             | Min. | Max. | Units |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------|------|------|-------|--|--|--|--|

| General I/O Pin       | eneral I/O Pin Parameters (Using Global Clock without PLL) <sup>1</sup> |      |      |       |  |  |  |  |

| t <sub>PD</sub>       | Best Case t <sub>PD</sub> Through 1 LUT                                 | —    | 4.9  | ns    |  |  |  |  |

| t <sub>CO</sub>       | Best Case Clock to Output - From PFU                                    | —    | 5.7  | ns    |  |  |  |  |

| t <sub>SU</sub>       | Clock to Data Setup - To PFU                                            | 1.5  | —    | ns    |  |  |  |  |

| t <sub>H</sub>        | Clock to Data Hold - To PFU                                             | -0.1 | —    | ns    |  |  |  |  |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and PFU Register                                 | —    | 500  | MHz   |  |  |  |  |

| t <sub>SKEW_PRI</sub> | Global Clock Skew Across Device                                         | —    | 240  | ps    |  |  |  |  |

1. General timing numbers based on LVCMOS2.5V, 12 mA. Rev. A 0.19

# **FPGA Sleep Mode Timing**

| Parameter            | Description              | Min. | Max. | Units |

|----------------------|--------------------------|------|------|-------|

| t <sub>PWRDN</sub>   | SLEEPN Low to Power Down | —    | 400  | ns    |

| t <sub>PWRUP</sub>   | SLEEPN High to Power Up  | —    | 600  | μs    |

| t <sub>WSLEEPN</sub> | SLEEPN Pulse Width       | 400  | —    | ns    |

| t <sub>WAWAKE</sub>  | SLEEPN Pulse Rejection   | —    | 100  | ns    |

# **FPGA Section Internal Timing Parameters**<sup>1</sup>

| <b>Over Recommended</b> | <b>Operating Conditions</b> |

|-------------------------|-----------------------------|

|-------------------------|-----------------------------|

| Parameter               | Description                                     | Min.  | Max. | Units |

|-------------------------|-------------------------------------------------|-------|------|-------|

| PFU/PFF Log             | jic Mode Timing                                 |       |      | I     |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F output)          | —     | 0.39 | ns    |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)        | —     | 0.62 | ns    |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU                      | _     | 1.26 | ns    |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) input setup time           | 0.15  | —    | ns    |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) input hold time            | -0.07 | —    | ns    |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                     | 0.18  | —    | ns    |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                      | -0.04 | —    | ns    |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, D-type register configuration | _     | 0.56 | ns    |

| t <sub>LE2Q_PFU</sub>   | Clock to Q delay latch configuration            | —     | 0.74 | ns    |

| t <sub>LD2Q_PFU</sub>   | D to Q throughput delay when latch is enabled   | —     | 0.77 | ns    |

| PFU Dual Po             | rt Memory Mode Timing                           |       |      |       |

| t <sub>CORAM_PFU</sub>  | Clock to Output                                 | —     | 0.56 | ns    |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                 | -0.25 | —    | ns    |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                  | 0.39  | —    | ns    |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                              | -0.65 |      | ns    |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                               | 0.99  | —    | ns    |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                    | -0.30 | —    | ns    |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                     | 0.47  | —    | ns    |

| PIO Input/Ou            | tput Buffer Timing                              |       | •    | •     |

| t <sub>IN_PIO</sub>     | Input Buffer Delay                              | _     | 1.06 | ns    |

| tout_pio                | Output Buffer Delay                             | —     | 1.80 | ns    |

1. Internal parameters are characterized but not tested on every device.

Rev. A 0.19

# FPGA Section Timing Adders<sup>1, 2, 3</sup>

#### **Over Recommended Operating Conditions**

| Buffer Type      | Description           |       | Units |

|------------------|-----------------------|-------|-------|

| Input Adjusters  |                       |       |       |

| LVTTL33          | LVTTL                 | 0.01  | ns    |

| LVCMOS33         | LVCMOS 3.3            | 0.01  | ns    |

| LVCMOS25         | LVCMOS 2.5            | 0.00  | ns    |

| LVCMOS18         | LVCMOS 1.8            | 0.10  | ns    |

| LVCMOS15         | LVCMOS 1.5            | 0.19  | ns    |

| LVCMOS12         | LVCMOS 1.2            | 0.56  | ns    |

| Output Adjusters |                       |       |       |

| LVTTL33_4mA      | LVTTL 4mA drive       | 0.05  | ns    |

| LVTTL33_8mA      | LVTTL 8mA drive       | 0.08  | ns    |

| LVTTL33_12mA     | LVTTL 12mA drive      | -0.01 | ns    |

| LVTTL33_16mA     | LVTTL 16mA drive      | 0.70  | ns    |

| LVCMOS33_4mA     | LVCMOS 3.3 4mA drive  | 0.05  | ns    |

| LVCMOS33_8mA     | LVCMOS 3.3 8mA drive  | 0.08  | ns    |

| LVCMOS33_12mA    | LVCMOS 3.3 12mA drive | -0.01 | ns    |

| LVCMOS33_14mA    | LVCMOS 3.3 14mA drive | 0.70  | ns    |

| LVCMOS25_4mA     | LVCMOS 2.5 4mA drive  | 0.07  | ns    |

| LVCMOS25_8mA     | LVCMOS 2.5 8mA drive  | 0.13  | ns    |

| LVCMOS25_12mA    | LVCMOS 2.5 12mA drive | 0.00  | ns    |

| LVCMOS25_14mA    | LVCMOS 2.5 14mA drive | 0.47  | ns    |

| LVCMOS18_4mA     | LVCMOS 1.8 4mA drive  | 0.15  | ns    |

| LVCMOS18_8mA     | LVCMOS 1.8 8mA drive  | 0.06  | ns    |

| LVCMOS18_12mA    | LVCMOS 1.8 12mA drive | -0.08 | ns    |

| LVCMOS18_14mA    | LVCMOS 1.8 14mA drive | 0.09  | ns    |

| LVCMOS15_4mA     | LVCMOS 1.5 4mA drive  | 0.22  | ns    |

| LVCMOS15_8mA     | LVCMOS 1.5 8mA drive  | 0.07  | ns    |

| LVCMOS12_2mA     | LVCMOS 1.2 2mA drive  | 0.36  | ns    |

| LVCMOS12_6mA     | LVCMOS 1.2 6mA drive  | 0.07  | ns    |

Timing adders are characterized but not tested on every device.

LVCMOS timing is measured with the load specified in Switching Test Conditions table.

All other standards tested according to the appropriate specifications.

Rev. A 0.19

## Flash Download Time

| Symbol               | Parameter                                                  | Min. | Тур. | Max. | Units |

|----------------------|------------------------------------------------------------|------|------|------|-------|

| t <sub>REFRESH</sub> | V <sub>CC</sub> or V <sub>CCAUX</sub> to Device I/O Active | _    | _    | 0.6  | ms    |

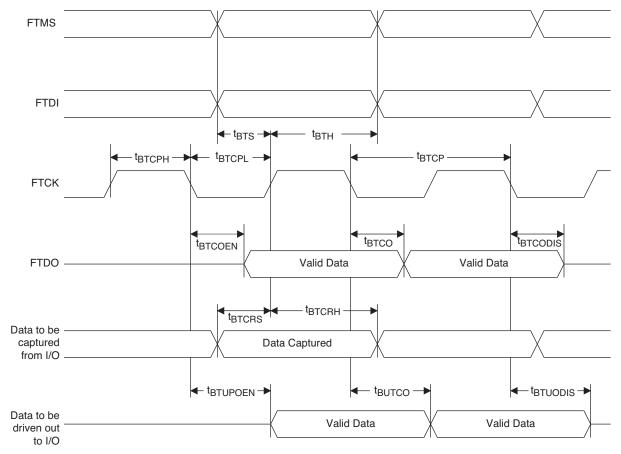

# **FPGA JTAG Port Timing Specifications**

| Symbol               | Parameter                                                            | Min.     | Max. | Units |

|----------------------|----------------------------------------------------------------------|----------|------|-------|

| f <sub>MAX</sub>     | FTCK [BSCAN] clock frequency                                         | —        | 25   | MHz   |

| t <sub>BTCP</sub>    | FTCK [BSCAN] clock pulse width                                       | 40       | —    | ns    |

| t <sub>BTCPH</sub>   | FTCK [BSCAN] clock pulse width high                                  | 20       |      | ns    |

| t <sub>BTCPL</sub>   | FTCK [BSCAN] clock pulse width low                                   | 20       |      | ns    |

| t <sub>BTS</sub>     | FTCK [BSCAN] setup time                                              | 8        |      | ns    |

| t <sub>BTH</sub>     | FTCK [BSCAN] hold time                                               | 10       | —    | ns    |

| t <sub>BTRF</sub>    | FTCK [BSCAN] rise/fall time                                          | 50       | —    | mV/ns |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to output valid                 | —        | 10   | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to output disabled              | —        | 10   | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to output enabled               | —        | 10   | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                               | 8        |      | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                                | 25       |      | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to output valid    | —        | 25   | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to output disabled | —        | 25   | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to output enabled  | <u> </u> | 25   | ns    |

| Rev. A 0.19          |                                                                      | •        | •    |       |

Rev. A 0.19

Figure 11. FPGA JTAG Port Timing Waveforms

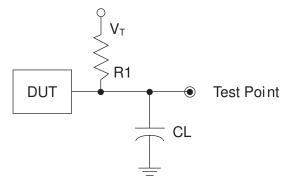

## **FPGA Output Switching Test Conditions**

Figure 12 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 2.

#### Figure 12. Output Test Load, LVTTL and LVCMOS Standards

Table 2. Test Fixture Required Components, Non-Terminated Interfaces

| Test Condition                             | R <sub>1</sub> | CL  | Timing Ref.                       | VT              |

|--------------------------------------------|----------------|-----|-----------------------------------|-----------------|

|                                            |                | 0pF | LVTTL, LVCMOS 3.3 = 1.5V          |                 |

|                                            |                |     | LVCMOS 2.5 = V <sub>CCIO</sub> /2 |                 |

| LVTTL and LVCMOS settings (L -> H, H -> L) | ×              |     | LVCMOS 1.8 = V <sub>CCIO</sub> /2 |                 |

|                                            |                |     | LVCMOS 1.5 = $V_{CCIO}/2$         | _               |

|                                            |                |     | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | _               |

| LVTTL and LVCMOS 3.3 (Z -> H)              |                |     | 1.5                               | V <sub>OL</sub> |

| LVTTL and LVCMOS 3.3 (Z -> L)              |                | 0pF | 1.5                               | V <sub>OH</sub> |

| Other LVCMOS (Z -> H)                      | 188            |     | V <sub>CCIO</sub> /2              | V <sub>OL</sub> |

| Other LVCMOS (Z -> L)                      | 100            | opi | V <sub>CCIO</sub> /2              | V <sub>OH</sub> |

| LVTTL + LVCMOS (H -> Z)                    |                |     | V <sub>OH</sub> - 0.15            | V <sub>OL</sub> |

| LVTTL + LVCMOS (L -> Z)                    |                |     | V <sub>OL</sub> - 0.15            | V <sub>OH</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.