# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

| SHARP                                                                                                                 | No. LD-25258A          |

|-----------------------------------------------------------------------------------------------------------------------|------------------------|

|                                                                                                                       | DATE 14-Feb-13<br>REV. |

| TECHNICAL LIT                                                                                                         | TERATURE               |

| FOR                                                                                                                   |                        |

| TFT - LCD n                                                                                                           | nodule                 |

| MODEL NO. LQ043                                                                                                       | <u>T1DG29</u>          |

| These parts have corresponded wit                                                                                     | th the RoHS directive. |

| The technical literature is subject to<br>So, please contact SHARP or its rep<br>designing your product based on this | presentative before    |

| DISPLY DEVICE<br>SHARP CORPOI                                                                                         |                        |

# **RECORDS OF REVISION**

# LQ043T1DG29

|           |           | REVI      |      |         |      |

|-----------|-----------|-----------|------|---------|------|

| SPEC No.  | DATE      | SED<br>No | PAGE | SUMMARY | NOTE |

| LD-25258A | 2013/2/14 |           |      | _       |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           | 1         |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           |           |           |      |         |      |

|           | ļ         |           |      |         |      |

|           |           |           |      |         |      |

#### NOTICE

This technical literature is the proprietary of SHARP and is copyrighted, with all rights reserved. Under the copyright laws, no part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical for any purpose, in whole or in part, without the express written permission of SHARP. Express written permission is also required before any use of this technical literature may be made by a third party.

The application circuit examples in this technical literature are provided to explain the representative applications of SHARP's devices and are not intended to guarantee any circuit design or permit any industrial property right or other rights to be executed. SHARP takes no responsibility for any problems related to any industrial property right or a third party resulting from the use of SHARP's devices, except for those resulting directly from device manufacturing processes.

In case of using the device for application such as control and safety equipment for transportation (controls of aircraft, trains, automobiles, etc), rescue and security equipment and various safety related equipment which require higher reliability and safety, take into consideration that appropriate measures such as fail-safe function and redundant system design should be taken.

Do not use the device for equipment that requires an extreme level or reliability, such as aerospace applications, telecommunication equipment (trunk lines), nuclear power control equipment and medical or other equipment for life support.

SHARP assumes no responsibility for any damage resulting from the use of the device which does not comply with the instructions and the precautions specified in this technical literature.

Contact and consult with a SHARP representative for any questions about this device.

#### 1. Applicable Scope

This technical literature is applicable to TFT-LCD Module "LQ043T1DG29".

#### 2. General Description

This module is a color active matrix LCD module incorporating amorphous silicon TFT (Thin Film Transistor). It is composed of a color TFT-LCD panel, driver IC, Input FPC, a back light unit and touch panel. Graphics and texts can be displayed on a 480 x 272 x RGB dots panel with about 262k colors by supplying 18bit data signals (6bit x RGB), four timing signals, 3wires 24bit serial interface signals, logic (Typ. +3.3V), analog (Typ. +3.3V) supply voltages for TFT-LCD panel driving and supply voltage for back light.

#### 3. Mechanical (Physical) Technical literatures

| Item                    | Specifications                 | Unit  |

|-------------------------|--------------------------------|-------|

| Screen size             | 10.9 (4.3" type) diagonal      | cm    |

| Active area             | 95.04 (H) × 53.856 (V)         | mm    |

|                         | 480 (H) x 272 (V)              | pixel |

| Pixel format            | 1Pixel =R+G+B dots             | -     |

| Pixel pitch             | 0.198 (H) x 0.198 (V)          | mm    |

| Pixel configuration     | R,G,B horizontal stripes       | -     |

| Display mode            | Normally white                 | -     |

| Unit outline dimensions | 105.5 (W) x 67.2 (H) x 3.1 (D) | mm    |

| Mass                    | About 36                       | g     |

| Surface hardness        | 2H                             | _     |

| Surface treatment       | Anti glare                     | _     |

%The above-mentioned table indicates module sizes without some projections and FPC.

For detailed measurements and tolerances, please refer to 18. Outline Dimensions.

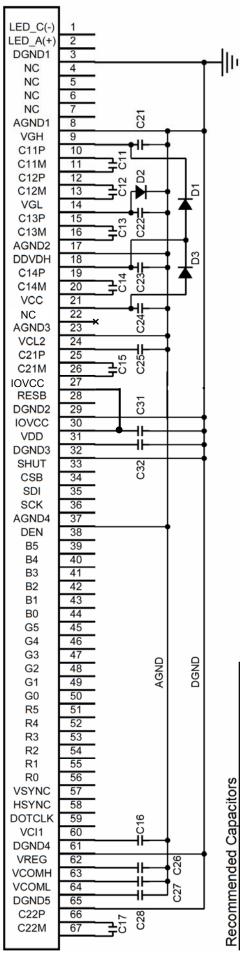

## 4. Input Terminal Names and Functions

## Recommendation CN : [HIROSE] FH26G-67S-0.3SHBW(05) or [KYOCERA ELCO] 00 6281 067 2X2 829 +

| Pin No | Symbol    | I/O | Description                            | Remarks  |

|--------|-----------|-----|----------------------------------------|----------|

| 1      | LED_C (-) | -   | Power supply for LED (Cathode)         |          |

| 2      | LED_0(+)  |     | Power supply for LED (Anode)           |          |

| 3      | DGND1     | _   | Digital Ground                         |          |

| 4      | NC        | -   | No connection                          |          |

| 5      | NC        | -   | No connection                          |          |

| 6      | NC        |     | No connection                          |          |

| 7      | NC        | -   | No connection                          |          |

| 8      | AGND1     | -   | Analog Ground                          |          |

| 9      | VGH       | -   | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 10     | C11P      | -   | Connect a Booster capacitor to C11M    | Note 4-1 |

| 11     | C11M      |     | Connect a Booster capacitor to C11P    | Note 4-1 |

| 12     | C12P      | _   | Connect a Booster capacitor to C12M    | Note 4-1 |

| 13     | C12M      | -   | Connect a Booster capacitor to C12P    | Note 4-1 |

| 14     | VGL       |     | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 15     | C13P      | _   | Connect a Booster capacitor to C13M    | Note 4-1 |

| 16     | C13M      |     | Connect a Booster capacitor to C13P    | Note 4-1 |

| 17     | AGND2     |     | Analog Ground                          |          |

| 18     | DDVDH     | -   | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 19     | C14P      |     | Connect a Booster capacitor to C14M    | Note 4-1 |

| 20     | C14M      |     | Connect a Booster capacitor to C14P    | Note 4-1 |

| 21     | VCC       |     | Booster input voltage pin              |          |

| 22     | NC        |     | No connection                          |          |

| 23     | AGND3     | -   | Analog Ground                          |          |

| 24     | VCL2      | -   | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 25     | C21P      |     | Connect a Booster capacitor to C21M    | Note 4-1 |

| 26     | C21M      |     | Connect a Booster capacitor to C21P    | Note 4-1 |

| 27     | IOVCC     |     | Voltage input pin for logic I/O        | Note 4-1 |

| 28     | RESB      | 1   | System reset                           |          |

| 29     | DGND2     | -   | Digital Ground                         |          |

| 30     | IOVCC     | _   | Voltage input pin for logic I/O        |          |

| 31     | VDD       | -   | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 32     | DGND3     |     | Digital Ground                         |          |

| 33     | SHUT      |     | Sleep mode control                     |          |

| 34     | CSB       |     | Chip select pin of serial interface    |          |

| 35     | SDI       |     | Data input pin in serial mode          |          |

| 36     | SCK       |     | Clock input pin in serial mode         |          |

| 37     | AGND4     |     | Analog Ground                          | Note 4-1 |

| 38     | DEN       |     | Display enable signal                  |          |

| 39     | B5        |     | BLUE data signal(MSB)                  |          |

| 40     | B3<br>B4  |     | BLUE data signal                       |          |

|        |           | 1   |                                        |          |

| 41     | B3        |     | BLUE data signal                       |          |

|         |        |                                          |                                        | LD-252   |

|---------|--------|------------------------------------------|----------------------------------------|----------|

| Pin No. | Symbol | I/O                                      | Description                            | Remarks  |

| 42      | B2     | I                                        | BLUE data signal                       |          |

| 43      | B1     | I                                        | BLUE data signal                       |          |

| 44      | B0     | I                                        | BLUE data signal(LSB)                  |          |

| 45      | G5     | Ι                                        | GREEN data signal(MSB)                 |          |

| 46      | G4     | Ι                                        | GREEN data signal                      |          |

| 47      | G3     | Ι                                        | GREEN data signal                      |          |

| 48      | G2     | Ι                                        | GREEN data signal                      |          |

| 49      | G1     | Ι                                        | GREEN data signal                      |          |

| 50      | G0     | I                                        | GREEN data signal(LSB)                 |          |

| 51      | R5     | Ι                                        | RED data signal(MSB)                   |          |

| 52      | R4     | Ι                                        | RED data signal                        |          |

| 53      | R3     | I                                        | RED data signal                        |          |

| 54      | R2     |                                          | RED data signal                        |          |

| 55      | R1     | I                                        | RED data signal                        |          |

| 56      | R0     |                                          | RED data signal(LSB)                   |          |

| 57      | VSYNC  | I                                        | Frame synchronization signal           |          |

| 58      | HSYNC  | I                                        | Line synchronization signal            |          |

| 59      | DOTCLK |                                          | Dot-clock signal                       |          |

| 60      | VCI1   | -                                        | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 61      | DGND4  | -                                        | Digital Ground                         |          |

| 62      | VREG   | -                                        | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 63      | VCOMH  | -                                        | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 64      | VCOML  | -                                        | Connect a Stabilizing capacitor to GND | Note 4-1 |

| 65      | DGND5  | -                                        | Digital Ground                         |          |

| 66      | C22P   | 2P - Connect a Booster capacitor to C22M |                                        | Note 4-1 |

| 67      | C22M   | -                                        | Connect a Booster capacitor to C22P    | Note 4-1 |

Recommended Capacitors

| Temperature<br>Characteristic | B(JIS) or X5R(EIA) | nA@25°C, VR≧25V      | nA@25°C, VR≧25V                    | <0.38V/5mA@25°C, VR≧25V |

|-------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------------|------------------------------------|-------------------------|

| Rated Voltage                 | 6.3 V              | 6.3 V              | 6.3 V              | 0.3 V              | 10 V               | 6.3 V              | 10 V               | 25 V               | 25 V               | 10 V               | 6.3 V              | 0°3 V              | 10 V               | 10 V               | 6.3 V              | 6.3 V              | 6.3 V              | VF < 0.38V/5mA@25°C, | VF < 0.38V/5n                      |                         |

| Capacitance                   | 1 µF               | 2.2 µF             | 1 µF               | 2.2 µF             | 2.2 µF             | 4.7 µF             | 2.2 µF             | 4.7 µF             | 4.7 µF             | 4.7 µF             | 4.7 µF             | 2.2 µF             | 2.2 µF             | Schottky diode       | Schottky diodeVF < 0.38V/5mA@25°C, | Schottky diodeVF        |

| Ref No.                       | C11                | C12                | C13                | C14                | C15                | C16                | C17                | C21                | C22                | C23                | C24                | C25                | C26                | C27                | C28                | C31                | C32                | D1                   | D2                                 | D3                      |

[Note]

Also aware the PCB design to avoid other components to be affected by noise on those dcdc pins. C11P/M, C12P/M, C13P/M, C14P/M, C21P/M, C22P/M are high voltage switching lines on FPC. Surround/shield by AGND to avoid noise coupling to other pins.

[Note 4-1] Recommended Capacitors and Diodes

#### 5. Absolute Maximum Ratings

| Item                           | Symbol           | Conditions | Rated value      | Unit | Remarks       |

|--------------------------------|------------------|------------|------------------|------|---------------|

| Input voltage                  | VI               | Ta = 25°C  | -0.3 ~ IOVCC+0.3 | V    | Note 5-1      |

| Logic I/O power supply voltage | IOVCC            | Ta = 25°C  | -0.3 ~ +4.0      | V    |               |

| Analog power supply voltage    | VCC              | Ta = 25°C  | AGND-0.3 ~ +4.6  | V    |               |

| Temperature for storage        | Tstg             | -          | -30~ +85         | °C   | Note 5-2      |

| Temperature for operation      | Topr             | -          | -10 ~ +70        | °C   | Note 5-2, 5-3 |

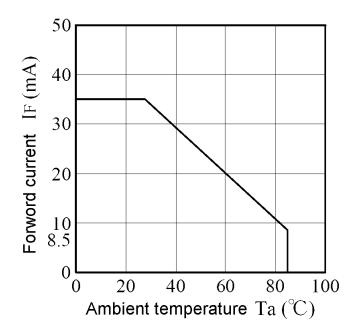

| LED input electric current     | I <sub>LED</sub> | Ta = 25°C  | 35               | mA   | Note 5-4      |

| LED electricity consumption    | $P_{LED}$        | Ta = 25°C  | 123              | mW   | Note 5-4      |

[Note 5-1] RESB, SHUT, CSB, SDI, SCK, DEN, B5~B0, G5~G0, R5~R0, VSYNC, HSYNC, DOTCLK [Note 5-2] Humidity: 95%RH Max. (Ta≦40°C)

Maximum bulb temperature under 39°C (Ta>40°C) See to it that no dew will be condensed. [Note 5-3] The high temperature is the panel surface temperature regulations.

[Note 5-4] Power consumption of one LED (Ta =  $25^{\circ}$ C).

Ambient temperature and the maximum input are fulfilling the following operating conditions.

#### 6. Electrical Characteristics

6-1. TFT LCD Panel Driving

| 5 |  |

|---|--|

|   |  |

|   |  |

|               |             |                                   |           |      |           |       | Ta = 25°C            |

|---------------|-------------|-----------------------------------|-----------|------|-----------|-------|----------------------|

| lt            | em          | Symbol                            | Min.      | Тур. | Max.      | Unit  | Remarks              |

| Logic I/O     | DC voltage  | IOVCC                             | +3.0      | +3.3 | +3.6      | V     |                      |

| power supply  | DC current  | I <sub>IOVCC</sub>                | -         | 0.1  | 0.2       | mA    | Note 6-1             |

| Analog        | DC voltage  | VCC                               | +3.2      | +3.3 | +3.4      | V     | Note 6-1<br>Note 6-6 |

| power supply  | DC current  | I <sub>VCC</sub>                  | -         | 16   | 24        | mA    | Note 6-3             |

| Permis        | sive input  | V <sub>RFIOVCC</sub>              | -         | -    | 100       | mVp-p | Note 6-4             |

| Ripple        | voltage     | V <sub>RFVCC</sub>                | -         | -    | 100       | mVp-p | Note 6-4             |

| Logic         | High        | V <sub>IH</sub>                   | 0.8xIOVCC | -    | IOVCC     | V     | Note 6-5             |

| Input Voltage | Low         | V <sub>IL</sub>                   | 0         | -    | 0.2xIOVCC | V     | Note 6-5             |

| Logic inp     | out Current | I <sub>IH</sub> / I <sub>IL</sub> | -1        | -    | 1         | μA    | Note 6-5             |

[Note 6-1] IOVCC = +3.3V, VCC = +3.3V, f<sub>VSYNC</sub> = 60Hz

Current situation for I<sub>IOVCC</sub>: Black & White checker flag pattern

[Note 6-2] Refer to Recommended Capacitors and Register setting.

[Note 6-3] IOVCC = +3.3V, VCC = +3.3V, f<sub>VSYNC</sub> = 60Hz

Current situation for  $I_{VCC}$ : All black pattern

[Note 6-4] IOVCC = +3.3V, VCC = +3.3V

[Note 6-5] RESB, SHUT, CSB, SDI, SCK, DEN, B5~B0, G5~G0, R5~R0, VSYNC, HSYNC, DOTCLK

[Note 6-6] When it is out of the above recommended operating voltage, for example, in case of

$+3.0V \leq VCC < +3.3V$ ,  $+3.4V < VCC \leq +3.6V$ , the module does not break.

But the deterioration of display quality, flicker etc., may be occurred.

#### 6-2. Register Setting

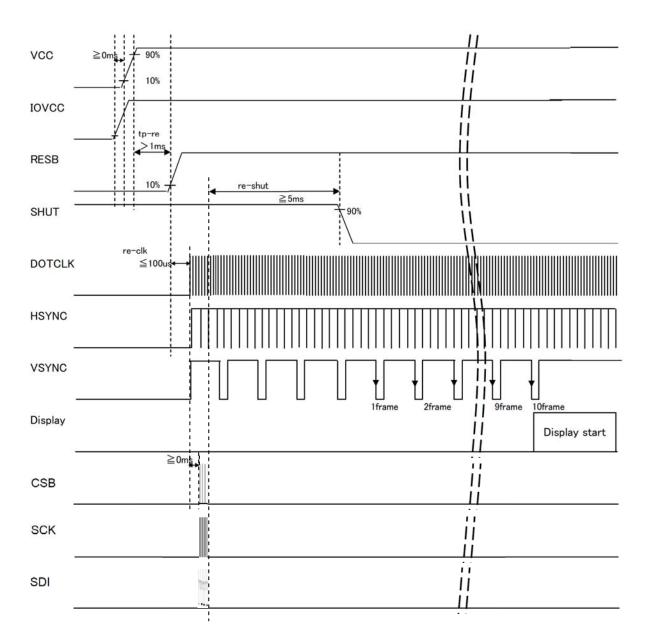

#### IOVCC and VCC ON (%hold RESB = "L", hold SHUT = "H")

# Wait min. 1ms

#### Hard Reset ( $\stackrel{v}{\text{RESB}}$ "L" $\rightarrow$ "H")

↓ Wait max.100us

# Display Data Start (DOTCLK, HSYNC, VSYNC)

Register Setting ( $\overset{\downarrow}{\otimes}$ )

| Reg.# | Register                      | Data<br>(Gamma2.2) | Remark   |

|-------|-------------------------------|--------------------|----------|

| R00 h | Panel Driving Control         | 0013 h             | Note 6-7 |

| R01 h | Power Control 1               | 9A09 h             |          |

| R02 h | Power Control 2               | 9A11 h             |          |

| R03 h | Power Control 3               | 1100 h             |          |

| R04 h | Power Control 4               | 1100 h             |          |

| R05 h | Power Control 5               | 0232 h             |          |

| R06 h | Horizontal Back Porch Control | 000E h             | Note 6-8 |

| R07 h | Vertical Back Porch Control   | 0004 h             | Note 6-9 |

| R09 h | Interface Control             | 0001 h             |          |

| R0A h | Power Control 6               | 1A61 h             |          |

| R0B h | Power Control 7               | FF9B h             |          |

| R0C h | Power Control 8               | 00B0 h             |          |

| R0D h | Power Control 9               | CA53 h             |          |

| R0E h | Power Control 10              | CA53 h             |          |

| R10 h | Gamma Set 1                   | 0616 h             |          |

| R11 h | Gamma Set 2                   | 7916 h             |          |

| R12 h | Gamma Set 3                   | 0805 h             |          |

| R13 h | Gamma Set 4                   | 0217 h             |          |

| R14 h | Gamma Set 5                   | 3121 h             |          |

| R15 h | Gamma Set 6                   | 1707 h             |          |

| R16 h | Gamma Set 7                   | 750F h             |          |

| R17 h | Gamma Set 8                   | 1B0D h             |          |

| R18 h | Gamma Set 9                   | 0106 h             |          |

| R19 h | Gamma Set 10                  | 1112 h             |          |

Wait min. 5ms

Sleep mode  $\rightarrow$ Normal mode conversion (SHUT "H"  $\rightarrow$  "L")

Wait min.10 frame ↓ Back light ON

Display ON

XIf a setting other than the Register setting is captured temporarily due to disturbances such as electrostatic discharge, the normal display is restored by transmitting the recommended setting again.

(At this time, it is not necessary to turn on the power again or perform initializing with RESB.)

| Characteristics                       | symbol   | Min | Тур | Max | Units |

|---------------------------------------|----------|-----|-----|-----|-------|

| VCC on to rising edge of RESB         | tp-re    | 1   | -   | -   | ms    |

| Register set to Falling edge of SHUT  | re-shut  | 5   | -   | -   | ms    |

| RESB on to rising edge of DOTCLK      | re-clk   | -   | -   | 100 | usec  |

| Falling edge of SHUT to display start |          | -   | -   | 10  | frame |

| 1 line: 512 clk                       |          |     |     |     |       |

| 1 frame: 278 line                     | tshut-on | -   | 167 | -   | msec  |

| PIXCLK = 8.5MHz                       |          |     |     |     |       |

\*Display starts at 10<sup>th</sup> falling edge of VSYNC after the falling edge of SHUT.

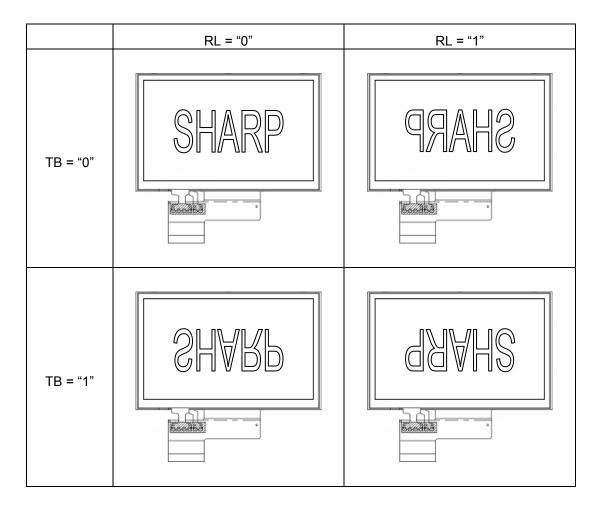

#### [Note 6-7]

Panel Driving Control (R00h)

| F | R/W | DC | IB15 | IB14 | IB13 | IB12 | IB11 | IB10 | IB9 | IB8 | IB7 | IB6 | IB5 | IB4 | IB3 | IB2 | IB1 | IB0 |

|---|-----|----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | W   | 1  | 0    | RL   | 0    | 0    | 0    | 0    | ТВ  | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 1   |

|   | PC  | )R | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 1   |

TB: Selects the output shift direction of the gate driver.

When TB = "0", Top shifts to Bottom.

When TB = "1", Bottom shifts to Top.

RL: Selects the output shift direction of the source driver.

When RL ="0", Left shifts to Right.

When RL ="1", Right shifts to Left.

#### [Note 6-8]

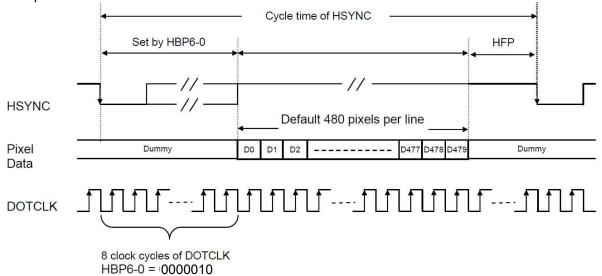

#### Horizontal Back Porch Control (R06h)

| R/W | DC | IB15 | IB14 | IB13 | IB12 | IB11 | IB10 | IB9 | IB8 | IB7 | IB6  | IB5  | IB4  | IB3  | IB2  | IB1  | IB0  |

|-----|----|------|------|------|------|------|------|-----|-----|-----|------|------|------|------|------|------|------|

| W   | 1  | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | HBP6 | HBP5 | HBP4 | HBP3 | HBP2 | HBP1 | HBP0 |

| PC  | DR | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0    | 0    | 0    | 1    | 1    | 1    | 0    |

Number of DOTCLK for HSYNC active low period must be smaller than that of HBP.

HBP6-0: Set the delay period from falling edge of HSYNC signal to first valid data.

| HBP6 | HBP5 | HBP4 | HBP3 | HBP2 | HBP1 | HBP0 | No. of clock cycle of<br>DOTCLK |

|------|------|------|------|------|------|------|---------------------------------|

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 2                               |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 3                               |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 4                               |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 5                               |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 6                               |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 7                               |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 8                               |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 9                               |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 10                              |

|      |      |      |      | :    |      |      | :                               |

|      |      |      |      | :    |      |      | Step = 1                        |

|      | -    |      |      |      | -    |      | :                               |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 121                             |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | 122                             |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 123                             |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 124                             |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 125                             |

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 126                             |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 127                             |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 128                             |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 129                             |

Example

#### [Note 6-9]

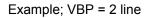

#### Vertical Back Porch Control (R07h)

| _ | R/W | DC | IB15 | IB14 | IB13 | IB12 | IB11 | IB10 | IB9 | IB8 | IB7  | IB6  | IB5  | IB4  | IB3  | IB2  | IB1  | IB0  |

|---|-----|----|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|------|------|

|   | W   | 1  | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | VBP7 | VBP6 | VBP5 | VBP4 | VBP3 | VBP2 | VBP1 | VBP0 |

|   | PC  | DR | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    |

VBP7-0: Set the delay period from falling edge of VSYNC to first valid line.

The line data within this delay period will be treated as dummy line.

| VBP7 | VBP6 | VBP5 | VBP4 | VBP3 | VBP2 | VBP1 | VBP0 | No. of clock cycle of<br>HSYNC |

|------|------|------|------|------|------|------|------|--------------------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | Setting inhibited              |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1                              |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 2                              |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 3                              |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 4                              |

|      |      |      | :    |      |      |      |      |                                |

|      |      |      | :    |      |      |      |      | Step = 1                       |

|      |      |      | :    |      |      |      |      |                                |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 224                            |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 225                            |

| 1    | 1    | 1    | 1    | *    | *    | *    | *    | Reserved                       |

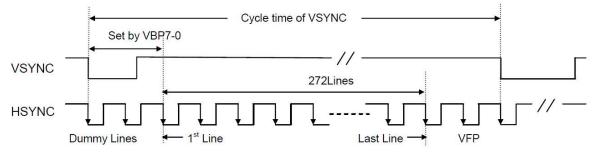

| Characteristics                         | symbol              | Min | Тур | Max | Units |

|-----------------------------------------|---------------------|-----|-----|-----|-------|

| Rising edge of SHUT to input-signal off | Tshut-dotclk<br>Off | 10  | -   | -   | frame |

| 1 line: 512 clk                         |                     |     |     |     |       |

| 1 frame: 278 line                       |                     | 167 | -   | -   | msec  |

| PIXCLK = 8.5MHz                         |                     |     |     |     |       |

| Input-signal-off to IOVCC off           | toff-vdd            | 1   | -   | -   | ms    |

Note1) DOTCLK/HSYNC/VSYNC must be maintained at least 10 frames after the rising edge of SHUT.

Note2) Display become off at the 2<sup>nd</sup> falling edge of VSYNC after the rising edge of SHUT.

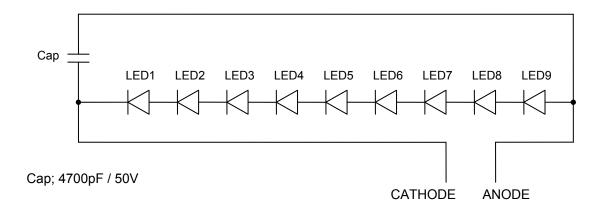

#### 6-4. Back light driving

## The back light system has 9 pieces LED

[LED] NSSW006T (Nichia)

| Parameter         | Symbol   | Min. | Тур. | Max. | Unit | Remark  |

|-------------------|----------|------|------|------|------|---------|

| Rated Voltage     | $V_{BL}$ | -    | 28.8 | 31.5 | V    |         |

| Rated Current     | ١L       | -    | 20   | -    | mA   | Ta=25°C |

| Power consumption | WL       | -    | 576  | -    | mW   |         |

[LED-FPC circuit]

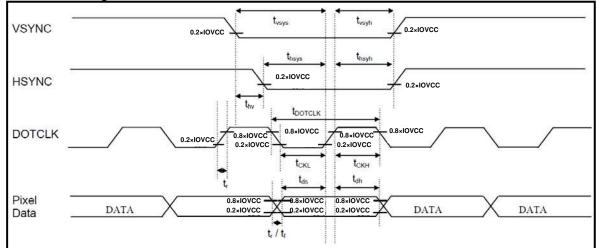

- 7. Timing characteristics of input signals

- 7-1. Pixel Clock Timing

#### IOVCC=2.7V~3.6V

| Characteristics                              | Symbol                          | Min | Тур  | Max               | Units               |

|----------------------------------------------|---------------------------------|-----|------|-------------------|---------------------|

| DOTCLK Frequency                             | f <sub>DOTCLK</sub>             | -   | 8.54 | 12                | MHz                 |

| DOTCLK Period                                | t <sub>DOTCLK</sub>             | 83  | -    | -                 | nsec                |

| DOTCLK Low Period                            | t <sub>скь</sub>                | 41  | -    | -                 | nsec                |

| DOTCLK High Period                           | t <sub>скн</sub>                | 41  | -    | -                 | nsec                |

| Vertical Sync Setup Time                     | t <sub>vsys</sub>               | 20  | -    | -                 | nsec                |

| Vertical Sync Hold Time                      | t <sub>vsyh</sub>               | 20  | -    | -                 | nsec                |

| Horizontal Sync Setup Time                   | t <sub>hsys</sub>               | 20  | -    | -                 | nsec                |

| Horizontal Sync Hold Time                    | t <sub>hsyh</sub>               | 20  | -    | -                 | nsec                |

| Phase difference of Sync signal falling edge | t <sub>hv</sub>                 | 0   | -    | t <sub>∺</sub> -2 | t <sub>DOTCLK</sub> |

| Data Setup Time                              | t <sub>ds</sub>                 | 20  | -    | -                 | nsec                |

| Data Hold Time                               | t <sub>dh</sub>                 | 20  | -    | -                 | nsec                |

| Rise / Fall Time                             | t <sub>r</sub> / t <sub>f</sub> | -   | -    | 10                | nsec                |

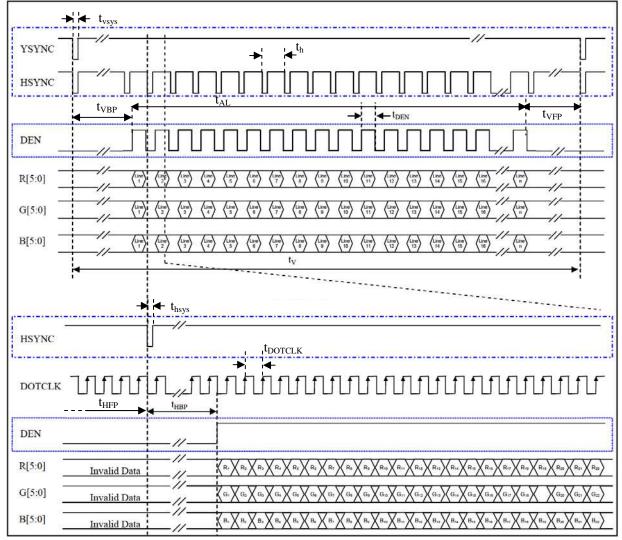

#### 7-2. 18-bit RGB Interface Timing Diagram & Transaction Example

|            | Norostoristics         | Symbol                              | [   | DEN Mode 💥 |                   | Units               |

|------------|------------------------|-------------------------------------|-----|------------|-------------------|---------------------|

|            | Characteristics        |                                     | Min | Тур        | Max               |                     |

| Seria      | I Clock Frequency      | 1/t <sub>DOTCLK</sub>               | _   | 8.54       | 12.0              | MHz                 |

|            | One Line Period        | t <sub>H</sub>                      | 505 | 512        | _                 | t <sub>DOTCLK</sub> |

|            | Active Data Period     | t <sub>data,</sub> t <sub>DEN</sub> | 480 | 480        | 480               | t <sub>DOTCLK</sub> |

| Horizontal | Horizontal Back Porch  | t <sub>HBP</sub>                    | 2   | 16         | _                 | t <sub>DOTCLK</sub> |

|            | Horizontal Front Porch | t <sub>HFP</sub>                    | 2   | 16         | _                 | t <sub>DOTCLK</sub> |

|            | Horizontal sync Period | t <sub>hsys</sub>                   | 2   | _          | t <sub>H</sub> -2 | t <sub>DOTCLK</sub> |

|            | One Field Period       | t <sub>v</sub>                      | 275 | 278        | —                 | t <sub>H</sub>      |

|            | Active Line Period     | t <sub>AL</sub>                     | 272 | 272        | 272               | t <sub>H</sub>      |

|            | Vertical Back Porch    | t <sub>VBP</sub>                    | 2   | 4          | _                 | t <sub>H</sub>      |

| Vertical   | Vertical Front Porch   | t <sub>VFP</sub>                    | 1   | 2          | _                 | t <sub>H</sub>      |

|            | Vertical sync Period   | t <sub>vsys</sub>                   | 1   | 2          | T <sub>v</sub> -2 | t <sub>H</sub>      |

|            | Frequency ※            | 1/tv                                | 50  | 60         | -                 | t <sub>H</sub>      |

%If frequency is low, the display grade, flicker and others may become deterioration. Keep frequency over 50Hz(1/Tv). Although this module is operated in DEN mode to decide a horizontal first position, the inputs of not only DEN but Hsync and Vsync are also required.

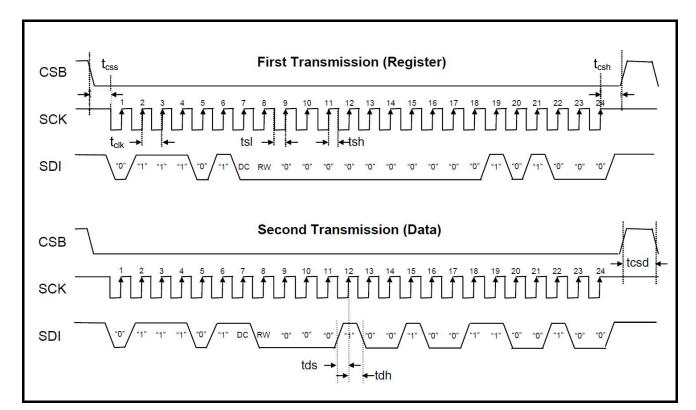

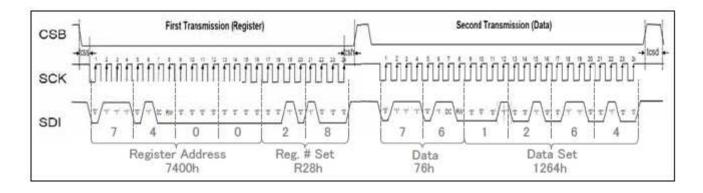

#### 7-3. SPI Interface Timing Diagram & Transaction Example (3-wires 24 bit)

| IOVCC=2.7V~3.6V |

|-----------------|

|-----------------|

| Characteristics             | symbol | Min | Тур | Max | Units |

|-----------------------------|--------|-----|-----|-----|-------|

| Serial Clock Frequency      | fclk   | -   | -   | 20  | MHz   |

| Serial Clock Cycle Time     | tclk   | 50  | -   | -   | nsec  |

| Clock Low Width             | tsl    | 25  | -   | -   | nsec  |

| Clock High Width            | tsh    | 25  | -   | -   | nsec  |

| Chip Select Setup Time      | tcss   | 10  | -   | -   | nsec  |

| Chip Select Hold Time       | tcsh   | 10  | -   | -   | nsec  |

| Chip Select High Delay Time | tcsd   | 25  | -   | -   | nsec  |

| Data Setup Time             | tds    | 10  | -   | -   | nsec  |

| Data Hold Time              | tdh    | 10  | -   | -   | nsec  |

Register write example example) write [1264h] to Register # [R28h]

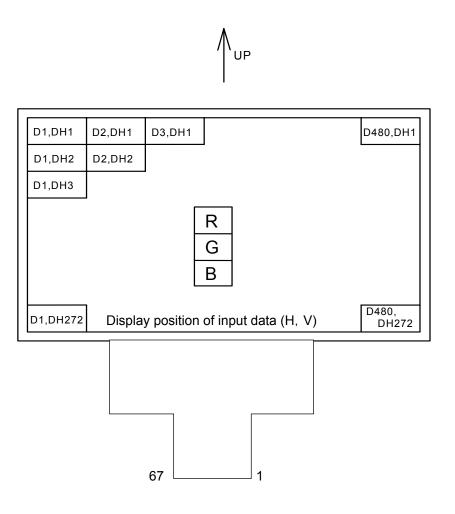

7-4. Input Data Signals and Display Position on the screen

8. Input Signals, Basic Colors and Gray Scale of Each Color

|                    | Colors & |              |     |    |    |    |    |     |              |       | e sign                                 | al |    |             |              |       |        |    |    |     |

|--------------------|----------|--------------|-----|----|----|----|----|-----|--------------|-------|----------------------------------------|----|----|-------------|--------------|-------|--------|----|----|-----|

|                    | Gray     | Gray         | R0  | R1 | R2 | R3 | R4 | R5  | G0           | G1    | G2                                     | G3 | G4 | G5          | В0           | B1    | B2     | В3 | B4 | B5  |

|                    | Scale    | Scale        | LSB |    |    |    |    | MSB | LSB          | 1     | 1                                      | 1  |    | MSB         | LSB          | 1     | 1      | 1  | 1  | MSB |

|                    | Black    | _            | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Blue     | -            | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 1            | 1     | 1      | 1  | 1  | 1   |

| ш                  | Green    | -            | 0   | 0  | 0  | 0  | 0  | 0   | 1            | 1     | 1                                      | 1  | 1  | 1           | 0            | 0     | 0      | 0  | 0  | 0   |

| Basic Color        | Cyan     | -            | 0   | 0  | 0  | 0  | 0  | 0   | 1            | 1     | 1                                      | 1  | 1  | 1           | 1            | 1     | 1      | 1  | 1  | 1   |

| Colo               | Red      | —            | 1   | 1  | 1  | 1  | 1  | 1   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| or                 | Magenta  | -            | 1   | 1  | 1  | 1  | 1  | 1   | 0            | 0     | 0                                      | 0  | 0  | 0           | 1            | 1     | 1      | 1  | 1  | 1   |

|                    | Yellow   | -            | 1   | 1  | 1  | 1  | 1  | 1   | 1            | 1     | 1                                      | 1  | 1  | 1           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | White    | -            | 1   | 1  | 1  | 1  | 1  | 1   | 1            | 1     | 1                                      | 1  | 1  | 1           | 1            | 1     | 1      | 1  | 1  | 1   |

|                    | Black    | GS0          | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| 0                  | 仓        | GS1          | 1   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| Gray Scale of Red  | Darker   | GS2          | 0   | 1  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| Scal               | 仓        | $\checkmark$ |     |    |    | ŀ  |    |     |              |       | `                                      | r  |    |             |              |       |        | Ł  |    |     |

| e of               | Û        | $\checkmark$ |     |    |    |    |    |     | 1            | 、<br> | 1                                      |    | 1  |             | 1            | ,<br> | Ł      | 1  |    |     |

| Red                | Brighter | GS61         | 1   | 0  | 1  | 1  | 1  | 1   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Û        | GS62         | 0   | 1  | 1  | 1  | 1  | 1   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Red      | GS63         | 1   | 1  | 1  | 1  | 1  | 1   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Black    | GS0          | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| G                  | 仓        | GS1          | 0   | 0  | 0  | 0  | 0  | 0   | 1            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| Gray Sca           | Darker   | GS2          | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 1     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| icale              | 仓        | $\checkmark$ |     |    |    | ŀ  |    |     | $\downarrow$ |       |                                        |    |    |             | $\checkmark$ |       |        |    |    |     |

| of G               | Û        | $\checkmark$ |     |    |    |    |    |     |              | r     | `````````````````````````````````````` | 1  |    | 1           |              | 1     | ,<br>I | Ł  | r  |     |

| le of Green        | Brighter | GS61         | 0   | 0  | 0  | 0  | 0  | 0   | 1            | 0     | 1                                      | 1  | 1  | 1           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Û        | GS62         | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 1     | 1                                      | 1  | 1  | 1           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Green    | GS63         | 0   | 0  | 0  | 0  | 0  | 0   | 1            | 1     | 1                                      | 1  | 1  | 1           | 0            | 0     | 0      | 0  | 0  | 0   |

|                    | Black    | GS0          | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 0     | 0      | 0  | 0  | 0   |

| G                  | 仓        | GS1          | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 1            | 0     | 0      | 0  | 0  | 0   |

| Gray Scale of Blue | Darker   | GS2          | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 1     | 0      | 0  | 0  | 0   |

| Scale              | 仓        | $\checkmark$ |     |    |    | ŀ  |    |     | $\checkmark$ |       |                                        |    |    |             | $\checkmark$ |       |        |    |    |     |

| e of E             | Û        | $\checkmark$ |     |    |    |    |    |     |              |       |                                        |    |    | 1           |              | 1     | 、<br>I | ₽  | 1  |     |

| 3lue               | Brighter | GS61         | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 1            | 0     | 1      | 1  | 1  | 1   |

|                    | Û        | GS62         | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0           | 0            | 1     | 1      | 1  | 1  | 1   |

|                    | Blue     | GS63         | 0   | 0  | 0  | 0  | 0  | 0   | 0            | 0     | 0                                      | 0  | 0  | 0<br>el vol | 1            | 1     | 1      | 1  | 1  | 1   |

Each basic color can be displayed in 64 gray scales from 6 bit data signals.

According to the combination of 18 bit data signals, the 262k color display can be achieved on the screen.

#### 9. Optical Characteristics

Module characteristics

| Parameter                                        |            | Symbol | Condition                   | Min.     | Тур. | Max. | Unit  | Remark                   |

|--------------------------------------------------|------------|--------|-----------------------------|----------|------|------|-------|--------------------------|

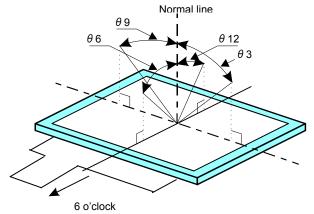

| Viewing<br>angle<br>range<br>(With<br>Wide View) | Horizontal | θ3     | CR≧10                       | -        | 80   | -    | deg.  |                          |

|                                                  |            | θ9     |                             | -        | 80   | -    | deg.  | [Note 9-1]               |

|                                                  | Vertical   | θ12    |                             | -        | 55   | -    | deg.  | [Note 9-4]               |

|                                                  |            | θ6     |                             | -        | 80   | -    | deg.  |                          |

| Contrast ratio                                   |            | CR     | Optimum<br>viewing<br>angle | 250      | 500  | -    | -     | [Note 9-2]<br>[Note 9-4] |

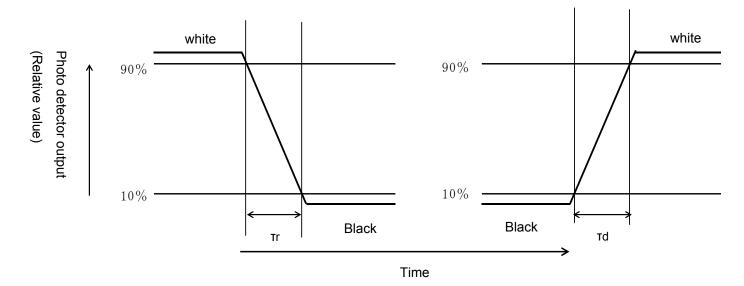

| Response                                         | Rise       | Tr     | θ=0°                        | -        | 22   | 40   | ms    | [Note 9-3]               |

| Time                                             | Decay      | Td     |                             | -        | 8    | 20   | ms    | [Note 9-4]               |

| Chromaticity of                                  |            | х      |                             | 0.26     | 0.31 | 0.36 | -     |                          |

| White                                            |            | у      |                             | 0.29     | 0.34 | 0.39 | -     | [Note 9-4]               |

| Luminance of white                               |            | XL     |                             | 300      | 360  | -    | cd/m² | ILED=20mA<br>[Note 9-4]  |

| The life of LED (Reference)                      |            |        | ILED=20mA                   | (10,000) |      |      | hour  | [Note 9-5]               |

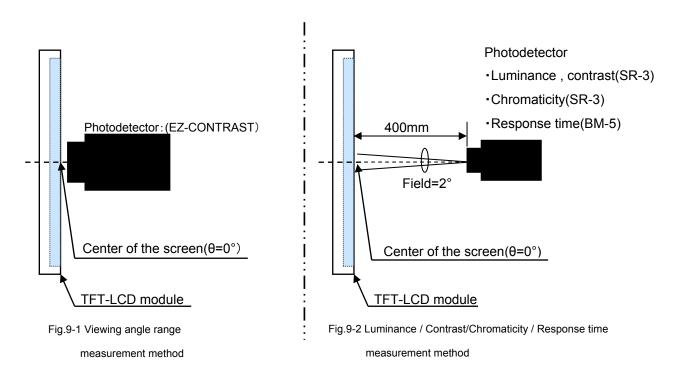

\* The optical characteristics measurements are operated under a stable luminescence

(ILED = 20mA) and a dark condition. (Refer to Fig.9-1 and Fig.9-2)

[Note 9-1] Definitions of viewing angle range

[Note 9-2] Definition of contrast ratio

The contrast ratio is defined as the following

$Contrast ratio (CR) = \frac{Luminance (brightness) with all pixels white}{Luminance (brightness) with all pixels black}$

[Note 9-3] Definition of response time

The response time is defined as the following figure and shall be measured by switching the input signal for "black" and "white"

[Note 9-4] This shall be measured at center of the screen.

[Note 9-5] The life of LED (Reference)

Luminosity will become 50% on more for an initial value in about 10,000H which condition is Ta=25°C and ILED=20mA.

- 10. Handling of modules

- 10-1. Inserting the FPC into its connector and pulling it out.

- 1) Be sure to turn off the power supply and the signals when inserting or disconnecting the cable.

- 2) Please insert for too much stress not to join FPC in the case of insertion of FPC.

- 10-2. Handling of FPC

- 1) The bending radius of the FPC on flexible part should be more than R0.6mm, and it should be bent evenly.

- 2) Do not dangle the LCD module by holding the FPC, or do not give any stress to it.

- 3) Do not add stress to the terminal area of FPC and LCD panel.

- 4) Do not bend FPC to the display direction when handling and mounting.

- 10-3. Mounting of the module

- 1) The module should be held on to the plain surface. Do not give any warping or twisting stress to the module. Refer to 18.Outline Dimensions about the handling area in surface and gasket area in back. When LCD surface is pushed by the power over 300gf/cm<sup>2</sup>, with use of handling area, the pooling may occur at a different place from the pushed place. Because there is a grade difference in the pooling, check and judge after mounting.

- 2) Please consider that GND can ground a modular metal portion etc. so that static electricity is not charged to the module.

- 10-4. Cautions in assembly / Handling pre cautions.

The protect film is attached on the module surface. Remove the film carefully to static electricity as much as possible just before use.

- 1) Notes about removing the protect film on the module surface

- A) Work environments

Since removing laminator may causes electrostatic charge that tends to attract dust, the following work environment would be desired.

- a) Implement more than  $1M\Omega$  conductive treatment (by placing a conductive mat or applying conductive paint on the floor or tiles.)

- b) No dusts come in to the working room. Place an adhesive, anti-dust mat at the entrance of the room.

- c) Humidity of 50 to 70% and temperature of 15 to 27°C are desirable.

- d) All workers wear conductive shoes, conductive clothes, conductive fingerstalls and grounding belts without fail.

- B) Instruction for working

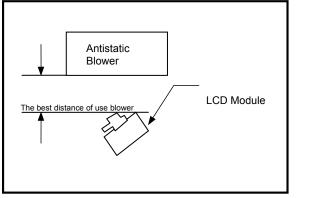

- a) Wind direction of an antistatic blower should slightly downward to properly blow the module.

The distance between the blower and the module should be the best distance of use blower.

Also, pay attention to the direction of the module. [See the above]

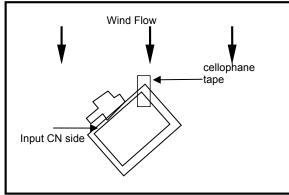

- c) To prevent polarizer from scratching, adhesive tape (cellophane tape) should be stuck at the part of laminator sheet, which is closed to blower. [See the above]

- b) Pull slowly adhesive tape to peel the laminator off, with spending more than 5 second.

- c) The module without laminator should be moved to the next process to prevent adhesion of dust.

- 2) How the remove dust on the polarizer

- a) Blow out dust by the use of an N2 blower with antistatic measures taken. Use of an ionized air Gun is recommendable.

- b) When the panel surface is soiled, wipe it with soft cloth.

- 3) In the case of the module's metal part (shield case) is stained, wipe it with a piece of dry, soft cloth. If rather difficult, give a breath on the metal part to clean better.

- 4) As a glass substrate is used for the TFT-LCD panel, if it is dropped on the floor or hit by something hard, it may be broken or chipped off. Take care of handling.

- 5) Since CMOS LSI is used in this module, take care of static electricity and take the human earth into consideration when handling.

#### 10-5. Others

1) Regarding storage of LCD modules, avoid storing them at direct sunlight-situation.

You are requested to store under the following conditions:

(Environmental conditions of temperature/humidity for storage)

- a) Temperature: 0 to 40°C

- b) Relative humidity : 95% or less

As average values of environments (temperature and humidity) for storing, use the following control guidelines:

Summer season: 20 to 35°C, 85% or less Winter season: 5 to 15°C, 85% or less.

If stored under the conditions of 40°C and 95% RH, cumulative time of storage must be less than 240 hours.

- 2) If stored at temperatures below the rated values, the inner liquid crystal may freeze, causing cell destruction. At temperatures exceeding the rated values for storage, the liquid crystal may become isotropic liquid, making it no longer possible to come back to its original state in some cases. Please store as near room temperature as possible.

- 3) If the LCD is broken, do not drink liquid crystal in the mouth. If the liquid crystal adheres to a hand or foot or to clothes, immediately cleanse it with soap.

- 4) If a water drop or dust adheres for a long time, it is apt to cause deterioration. Wipe it immediately.

- 5) Be sure to observe other caution items for ordinary electronic parts and components.

- 6) When handling and assembling this LCD module, avoid using and storing this module for a long time at the place where Oxidization gas and Reduction gas (SO<sub>2</sub>, H<sub>2</sub>S etc) including the reagent, the adhesives and resin etc which generate these gases may exist in the atmosphere because of corrosion, discoloration, an abnormal display and operation of this module. An abnormal display by changing in quality of the polarizer might occur regardless of contact or no contact to the polarizing plate, because of epoxy resin (amine