Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Dual Serial 12-Bit Multiplying DAC

## **FEATURES**

- DNL and INL Over Temperature: ±0.5LSB Max

- Gain Error: ±1LSB Max

- Low Supply Current: 10µA Max

- 4-Quadrant Multiplication

- Power-On Reset

- Asynchronous Clear Input

- Daisy-Chain 3-Wire Serial Interface

- 16-Pin Narrow SO and PDIP Packages

#### **APPLICATIONS**

- Process Control and Industrial Automation

- Software Controlled Gain Adjustment

- Digitally Controlled Filter and Power Supplies

- Automatic Test Equipment

## DESCRIPTION

The LTC®1590 is a dual, serial input 12-bit multiplying digital-to-analog converter (DAC). It includes two current output multiplying CMOS DACs and an easy SPI compatible serial interface with daisy-chain output. An asynchronous CLR pin sets both DACs to zero scale.

Excellent accuracy, stability and versatility are combined with the smallest package available for a dual 12-bit multiplying DAC.

Parts are available in 16-pin PDIP and narrow SO packages and are specified over the commercial and industrial temperature ranges.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

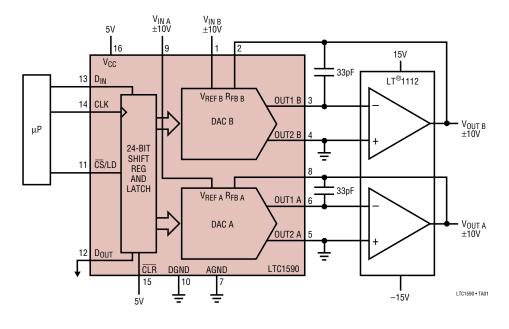

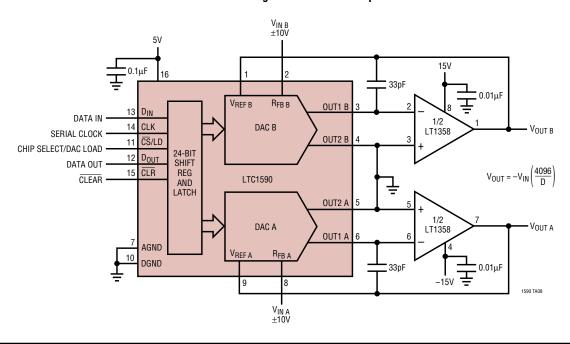

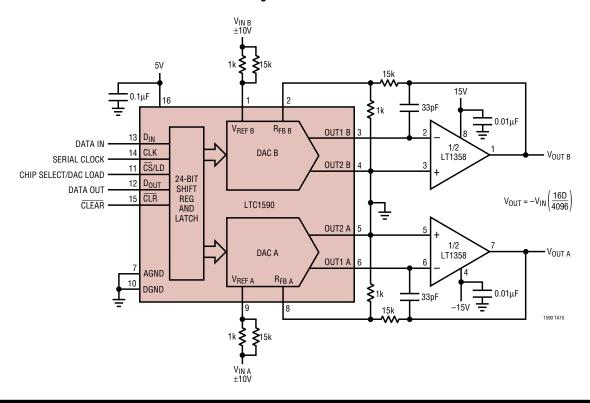

## TYPICAL APPLICATION

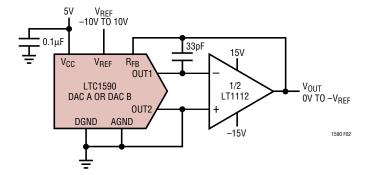

#### **Dual 12-Bit 2-Quadrant Multiplying DAC**

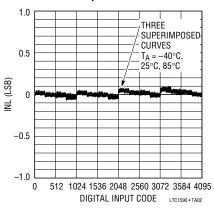

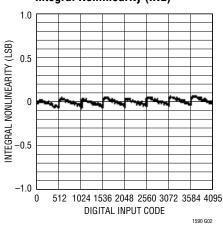

#### Integral Nonlinearity Over Temperature DAC A

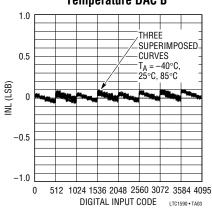

#### Integral Nonlinearity Over Temperature DAC B

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to AGND0.5                                           | V to 7V |

|----------------------------------------------------------------------|---------|

| V <sub>CC</sub> to DGND0.5                                           |         |

| AGND to DGND V <sub>CC</sub>                                         |         |

| DGND to AGNDVCC                                                      | + 0.5V  |

| V <sub>REF</sub> to AGND                                             | ±25V    |

| R <sub>FB</sub> to AGND                                              | ±25V    |

| Digital Inputs to DGND0.5V to V <sub>CC</sub>                        | + 0.5V  |

| V <sub>OUT1</sub> , V <sub>OUT2</sub> to AGND0.5V to V <sub>CC</sub> | + 0.5V  |

| Maximum Junction Temperature                                         | . 150°C |

| Operating Temperature Range                                          |         |

| LTC1590C0°C t                                                        |         |

| LTC1590I40°C t                                                       | :o 85°C |

| Storage Temperature Range65°C to                                     |         |

| Lead Temperature (Soldering, 10 sec)                                 | 300°C   |

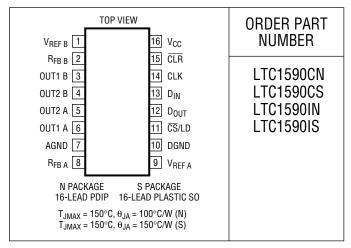

# PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

## **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 4.5V$  to 5.5V,  $V_{REF} = 10V$ ,  $V_{OUT1} = V_{OUT2} = AGND = DGND = 0V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL               | PARAMETER                                                    | CONDITIONS                                                              |   | MIN | TYP     | MAX            | UNITS      |

|----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|---|-----|---------|----------------|------------|

| Accuracy             |                                                              |                                                                         |   |     |         | 1              |            |

|                      | Resolution                                                   |                                                                         | • | 12  |         |                | Bits       |

| INL                  | Integral Nonlinearity                                        | (Note 1)                                                                | • |     |         | ± 0.5          | LSB        |

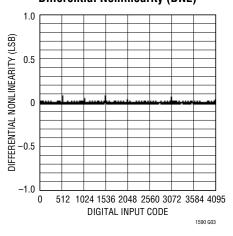

| DNL                  | Differential Nonlinearity                                    | Guaranteed Monotonic, T <sub>MIN</sub> to T <sub>MAX</sub>              | • |     |         | ± 0.5          | LSB        |

| GE                   | Gain Error                                                   | (Note 2), T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • |     |         | ±1<br>±2       | LSB<br>LSB |

|                      | Gain Temperature Coefficient                                 | (Note 3) ∆Gain/∆Temperature                                             | • |     | 1       | 5              | ppm/°C     |

| I <sub>LEAKAGE</sub> | OUT1 A, OUT1 B Leakage Current                               | (Note 4), T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • |     |         | ±5<br>±25      | nA<br>nA   |

|                      | Zero-Scale Error                                             | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>           | • |     |         | ±0.03<br>±0.15 | LSB<br>LSB |

| PSRR                 | Power Supply Rejection                                       | V <sub>CC</sub> = 5V ±10%                                               | • |     | ±0.0001 | ±0.002         | %/%        |

| Reference            | Input                                                        |                                                                         |   |     |         |                |            |

| R <sub>REF</sub>     | V <sub>REF</sub> Input Resistance                            |                                                                         | • | 8   | 11      | 15             | kΩ         |

|                      | V <sub>REFA</sub> , V <sub>REFB</sub> Input Resistance Match |                                                                         | • |     |         | 3              | %          |

| AC Perform           | nance (Note 3)                                               |                                                                         |   |     |         |                |            |

|                      | Digital-to-Analog Glitch Impulse                             | (Notes 5, 6)                                                            |   |     | 1       |                | nV-s       |

|                      | Multiplying Feedthrough Error                                | (Note 11)                                                               |   |     | -89     | -80            | dB         |

|                      | Output Current Settling Time                                 | (Note 5) To 0.01% for Full-Scale Change                                 |   |     | 0.3     | 0.8            | μs         |

|                      | Channel-to-Channel Isolation                                 | (Note 7)                                                                |   |     |         | -90            | dB         |

|                      | Digital Crosstalk                                            | (Notes 5, 8)                                                            |   |     | 1       |                | nV-s       |

|                      | Output Noise Voltage Density                                 | (Note 9)                                                                |   |     | 13      |                | nV/√Hz     |

| THD                  | Total Harmonic Distortion                                    | (Note 10)                                                               |   |     | -108    | -92            | dB         |

|                      | Multiplying Bandwidth                                        | (Note 12)                                                               |   |     | 1       |                | MHz        |

## **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 4.5V$  to 5.5V,  $V_{REF} = 10V$ ,  $V_{OUT1} = V_{OUT2} = AGND = DGND = 0V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL              | PARAMETER                                   | CONDITIONS                                                     |          | MIN | TYP      | MAX      | UNITS    |

|---------------------|---------------------------------------------|----------------------------------------------------------------|----------|-----|----------|----------|----------|

| Analog Ou           | itputs                                      |                                                                | <u>.</u> |     |          |          |          |

| C <sub>OUT</sub>    | Output Capacitance (Note 3)                 | DAC Register Loaded to All 1s<br>DAC Register Loaded to All 0s | •        |     | 60<br>30 | 90<br>60 | pF<br>pF |

| Digital Inp         | out                                         |                                                                |          |     |          |          |          |

| $\overline{V_{IH}}$ | Digital Input High Voltage                  |                                                                | •        | 2.4 |          |          | V        |

| $\overline{V_{IL}}$ | Digital Input Low Voltage                   |                                                                | •        |     |          | 0.8      | V        |

| I <sub>IN</sub>     | Digital Input Current                       |                                                                | •        |     | 0.001    | ±1       | μА       |

| C <sub>IN</sub>     | Digital Input Capacitance                   | (Note 3) V <sub>IN</sub> = 0V                                  | •        |     |          | 8        | pF       |

| Digital Ou          | tput                                        |                                                                |          |     |          |          |          |

| V <sub>OH</sub>     | Digital Output High Voltage                 | I <sub>OH</sub> = 200μA                                        | •        | 4   |          |          | V        |

| $\overline{V_{0L}}$ | Digital Output Low Voltage                  | I <sub>OH</sub> = 1.6mA                                        | •        |     |          | 0.4      | V        |

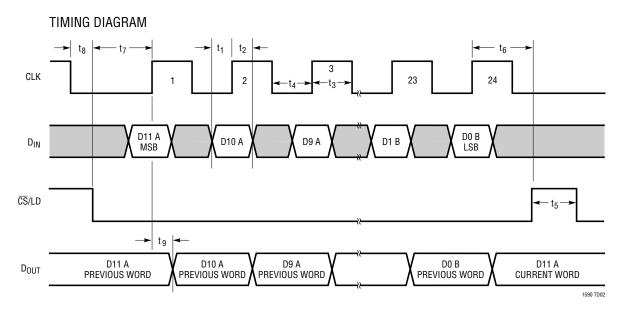

| Timing Ch           | naracteristics                              |                                                                |          |     |          |          |          |

| t <sub>1</sub>      | D <sub>IN</sub> to CLK Setup Time           |                                                                | •        | 50  |          |          | ns       |

| t <sub>2</sub>      | D <sub>IN</sub> to CLK Setup Hold Time      |                                                                | •        | 0   |          |          | ns       |

| t <sub>3</sub>      | CLK High Time                               |                                                                | •        | 40  |          |          | ns       |

| t <sub>4</sub>      | CLK Low Time                                |                                                                | •        | 40  |          |          | ns       |

| t <sub>5</sub>      | CS/LD High Time                             |                                                                | •        | 50  |          |          | ns       |

| $t_6$               | LSB CLK to $\overline{\text{CS}}/\text{LD}$ |                                                                | •        | 40  |          |          | ns       |

| t <sub>7</sub>      | CS/LD Low to CLK High                       |                                                                | •        | 20  |          |          | ns       |

| t <sub>8</sub>      | CLK Low to CS/LD Low                        |                                                                | •        | 20  |          |          | ns       |

| t <sub>9</sub>      | CLK to D <sub>OUT</sub> Delay               |                                                                | •        | 10  |          | 160      | ns       |

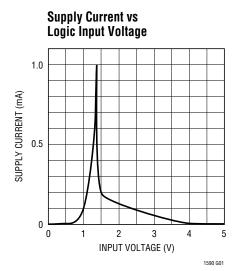

| Power Su            | pply                                        |                                                                |          |     |          |          |          |

| $\overline{V_{CC}}$ | Operating Supply Range                      |                                                                | •        | 4.5 | 5        | 5.5      | V        |

| I <sub>CC</sub>     | Supply Current                              | Digital Inputs = 0V or V <sub>CC</sub>                         | •        |     |          | 10       | μА       |

The • denotes specifications which apply over the full operating temperature range.

**Note 1:**  $\pm 0.5$ LSB =  $\pm 0.012\%$  of full scale.

Note 2: Using internal feedback resistor.

Note 3: Guaranteed by design, not subject to test.

Note 4: I<sub>OUT1</sub> with DAC register loaded with all 0s.

**Note 5:** OUT1 load =  $100\Omega$  in parallel with 13pF.

Note 6:  $V_{REF} = 0V$ . DAC register contents changed from all 0s to all 1s or all 1s to all 0s.

**Note 7:** DAC A output with  $V_{REF\,A}=0V$  and  $V_{REF\,B}=10$ kHz  $20V_{P-P}$ , or DAC B output with  $V_{REF\,B}=0V$ ,  $V_{REF\,A}=10$ kHz  $20V_{P-P}$ . Both DAC registers loaded with all 1s.

**Note 8:** Glitch on DAC A or DAC B output when the other DAC makes a full-scale transition.

**Note 9:** 10Hz to 100kHz. Calculation from  $e_n = \sqrt{4KTRB}$  where:

K = Boltzmann constant (J/K $^{\circ}$ ); R = resistance ( $\Omega$ ); T = resistor temperature ( $^{\circ}$ K); B = bandwidth (Hz).

Note10:  $V_{REF} = 6V_{RMS}$  at 1kHz. DAC register loaded with all 1s, using LT $^{\circ}$ 1124 op amp.

Note 11:  $V_{REF} = \pm 10V$ , 10kHz sine wave, DAC register loaded with all 0s, using LT1358 op amp.

Note 12: -3dB bandwidth using LT1358 op amp.

# TYPICAL PERFORMANCE CHARACTERISTICS

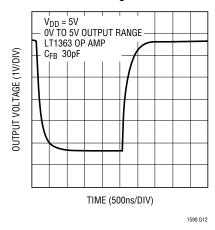

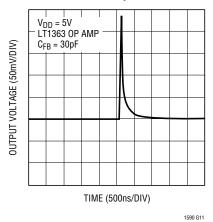

#### **Full-Scale Settling Waveform**

#### Integral Nonlinearity (INL)

**Differential Nonlinearity (DNL)**

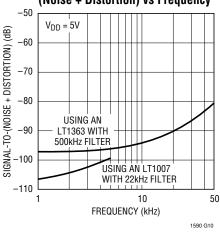

Multiplying Mode Signal-to-(Noise + Distortion) vs Frequency

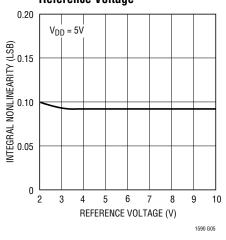

Integral Nonlinearity vs Reference Voltage

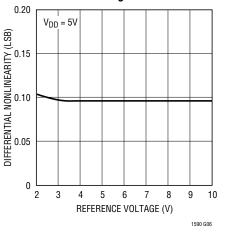

Differential Nonlinearity vs Reference Voltage

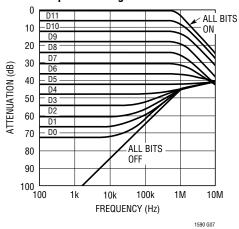

Multiplying Mode Frequency Response vs Digital Code

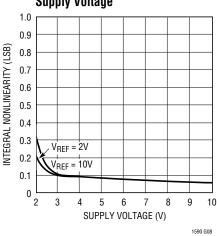

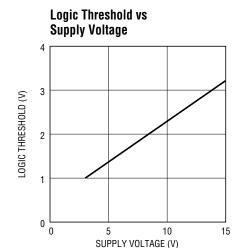

Integral Nonlinearity vs Supply Voltage

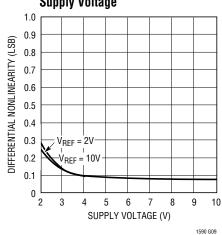

Differential Nonlinearity vs Supply Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS

#### Midscale Glitch Impulse

1590 G04

## PIN FUNCTIONS

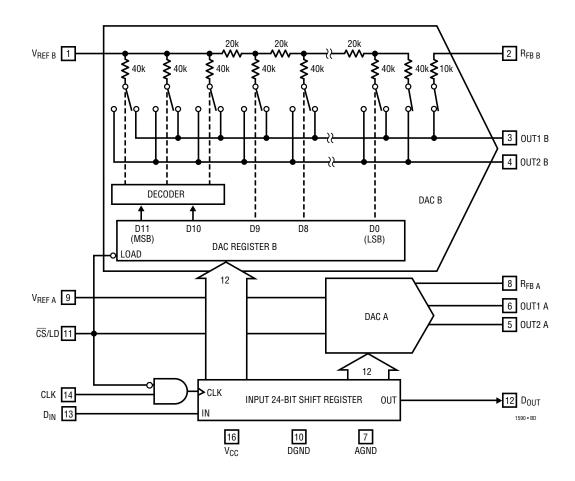

$V_{REF\,B}$ ,  $V_{REF\,A}$  (Pins 1, 9): Reference Inputs for DAC A/B. Typically  $\pm 10V$ , accepts up to  $\pm 25V$ .

$R_{FB\,B}$ ,  $R_{FB\,A}$  (Pins 2, 8): Feedback Resistors for DAC A/B. Normally tied to the output of current to voltage converter op amp. Typically swings to  $\pm 10V$ . Swings from 0V to  $-V_{RFF}$ .

**OUT1 B, OUT1 A (Pins 3, 6):** True Current Output for DAC A/B. Normally tied to inverting input of current to voltage converter op amp.

**OUT2 B, OUT2 A (Pins 4, 5):** Complement Current Output for DAC A/B. Normally tied to ground.

**AGND (Pin 7):** Analog Ground Pin. Tie to ground.

**DGND (Pin 10):** Digital Ground Pin. Tie to ground.

CS/LD (Pin 11): The Serial Interface Enable and Load Control Input. When CS/LD is low the CLK signal is

enabled so the data can be clocked in. When  $\overline{\text{CS}}/\text{LD}$  is pulled high, data is loaded from the shift register into the DAC register, updating the DAC output.

**D**<sub>OUT</sub> (**Pin 12**): The Serial Data Output. Data becomes valid on the rising edge of the CLK.

$D_{IN}$  (Pin 13): The Serial Data Input. Data on the  $D_{IN}$  pin is latched into the shift register on the rising edge of the serial clock. Data is loaded as one 24-bit word. The first 12 bits are for DAC A, MSB-first and the second 12 bits are for DAC B, MSB-first.

CLK (Pin 14): The Serial Interface Clock Input.

$\overline{\text{CLR}}$  (Pin 15): The Clear Pin for the DAC. Clears both DACs to zero scale when pulled low. This pin should be tied to  $V_{CC}$  for normal operation.

$V_{CC}$  (Pin 16): The Positive Supply Input. 4.5  $\leq$   $V_{CC} \leq$  5.5V. Requires a bypass capacitor to ground.

# **BLOCK DIAGRAM**

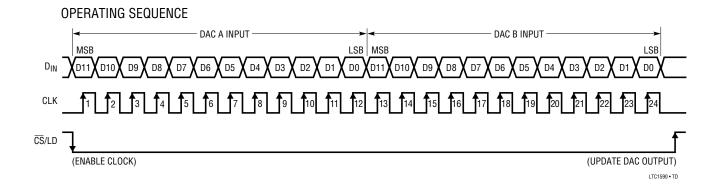

# TIMING DIAGRAMS

TECHNOLOGY TECHNOLOGY

## TIMING DIAGRAMS

## APPLICATIONS INFORMATION

### **Description**

The LTC1590 is a dual 12-bit multiplying DAC that has serial inputs and current outputs. It uses precision R/2R resistor ladder technology to provide exceptional linearity and stability. The device operates from a single 5V supply and provides a  $\pm 10V$  reference input and voltage output range when used with an external op amp.

#### Serial I/O

The LTC1590 has a 3-wire SPI/MICROWIRE<sup>TM</sup> compatible serial port that accepts 24-bit serial words. Data is loaded MSB first with the first 12 bits controlling DAC A and the second 12 bits controlling DAC B. Data is shifted into the D<sub>IN</sub> input on the rising edge of CLK. The  $\overline{\text{CS}}$ /LD input must be taken low before transferring data to enable the CLK input. After transferring data,  $\overline{\text{CS}}$ /LD is pulled high to load data from the shift register to the DAC registers which updates both DACs.

The buffered output of the 24-bit shift register is available on the  $D_{OUT}$  pin. Multiple DACs can be daisy-chained on one 3-wire interface by connecting the  $D_{OUT}$  pin to the  $D_{IN}$  pin of the next DAC (see the Timing Diagrams section).

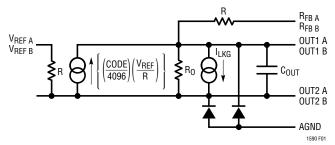

#### **Equivalent Circuit**

Figure 1 shows an equivalent analog circuit for the LTC1590 DACs. R is the reference input,  $R_{REF}$ , which is nominally 11k. The DAC output is represented by the Thevinin equivalent current source with a value of:

$$(Code/4096)(V_{REF}/R)$$

The current source  $I_{LKG}$  models the junction leakage of the DAC output switches.  $I_{LKG}$  is typically less than 5nA at 85°C and decreases by roughly two times for every 10°C reduction in temperature.  $C_{OUT}$  is the output capacitance, and it also comes from the DAC output switches and varies from 30pF at zero scale to 60pF at full scale.  $R_0$  is the equivalent output resistance, which varies with digital input code (see 0p Amp Selection section).

Figure 1. Equivalent Circuit

MICROWIRE is a trademark of National Semiconductor Corporation.

# **APPLICATIONS INFORMATION**

# Unipolar 2-Quadrant Multiplying Mode $(V_{OUT} = 0V \text{ to } -V_{REF})$

The LTC1590 can be used with a dual op amp to provide a dual 2-quadrant multiplying DAC as shown in Figure 2. The unipolar DAC transfer function is shown in Table 1. The 33pF feedback capacitor is recommended to compensate for the pole caused by the internal feedback resistor and the OUT1 output capacitance. For high speed op amps this feedback capacitor is required for stability, and a smaller value, 8pF to 15pF, may be desired to get the fastest transient response and shortest settling time. A larger feedback capacitor can be used to reduce wideband noise, glitch impulse and distortion for lower frequency signals. A pole is introduced in the DAC transfer function at approximately  $(C_{FB})(R_{FB})$ . For example, a 100pF feedback capacitor will typically give a pole at:

$$145 \text{kHz} = \frac{1}{2\pi \left(100 \text{pF}\right) \left(11 \text{k}\Omega\right)}$$

Figure 2. Unipolar Operation (2-Quadrant Multiplication)

Table 1. Unipolar Binary Code Table

| DIGITAL INPUT<br>Binary Number<br>In dac register                    | ANALOG OUTPUT<br>V <sub>out</sub>                                                                                         |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| MSB LSB                                                              |                                                                                                                           |

| 1111 1111 1111<br>1000 0000 0000<br>0000 0000 0001<br>0000 0000 0000 | -V <sub>REF</sub> (4095/4096)<br>-V <sub>REF</sub> (2048/4096) = -V <sub>REF</sub> /2<br>-V <sub>REF</sub> (1/4096)<br>0V |

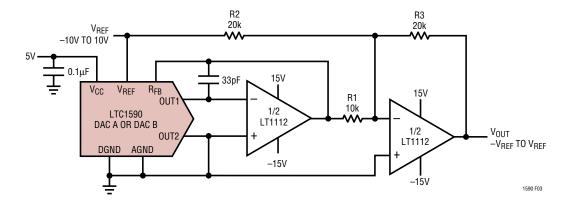

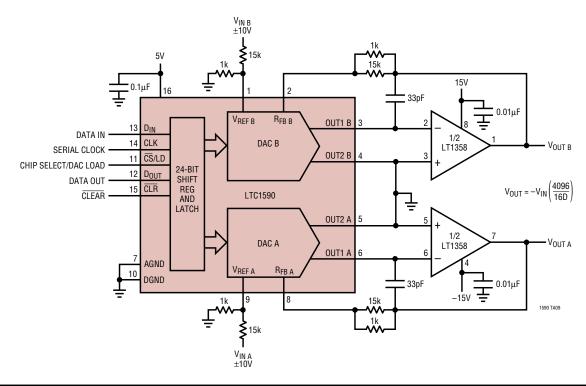

# Bipolar 4-Quadrant Multiplying Mode $(V_{OUT} = -V_{REF} \text{ to } +V_{REF})$

The circuit of Figure 3 can be used to provide a dual 4-quadrant multiplying DAC. This circuit starts with the unipolar application circuit and adds three resistors and an op amp. These extra devices provide a gain of -2 from the unipolar output to the bipolar output, plus an offset of  $(-1)(V_{REF})$  to produce the transfer function shown in Table 2. A pack of matched 20k resistors, with two resistors in parallel forming the 10k resistor, is recommended.

Table 2. Bipolar Offset Binary Code Table

| DIGITAL INPUT<br>BINARY NUMBER<br>IN DAC REGISTER                                      | ANALOG OUTPUT<br>V <sub>out</sub>                                                                                                                    |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSB LSB                                                                                |                                                                                                                                                      |

| 1111 1111 1111<br>1000 0000 0001<br>1000 0000 0000<br>0111 1111 1111<br>0000 0000 0000 | +V <sub>REF</sub> (2047/2048)<br>+V <sub>REF</sub> (1/2048)<br>0V<br>-V <sub>REF</sub> (1/2048)<br>-V <sub>REF</sub> (2048/2048) = -V <sub>REF</sub> |

Figure 3. Bipolar Operation (4-Quadrant Multiplication)

## APPLICATIONS INFORMATION

#### Op Amp Selection

To maintain the excellent accuracy and stability of the LTC1590 thought should be given to op amp selection. Fortunately, the sensitivity of INL and DNL to op amp offset has been significantly reduced compared to competing parts of this type. The op amp's V<sub>OS</sub> causes DAC output offset. In addition, because the DAC's equivalent output resistance R<sub>0</sub> changes as a function of code, there is a code-dependent DAC output error proportional to  $V_{OS}$ . For fixed reference applications this causes gain, INL and DNL error. For multiplying applications, a code-dependent, DC output voltage error is seen. At zero scale the DAC output error is equal to the op amp offset, and at full scale the output error is equal to twice the op amp offset. For example, a 1mV op amp offset will cause a 0.41LSB zeroscale error and a 0.82LSB full-scale error with a 10V fullscale range. The offset caused INL error is approximately 0.4 times the op amp  $V_{OS}$  and DNL error is 0.07 times op amp  $V_{OS}$ . For the same example of 1mV op amp  $V_{OS}$  and 10V full-scale range, the INL degradation will be 0.17LSB and DNL degradation will be 0.03LSB.

Op amp bias current causes only an offset error equal to  $(I_{BIAS})(R_{FB}) \approx (I_{BIAS})(11k\Omega)$ . For example, a 100nA op

amp bias current causes a 1.1mV DAC offset, or 0.45LSB for a 10V full-scale range. It is important to note that connecting the op amp noninverting input to ground through a resistor will not cancel bias current errors and should never be done! Similarly an offset caused by op amp bias current should not be adjusted by using the op amp null pins since this increases offset between DAC OUT1 and OUT2 pins, causing INL, DNL and gain errors. If op amp offset error adjustment is required, the op amp input offset voltage (the voltage difference between OUT1 and OUT2) should be nulled.

#### Grounding

As with any high precision data converter, clean grounding is important. A low impedance analog ground plane and star grounding should be used. OUT2 carries the complementary DAC output current and should be tied to the star ground with as low a resistance as possible. Other ground points that must be tied to the star ground point include the  $V_{REF}$  input ground, the op amp noninverting input(s) and the  $V_{OUT}$  ground reference point.

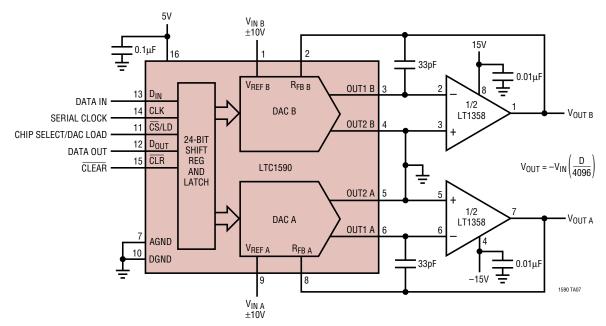

# TYPICAL APPLICATIONS

#### **Dual Programmable Attenuator**

# TYPICAL APPLICATIONS

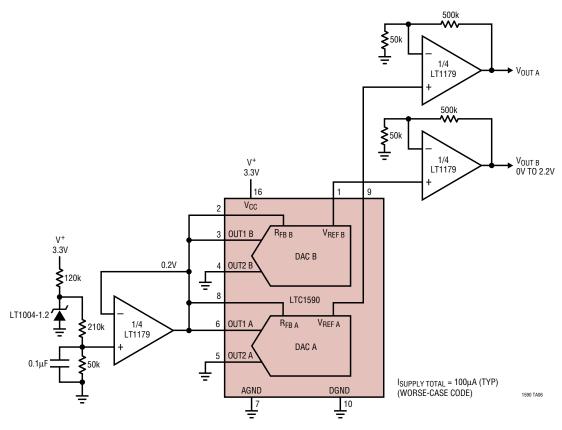

### Very Low Power Single Supply Dual Vout DAC

#### **Dual Programmable Gain Amplifier**

# TYPICAL APPLICATIONS

#### **Dual Programmable Gain Amplifier with Input Attenuation**

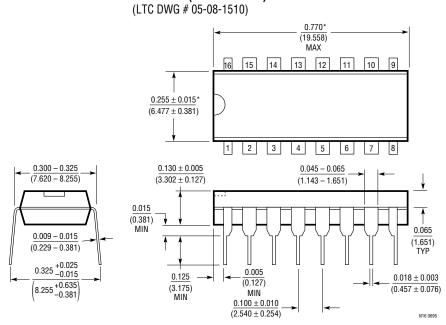

# PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

## N Package 16-Lead PDIP (Narrow 0.300)

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

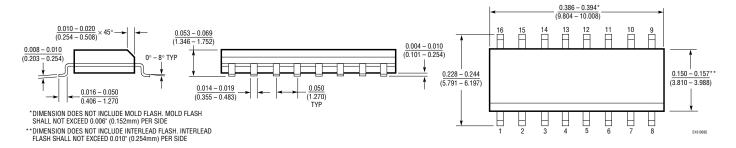

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### S Package 16-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

# TYPICAL APPLICATION

#### **Dual Programmable Attenuator with Gain**

# **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                                          | COMMENTS                                   |

|-----------------|------------------------------------------------------|--------------------------------------------|

| LTC1595         | 16-Bit Multiplying I <sub>OUT</sub> DAC in SO-8      | True 16-Bit Upgrade for DAC8043            |

| LTC1596         | 16-Bit Multiplying I <sub>OUT</sub> DAC              | True 16-Bit Upgrade for DAC8143 and AD7543 |

| LTC7541A        | Parallel I/O Multiplying I <sub>OUT</sub> 12-Bit DAC | 12-Bit Wide Parallel Input                 |

| LTC7543/LTC8143 | Serial I/O Multiplying I <sub>OUT</sub> 12-Bit DACs  | Clear Pin and Serial Data Output (LTC8143) |

| LTC7545A        | Parallel I/O Multiplying I <sub>OUT</sub> 12-Bit DAC | 12-Bit Wide Latched Parallel Input         |

| LTC8043         | Serial I/O Multiplying I <sub>OUT</sub> 12-Bit DAC   | 8-Pin SO and PDIP                          |