Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Precision Triple Supply Monitor with Power-Fail Comparator

## **FEATURES**

- Ultralow Voltage Reset: V<sub>CC</sub> = 0.5V Guaranteed

- Monitors Three Inputs Simultaneously:

- 3.3V, 5V, ADJ (LTC2911-1)

- 3.3V, 2.5V, ADJ (LTC2911-2)

- 3.3V, 1.8V, ADJ (LTC2911-3)

- 3.3V, 1.2V, ADJ (LTC2911-4)

- 3.3V, ADJ, ADJ (LTC2911-5)

- ±1.5% Threshold Accuracy

- Power-Fail Monitor

- RST State Can Be Held for Margining

- Low Supply Current: 30µA Typical

- Input Glitch Immunity

- Adjustable Reset Timeout Period

- Selectable Internal Timeout Saves Components

- Space Saving 8-Lead TSOT-23 and 3mm × 2mm DFN Packages

## **APPLICATIONS**

- Network Servers

- Desktop and Notebook Computers

- Automotive and Industrial Electronics

## DESCRIPTION

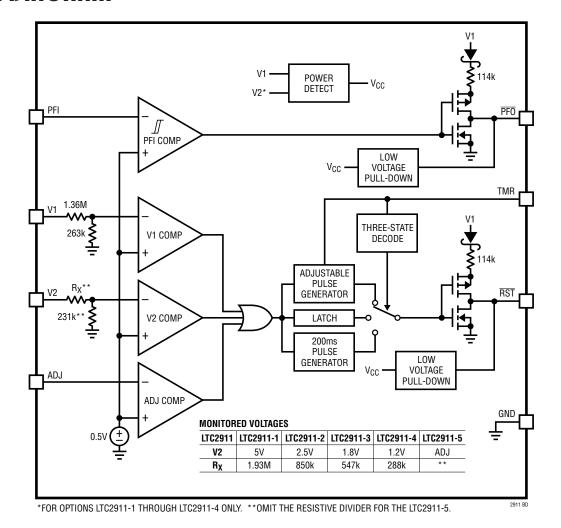

The LTC®2911 is a low power, high accuracy triple supply monitor with a power-fail comparator. Reset timeout may be selected with an external capacitor or set to an internally generated 200ms.

The V1 pin monitors a 3.3V supply. The V2 pin monitors a 5V, 2.5V, 1.8V, 1.2V or adjustable supply. A third adjustable input has a nominal 0.5V threshold allowing a resistive divider to configure its threshold. All three comparators feature a tight 1.5% threshold accuracy over the entire operating temperature range while a glitch filter ensures reliable reset operation.

A spare comparator can be configured to provide early warning of a low voltage condition. It causes the  $\overline{PFO}$  output to pull low when the voltage of the PFI input falls below 0.5V, allowing the power-fail threshold to be configured with a resistive divider. A latch feature on the TMR pin allows the  $\overline{RST}$  output to be latched to prevent system resets, simplifying margin testing.

LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 6949965, 7292076.

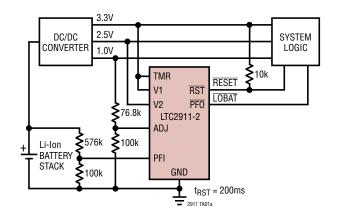

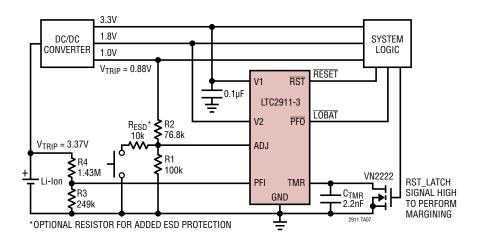

## TYPICAL APPLICATION

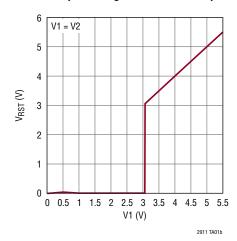

#### RST Output Voltage With 10k Pull-Up to V1

2911f

# **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2, 3)

| Supply Voltages | 0.01/10.51/         |

|-----------------|---------------------|

| *               | –0.3V to 6.5V       |

| Input Voltages  |                     |

|                 | 0.3V to 6.5V        |

|                 |                     |

| TMR             | 0.3V to (V1 + 0.3V) |

| Output Voltages | ,                   |

| RST, PFO        | 0.3V to 6.5V        |

| Operating Temperature Range       |               |

|-----------------------------------|---------------|

| LTC2911C                          | 0°C to 70°C   |

| LTC29111                          | 40°C to 85°C  |

| LTC2911H                          | 40°C to 125°C |

| Storage Temperature Range         | 65°C to 150°C |

| Lead Temperature (Soldering, 10 s | sec)          |

| TSOT-23                           | 300°C         |

|                                   |               |

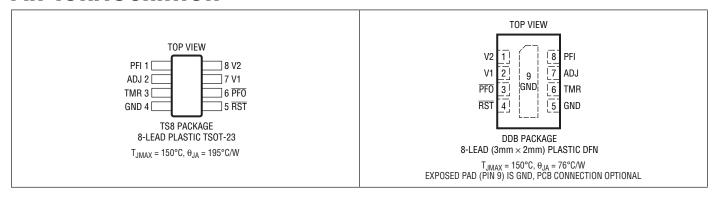

## PIN CONFIGURATION

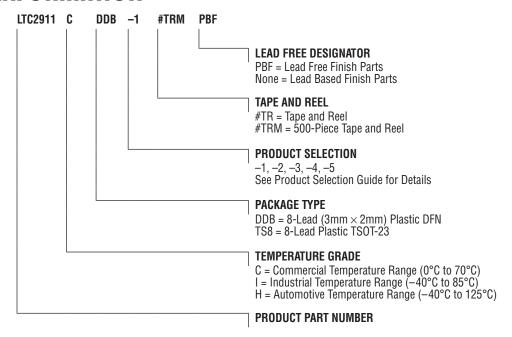

## ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **PRODUCT SELECTION GUIDE**

| PART NUMBER | PART MARKING | PACKAGE DESCRIPTION                 | V1                                  | V2   |  |

|-------------|--------------|-------------------------------------|-------------------------------------|------|--|

| LTC2911-1   | LFHZ         | 8-Lead (3mm × 2mm) Plastic DFN 3.3V |                                     | 5V   |  |

| LTC2911-2   | LFPG         | 8-Lead (3mm × 2mm) Plastic DFN      | 8-Lead (3mm × 2mm) Plastic DFN 3.3V |      |  |

| LTC2911-3   | LFPJ         | 8-Lead (3mm × 2mm) Plastic DFN 3.3V |                                     | 1.8V |  |

| LTC2911-4   | LFPM         | 8-Lead (3mm × 2mm) Plastic DFN      | 3.3V                                | 1.2V |  |

| LTC2911-5   | LFPP         | 8-Lead (3mm × 2mm) Plastic DFN      | 3.3V                                | ADJ  |  |

| LTC2911-1   | LTFJB        | 8-Lead Plastic TSOT-23              | 3.3V                                | 5V   |  |

| LTC2911-2   | LTFPH        | 8-Lead Plastic TSOT-23              | 3.3V                                | 2.5V |  |

| LTC2911-3   | LTFPK        | 8-Lead Plastic TSOT-23              | 3.3V                                | 1.8V |  |

| LTC2911-4   | LTFPN        | 8-Lead Plastic TSOT-23              | 3.3V                                | 1.2V |  |

| LTC2911-5   | LTFPQ        | 8-Lead Plastic TSOT-23 3.3V AI      |                                     | ADJ  |  |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{ADJ} = 0.55V$ ,  $V_{PFI} = 0.55V$ ,  $V_{1} = 3.3V$  unless otherwise noted. (Notes 2, 3)

| SYMBOL                 | PARAMETER                                                | CONDITIONS                                                                                                                                             |           | MIN               | TYP                  | MAX                                | UNITS                      |

|------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|----------------------|------------------------------------|----------------------------|

| V <sub>RT33</sub>      | 3.3V, 5% Reset Threshold                                 | V1 Input                                                                                                                                               | •         | 3.036             | 3.086                | 3.135                              | V                          |

| V <sub>RT50</sub>      | 5V, 5% Reset Threshold                                   | V2 Input (LTC2911-1)                                                                                                                                   | •         | 4.600             | 4.675                | 4.750                              | V                          |

| V <sub>RT25</sub>      | 2.5V, 5% Reset Threshold                                 | V2 Input (LTC2911-2)                                                                                                                                   | •         | 2.300             | 2.338                | 2.375                              | V                          |

| V <sub>RT18</sub>      | 1.8V, 5% Reset Threshold                                 | V2 Input (LTC2911-3)                                                                                                                                   | •         | 1.656             | 1.683                | 1.710                              | V                          |

| V <sub>RT12</sub>      | 1.2V, 5% Reset Threshold                                 | V2 Input (LTC2911-4)                                                                                                                                   | •         | 1.104             | 1.122                | 1.140                              | V                          |

| V <sub>RTA</sub>       | ADJ Pin Threshold                                        | ADJ Input and V2 Input of LTC2911-5                                                                                                                    | •         | 492.5             | 500                  | 507.5                              | mV                         |

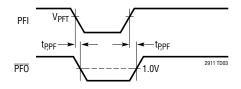

| $V_{PFT}$              | PFI Pin Threshold                                        | PFI Input Threshold (Falling)                                                                                                                          | •         | 492.5             | 500                  | 507.5                              | mV                         |

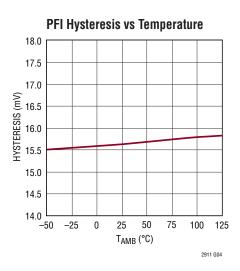

| $\Delta V_{PFT}$       | PFI Hysteresis                                           |                                                                                                                                                        | •         | 10                | 15                   | 19                                 | mV                         |

| V <sub>CC,OP</sub>     | Minimum Operating Voltage to Guarantee PFO High (Note 3) | V <sub>PFI</sub> = 0.55V                                                                                                                               | •         |                   |                      | 2.3                                | V                          |

| I <sub>V1</sub>        | V1 input Current (Note 4)                                | V1 = 3.3V, V1 > V2                                                                                                                                     | •         | 10                | 30                   | 80                                 | μА                         |

|                        |                                                          | V1 = 3.3V, V1 < V2                                                                                                                                     | •         | 3                 | 10                   | 30                                 | μА                         |

| I <sub>V2</sub>        | V2 Input Current (Note 4)                                | V2 = 5V (LTC2911-1)<br>V2 = 2.5V (LTC2911-2)<br>V2 = 1.8V (LTC2911-3)<br>V2 = 1.2V (LTC2911-4)<br>V2 = 0.55V (LTC2911-5)<br>C-Grade/I-Grade<br>H-Grade | • • • • • | 10<br>3<br>2<br>2 | 35<br>10<br>10<br>10 | 80<br>30<br>30<br>30<br>±15<br>±40 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>nA |

| I <sub>ADJ</sub>       | ADJ Input Current                                        | $V_{ADJ} = 0.55V$ (C-Grade) (I-Grade)<br>$V_{ADJ} = 0.55V$ (H-Grade)                                                                                   | •         |                   |                      | ±15<br>±40                         | nA<br>nA                   |

| I <sub>PFI</sub>       | PFI Input Current                                        | V <sub>PFI</sub> = 0.55V (C-Grade) (I-Grade)<br>V <sub>PFI</sub> = 0.55V (H-Grade)                                                                     | •         |                   |                      | ±15<br>±40                         | nA<br>nA                   |

| I <sub>TMR(UP)</sub>   | TMR Pull-Up Current                                      | V <sub>TMR</sub> = 1V                                                                                                                                  | •         | -1.5              | -2.2                 | -2.9                               | μА                         |

| I <sub>TMR(DOWN)</sub> | TMR Pull-Down Current                                    | V <sub>TMR</sub> = 1V                                                                                                                                  | •         | 1.5               | 2.2                  | 2.9                                | μА                         |

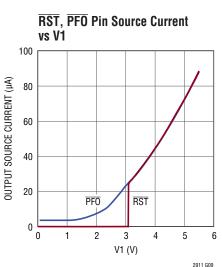

| I <sub>PU</sub>        | RST, PFO Pull-Up Current                                 | V <sub>PIN</sub> = 0V                                                                                                                                  | •         | -20               | -29                  | -40                                | μА                         |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{ADJ} = 0.55V$ , $V_{PFI} = 0.55V$ , $V_{1} = 3.3V$ unless otherwise noted. (Notes 2, 3)

| SYMBOL                  | PARAMETER                                                                                      | CONDITIONS                                                                                      |   | MIN       | MIN TYP              |                      | UNITS       |

|-------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---|-----------|----------------------|----------------------|-------------|

| t <sub>P,PF</sub>       | PFI Comparator Propagation Delay to PFO                                                        | V <sub>PFI</sub> Driven Beyond Threshold<br>V <sub>PFT</sub> by More Than 10%                   | • | 8         | 30                   | 80                   | μs          |

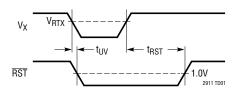

| t <sub>UV</sub>         | V1, V2, ADJ Undervoltage Detect to RST Low                                                     | V <sub>X</sub> Less Than Threshold V <sub>RTX</sub> by<br>More Than 10%                         | • | 8         | 30                   | 80                   | μs          |

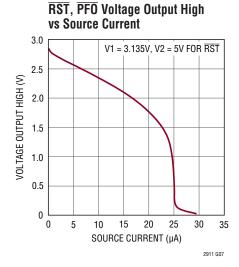

| V <sub>OH</sub>         | RST, PFO Output Voltage High (Note 5)                                                          | I <sub>RST</sub> = −1μA                                                                         | • | V1 – 1    |                      | V1                   | V           |

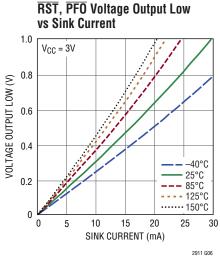

| $V_{0L}$                | RST, PFO Output Voltage Low (Note 6)                                                           | $V_{CC} = 0.5V$ , $I = 5\mu A$<br>$V_{CC} = 1V$ , $I = 100\mu A$<br>$V_{CC} = 3V$ , $I = 2.5mA$ | • |           | 0.01<br>0.01<br>0.10 | 0.15<br>0.15<br>0.30 | V<br>V<br>V |

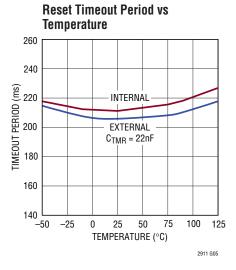

| t <sub>RST(EXT)</sub>   | Reset Timeout Period, External                                                                 | C <sub>TMR</sub> = 2.2nF                                                                        | • | 15        | 20                   | 27                   | ms          |

| t <sub>RST(INT)</sub>   | Reset Timeout Period, Internal                                                                 | V <sub>TMR</sub> = V1                                                                           | • | 140       | 200                  | 280                  | ms          |

| V <sub>TMR(INT)</sub>   | Timer Internal Mode Threshold                                                                  | V <sub>TMR</sub> Rising                                                                         | • | V1 – 0.40 | V1 - 0.020           | V1 – 0.10            | V           |

| $\Delta V_{TMR(INT)}$   | Timer Internal Mode Hysteresis                                                                 | V <sub>TMR</sub> Falling                                                                        | • | 40        | 100                  | 160                  | mV          |

| V <sub>TMR(LATCH)</sub> | Timer Latch Mode Threshold                                                                     | V <sub>TMR</sub> Falling                                                                        | • | 0.10      | 0.20                 | 0.40                 | V           |

| $\Delta V_{TMR(LATCH)}$ | Timer Latch Mode Hysteresis                                                                    | V <sub>TMR</sub> Rising                                                                         | • | 40        | 75                   | 160                  | mV          |

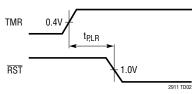

| t <sub>P,LR</sub>       | Latch Release Propagation Delay to RST Low                                                     | V <sub>TMR</sub> Rising, Step 0V to 0.6V                                                        | • |           | 0.5                  | 3                    | μs          |

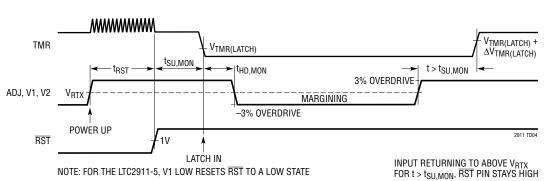

| t <sub>SU,MON</sub>     | Monitor Input Setup Time to Latch Enable (Note 7)<br>Monitor Input Setup Time to Latch Release | V <sub>TMR</sub> Falling, Step 0.6V to 0V<br>V <sub>TMR</sub> Rising, Step 0V to 0.6V           | • | 2         |                      |                      | ms          |

| t <sub>HD, MON</sub>    | Monitor Input Hold Time to Latch Enable<br>Monitor Input Hold Time to Latch Release            | V <sub>TMR</sub> Falling, Step 0.6V to 0V<br>V <sub>TMR</sub> Rising, Step 0V to 0.6V           | • | 0         |                      |                      | μѕ          |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive; all voltages are referenced to GND unless otherwise noted.

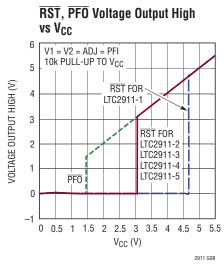

**Note 3:** The internal supply voltage ( $V_{CC}$ ) is generated from the greater of the voltages on the V1 and V2 inputs.  $V_{CC}$  = V1 for the LTC2911-5.

**Note 4:** Under typical operating conditions, quiescent current is drawn from the greater of the voltages on the V1 and V2 inputs. For the LTC2911-5 only V1 supplies the quiescent current.

**Note 5:** The  $\overline{RST}$  and  $\overline{PFO}$  output pins on the LTC2911 have internal pullups to V1. However, for faster rise times or for V<sub>OH</sub> voltages greater than V1, use an external pull-up resistor.

**Note 6:** The  $\overline{RST}$  and  $\overline{PFO}$  pull-down currents are derived from V1 and V2 except for the LTC2911-5 where the pull-down strength is derived only from V1.

**Note 7:**  $t_{SU,MON}$  is required to latch a low  $\overline{RST}$  state and  $t_{SU,MON}$  +  $t_{RST}$  is required to latch a high  $\overline{RST}$  state.

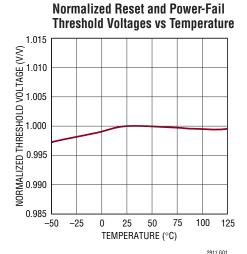

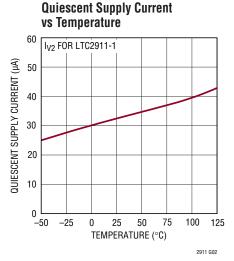

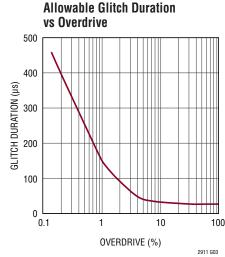

## TYPICAL PERFORMANCE CHARACTERISTICS

2911f

## PIN FUNCTIONS

**ADJ:** Adjustable Voltage Monitor Input. Input to a voltage monitor comparator with a 0.5V nominal threshold. Tie to V1 if unused.

**Exposed Pad (DFN Only):** Exposed pad may be left open or connected to device ground.

**GND:** Device Ground.

**PFI:** Power-Fail Voltage Monitor Input. Input to the powerfail comparator with a 500mV threshold at the falling edge and a 515mV threshold at the rising edge, giving a 3% hysteresis for noise rejection. Tie to V1 or GND if unused.

**PFO**: Power-Fail Logic Output. This pin asserts low when the PFI input voltage is below its threshold and goes high when the PFI input voltage is above its threshold. This pin provides a weak pull-up current to V1. This current is typically  $29\mu A$  at V1 = 3.3V. The pin can be pulled to voltages higher than V1 by external pull-up resistors.  $\overline{PFO}$  provides an early warning signal of a system power failure.

**RST**: Reset Logic Output. This pin asserts low when any of the V1, V2, or ADJ inputs are below their reset thresholds. Pulls high when all the monitored inputs are above their thresholds for longer than a timeout period. This pin provides a weak pull-up current to V1. This current is typically  $29\mu A$  at V1 = 3.3V. The pin can be pulled to voltages higher than V1 by external pull-up resistors. The status of RST can be latched by holding the TMR pin at GND.

**TMR:** Reset Timeout Control. Attach an external capacitor,  $C_{TMR}$ , to GND to set a reset timeout period of 9.4ms/nF. A low leakage ceramic capacitor is recommended for timer accuracy. A 2.2nF capacitor generates a 20ms timeout. Leaving the TMR pin open without a capacitor generates a minimum timeout of approximately 400 $\mu$ s which will vary depending on the parasitic capacitance on the pin. Tying this pin to V1 enables the internal 200ms timeout. Pulling this pin to GND latches the reset state.

**V1:** 3.3V Monitor and Power Supply Input. V1 is an accurate 3.3V, -5% undervoltage supply monitor. The internal V<sub>CC</sub> is generated from the greater of the voltages at the V1 and V2 inputs for the LTC2911-1/LTC2911-2/LTC2911-3/LTC2911-4 options. The LTC2911-5 option always derives its power supply from the V1 pin. Bypass this pin to GND with a  $0.1\mu F$  (or greater) capacitor for the LTC2911-2 through LTC2911-5.

**V2:** Voltage Monitor and Power Supply Input. V2 is a -5% undervoltage supply monitor for a 5V, 2.5V, 1.8V or 1.2V supply for the LTC2911-1/LTC2911-2/LTC2911-3/LTC2911-4 options, respectively. Because the internal V<sub>CC</sub> is generated from the greater of the V1 and V2 inputs for these options, the V2 pin should be bypassed to GND with a 0.1μF (or greater) capacitor for the LTC2911-1. The V2 pin of the LTC2911-5 is a high impedance input with a 0.5V threshold, allowing the trip threshold of the monitored supply to be configured with a resistive divider.

## **BLOCK DIAGRAM**

## TIMING DIAGRAMS

#### **Undervoltage and Reset Timing**

#### Power-Fail Timing

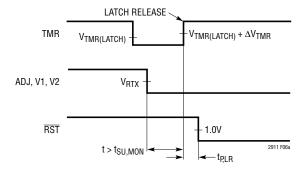

#### Latch Release to RST Low Timing

NOTE: ADJ FORCED LOW BEFORE TMR RELEASE

## Latching RST High

#### Input Valid to Latch Enable Setup and Hold Timing

#### Input Valid to Latch Release Setup Timing

## Latching RST Low

#### Input Invalid to Latch Enable **Input Invalid to Latch Setup and Hold Timing Release Setup Timing** V<sub>TMR(LATCH)</sub> + **TMR** V<sub>TMR(LATCH)</sub> ΔV<sub>TMR</sub>(LATCH) t<sub>HD,MON</sub> $t > t_{SU,MON}$ t<sub>SU,MON</sub> tuv · 3% OVERDRIVE MARGINING ADJ, V1, V2 $V_{\text{RTX}}$ $V_{RTX}$ -3% OVERDRIVE -3% OVERDRIVE RST LATCH IN NOTE: FOR THE LTC2911-5, V1 LOW RESETS RST TO A LOW STATE INPUT RETURNING TO BELOW VRTX FOR $t > t_{SU,MON}$ , $\overline{RST}$ PIN STAYS LOW

2911f

The LTC2911 is a low power, high accuracy triple supply monitor with power-fail comparator. For the LTC2911-1, LTC2911-2, LTC2911-3 and LTC2911-4 options, the V1 and V2 pins monitor two supplies. Their thresholds are preset internally based on the option chosen. A resistive divider connected to the ADJ pin configures the third threshold. For the LTC2911-5, the V2 pin is a high impedance adjustable input similar to the ADJ pin.

Reset timeout of the device may be selected with an external capacitor or set to an internally generated 200ms. The ADJ, V1 and V2 inputs must be valid (above their thresholds) for longer than the reset timeout period before the RST pin transitions high.

The power-fail comparator causes the PFO pin to pull low when the PFI pin falls below 0.5V. A resistive divider connected to the PFI pin configures the threshold of the monitored voltage. The PFO output typically provides an early warning of imminent power failure so that the system may begin shutdown procedures such as supply sequencing and/or storage of system state in nonvolatile memory.

#### Power-Up

The LTC2911-1, LTC2911-2, LTC2911-3 and LTC2911-4 supervisors are powered from the V1 and V2 pins, automatically selecting the pin with the higher potential. The exception in the device family, the LTC2911-5, derives its internal supply voltage ( $V_{CC}$ ) only from V1. When all monitor inputs are above their thresholds, the quiescent supply current drawn from  $V_{CC}$  is typically  $30\mu A$  ( $35\mu A$  for the LTC2911-1). When the three monitor inputs (V1, V2 and ADJ) rise above their thresholds, the appropriate timeout delay begins, after which  $\overline{RST}$  pulls to V1. Once the PFI input rises above 515mV, the  $\overline{PFO}$  output signals high indicating that the supply or voltage monitored by PFI is above threshold.

The LTC2911 uses proprietary low voltage drive circuitry for the  $\overline{RST}$  and  $\overline{PFO}$  pins which holds them low with  $V_{CC}$  (the higher of V1 and V2) as low as 0.5V. This helps prevent indeterminate voltages from appearing on the outputs during power-up. For additional details refer to the Output Pin Characteristics section.

When V1 and V2 are ramped simultaneously (for LTC2911-1/LTC2911-2/LTC2911-3/LTC2911-4), the pull-down current from the  $\overline{RST}$  and  $\overline{PFO}$  pins is about twice the current available when V1 or V2 is grounded.

#### **Power Down**

On power-down, when the voltage monitored by the power-fail comparator falls below the threshold configured by its resistive divider, the  $\overline{PFO}$  pin pulls low to provide an early warning of imminent power failure. In a typically configured system, this occurs before the supplies monitored by V1, V2 or ADJ fall below their thresholds and cause the  $\overline{RST}$  pin to pull low. The  $\overline{RST}$  and  $\overline{PFO}$  pins maintain a logic low output for V<sub>CC</sub> as low as 0.5V. See the Output PIn Characteristics section for additional details.

## Power-Fail Monitoring and PFO Signaling

The LTC2911's PFI input monitors a voltage through a resistive divider and compares it to the internal power-fail threshold. When PFI drops below 0.50V (the power-fail threshold) the  $\overline{PFO}$  output pulls low to provide an early warning of a low voltage condition. When the PFI pin rises above 0.515V again, the  $\overline{PFO}$  output signals high indicating a valid supply condition.

The PFI input typically monitors the primary power supply of a system. For example, the PFI pin may monitor the input supply of a DC/DC converter or a Li-Ion battery stack voltage. The PFO output typically provides a warning to the system that the power supply is on the verge of failing so that it can prepare for a controlled shutdown. For

example, the PFO pin may connect to a processor non-maskable interrupt. When the battery pack voltage drops below the shutdown threshold, as sensed at PFI, the PFO pin pulls low to issue an interrupt. Next, the processor begins shutdown procedures which may include supply sequencing and/or storage/erasure of system state in nonvolatile memory.

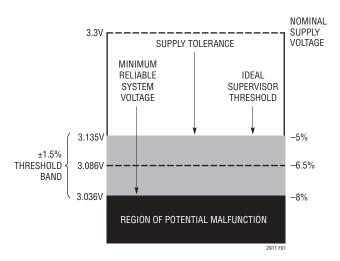

#### **Threshold Accuracy**

Specifying the minimum supply voltage for a system requires the designer to consider three factors: minimum supply voltage for proper operation, power supply tolerance, and supervisor reset threshold accuracy. Highly accurate supervisors ease the design challenge by decreasing the overall voltage margin required for reliable system operation.

The reset threshold band and the power supply tolerance bands should not overlap. This prevents false or nuisance resets when the power supply is actually within its specified tolerance band. The actual reset threshold of supervisors varies over a specified band. The LTC2911 supervisor varies  $\pm 1.5\%$  around its nominal threshold voltage over temperature.

Figure 1 illustrates a typical 3.3V monitor. The LTC2911 has  $\pm 1.5\%$  reset threshold accuracy. The nearest practical supervisor trip point is the sum of power supply tolerance and the LTC2911 tolerance. So a "5%" threshold is typically set to -6.5%, excluding resistor errors. Thus for a 3.3V "5%" threshold, the practical supervisor trip point is at 3.086V. The threshold is guaranteed to lie in the band between 3.036V and 3.135V over the operating temperature range. This 3.135V maximum threshold is at the lower limit of supply tolerance (3.3V -5%) to prevent false tripping.

The system must operate reliably a little below 3.036V (or 3.3V, -8%), or risk malfunction before a reset signal is properly issued. A less accurate supervisor increases the supply voltage tolerance requirements and the risk of system malfunction. The LTC2911's ±1.5% threshold voltage specification minimizes these requirements.

#### V1 and V2 Supply Monitors

All the LTC2911 options have a V1 threshold equal to 3.086V (3.3V-6.5%). The V2 thresholds are 4.675V (5V-6.5%), 2.338V (2.5V-6.5%), 1.683V (1.8V-6.5%) and 1.122V (1.2V-6.5%) for options LTC2911-1,

Figure 1. 1.5% Threshold Accuracy Improves System Reliability

LTC2911-2, LTC2911-3 and LTC2911-4 respectively. V2 of the LTC2911-5 option is a high impedance input with a nominal 0.5V threshold.

#### Input Noise Filtering for RST

The V1, V2 and ADJ comparators have a response time that is inversely proportional to overdrive. This characteristic is illustrated in the Typical Performance Characteristics as the graph Allowable Glitch Duration versus Overdrive. The ADJ and the LTC2911-5's V2 pin may be bypassed with a capacitor to increase the filtering in applications that demand it. The resultant RC lowpass filter at the inputs will further reject high frequency components, at the cost of slowing the monitor's response to fault conditions.

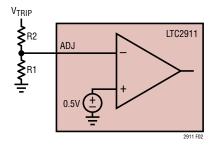

#### **Resistor Selection for ADJ**

The threshold of the supply monitored by the ADJ pin is configured with an external resistive divider (R2 and R1) connected between the supply and ground. The tap point for the divider is connected to the adjustable input (ADJ) which has a 0.5V threshold. (See Figure 2)

Normally, the user selects a trip voltage based on the supply and acceptable tolerances, and a value of R1 based on current drawn. For a given current, I, R1 is given by:

$$R1 = \frac{0.5V}{I}$$

To minimize errors arising from the ADJ input bias current, a value of less than 100k is recommended for R1.

R2 is then chosen by:

$$R2 = R1 \bullet \left( \frac{V_{TRIP\_ADJ}}{0.5V} - 1 \right)$$

where,  $V_{TRIP\_ADJ}$  is the supply threshold when the ADJ pin falls below its 0.5V threshold.

For accurate monitoring, the resistor tolerance should be as small as possible. Resistor tolerance of 0.1% or some trimming of components should be considered for R2/R1 in applications that require an accurate trip point.

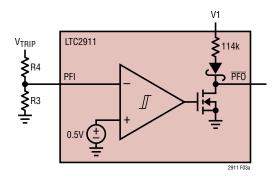

#### **Resistor Selection for PFI**

An external resistive divider (R3 and R4) connected between the supply and ground configures the threshold of the supply monitored by the power-fail comparator. The tap point for the divider is connected to the PFI input which has a 0.5V threshold. (See Figure 3a)

Resistor selection follows a process similar to that for the ADJ pin.

R3 is given by:

$$R3 = \frac{0.5V}{I}$$

Figure 2. Setting the Adjustable (ADJ) Trip Point

Figure 3a. Setting the Power-Fail (PFI) Trip Point

Again, to minimize errors arising from the PFI input bias current, a value of less than 100k is recommended for R3.

R4 can be chosen either using the PFI falling threshold or the PFI rising threshold.

For the falling edge threshold, use the equation:

$$R4 = R3 \bullet \left( \frac{V_{TRIP\_PFI\_FALL}}{0.5V} - 1 \right)$$

Alternatively, for the rising edge threshold, use the equation:

$$R4 = R3 \bullet \left( \frac{V_{TRIP\_PFI\_RISE}}{0.515V} - 1 \right)$$

where  $V_{TRIP\_PFI\_FALL}$  is the supply threshold when the PFI pin falls below the 0.5V falling threshold, and  $V_{TRIP\_PFI\_RISE}$  is the supply threshold when the PFI pin rises above the 0.515V rising threshold.

Note that  $V_{TRIP\_PFI\_RISE}$  is typically 3% above the  $V_{TRIP\_PFI\_FALL}$  due to the fact that the PFI 515mV rising threshold is 3% above its 500mV falling threshold.

In applications that require an accurate trip point, the R4 and R3 resistors should have small tolerances.

#### Hysteresis for Power-Fail Comparator

The power-fail comparator uses a positive 3% accurate hysteresis to combat spurious triggering while maintaining accurate thresholds for both the rising and falling

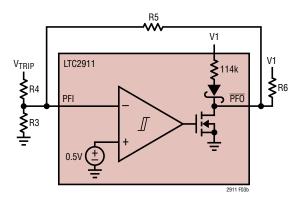

Figure 3b. Increasing Power-Fail Hysteresis

edges. The nominal threshold is 500mV at the falling edge and 515mV at the rising edge. The hysteresis prevents oscillation when the monitored voltage passes through the thresholds. If the PFI pin is connected to an external resistive divider, it may be bypassed with a capacitor for additional noise filtering.

#### **Increasing the Power-Fail Hysteresis**

The power-fail comparator hysteresis can be increased by adding two resistors, R5 and R6, as shown in Figure 3b. When  $\overline{PFO}$  is low, R5 sinks current from the center tap of the R3 and R4 resistive divider. The upper threshold is therefore given by:

$$V_{H} = 0.515V \left(1 + \frac{R4}{R3} + \frac{R4}{R5}\right)$$

When PFO is high, the series combination of R5 and R6 sources current into the center tap of the R3 and R4 resistive divider. This leads to a lower threshold of:

$$V_L = 0.5V \left(1 + \frac{R4}{R3}\right) - \frac{\left(3.3V - 0.5V\right)R4}{R5 + R6}$$

The addition of R5 and R6 increases the hysteresis to:

$$\begin{split} V_{HYST} &= V_H - V_L \\ &= 0.015 \bigg(1 + \frac{R4}{R3}\bigg) + 0.515 \bigg(\frac{R4}{R5}\bigg) + \frac{\big(3.3V - 0.5V\big)R4}{R5 + R6} \end{split}$$

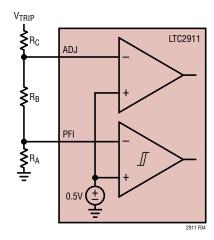

# Resistor Selection for Combined Reset and Power-Fail Divider

When the power-fail and reset signals are based on the same supply, the PFI and ADJ inputs may be connected to a single resistive divider formed from three resistors. The configuration is shown in Figure 4. For a given bias current I,  $R_A$ ,  $R_B$  and  $R_C$  can be calculated from:

$$R_{A} = \frac{0.5V}{I}$$

$$R_{B} = R_{A} \cdot \left( \frac{V_{TRIP\_PFI\_FALL}}{V_{TRIP\_ADJ}} - 1 \right)$$

$$R_{C} = R_{A} \cdot \left( \frac{V_{TRIP\_ADJ}}{0.5V} - 1 \right) \cdot \left( \frac{V_{TRIP\_PFI\_FALL}}{V_{TRIP\_ADJ}} \right)$$

For example, consider monitoring a 5V,  $\pm 5\%$  supply with  $V_{TRIP\_PFI\_FALL} = 4.5V$  and  $V_{TRIP\_ADJ} = 4V$ . The resulting  $V_{TRIP\_PFI\_RISE}$  is equal to 4.63V or 3% above  $V_{TRIP\_PFI\_FALL}$ . The maximum  $V_{TRIP\_PFI\_RISE}$  should not overlap the minimum power supply voltage level for  $\overline{PFO}$  to deassert when the supply recovers. Mathematically, after factoring in the sum of the power supply tolerance and the LTC2911 tolerance, the  $V_{TRIP\_PFI\_RISE}$  should be lower than 5V-6.5%.

See Threshold Accuracy section for more details. In the design, if we wish to consume about  $5\mu A$  in the divider,  $R_A$  = 100k. We then find  $R_B$  = 12.4k and  $R_C$  = 787k (nearest 1% standard values).

### **Setting the Reset Timeout**

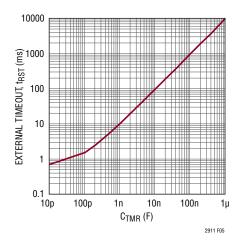

RST goes high after the V1, V2 and ADJ inputs are above their thresholds for a reset timeout period. Connecting the TMR pin to V1 enables the internal 200ms timer. To configure a different reset timeout period connect a capacitor between the TMR pin and ground.

The following formula approximates the value of capacitor needed for a particular timeout:

$$C_{TMR} = t_{RST} \cdot 106.5 [pF/ms]$$

Leaving the TMR pin open with no external capacitor generates a reset timeout of approximately 400µs. Larger capacitors may be used to increase the timeout, but the capacitor leakage current must not exceed 500nA. Otherwise, the timer accuracy will be severely affected.

Suitable values of  $C_{TMR}$  for a given  $t_{RST}$  may be selected from Figure 5.

Figure 4. Combining PFI/ADJ Monitoring of One Supply with Three Resistors

Figure 5. External Timeout vs  $C_{TMR}$

#### **Reset Latch Mode**

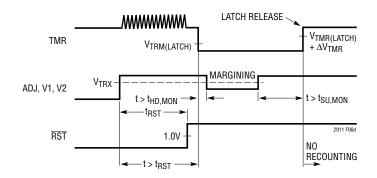

At any time, the TMR pin can be pulled low to latch the RST pin status, overriding the reset operation. This feature is useful when testing a system at supply voltages that might otherwise cause the RST pin to assert.

If the RST pin is unasserted (high) before the latch is enabled (by pulling the TMR pin low), RST will remain unasserted after the TMR pin is released. This is true provided that all reset monitor inputs are valid when TMR releases, regardless of their state while the TMR pin was low. However, if RST was unasserted before TMR was pulled low, and now one of the inputs is invalid when TMR is released, RST will assert after a tpl\_LR propagation delay (see Figure 6a). Conversely, if RST was asserted (low)

was enabled. The reset latch mode is useful for performing supply margining tests without resetting the system (see Figure 6d).

At least 2.9µA of pull-up or pull-down current is required to hold the TMR pin high or low to configure the internal timer or reset latch mode. However, during the timer mode transition, 100µA will be required to switch the TMR floating state to ground or V1. Connecting the TMR pin to any

voltage other than ground or V1 may have unpredictable

results.

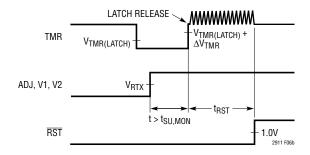

before TMR was pulled low, and all inputs are valid when TMR is released, RST will deassert (go high) after a t<sub>RST</sub>

delay (see Figures 6b and 6c). The RST pin remains as-

serted for a full t<sub>RST</sub> timeout after the TMR pin is released,

regardless of the state of the t<sub>RST</sub> timer before the latch

Figure 6a. Input Toggled Low While Timer Latched. RST Goes Low t<sub>PLR</sub> After Latch Release

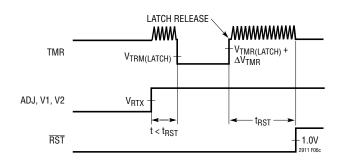

Figure 6c. Timer Latched Before Timeout. After Latch Release, RST Stays Low for a Full Timeout Before Going High

Figure 6b. Input Toggled High While Timer Latched.

RST Goes High t<sub>RST</sub> After Latch Release

Figure 6d. Timer Latched After Timeout and RST High.

RST Stays High After Margining if Inputs are Restored

Before Release

During power-up, with a capacitor connected to the TMR pin, the part remains in the reset latch mode described above until the 2.2 $\mu$ A flowing out of the TMR pin charges the capacitor beyond the V<sub>TMR(LATCH)</sub> threshold. For this reason, large capacitors will extend the RST timeout during power-up. For example, if C<sub>TMR</sub> = 1 $\mu$ F, the LTC2911 leaves the reset latch mode 90ms after power-up and the RST pin goes high after a 9 second timeout.

Figures 7a and 7b show how the TMR pin can be driven low to latch the state of the  $\overline{RST}$  pin or floated or driven high for external and internal reset timing, respectively.

Figure 7a. Open-Drain (or Three-State Buffer) Output. Grounds TMR to Latch the State of RST. Floats TMR for External Reset Timing

Figure 7b. V1 Powered Inverter. Grounds TMR to Latch the State of RST. Drives TMR High for Internal Reset Timing

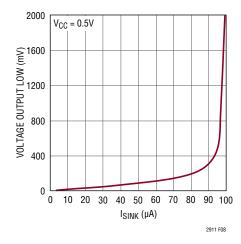

Figure 8. Voltage Output Low vs  $I_{SINK}$  at  $V_{CC} = 0.5V$

#### **Output Pin Characteristics**

The DC characteristics of the  $\overline{RST}$  and  $\overline{PFO}$  pull-down strength are shown in the Typical Performance Characteristics. The circuits that drive the pull-down of the output pins are powered by the internal  $V_{CC}$  (the greater voltage of V1 or V2). During power-up, a  $V_{CC}$  of at least 0.5V ensures a low output state. The  $V_{OL}$  voltage depends on the current sunk by  $\overline{RST}$  and  $\overline{PFO}$  as shown in the Figure 8. The open-drain nature of the  $\overline{RST}$  and  $\overline{PFO}$  pins allows for wire-ORed connections. For example, multiple LTC2911s may be wire-ORed to monitor additional supplies, or opendrain logic can be connected to allow other conditions to issue the reset and/or power-fail signals.

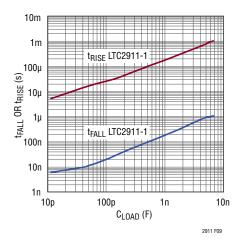

## **Output Pin Rise and Fall Time**

The open-drain output pins ( $\overline{RST}$  and  $\overline{PFO}$ ) contain weak pull-up circuitry to V1. Use an external pull-up resistor when the outputs need to pull beyond V1 and/or require a faster rise time. Use external pull-up resistor values of 100k or less.

When output pins are externally pulled up to voltages higher than V1, an internal network automatically protects the weak pull-up circuitry from reverse currents. For a given external load capacitance or  $C_{LOAD}$ , the rise and fall times can be estimated using Figure 9. The output pins have very strong pull-down capability. With a 150pF load capacitance the reset line can pull down in about 30ns.

Figure 9. t<sub>RISE</sub> and t<sub>FALL</sub> vs C<sub>LOAD</sub>

## TYPICAL APPLICATIONS

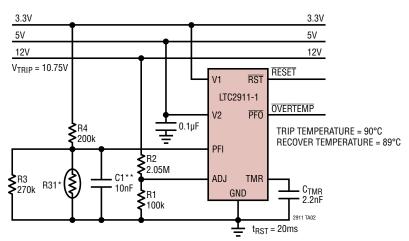

#### **Triple Supply Monitor and Overtemperature Signal**

- \*THERMISTOR MURATA NTC NCP15WM474J03RC TOLERANCE 5%.

NTC RESISTANCE IS 474k AT ROOM, 35.8k AT 85°C

\*\*OPTIONAL BYPASS CAPACITOR FOR SUPPLY TRANSIENT NOISE FILTERING

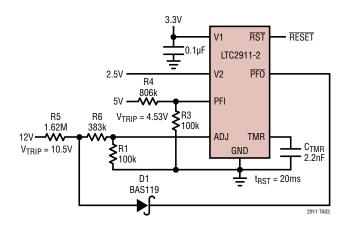

#### **Quad Supply Monitor**

## TYPICAL APPLICATIONS

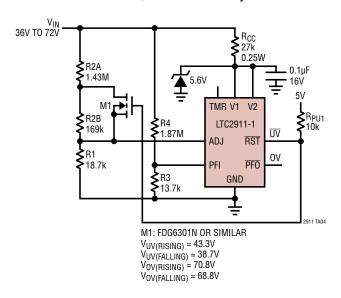

#### 48V Telecom UV/OV Monitor with Hysteresis

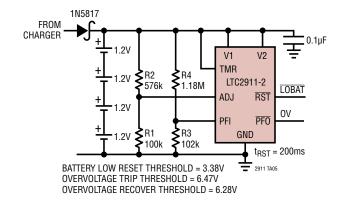

#### 4-Cell NiMH Stack Voltage Monitor with Input Overvoltage Signaling

#### 4-Cell Alkaline Stack Voltage Monitor with Early Power-Fail Warning

POWER-FAIL FALLING THRESHOLD = 3.90V POWER-FAIL RISING THRESHOLD = 4.02V RESET THRESHOLD = 3.39V

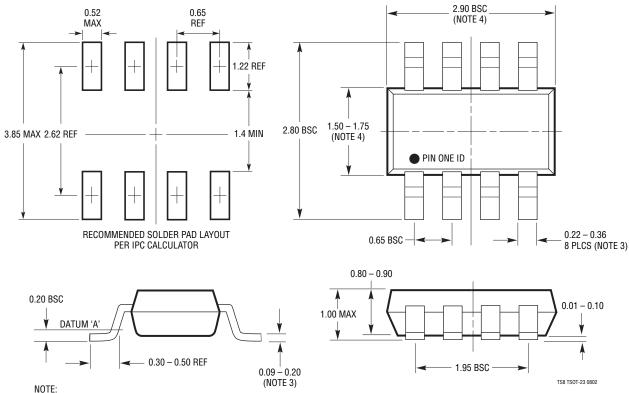

## PACKAGE DESCRIPTION

#### TS8 Package 8-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1637)

- 1. DIMENSIONS ARE IN MILLIMETERS

- 2. DRAWING NOT TO SCALE

- 3. DIMENSIONS ARE INCLUSIVE OF PLATING

- 4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

- 5. MOLD FLASH SHALL NOT EXCEED  $0.254 \mathrm{mm}$

- 6. JEDEC PACKAGE REFERENCE IS MO-193

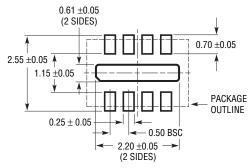

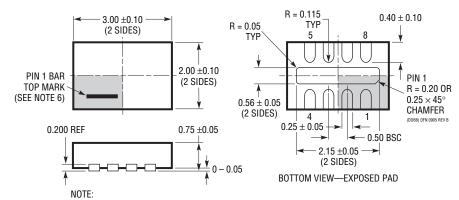

## PACKAGE DESCRIPTION

# $\begin{array}{c} \text{DDB Package} \\ \text{8-Lead Plastic DFN (3mm} \times \text{2mm)} \end{array}$

(Reference LTC DWG # 05-08-1702 Rev B)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

- 1. DRAWING CONFORMS TO VERSION (WECD-1) IN JEDEC PACKAGE OUTLINE M0-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# TYPICAL APPLICATION

Triple Supply Monitor with Early Power-Fail Warning (With Manual Reset and Latchable Reset for Margining)

## **RELATED PARTS**

| PART NUMBER                         | DESCRIPTION                                                          | COMMENTS                                                                                                               |

|-------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| LTC1326/LTC1326-2.5                 | Micropower Precision Triple Supply Monitor for 5V/2.5V, 3.3V and ADJ | 4.725V, 3.118V, 1V Threshold (±0.75%)                                                                                  |

| LTC1536                             | Precision Triple Supply Monitor for PCI Applications                 | Meets PCI t <sub>FAIL</sub> Timing Specifications                                                                      |

| LTC1726-2.5/LTC1726-5               | Micropower Triple Supply Monitor for 2.5V/5V, 3.3V and ADJ           | Adjustable Reset and Watchdog Timeouts                                                                                 |

| LTC1727/LTC1728                     | Micropower Triple Supply Monitor With Open-Drain Reset               | Individual Monitor Outputs in MSOP/5-Lead SOT-23                                                                       |

| LTC1985-1.8                         | Micropower Triple Supply Monitor with Push-Pull Reset<br>Output      | 5-Lead SOT-23 Package                                                                                                  |

| LTC2909                             | Precision, Triple/Dual Input UV, OV and Negative Voltage<br>Monitor  | 8-Lead SOT-23 and DFN Packages                                                                                         |

| LTC2912/LTC2913/<br>LTC2914         | Single/Dual/Quad UV and OV Voltage Monitors                          | Separate V <sub>CC</sub> Pin, Adjustable Reset Timer, H-Grade Temperature Range                                        |

| LTC2915/LTC2916/<br>LTC2917/LTC2918 | Single Voltage Monitor With 27 Unique Thresholds                     | Manual Reset, Watchdog, TSOT-8/MSOP-10 and 3mm × 2mm DFN Packages, H-Grade Temperature Range                           |

| LTC2919                             | Precision, Triple/Dual Input UV, OV and Negative Voltage<br>Monitor  | 10-Lead 3mm × 2mm and MSOP Packages, H-Grade Temperature Range (Individual Outputs for ADJ Comparators and System RST) |