# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### FEATURES

- Triple I<sup>2</sup>C Adjustable High Efficiency Step-Down DC/ DC Converters: 1.6A, 1A/1.2A, 1A/1.2A

- High Efficiency 1.2A Buck-Boost DC/DC Converter

- Triple 250mA LDO Regulators

- Pushbutton ON/OFF Control with System Reset

- Flexible Pin-Strap Sequencing Operation

- I<sup>2</sup>C and Independent Enable Control Pins

- Power Good and Reset Outputs

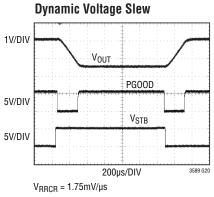

- Dynamic Voltage Scaling and Slew Rate Control

- Selectable 2.25MHz or 1.12MHz Switching Frequency

- Always-Alive 25mA LDO Regulator

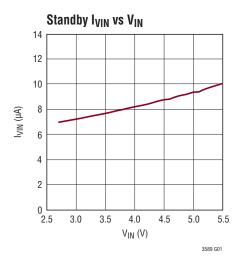

- 8µA Standby Current

- 40-Pin 6mm × 6mm × 0.75mm QFN

### **APPLICATIONS**

- Handheld Instruments and Scanners

- Portable Industrial Devices

- Automotive Infotainment

- Medical Devices

- High End Consumer Devices

- Multirail Systems

- Supports Freescale i.MX53/51, Marvell PXA and Other Application Processors

### DESCRIPTION

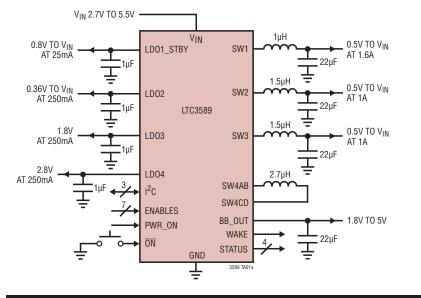

The LTC<sup>®</sup>3589 is a complete power management solution for ARM and ARM-based processors and advanced portable microprocessor systems. The device contains three step-down DC/DC converters for core, memory and SoC rails, a buck-boost regulator for I/O at 1.8V to 5V and three 250mA LDO regulators for low noise analog supplies. An I<sup>2</sup>C serial port is used to control enables, output voltage levels, dynamic voltage scaling, operating modes and status reporting. Differences between the LTC3589, LTC3589-1, and LTC3589-2 are summarized in Table 1.

Regulator start-up is sequenced by connecting outputs to enable pins in the desired order or programmed via the  $I^2C$  port. System power-on, power-off, and reset functions are controlled by pushbutton interface, pin inputs, or  $I^2C$ interface.

The LTC3589 supports i.MX53/51, PXA and OMAP processors with eight independent rails at appropriate power levels. Other features include interface signals such as the VSTB pin that simultaneously toggle up to four rails between programmed run and standby output voltages. The device is available in a low profile 40-pin 6mm × 6mm exposed pad QFN package.

**Δ7**, LT, LTC, LTM, Burst Mode, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### TYPICAL APPLICATION

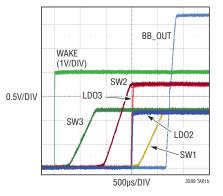

#### Start-Up Sequence

TECHNOLOGY

### TABLE OF CONTENTS

| Features                                                | 1  |

|---------------------------------------------------------|----|

| Applications                                            |    |

| Typical Application                                     | 1  |

| Description                                             | 1  |

| Absolute Maximum Ratings                                | 3  |

| Pin Configuration                                       | 3  |

| Order Information                                       |    |

| Electrical Characteristics                              | 4  |

| Typical Performance Characteristics                     | 9  |

| Pin Functions                                           | 13 |

| Block Diagram                                           |    |

| Operation                                               | 16 |

| Introduction                                            |    |

| LTC3589, LTC3589-1, and LTC3589-2 Functional Comparison | 17 |

| Always-On LDO                                           |    |

| Step-Down Switching Regulators                          | 20 |

| Buck-Boost Switching Regulator                          | 24 |

| Slewing DAC Reference Operation                         | 28 |

| Pushbutton Operation                                    | 29 |

| Enable and Power-On Sequencing                          | 31 |

| Fault Detection, Shutdown, and Reporting                | 32 |

| I <sup>2</sup> C Operation                              | 36 |

| Thermal Considerations and Board Layout                 | 42 |

| Typical Application                                     |    |

| Package Description                                     |    |

| Revision History                                        | 49 |

| Typical Application                                     |    |

| Related Parts                                           |    |

|                                                         |    |

3589fg

### ABSOLUTE MAXIMUM RATINGS (Notes 1, 3)

$\begin{array}{l} \mathsf{V}_{\text{IN}}, \mathsf{DV}_{\text{DD}}, \mathsf{SW1}, \mathsf{SW2}, \mathsf{SW3}, \mathsf{SW4AB}, \mathsf{SW4CD}, \ldots -0.3 \mathsf{V} \text{ to } 6 \mathsf{V} \\ \mathsf{SW1}, \mathsf{SW2}, \mathsf{SW3}, \mathsf{SW4AB}, \mathsf{SW4CD} \\ (\text{Transients} < 1 \mu \mathsf{s}, \text{Duty Cycle} < 5 \%), \ldots, -2 \mathsf{V} \text{ to } 7 \mathsf{V} \\ \mathsf{PV}_{\text{IN1}}, \mathsf{PV}_{\text{IN2}}, \mathsf{PV}_{\text{IN3}}, \mathsf{PV}_{\text{IN4}}, \ldots, -0.3 \mathsf{V} \text{ to } \mathsf{V}_{\text{IN}} + 0.3 \mathsf{V} \\ \mathsf{V}_{\text{IN}\_\text{LD02}}, \mathsf{V}_{\text{IN}\_\text{LD034}}, \mathsf{PV}_{\text{IN4}}, \ldots, -0.3 \mathsf{V} \text{ to } \mathsf{V}_{\text{IN}} + 0.3 \mathsf{V} \\ \mathsf{LD01\_\text{STBY}}, \text{ LD01\_\text{FB}}, \text{ BUCK1\_\text{FB}}, \text{ BUCK2\_\text{FB}}, \\ \mathsf{BUCK3\_\text{FB}}, \text{ BB\_\text{FB}}, \text{ BB\_\text{OUT}}, \text{ LD02}, \text{ LD02\_\text{FB}}, \text{ LD03}, \end{array}$

| LDO4, PGOOD, VSTB, EN1, EN2, EN3, EN4, EN_LDO2, |

|-------------------------------------------------|

| EN_LD034, EN_LD03, ON, PBSTAT, WAKE, RSTO,      |

| PWR_ON, IRQ,0.3V to 6V                          |

| SDA, SCL– $0.3V$ to $DV_{DD}$ + $0.3V$          |

| Operating Junction Temperature Range            |

| (Note 2)–40°C to 150°C                          |

| Storage Temperature Range–65°C to 150°C         |

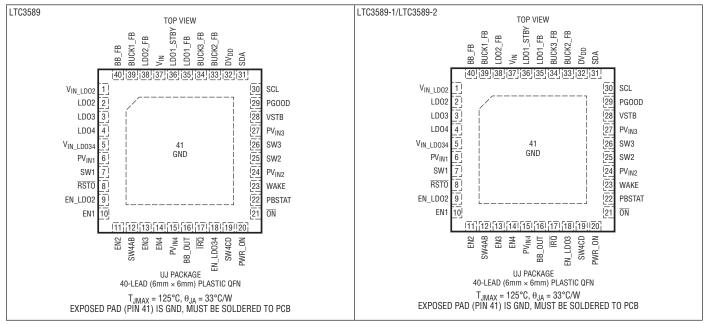

## PIN CONFIGURATION

### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC3589EUJ#PBF   | LTC3589EUJ#TRPBF   | LTC3589UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589IUJ#PBF   | LTC3589IUJ#TRPBF   | LTC3589UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589HUJ#PBF   | LTC3589HUJ#TRPBF   | LTC3589UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 150°C    |

| LTC3589EUJ-1#PBF | LTC3589EUJ-1#TRPBF | LTC3589UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589IUJ-1#PBF | LTC3589IUJ-1#TRPBF | LTC3589UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589HUJ-1#PBF | LTC3589HUJ-1#TRPBF | LTC3589UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 150°C    |

| LTC3589EUJ-2#PBF | LTC3589EUJ-2#TRPBF | LTC3589UJ-2   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589IUJ-2#PBF | LTC3589IUJ-2#TRPBF | LTC3589UJ-2   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589HUJ-2#PBF | LTC3589HUJ-2#TRPBF | LTC3589UJ-2   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

### **ELECTRICAL CHARACTERISTICS**

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                        | CONDITIONS                                                 |   | MIN        | ТҮР        | MAX   | UNITS   |

|----------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|---|------------|------------|-------|---------|

| V <sub>IN</sub>      | Operating Input Supply Voltage, VIN                                                              |                                                            | • | 2.7        |            | 5.5   | V       |

| ISTANDBY             | V <sub>IN</sub> Standby Current                                                                  | All Enables = 0V, PWR_ON = 0V, I <sub>LD01</sub> = 0mA     | • |            | 8          | 18    | μA      |

| f <sub>OSC</sub>     | Oscillator Frequency                                                                             |                                                            | • | 1.8        | 2.25       | 2.6   | MHz     |

| Step-Down            | Switching Regulators 1, 2, and 3                                                                 |                                                            |   |            |            |       | ·       |

| I <sub>VIN</sub>     | Pulse-Skipping Mode V <sub>IN</sub> Quiescent Current                                            | V <sub>FB</sub> = 0.85V (Note 5)                           |   |            | 120        | 200   | μA      |

|                      | per Buck<br>Burst Mode <sup>®</sup> V <sub>IN</sub> Quiescent Current per Buck                   |                                                            | • |            | 23         | 40    | μA      |

| I <sub>FB</sub>      | Feedback Pin Input Current                                                                       | V <sub>FB</sub> = 0.8V                                     |   | -50        |            | 50    | nA      |

| D <sub>X</sub>       | Maximum Duty Cycle                                                                               | V <sub>FB</sub> = 0V                                       |   | 100        |            |       | %       |

| R <sub>SW</sub>      | SW Pull-Down Resistance                                                                          | Regulators Disabled                                        |   |            | 2.5        |       | kΩ      |

| t <sub>SS</sub>      | Soft-Start Rate                                                                                  | (Note 6)                                                   |   |            | 0.8        |       | V/ms    |

| V <sub>FB(MAX)</sub> | Maximum Feedback Voltage                                                                         | BxDTV1 = BxDTV2 = 11111,<br>V <sub>IN</sub> = 2.7V to 5.5V | • | 0.735      | 0.75       | 0.765 | V       |

| V <sub>FB(LSB)</sub> | Feedback LSB Step Size                                                                           |                                                            |   |            | 12.5       |       | mV      |

| V <sub>FB(MIN)</sub> | Minimum Feedback Voltage                                                                         | BxDTV1 = BxDTV2 = 00000,<br>V <sub>IN</sub> = 2.7V to 5.5V | • | 0.351      | 0.3625     | 0.374 | V       |

| 1.6A Step-           | Down Switching Regulator 1                                                                       |                                                            |   |            |            |       |         |

| I <sub>LIM1</sub>    | Peak PMOS Current Limit SW1                                                                      |                                                            |   | 2.0        | 2.7        |       | A       |

| RP1                  | R <sub>DS(ON)</sub> of PMOS1                                                                     | I <sub>SW1</sub> = -100mA                                  |   |            | 180        |       | mΩ      |

| RN1                  | R <sub>DS(ON)</sub> of NMOS1                                                                     | I <sub>SW1</sub> = 100mA                                   |   |            | 110        |       | mΩ      |

| 1.0A/1.2A            | Step-Down Switching Regulators 2 and 3                                                           | ·                                                          |   |            |            |       |         |

| I <sub>LIM2, 3</sub> | Peak PMOS Current Limit SW2 and SW3 (LTC3589)<br>Peak PMOS Current Limit SW2 and SW3 (LTC3589-1/ |                                                            | • | 1.5<br>1.8 | 1.9<br>2.3 |       | A       |

| <br>RP2, 3           | LTC3589-2)<br>R <sub>DS(ON)</sub> of PMOS2 and PMOS3                                             | I <sub>SW1</sub> = -100mA                                  | - | 1.0        | 2.5        |       | A<br>mΩ |

| RN2, 3               | R <sub>DS(0N)</sub> of NMOS2 and NMOS3<br>R <sub>DS(0N)</sub> of NMOS2 and NMOS3                 | I <sub>SW1</sub> = 100mA                                   |   |            | 130        |       | mΩ      |

| -                    | Boost Switching Regulator 4 (Buck-Boost)                                                         |                                                            |   |            | 130        |       | 11152   |

|                      | PWM Mode V <sub>IN</sub> Quiescent Current                                                       | V <sub>BB FB</sub> = 0.85V (Note 5)                        |   |            | 115        | 170   | μA      |

|                      | Burst Mode VIN Quiescent Current                                                                 |                                                            | • |            | 19         | 35    | μA      |

| V <sub>BB_FB</sub>   | Feedback Voltage                                                                                 | V <sub>IN</sub> = 2.7V to 5.5V                             | • | 0.776      | 0.8        | 0.824 | V       |

| V <sub>OUTBB</sub>   | Output Voltage Range                                                                             |                                                            |   | 1.8        |            | 5.0   | V       |

| I <sub>LIM4</sub>    | Peak PMOS Current Limit SW4AB                                                                    |                                                            |   | 2.3        | 2.9        |       | A       |

| I <sub>PEAK4</sub>   | Forward Burst Current Limit (Switch A)                                                           | Burst Mode Operation                                       |   |            | 600        |       | mA      |

| I <sub>LIMR4</sub>   | Reverse Current Limit (Switch D)                                                                 |                                                            |   |            | 1          |       | A       |

| I <sub>ZER04</sub>   | Reverse Burst Current Limit (Switch D)                                                           | Burst Mode Operation                                       |   |            | 0          |       | mA      |

| RP4                  | R <sub>DS(ON)</sub> of Switch A and Switch D                                                     | I <sub>SW4AB</sub> = I <sub>SW4CD</sub> = 100mA            |   |            | 160        |       | mΩ      |

| RN4                  | R <sub>DS(ON)</sub> of Switch B and Switch C                                                     | $I_{SW4AB} = I_{SW4CD} = -100 \text{mA}$                   |   |            | 110        |       | mΩ      |

| R <sub>OUT4</sub>    | BB_OUT Pull-Down Resistance                                                                      | Regulator Disabled                                         |   |            | 2.5        |       | kΩ      |

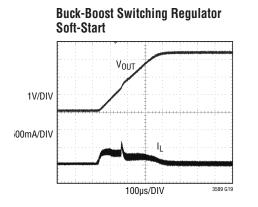

| t <sub>SS</sub>      | Soft-Start Rate                                                                                  | (Note 6)                                                   |   |            | 2          |       | V/ms    |

| I <sub>FB</sub>      | Feedback Pin Input Current                                                                       | V <sub>FB</sub> = 0.85V                                    |   | -50        |            | 50    | nA      |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL                 | PARAMETER                                                                                              | CONDITIONS                                                                                                                   |   | MIN            | ТҮР        | MAX                                | UNITS    |

|------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---|----------------|------------|------------------------------------|----------|

| LDO Regulat            | ors                                                                                                    | I                                                                                                                            |   |                |            |                                    | 1        |

| t <sub>LDO_SS</sub>    | Soft-Start Time LD02, LD03, LD04                                                                       |                                                                                                                              |   |                | 100        |                                    | μs       |

| R <sub>LDO PD</sub>    | Output Pull-Down Resistance LD02, LD03, LD04                                                           | LDO Disabled                                                                                                                 |   |                | 2.5        |                                    | kΩ       |

| Always-On R            | egulator (LDO1_STBY)                                                                                   |                                                                                                                              |   |                |            |                                    |          |

| V <sub>LD01_FB</sub>   | LDO1 Feedback Voltage                                                                                  |                                                                                                                              |   | 0.76           | 0.8        | 0.84                               | V        |

| V <sub>LD01</sub>      | LD01 Line Regulation                                                                                   | $I_{LD01\_STBY}$ = 1mA, LD01_STBY = 1.2V,<br>V <sub>IN</sub> = 2.7V to 5.5V                                                  |   |                | 0.15       |                                    | %/V      |

|                        | LD01 Load Regulation                                                                                   | I <sub>LD01</sub> = 0.1mA to 25mA,<br>LD01_STBY = 1.2V                                                                       |   |                | 0.1        |                                    | %        |

| I <sub>LD01</sub>      | Available Output Current                                                                               |                                                                                                                              |   | 25             |            |                                    | mA       |

| I <sub>LD01_SC</sub>   | Short-Circuit Output Current Limit                                                                     |                                                                                                                              |   |                | 65         | 100                                | mA       |

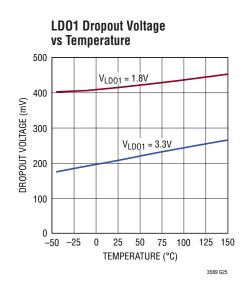

| V <sub>DR0P1</sub>     | Dropout Voltage (Note 4)                                                                               | I <sub>LD01</sub> = 25mA, LD01_STBY = 3.3V                                                                                   |   |                | 200        |                                    | mV       |

| I <sub>LD01_FB</sub>   | LD01_FB Input Current                                                                                  | V <sub>LD01 FB</sub> = 0.85V                                                                                                 |   | -50            |            | 50                                 | nA       |

| LDO Regulat            | or 2 (LDO2)                                                                                            | . –                                                                                                                          |   |                |            |                                    |          |

| V <sub>IN_LD02</sub>   | V <sub>IN LDO2</sub> Input Voltage Range                                                               |                                                                                                                              |   | 1.7            |            | V <sub>IN</sub>                    | V        |

| I <sub>VIN_LD02</sub>  | V <sub>IN_LD02</sub> Quiescent Current<br>V <sub>IN_LD02</sub> Shutdown Current                        | Regulator Enabled<br>Regulator Disabled                                                                                      | • |                | 12<br>0    | 20<br>1                            | μA<br>μA |

| I <sub>VIN</sub>       | V <sub>IN</sub> Quiescent Current                                                                      | EN_LD02 = High                                                                                                               |   |                | 50         | 85                                 | μA       |

| V <sub>FB2(MAX)</sub>  | LDO2 Maximum Feedback Voltage                                                                          | L2DTV1 = L2DTV2 = 11111                                                                                                      |   | 0.735          | 0.75       | 0.765                              | V        |

| V <sub>FB2(LSB)</sub>  | LDO2 Feedback LSB Step Size                                                                            |                                                                                                                              |   |                | 12.5       |                                    | mV       |

| V <sub>FB2(MIN)</sub>  | LDO2 Minimum Feedback Voltage                                                                          | $ \begin{array}{l} L2DTV1 = L2DTV2 = 00000 \\ V_{IN\_LD02} = V_{IN} = 2.7V \mbox{ to } 5.5V, \\ I_{LD02} = 1mA \end{array} $ | • | 0.351          | 0.3625     | 0.374                              | V        |

|                        | LD02 Line Regulation                                                                                   | I <sub>LD02</sub> =1mA, V <sub>IN_LD02</sub> = 2.7V to 5.5V                                                                  |   |                | 0.01       |                                    | %/V      |

|                        | LDO2 Load Regulation                                                                                   | I <sub>LD02</sub> = 1mA to 250mA                                                                                             |   |                | 0.01       |                                    | %        |

| I <sub>LD02</sub>      | LDO2 Available Output Current                                                                          |                                                                                                                              |   | 250            |            |                                    | mA       |

| I <sub>LD02_SC</sub>   | LDO2 Short-Circuit Current Limit                                                                       |                                                                                                                              |   | 300            | 450        | 600                                | mA       |

| V <sub>DR0P2</sub>     | Dropout Voltage (Note 4)                                                                               | I <sub>LD02</sub> = 200mA, V <sub>LD02</sub> = 2.5V<br>I <sub>LD02</sub> = 200mA, V <sub>LD02</sub> = 1.2V                   |   |                | 140<br>350 | 180<br>500                         | mV<br>mV |

| ILD02_FB               | LD02_FB Input Current                                                                                  | $V_{LD02 FB} = 0.8V$                                                                                                         |   | -50            |            | 50                                 | nA       |

| LDO Regulat            | or 3 (LDO3)                                                                                            | · · -                                                                                                                        |   |                |            |                                    |          |

| V <sub>IN_LD034</sub>  | V <sub>IN_LD034</sub> Input Range (LTC3589)<br>V <sub>IN_LD034</sub> Input Range (LTC3589-1/LTC3589-2) |                                                                                                                              | • | 2.35<br>3.0    |            | V <sub>IN</sub><br>V <sub>IN</sub> | V<br>V   |

| I <sub>VIN_LD034</sub> | V <sub>IN_LD034</sub> Quiescent Current<br>V <sub>IN_LD034</sub> Shutdown Current                      | Regulator Enabled<br>Regulator Disabled                                                                                      | • |                | 15<br>0    | 29<br>1                            | μA<br>μA |

| I <sub>VIN</sub>       | V <sub>IN</sub> Quiescent Current                                                                      | EN_LD03 = High                                                                                                               |   |                | 50         | 85                                 | μA       |

| V <sub>LD03</sub>      | LDO3 Output Voltage (LTC3589)<br>LDO3 Output Voltage (LTC3589-1/LTC3589-2)                             | $V_{IN\_LD034}$ = $V_{IN}$ = 2.7V to 5V, $I_{LD03}$ = 1mA                                                                    | • | 1.746<br>2.716 | 1.8<br>2.8 | 1.854<br>2.884                     | V<br>V   |

|                        | LD03 Line Regulation                                                                                   | I <sub>LD03</sub> =1mA, V <sub>IN_LD034</sub> = 2.7V to 5.5V                                                                 |   |                | 0.01       |                                    | %/V      |

|                        | LDO3 Load Regulation                                                                                   | I <sub>LDO3</sub> = 1mA to 250mA                                                                                             |   |                | 0.05       |                                    | %        |

| I <sub>LD03</sub>      | LDO3 Available Output Current                                                                          |                                                                                                                              |   | 250            |            |                                    | mA       |

| I <sub>LD03_SC</sub>   | LD03 Short-Circuit Current Limit                                                                       |                                                                                                                              |   | 300            | 450        | 600                                | mA       |

| V <sub>DROP3</sub>     | LDO3 Dropout Voltage (LTC3589) (Note 4)<br>LDO3 Dropout Voltage (LTC3589-1/LTC3589-2)<br>(Note 4)      | I <sub>LD03</sub> = 200mA, V <sub>LD03</sub> = 1.8V<br>I <sub>LD03</sub> = 200mA, V <sub>LD03</sub> = 2.8V                   |   |                | 190<br>140 | 250<br>180                         | mV<br>mV |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL                                               | PARAMETER                                                                                              | CONDITIONS                                                                                                                                                                                                                               |   | MIN                              | ТҮР                      | MAX                                | UNITS                                  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------|--------------------------|------------------------------------|----------------------------------------|

| LDO Regulat                                          | or 4 (LDO4)                                                                                            |                                                                                                                                                                                                                                          |   |                                  |                          |                                    |                                        |

| V <sub>IN_LD034</sub>                                | V <sub>IN_LD034</sub> Input Range (LTC3589)<br>V <sub>IN_LD034</sub> Input Range (LTC3589-1/LTC3589-2) |                                                                                                                                                                                                                                          | • | 2.35<br>1.7                      |                          | V <sub>IN</sub><br>V <sub>IN</sub> | V<br>V                                 |

| I <sub>VIN_LD034</sub>                               | V <sub>IN_LD034</sub> Quiescent Current<br>V <sub>IN_LD034</sub> Shutdown Current                      | Regulator Enabled<br>Regulator Disabled                                                                                                                                                                                                  | • |                                  | 14<br>0                  | 24<br>1                            | μA<br>μA                               |

| I <sub>VIN</sub>                                     | V <sub>IN</sub> Quiescent Current                                                                      | EN_LDO4 = High                                                                                                                                                                                                                           |   |                                  | 50                       | 85                                 | μA                                     |

| V <sub>LD04</sub><br>(LTC3589)                       | LDO 4 Output Voltage                                                                                   | I <sub>LD04</sub> = 1mA, L2DTV2[6:5] = 00<br>L2DTV2[6:5] = 01<br>L2DTV2[6:5] = 10<br>L2DTV2[6:5] = 11                                                                                                                                    | • | 2.716<br>2.425<br>1.746<br>3.201 | 2.8<br>2.5<br>1.8<br>3.3 | 2.884<br>2.575<br>1.854<br>3.399   | V<br>V<br>V<br>V                       |

| V <sub>LD04</sub><br>(LTC3589-1)<br>(LTC3589-2)      | LDO 4 Output Voltage                                                                                   | I <sub>LD04</sub> = 1mA, L2DTV2[6:5] = 00<br>L2DTV2[6:5] = 01<br>L2DTV2[6:5] = 10<br>L2DTV2[6:5] = 11                                                                                                                                    | • | 1.164<br>1.746<br>2.425<br>3.104 | 1.2<br>1.8<br>2.5<br>3.2 | 1.236<br>1.854<br>2.575<br>3.296   | V<br>V<br>V<br>V                       |

|                                                      | LD04 Line Regulation                                                                                   | $I_{LD04} = 1$ mA, $V_{IN\_LD034} = 2.7$ V to 5.5V,<br>$V_{OUT} = 1.8$ V                                                                                                                                                                 |   |                                  | 0.01                     |                                    | %/V                                    |

|                                                      | LDO4 Load Regulation                                                                                   | I <sub>LD04</sub> = 1mA to 250mA                                                                                                                                                                                                         |   |                                  | 0.05                     |                                    | %                                      |

| I <sub>LDO4</sub>                                    | LDO4 Available Output Current                                                                          |                                                                                                                                                                                                                                          |   | 250                              |                          |                                    | mA                                     |

| I <sub>LD04_SC</sub>                                 | LDO4 Short-Circuit Current Limit                                                                       |                                                                                                                                                                                                                                          |   | 300                              | 450                      | 600                                | mA                                     |

| V <sub>DROP4</sub>                                   | LDO4 Dropout Voltage (Note 4)                                                                          | $ \begin{array}{l} I_{LD04} = 200 \text{mA}, \ V_{LD04} = 3.3 \text{V} \\ I_{LD04} = 200 \text{mA}, \ V_{LD04} = 1.8 \text{V} \\ I_{LD04} = 200 \text{mA}, \ V_{LD04} = 3.2 \text{V} \ (\text{LTC3589-1}/\text{LTC3589-2}) \end{array} $ |   |                                  | 120<br>190<br>120        | 160<br>250<br>160                  | mV<br>mV<br>mV                         |

| Enable Inputs                                        | 3                                                                                                      |                                                                                                                                                                                                                                          |   |                                  |                          |                                    |                                        |

| V <sub>ENx_THR</sub>                                 | Threshold Rising                                                                                       | All Enables Low                                                                                                                                                                                                                          |   |                                  | 0.8                      | 1.2                                | V                                      |

| V <sub>ENx_THR2</sub><br>V <sub>ENx_THF2</sub>       | Threshold Rising<br>Threshold Falling                                                                  | Any Enable High<br>Any Enable High                                                                                                                                                                                                       | • | 0.420                            | 0.5<br>0.45              | 0.530                              | V<br>V                                 |

| R <sub>ENX</sub>                                     | Input Pull-Down Resistance                                                                             |                                                                                                                                                                                                                                          |   |                                  | 4.5                      |                                    | MΩ                                     |

| VSTB, PWR_                                           | ON Inputs                                                                                              | 1                                                                                                                                                                                                                                        |   |                                  |                          |                                    |                                        |

| V <sub>VSTB_THR</sub><br>V <sub>VSTB_THF</sub>       | VSTB Pin Threshold Rising<br>VSTB Pin Threshold Falling                                                |                                                                                                                                                                                                                                          | • | 0.4                              | 0.8<br>0.7               | 1.2                                | V<br>V                                 |

| R <sub>VSTB</sub>                                    | Pull-Down Resistance                                                                                   |                                                                                                                                                                                                                                          |   |                                  | 4.5                      |                                    | MΩ                                     |

| V <sub>PWR_ONTHR</sub><br>V <sub>PWR_ONTHF</sub>     | PWR_ON Pin Threshold Rising<br>PWR_ON Pin Threshold Falling                                            |                                                                                                                                                                                                                                          | • | 0.4                              | 0.8<br>0.7               | 1.2                                | V<br>V                                 |

| R <sub>PWR_ON</sub>                                  | Pull-Down Resistance                                                                                   |                                                                                                                                                                                                                                          |   |                                  | 4.5                      |                                    | MΩ                                     |

| I <sup>2</sup> C Port                                |                                                                                                        |                                                                                                                                                                                                                                          |   |                                  |                          |                                    |                                        |

| DV <sub>DD</sub>                                     | DV <sub>DD</sub> Input Supply Voltage                                                                  |                                                                                                                                                                                                                                          |   | 1.6                              |                          | 5.5                                | V                                      |

| IDVDD                                                | DV <sub>DD</sub> Quiescent Current                                                                     | SCL/SDA = 0kHz                                                                                                                                                                                                                           |   |                                  | 0.5                      |                                    | μA                                     |

| V <sub>DVDD_UVL0</sub>                               | DV <sub>DD</sub> UVLO Level                                                                            |                                                                                                                                                                                                                                          |   |                                  | 0.8                      |                                    | V                                      |

| ADDRESS                                              | Device Address – Write<br>Device Address – Read                                                        |                                                                                                                                                                                                                                          |   |                                  | 01101000<br>01101001     |                                    |                                        |

| V <sub>IH</sub> SDA, SCL<br>V <sub>IL</sub> SDA, SCL |                                                                                                        |                                                                                                                                                                                                                                          |   | 70                               |                          | 30                                 | %DV <sub>DD</sub><br>%DV <sub>DD</sub> |

| I <sub>IHSCx</sub> I <sub>ILSCx</sub>                | SDA and SCL Input Current                                                                              | SDA = SCL = 0V to 5.5V                                                                                                                                                                                                                   |   | -250                             |                          | 250                                | nA                                     |

| V <sub>OL</sub> SDA                                  | SDA Output Low Voltage                                                                                 | I <sub>SDA</sub> = 3mA                                                                                                                                                                                                                   | • |                                  |                          | 0.4                                | V                                      |

| f <sub>SCL</sub>                                     | SCL Clock Operating Frequency                                                                          |                                                                                                                                                                                                                                          |   |                                  |                          | 400                                | kHz                                    |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25$ °C (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL                    | PARAMETER                                                                | CONDITIONS                                                                     |   | MIN                    | ТҮР          | MAX | UNITS    |

|---------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|---|------------------------|--------------|-----|----------|

| t <sub>su_sta</sub>       | Repeated Start Condition Set-Up Time                                     |                                                                                |   | 0.6                    |              |     | μs       |

| t <sub>SU_STO</sub>       | Stop Condition Set-Up Time                                               |                                                                                |   | 0.6                    |              |     | μs       |

| t <sub>HD_DAT(0)</sub>    | Data Hold Time Output                                                    |                                                                                |   | 0                      |              | 900 | ns       |

| t <sub>HD_DAT(I)</sub>    | Data Hold Time Input                                                     |                                                                                |   | 0                      |              |     | ns       |

| t <sub>SU_DAT</sub>       | Data Set-Up Time                                                         |                                                                                |   | 100                    |              |     | ns       |

| t <sub>LOW</sub>          | SCL Clock Low Period                                                     |                                                                                |   | 1.3                    |              |     | μs       |

| t <sub>HIGH</sub>         | SCL Clock High Period                                                    |                                                                                |   | 0.6                    |              |     | μs       |

| t <sub>f</sub>            | Data Fall Time                                                           | $C_B$ = Capacitance of One BUS Line (pF)                                       |   | 20 + 0.1C <sub>B</sub> |              | 300 | ns       |

| t <sub>r</sub>            | Data Rise Time                                                           | $C_B$ = Capacitance of One BUS Line (pF)                                       |   | 20 + 0.1C <sub>B</sub> |              | 300 | ns       |

| t <sub>SP</sub>           | Input Spike Suppression Pulse Width                                      |                                                                                |   |                        |              | 50  | ns       |

| Pushbutton I              | nterface                                                                 | 1                                                                              |   | 1                      |              |     |          |

| $V_{\overline{ON}_{THR}}$ | ON Threshold Rising                                                      |                                                                                | • |                        | 0.8          | 1.2 | V        |

| V <sub>ON_THF</sub>       | ON Threshold Falling                                                     |                                                                                | • | 0.4                    | 0.7          |     | V        |

| I                         | ON Input Current                                                         | $\begin{vmatrix} \overline{ON} &= V_{IN} \\ \overline{ON} &= 0V \end{vmatrix}$ |   | -100                   | 40           | 100 | nA<br>μA |

| ton pbstat1               | ON Low Time to PBSTAT Low                                                |                                                                                |   |                        | 50           |     | ms       |

| ton_pbstatt               | ON Description   ON High                                                 |                                                                                |   |                        | 0.2          |     | μs       |

| ton_pastatz               | ON Low Time to WAKE High                                                 |                                                                                |   |                        | 400          |     | ms       |

|                           | ON Low Time to Hard Reset                                                |                                                                                |   |                        | 5            |     | s        |

| tpbstat_pw                | PBSTAT Minimum Pulse Width                                               |                                                                                |   |                        | 50           |     | ms       |

| tpbstat_bk                | PBSTAT Blanking from WAKE Low                                            |                                                                                |   |                        | 1            |     | s        |

| twake off                 | Minimum WAKE Low Time                                                    |                                                                                |   |                        | 1            |     | S        |

| twake_on                  | WAKE High Time with PWR_ON = 0V                                          |                                                                                |   |                        | 5            |     | s        |

| tpwr_on                   | PWR_ON to WAKE High (LTC3589)                                            |                                                                                | + |                        | 50           |     | ms       |

|                           | PWR_ON to WAKE High (LTC3589-1/LTC3589-2)                                |                                                                                |   |                        | 2            |     | ms       |

| t <sub>PWR_OFF</sub>      | PWR_ON to WAKE Low (LTC3589)<br>PWR_ON to WAKE Low (LTC3589-1/LTC3589-2) |                                                                                |   |                        | 50<br>2      |     | ms<br>ms |

| Status Outpu              | t Pins (PBSTAT, WAKE, PGOOD, RSTO, IRQ)                                  |                                                                                |   |                        |              |     |          |

| V <sub>PBSTAT</sub>       | PBSTAT Output Low Voltage                                                | I <sub>PBSTAT</sub> = 3mA                                                      |   |                        | 0.1          | 0.4 | V        |

| I <sub>PBSTAT</sub>       | PBSTAT Output High Leakage Current                                       | V <sub>PBSTAT</sub> = 3.8V                                                     |   | -0.1                   |              | 0.1 | μA       |

| V <sub>WAKE</sub>         | WAKE Output Low Voltage                                                  | I <sub>WAKE</sub> = 3mA                                                        |   |                        | 0.1          | 0.4 | V        |

| I <sub>WAKE</sub>         | WAKE Output High Leakage Current                                         | V <sub>WAKE</sub> = 3.8V                                                       |   | -0.1                   |              | 0.1 | μA       |

| V <sub>PGOOD</sub>        | PGOOD Output Low Voltage                                                 | I <sub>PGOOD</sub> = 3mA                                                       |   |                        | 0.1          | 0.4 | V        |

| I <sub>PGOOD</sub>        | PGOOD Output High Leakage Current                                        | V <sub>PGOOD</sub> = 3.8V                                                      |   | -0.1                   |              | 0.1 | μA       |

| V <sub>PGOOD</sub>        | PGOOD Threshold Rising<br>PGOOD Threshold Falling                        |                                                                                |   |                        | 6<br>8       |     | %        |

| V <sub>NRSTO</sub>        | LD01 Power Good Threshold Rising<br>LD01 Power Good Threshold Falling    |                                                                                |   |                        | 6<br>8       |     | %        |

| V <sub>UVLO</sub>         | Undervoltage Lockout Rising<br>Undervoltage Lockout Falling              |                                                                                |   |                        | 2.65<br>2.55 | 2.7 | V<br>V   |

### **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the specified operating iunction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Note 2). V<sub>IN</sub> = PV<sub>IN1</sub> = PV<sub>IN2</sub> = PV<sub>IN3</sub> = PV<sub>IN4</sub> = V<sub>IN\_LD02</sub> = V<sub>IN\_LD034</sub> =  $DV_{DD}$  = 3.8V. All regulators disabled unless otherwise noted.

| SYMBOL              | PARAMETER                                                   | CONDITIONS                  | MIN  | ТҮР      | MAX | UNITS |

|---------------------|-------------------------------------------------------------|-----------------------------|------|----------|-----|-------|

| V <sub>UVWARN</sub> | Undervoltage Warning Rising<br>Undervoltage Warning Falling |                             |      | 3<br>2.9 |     |       |

| V <sub>RSTO</sub>   | RSTO Output Low Voltage                                     | I <sub>RSTO</sub> = 3mA     |      | 0.1      | 0.4 | V     |

| IRSTO               | RSTO Output High Leakage Current                            | V <sub>RST0</sub> = 3.8V    | -0.1 |          | 0.1 | μA    |

| VIRQ                | IRQ Output Low Voltage                                      | I <sub>IRQ</sub> = 3mA      |      | 0.1      | 0.4 | V     |

| IIRQ                | IRQ Output High Leakage Current                             | $V_{\overline{IRQ}} = 3.8V$ | -0.1 |          | 0.1 | μA    |

Note 1: Stresses beyond those listed Under Absolute Maximum ratings may cause permanent damage to the device. Exposure to any Absolute Maximum rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3589 are tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3589E are guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3589I are guaranteed over the -40°C to 125°C operating junction temperature range and the LTC3589H are guaranteed over the full -40°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than  $125^{\circ}$ C. The junction temperature (T<sub>1</sub>) in °C) is calculated from the ambient temperature (T<sub>A</sub> in °C) and power dissipation (PD, in Watts) according to the formula:

$T_J = T_A + (PD \bullet \theta_{JA})$ , where the package junction to ambient thermal impedance  $\theta_{JA} = 33^{\circ}C/W$ .

Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

Note 3: The LTC3589 include overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating temperature may impair device reliability.

Note 4: Dropout voltage is defined as  $(V_{IN} - V_{LDO})$  for LDO1 or  $(V_{IN\_LD0} - V_{LD0})$  for other LDOs when  $V_{LD0}$  is 3% lower than  $V_{LD0}$ measured with  $V_{IN} = V_{IN\_LDO} = 4.3V$ .

**Note 5:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency.

Note 6: Soft-start measured in test mode with regulator error amplifier in unity gain mode.

3589fc

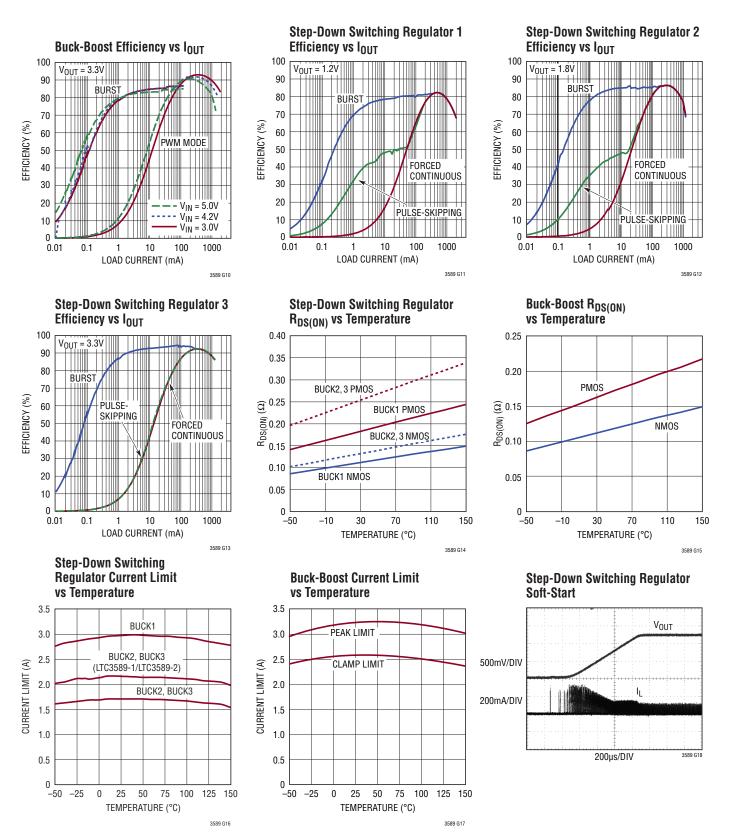

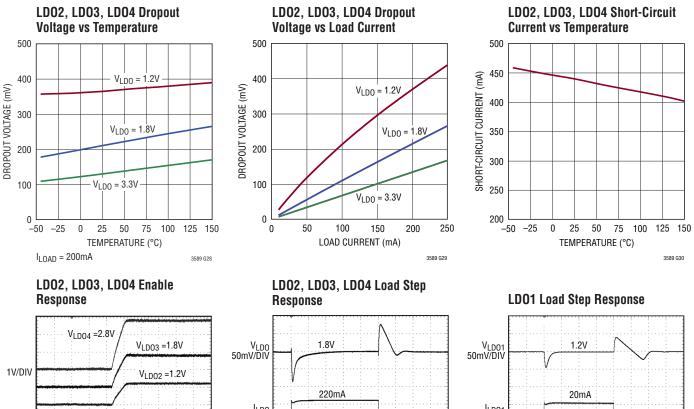

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 3.8V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

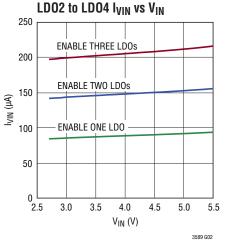

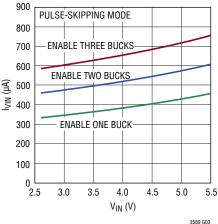

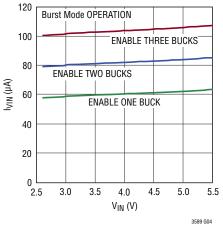

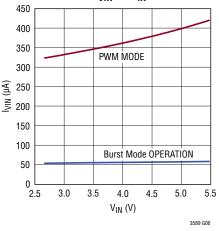

Step-Down Switching Regulator  $I_{VIN} \ vs \ V_{IN}$

Step-Down Switching Regulator I<sub>VIN</sub> vs V<sub>IN</sub>

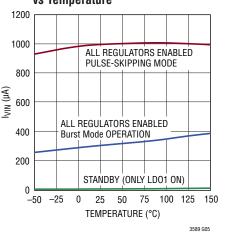

Input Supply Current vs Temperature

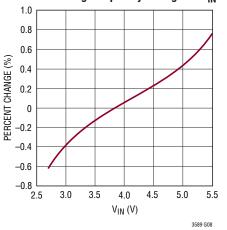

Buck-Boost I<sub>VIN</sub> vs V<sub>IN</sub>

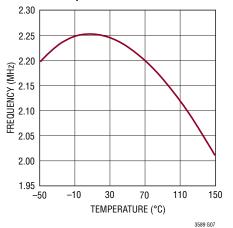

Oscillator Frequency vs Temperature

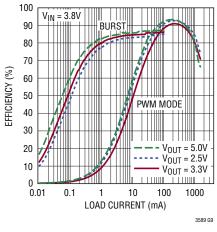

Buck-Boost Efficiency vs I<sub>OUT</sub>

3589fg

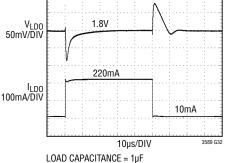

### TYPICAL PERFORMANCE CHARACTERISTICS v

$V_{IN} = 3.8V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 3.8V,  $T_A$  = 25°C, unless otherwise noted.

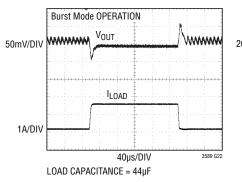

#### Step-Down Switching Regulator 1 Load Step

Step-Down Switching Regulator 1 Load Step

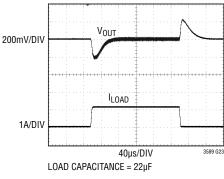

Buck-Boost Switching Regulator 1 Load Step

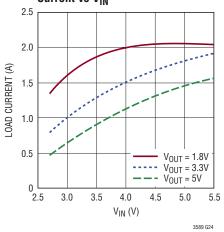

Maximum Buck-Boost Load Current vs V<sub>IN</sub>

LDO1 Output Change vs VIN 0.5 V<sub>LD01</sub> = 25mA 0.0 CHANGE IN V<sub>LD01</sub> (%) -0.5 -1.0 V<sub>LD01</sub> = 1.2V V<sub>LD01</sub> = 1.8V -1.5 V<sub>LD01</sub> = 2.8V V<sub>LD01</sub> = 3.3V -2.0 2 3 4 5 VIN (V) 3589 G26

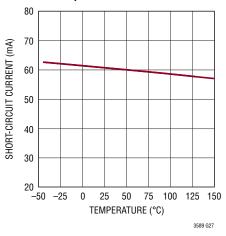

#### LDO1 Short-Circuit Current vs Temperature

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 3.8V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

VEN\_LD02, VEN\_LD034 100µs/DIV

3589 G31

3589fg

### PIN FUNCTIONS

$V_{IN\_LDO2}$  (Pin 1): Power Input for LDO2. This pin should be bypassed to ground with a 1µF or greater ceramic capacitor.

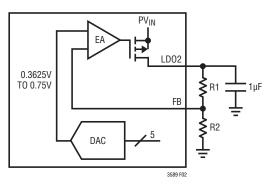

**LD02 (Pin 2):** Output Voltage of LD02. Nominal output voltage is set with a resistor feedback divider that servos to an  $I^2C$  register controlled DAC reference. This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

**LD03 (Pin 3):** Output Voltage of LD03. Nominal output voltage is fixed at 1.8V or 2.8V (LTC3589-1/LTC3589-2). This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

**LD04 (Pin 4):** Output Voltage of LD04. Output voltage is selected via the  $I^2C$  port. This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

$V_{IN\_LD034}$  (Pin 5): Power Input for LD03 and LD04. This pin should be bypassed to ground with a 1µF or greater ceramic capacitor.

$\text{PV}_{\text{IN1}}$  (Pin 6): Power Input for Step-Down Switching Regulator 1. Tie this pin to V\_{IN} supply. This pin should be bypassed to ground with a 4.7µF or greater ceramic capacitor.

**SW1 (Pin 7):** Switch Pin for Step-Down Switching Regulator 1. Connect one side of step-down switching regulator 1 inductor to this pin.

**RSTO** (Pin 8): Reset Output. Open-drain output pulls low when the always-on regulator LDO1 is below regulation and during a hard reset initiated by a pushbutton input.

**EN\_LD02 (Pin 9):** Enable LD02 Logic Input. Active high input to enable LD02. A weak pull-down forces EN\_LD02 low when left floating.

**EN1 (Pin 10):** Enable Step-Down Switching Regulator 1. Active high input to enable step-down switching regulator 1. A weak pull-down forces EN1 low when left floating.

**EN2 (Pin 11):** Enable Step-Down Switching Regulator 2. Active high input to enable step-down switching regulator 2. A weak pull-down forces EN2 low when left floating.

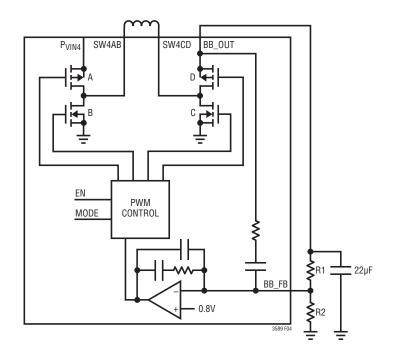

**SW4AB (Pin 12):** Switch Pin for Buck-Boost Switching Regulator 4. Connected to the buck-boost internal power switches A and B. Connect an inductor between this pin and SW4CD (Pin 19).

**EN3 (Pin 13):** Enable Step-Down Switching Regulator 3. Active high input to enable step-down switching regulator 3. A weak pull-down forces EN3 low when left floating.

**EN4 (Pin 14):** Enable Buck-Boost Switching Regulator 4. Active high input to enable buck-boost switching regulator 4. A weak pull-down forces EN4 low when left floating.

$PV_{IN4}$  (Pin 15): Power Input for Switching Regulator 4. Tie this pin to V<sub>IN</sub> supply. This pin should be bypassed to ground with a 4.7µF or greater ceramic capacitor.

**BB\_OUT (Pin 16):** Output Voltage of Buck-Boost Switching Regulator 4. This pin must be bypassed to ground with a  $22\mu$ F or greater ceramic capacitor.

**IRQ** (Pin 17): Interrupt Request Output. Open-drain driver is pulled low for power good, undervoltage, and overtemperature warning and fault conditions. Clear IRQ by writing to the I<sup>2</sup>C CLIRQ command register.

**EN\_LD034 (Pin 18):** LTC3589 Enable LD03 and LD04 Logic Input. Active high to enable LD03 and LD04. Disable LD04 via I<sup>2</sup>C software commands using I<sup>2</sup>C command registers OVEN or L2DTV2. A weak pull-down forces EN\_LD034 low when left floating.

**EN\_LD03 (Pin 18):** LTC3589-1/LTC3589-2 Enable LD03 Logic Input. Active high to enable LD03. A weak pull-down forces EN\_LD03 low when left floating.

**SW4CD (Pin 19):** Switch Pin for Buck-Boost Switching Regulator 4. Connected to the buck-boost internal power switches C and D. Connect an inductor between this node and SW4AB (Pin 12).

**PWR\_ON (Pin 20):** External Power-On. Handshaking pin to acknowledge successful power-on sequence. PWR\_ON must be driven high within five seconds of WAKE going high to keep power on. It can be used to activate the WAKE output by driving high. Drive low to shut down WAKE.

3589f

### PIN FUNCTIONS

$\overline{\text{ON}}$  (Pin 21): Pushbutton Input. A weak internal pullup forces  $\overline{\text{ON}}$  high when left floating. A normally open pushbutton is connected from  $\overline{\text{ON}}$  to ground to force a low state on this pin.

**PBSTAT (Pin 22):** Pushbutton Status. Open-drain output to be used for processor interrupts. PBSTAT mirrors the status of  $\overline{ON}$  pushbutton pin. PBSTAT is delayed 50ms from  $\overline{ON}$  pin for debounce.

**WAKE (Pin 23):** System Wake Up. Open-drain driver output releases high when signaled by pushbutton activation or PWR\_ON input. It may be used to initiate a pin-strapped power-up sequence by connecting to a regulator enable pin.

**PVIN2 (Pin 24):** Power Input for Step-Down Switching Regulator 2. Tie this pin to  $V_{IN}$  supply. This pin should be bypassed to ground with a  $4.7\mu$ F or greater ceramic capacitor.

**SW2 (Pin 25):** Switch Pin for Step-Down Switching Regulator 2. Connect one side of step-down switching regulator 2 inductor to this pin.

**SW3 (Pin 26):** Switch Pin for Step-Down Switching Regulator 3. Connect one side of step-down switching regulator 3 inductor to this pin.

**PVIN3 (Pin 27):** Power Input for Step-Down Switching Regulator 3. Tie this pin to the  $V_{IN}$  supply. This pin should be bypassed to ground with a 4.7µF or greater ceramic capacitor.

**VSTB (Pin 28):** Voltage Standby. When VSTB is low, DAC reference registers are selected by bit values in command register VCCR. When VSTB is high, the DAC registers are forced xxDVT2 registers. Tie VSTB to ground if unused.

**PGOOD (Pin 29):** Power Good Output. Open-drain output pulls down when any regulator falls below power good threshold and during regulator dynamic voltage slew unless disabled in  $I^2C$  register. Pulls down when all regulators are disabled.

**SCL (Pin 30):** Clock Input Pin for the  $I^2C$  Serial Port. The  $I^2C$  logic levels are scaled with respect to  $DV_{DD}$ .

**SDA (Pin 31):** Data Input Pin for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C logic levels are scaled with respect to DV<sub>DD</sub>.

$DV_{DD}$  (Pin 32): Supply Voltage for I<sup>2</sup>C Serial Port. This pin sets the logic reference level of SCL and SDA I<sup>2</sup>C pins.  $DV_{DD}$  resets I<sup>2</sup>C registers to power on state when driven to <1V. SCL and SDA logic levels are scaled to  $DV_{DD}$ . Connect a 0.1µF decoupling capacitor from this pin to ground.

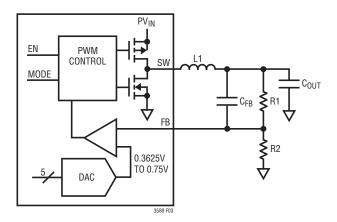

**BUCK2\_FB (Pin 33):** Feedback Input for Step-Down Switching Regulator 2. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 2 to this pin to ground.

**BUCK3\_FB (Pin 34):** Feedback Input for Step-Down Switching Regulator 3. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 3 to this pin to ground.

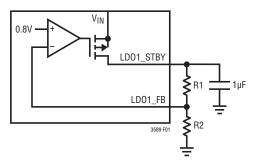

**LD01\_FB (Pin 35):** Feedback Input for LD01. Set output voltage using a resistor divider connected from LD01\_STDBY to this pin to ground.

**LD01\_STDBY (Pin 36):** Always-On LD01 Output. This pin provides an always-on supply voltage useful for light loads such as a watchdog microprocessor or a real-time clock. Connect a  $1\mu$ F capacitor from LD01\_STBY to ground.

$V_{IN}$  (Pin 37): Supply Voltage Input. This pin should be bypassed to ground with a  $1\mu F$  or greater ceramic capacitor.

**LD02\_FB (Pin 38):** Feedback Input for LD02. Set full-scale output voltage using a resistor divider connected from LD02\_OUT to this pin to ground.

**BUCK1\_FB (Pin 39):** Feedback Input for Step-Down Switching Regulator 1. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 1 to this pin to ground.

**BB\_FB (Pin 40):** Feedback Input for Buck-Boost Switching Regulator 4. Set the output voltage using resistor divider connected from BB\_OUT to this pin to ground.

**GND (Exposed Pad Pin 41):** Ground. The Exposed Pad must be connected to a continuous ground plane on the second layer of the printed circuit board by several interconnect vias directly under the LTC3589 for maximum heat transfer.

3589fc

### LTC3589/LTC3589-1/ LTC3589-2

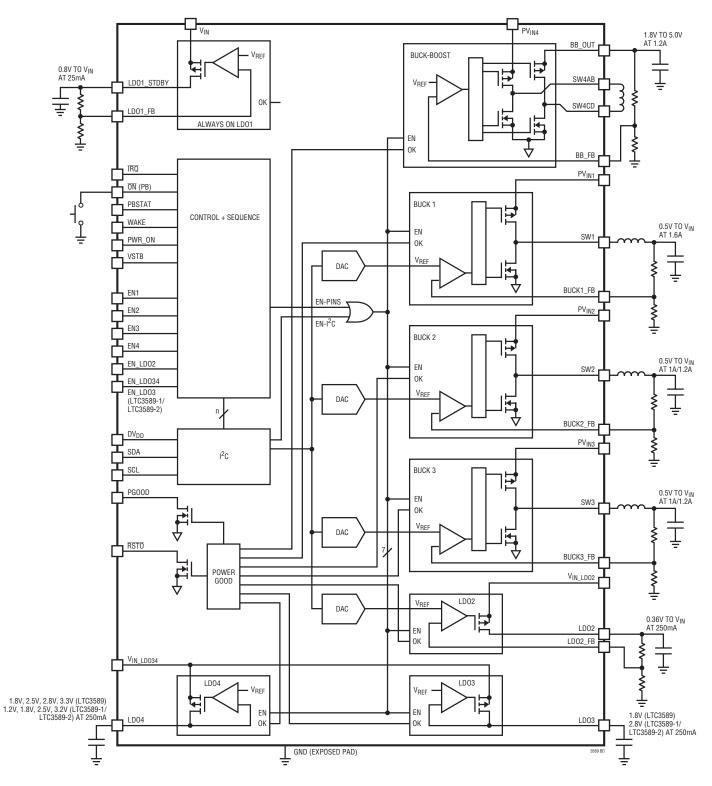

### **BLOCK DIAGRAM**

3589fg

#### INTRODUCTION

The LTC3589 is a complete power management solution for portable microprocessors and peripheral devices. It generates a total of eight voltage rails for supplying power to the processor core, SDRAM, system memory, PC cards, always-on real-time clock and HDD functions. Supplying the voltage rails are an always-on low quiescent current 25mA LDO, one 1.6A and two 1A (1.2A for LTC3589-1/LTC3589-2) step-down regulators, a 1.2A buck-boost regulator, and three 250mA low dropout regulators. Supporting the multiple regulators is a highly configurable poweron sequencing capability, dynamic voltage slewing DAC output voltage control, a pushbutton interface controller, regulator control via an  $I^2C$  interface, and extensive status and interrupt outputs.

The LTC3589 operates over an input supply range of 2.7V to 5.5V. The input supplies for the 250mA LDO regulators may operate as low as 1.7V to limit power loss at low output voltages.

The always-on LDO1 provides a resistor programmable output voltage as low as 0.8V and is capable of supplying 25mA. With only the always-on LDO active the LTC3589 draws just 8 $\mu$ A (typical). Always-on LDO1 will continue to operate with V<sub>IN</sub> levels as low as 2.0V (typical) to maintain memory and RTC function as long as possible.

Each of the 250mA LDO regulators has unique output voltage configurations. LDO3 has a fixed 1.8V (2.8V for LTC3589-1/LTC3589-2) output. LDO4 has four output levels selectable via the I<sup>2</sup>C interface. Its possible outputs are 1.8V, 2.5V, 2.8V, and 3.3V (1.2V, 1.8V, 2.5V, 3.2V for LTC3589-1/LTC3589-2). LDO2 has a dynamically slewing DAC set point reference and an external feedback pin to set the output voltage range with a resistive divider. Each LDO draws 50µA (typical) quiescent current.

The LTC3589 includes three internally compensated constant frequency current mode step-down switching regulators two capable of supplying 1A of output current and one capable of supplying 1.6A. The LTC3589-1/LTC3589-2 step-down regulators can supply 1.2A, 1.2A, and 1.6A. Step-down regulator switching frequencies of 2.25MHz or 1.125MHz are independently selected for each step-down regulator using the I<sup>2</sup>C command registers.

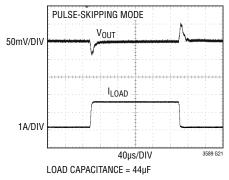

The power-on default frequency is 2.25MHz. Each of the step-down regulators have dynamically slewing DAC input references and external feedback pins to set output voltage range. The step-down regulators three operating modes, pulse-skipping, burst, or forced continuous, are set using the I<sup>2</sup>C interface. In pulse-skipping mode the regulator will support 100% duty cycle. For best efficiency at low output loads select Burst Mode operation. Forced continuous mode minimizes output voltage ripple at light loads.

The 4-switch buck-boost DC/DC voltage mode converter generates a user-programmable output voltage rail from 1.8V to 5V. Utilizing a proprietary switching algorithm, the buck-boost converter maintains high efficiency and low noise operation with input voltages that are above, below or equal to the required output rail. The buck-boost error amplifier uses a fixed 0.8V reference and the output voltage is set by an external resistor divider. Burst Mode operation is enabled through the l<sup>2</sup>C control registers. No external compensation components are required for the buck-boost converter.

The reference inputs for the three step-down regulators and LDO2 are 5-bit D to A converters with up-down ramping at selectable slew rates. The slew endpoint voltages and select bits are stored in  $I^2C$  registers for each DAC. A select bit in the  $I^2C$  command registers chooses which register to use for each target voltage. Variable reference slew rates from 0.88mV/µs to 7mV/µs are selectable in the  $I^2C$  register. Each of the four DACs has independent voltage, voltage select, and slew rate control registers.

The LTC3589 is equipped with a pushbutton control circuit that will activate the WAKE output, indicate pushbutton status via the PBSTAT pin, and initiate a hard reset shutdown of the regulators. Grounding the ON pin with the pushbutton for 400ms will force the WAKE pin to release HIGH. The WAKE pin output can be tied to the enable pin of the first regulator in a power-on sequence. Once in the power-on state, subsequent pushes of the button longer than 50ms are mirrored by the PBSTAT output. Holding ON LOW for five seconds disables all the regulators, pulls down the WAKE pin, and pulls down RSTO for one second to indicate to the processor that a hard reset occurred. All regulator enables and pushbutton inputs are inhibited for one second following the hard reset.

3589fg

The LTC3589 has flexible options for enabling and sequencing the regulator enables. The regulators are enabled using input pins or the I<sup>2</sup>C serial port. To define a power-on sequence tie the enable of the first regulator to be powered up to the WAKE pin. Connect the first regulators output to the enable pin of the second regulator, and so on. One or more regulators may be started in any sequence. Each enable pin has a 200µs (typical) delay between the pin and the internal enable of the regulator. When the system controllers are satisfied that power rails are up, the controller must drive PWR ON HIGH to keep WAKE active. To ensure correct start-up sequencing, the regulators outputs are monitored by voltage comparators which require each output to discharge below 300mV before re-enabling. A software control command register function is available which sets the regulators to effectively ignore their enable pins but respond to I<sup>2</sup>C register enables. This function enables software-only control of any combination of pin-strapped regulators and is useful for implementing system power saving modes. Keep-alive mode exempts selected regulators from turning off during normal shutdown. In keep-alive mode, the LTC3589 powers down normally and is ready for the next start-up sequence, but selected regulators are kept on to power memory or other functions during system standby modes.

The LTC3589 will shut down all regulators and pull down the WAKE pin under high temperature,  $V_{IN}$  undervoltage, and extended low regulator output voltage conditions. Status of a hard shutdown is reported by the  $\overline{IRQ}$  status pin and the IRQSTAT status register.

The  $I^2C$  serial port on the LTC3589 contains 13 command registers for controlling each of the regulators, one readonly register for monitoring each regulators power good status, one read-only register for reading the cause of an IRQ event, and one clear IRQ command register. The LTC3589 I<sup>2</sup>C supports random addressing of any register.

# LTC3589, LTC3589-1, AND LTC3589-2 FUNCTIONAL COMPARISON

Table 1. summarizes the functional differences between the LTC3589, LTC3589-1, and LTC3589-2.

| Table 1. LTC3589, LTC3589-1, and LTC3589-2 Functional |

|-------------------------------------------------------|

| Differences                                           |

|                                                                  | LTC3589                                                         | LTC3589-1                                                       | LTC3589-2                                           |  |

|------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|--|

| Power-On Inhibit<br>Enable Delay                                 | 1 second                                                        | <2ms                                                            | <2ms                                                |  |

| Buck2 Current<br>Output                                          | 1A                                                              | 1.2A                                                            | 1.2A                                                |  |