# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### LTC3887/LTC3887-1

Dual Output PolyPhase Step-Down DC/DC Controller with Digital Power System Management DESCRIPTION

### **FEATURES**

- PMBus/I<sup>2</sup>C Compliant Serial Interface

- Telemetry Read Back includes VIN, IIN, VOUT, IOUT, **Temperature, Duty Cycle and Faults**

- Programmable Voltage, Current Limit, Digital Soft-Start/Stop, Sequencing, Margining, OV/UV and Frequency Synchronization (250kHz to 1MHz)

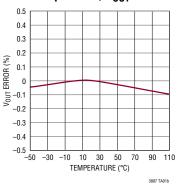

- ±0.5% Output Voltage Accuracy Over Temperature

- **Integrated 16-Bit ADC**

- V<sub>OUT</sub> Range: 0.5V to 5.5V (V<sub>OUT0</sub>, V<sub>OUT1</sub>)

- Internal EEPROM and Fault Logging

- Integrated N-Channel MOSFET Gate Drivers (LTC3887)

- Wide VIN Range: 4.5V to 24V

- Analog Current Mode Control Loop

- Remote Differential Sense for PolyPhase® Applications

- Accurate PolyPhase Current Sharing for Up to Six Phases

- Available in a 40-Pin (6mm × 6mm) QFN Package

#### **APPLICATIONS**

- High Current Distributed Power Systems

- Telecom, Datacom and Storage Systems

- Intelligent Energy Efficient Power Regulation

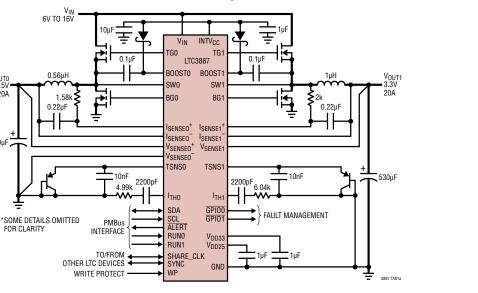

### TYPICAL APPLICATION

Dual 350kHz 3.3V/0.5V Step-Down Converter

The LTC®3887/LTC3887-1 are dual, PolyPhase DC/DC synchronous step-down switching regulator controllers with an I<sup>2</sup>C-based PMBus compliant serial interface. The controllers use a constant frequency, current mode architecture that is supported by LTpowerPlay<sup>™</sup> a software development tool with graphical user interface (GUI).

Switching frequency, channel phasing, output voltage, and device address can be programmed using external configuration resistors. Additionally, parameters can be set via the digital interface or stored in EEPROM. Voltage, current, internal/external temperature and fault status can be read back through the bus interface.

The LTC3887 has integrated gate drivers. The LTC3887-1 has three-state PWM pins to drive power blocks or DrMOS power stages. The LTC3887 is an enhanced version of the LTC3880 with greater output voltage range and more digital features. Refer to page 15 for more detail.

Δ. LT. LTC, LTM, PolyPhase, μModule, Linear Technology and the Linear logo are registered trademarks and LTpowerPlay is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5481178, 5705919, 5929620, 6144194, 6177787, 6580258, 5408150, 7420359, Licensed under U.S. Patent 7000125 and other related patents worldwide.

#### **Regulated Output Voltage vs** Temperature, $V_{OUT} = 0.5V$

V<sub>OUTO</sub> 0.5V

20A

530uF

### TABLE OF CONTENTS

| Features                                                  | 1  |

|-----------------------------------------------------------|----|

| Applications                                              | 1  |

| Typical Application                                       | 1  |

| Description                                               | 1  |

| Table of Contents                                         |    |

| Absolute Maximum Ratings                                  | 4  |

| Pin Configuration                                         |    |

| Order Information                                         |    |

| Electrical Characteristics                                |    |

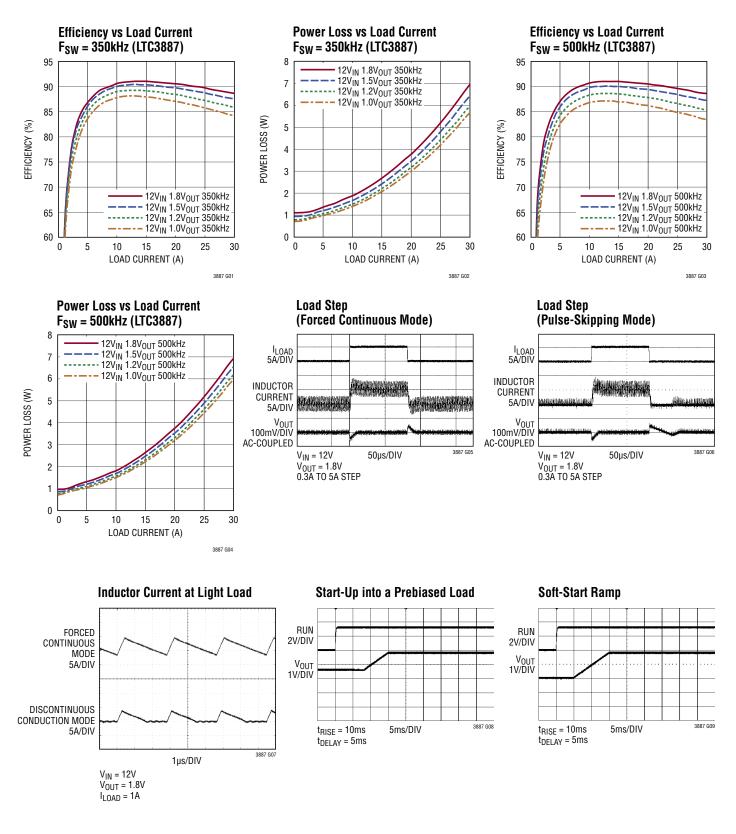

| Typical Performance Characteristics                       | 9  |

| Pin Functions                                             |    |

| Block Diagram                                             | 14 |

| Operation                                                 | 15 |

| Overview                                                  | 15 |

| Main Control Loop                                         | 16 |

| EEPROM (NVM)                                              | 16 |

| Power Up and Initialization                               | 17 |

| Soft-Start                                                | 17 |

| Sequencing                                                | 18 |

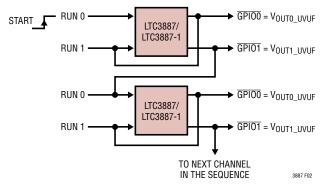

| EVENT-Based Sequencing                                    | 18 |

| Shutdown                                                  |    |

| Light Load Current Operation                              | 19 |

| Switching Frequency and Phase                             | 20 |

| Output Voltage Sensing                                    | 20 |

| Current Sensing                                           |    |

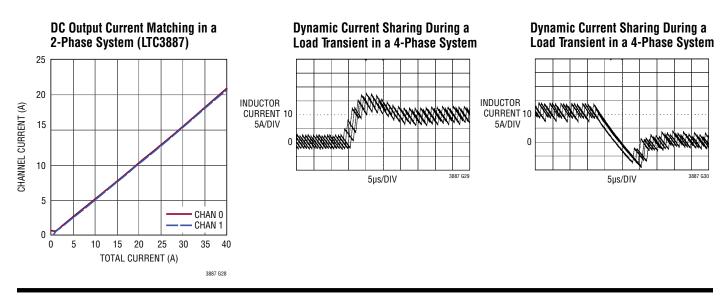

| PolyPhase Load Sharing                                    |    |

| External/Internal Temperature Sense                       |    |

| RCONFIG (Resistor Configuration) Pins                     |    |

| Fault Detection and Handling                              |    |

| CRC Protection                                            |    |

| Serial Interface                                          |    |

| Communication Protection                                  |    |

| Device Addressing                                         |    |

| Responses to V <sub>OUT</sub> and I <sub>OUT</sub> Faults |    |

| Output Overvoltage Fault Response                         |    |

| Output Undervoltage Response                              |    |

| Peak Output Overcurrent Fault Response                    |    |

| Responses to Timing Faults                                |    |

| Responses to V <sub>IN</sub> OV Faults                    | 26 |

| Responses to OT/UT Faults                                                | 26 |

|--------------------------------------------------------------------------|----|

| Internal Overtemperature Fault/                                          |    |

| Warn Response                                                            | 26 |

| External Overtemperature and                                             |    |

| Undertemperature Fault Response                                          | 26 |

| Responses to External Faults                                             |    |

| Fault Logging                                                            |    |

| Bus Timeout Protection                                                   | 27 |

| Similarity Between PMBus, SMBus and I <sup>2</sup> C                     |    |

| 2-Wire Interface                                                         | 27 |

| PMBus Serial Digital Interface                                           | 28 |

| PMBus Command Summary                                                    |    |

| PMBus Commands                                                           | 33 |

| *Data Format                                                             | 38 |

| Applications Information                                                 |    |

| Current Limit Programming                                                | 39 |

| I <sub>SENSE</sub> <sup>+</sup> and I <sub>SENSE</sub> <sup>-</sup> Pins |    |

| Low Value Resistor Current Sensing                                       | 40 |

| Inductor DCR Current Sensing                                             |    |

| Slope Compensation and Inductor Peak Current                             |    |

| Inductor Value Calculation                                               |    |

| Inductor Core Selection                                                  | 43 |

| Power MOSFET and Schottky Diode (Optional)                               |    |

| Selection                                                                | 43 |

| Variable Delay Time, Soft-Start and Output                               |    |

| Voltage Ramping                                                          |    |

| Digital Servo Mode                                                       |    |

| Soft Off (Sequenced Off)                                                 |    |

| INTV <sub>CC</sub> Regulator                                             | 46 |

| Topside MOSFET Driver Supply ( $C_B$ , $D_B$ )                           | 40 |

| (LTC3887)                                                                |    |

| Undervoltage Lockout                                                     |    |

| C <sub>IN</sub> and C <sub>OUT</sub> Selection                           | 47 |

| Fault Conditions                                                         |    |

| Open-Drain Pins                                                          | 48 |

| Phase-Locked Loop and Frequency                                          | 40 |

| Synchronization                                                          |    |

| Minimum On-Time Considerations                                           | วบ |

### TABLE OF CONTENTS

| RCONFIG (External Resistor                             |    |

|--------------------------------------------------------|----|

| Configuration Pins)                                    | 50 |

| Voltage Selection                                      |    |

| Frequency and Phase Selection Using                    |    |

| RCONFIG                                                | 51 |

| Address Selection Using RCONFIG                        | 52 |

| Efficiency Considerations                              | 52 |

| Checking Transient Response                            | 53 |

| PC Board Layout Checklist                              | 54 |

| PC Board Layout Debugging                              | 56 |

| Design Example                                         | 57 |

| Additional Design Checks                               | 59 |

| Connecting the USB to the I <sup>2</sup> C/SMBus/PMBus |    |

| Controller to the LTC3887 In System                    | 59 |

| LTpowerPlay: An Interactive GUI for                    |    |

| Digital Power                                          | 61 |

| PMBus Communication and Command                        |    |

| Processing                                             |    |

| PMBus Command Details                                  |    |

| Addressing and Write Protect                           |    |

| General Configuration Registers                        |    |

| On/Off/Margin                                          |    |

| PWM Config                                             |    |

| Voltage                                                |    |

| Input Voltage and Limits                               |    |

| Output Voltage and Limits                              |    |

| Current                                                |    |

| Input Current Calibration                              |    |

| Output Current Calibration                             |    |

| Input Current                                          |    |

| Output Current                                         | 75 |

|                                                        |    |

| Temperature                          |     |

|--------------------------------------|-----|

| External Temperature Calibration     | 76  |

| External Temperature Limits          |     |

| Timing                               | 78  |

| Timing—On Sequence/Ramp              |     |

| Timing—Off Sequence/Ramp             | 79  |

| Precondition for Restart             |     |

| Fault Response                       |     |

| Fault Responses All Faults           |     |

| Fault Responses Input Voltage        |     |

| Fault Responses Output Voltage       |     |

| Fault Responses Output Current       |     |

| Fault Responses IC Temperature       |     |

| Fault Responses External Temperature |     |

| Fault Sharing                        |     |

| Fault Sharing Propagation            | 87  |

| Fault Sharing Response               |     |

| Scratchpad                           |     |

| Identification                       |     |

| Fault Warning and Status             | 90  |

| Telemetry                            |     |

| NVM (EEPROM) Memory Commands         | 100 |

| Store/Restore                        | 100 |

| Fault Logging                        | 101 |

| Block Memory Write/Read              |     |

| Typical Applications                 | 107 |

| Package Description                  | 112 |

| Revision History                     | 113 |

| Typical Application                  | 114 |

| Related Parts                        | 114 |

### ABSOLUTE MAXIMUM RATINGS

| (Note 1)                                               |      |

|--------------------------------------------------------|------|

| V <sub>IN</sub> Voltage0.3V to                         | 28V  |

| Top Gate Transient Voltage TG0,                        |      |

| TG1 LTC38875V to 2                                     | 34V  |

| Top Gate Transient Voltage PWM0,                       |      |

| PWM1 LTC3887-10.3V to                                  | ) 6V |

| BOOST1, BOOST0 LTC38870.3V to 3                        | 34V  |

| V <sub>CC1</sub> , V <sub>CC0</sub> LTC3887-1 –0.3V to | ) 6V |

| Switch Transient Voltage SW1,                          |      |

| SW0 LTC3887 –5V to                                     | 28V  |

| INTV <sub>CC</sub> , (BOOST1 – SW1), (BOOST0 – SW0),   |      |

| BG0, BG1, LTC3887                                      | ) 6V |

|                                                        |      |

| V <sub>SENSE0</sub> <sup>+</sup> , V <sub>SENSE1</sub> , I <sub>SENSE0n</sub> , I <sub>SENSE1n</sub> 0.3V to 6V<br>RUNO, RUN1, SDA, SCL, ALERT0.3V to 5.5V<br>FREQ_CFG, V <sub>OUTn CFG</sub> , ASEL0/1, V <sub>DD25</sub> 0.3V to 2.75V |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD33</sub> , GPIO0, GPIO1, TSNS0, TSNS1, V <sub>SENSE0</sub> <sup>-</sup> ,                                                                                                                                                       |

| SHARE_CLK, WP, SYNC, ITH <i>n</i> –0.3V to 3.6V                                                                                                                                                                                          |

| INTV <sub>CC</sub> Peak Output Current100mA                                                                                                                                                                                              |

| Operating Junction Temperature Range                                                                                                                                                                                                     |

| (Note 2)–40°C to 125°C                                                                                                                                                                                                                   |

| Storage Temperature Range40°C to 150°C*                                                                                                                                                                                                  |

| *See Derating EEPROM Retention at Temperature in the                                                                                                                                                                                     |

| Applications Information section for junction temperatures                                                                                                                                                                               |

| in excess of 125°C.                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                          |

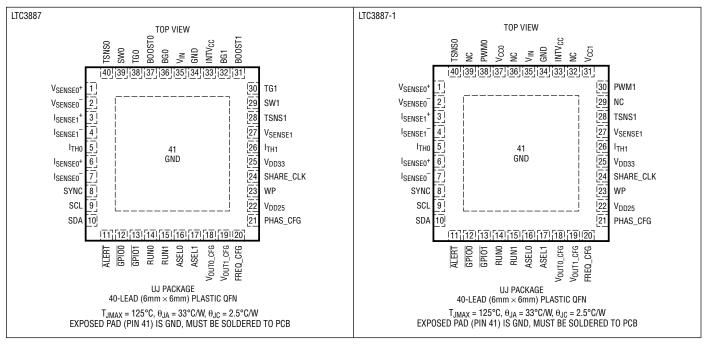

### PIN CONFIGURATION

### ORDER INFORMATION http://www.linear.com/product/LTC3887#orderinfo

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | JUNCTION TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|----------------------------|

| LTC3887EUJ#PBF   | LTC3887EUJ#TRPBF   | LTC3887UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C             |

| LTC3887IUJ#PBF   | LTC3887IUJ#TRPBF   | LTC3887UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C             |

| LTC3887EUJ-1#PBF | LTC3887EUJ-1#TRPBF | LTC3887UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C             |

| LTC3887IUJ-1#PBF | LTC3887IUJ-1#TRPBF | LTC3887UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C             |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 2) V<sub>IN</sub> = 12V, V<sub>RUN0,1</sub> = 3.3V, f<sub>SYNC</sub> = 500kHz (externally driven) unless otherwise specified.

| SYMBOL                                    | PARAMETER                                                                                        | CONDITIONS                                                                   |     | MIN          | ТҮР          | MAX         | UNITS                |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|--------------|--------------|-------------|----------------------|

| Input Voltag                              |                                                                                                  | 1                                                                            |     |              |              |             |                      |

| V <sub>IN</sub>                           | Input Voltage Range                                                                              | (Note 12)                                                                    |     | 4.5          |              | 24          | V                    |

| IQ                                        | Input Voltage Supply Current<br>Normal Operation                                                 | V <sub>RUN0,1</sub> = 3.3V, No Caps on TG and BG<br>V <sub>RUN0,1</sub> = 0V |     |              | 25<br>20     |             | mA<br>mA             |

| V <sub>UVLO</sub>                         | Undervoltage Lockout Threshold when $V_{IN} > 4.3V$                                              | V <sub>INTVCC</sub> Falling<br>V <sub>INTVCC</sub> Rising                    |     |              | 3.7<br>3.95  |             | V<br>V               |

| T <sub>INIT</sub>                         | Initialization Time                                                                              | Time from V <sub>IN</sub> Applied Until the TON_DELAY Timer Starts.          |     |              | 70           |             | ms                   |

| Control Loop                              | 0                                                                                                |                                                                              |     |              |              |             |                      |

| V <sub>OUTRO</sub>                        | Full-Scale Voltage High Range<br>Set Point Accuracy (0.6V to 5V)<br>Resolution<br>LSB Step Size  | VOUT_COMMAND = 5.500V (Note 9)                                               | • • | 5.45<br>-0.5 | 12<br>1.375  | 5.55<br>0.5 | V<br>%<br>Bits<br>mV |

| V <sub>OUTR1</sub>                        | Full-Scale Voltage Low Range<br>Set Point Accuracy (0.6V to 2.5V)<br>Resolution<br>LSB Step Size | VOUT_COMMAND = 2.75V (Note 9)                                                | •   | 2.7<br>-0.5  | 12<br>0.6875 | 2.8<br>0.5  | V<br>%<br>Bits<br>mV |

| V <sub>LINEREG</sub>                      | Line Regulation                                                                                  | 6V < V <sub>IN</sub> < 24V                                                   |     |              |              | ±0.02       | %/V                  |

| V <sub>LOADREG</sub>                      | Load Regulation                                                                                  | $\Delta V_{ITH} = 1.35V - 0.7V$<br>$\Delta V_{ITH} = 1.35V - 2.0V$           | •   |              | 0.01<br>0.01 | 0.1<br>-0.1 | %<br>%               |

| 9 <sub>m0,1</sub>                         | Error Amplifier g <sub>m</sub>                                                                   | I <sub>TH0,1</sub> =1.22V                                                    |     |              | 3            |             | mmho                 |

| ISENSE0,1                                 | Input Current                                                                                    | V <sub>ISENSE</sub> = 5.5V                                                   |     |              | ±1           | ±3          | μA                   |

| V <sub>SENSERINO</sub>                    | V <sub>SENSE</sub> Input Resistance to Ground                                                    | $0V \le V_{PIN} \le 5.5V$                                                    |     |              | 41           |             | kΩ                   |

| V <sub>SENSERIN1</sub>                    | V <sub>SENSE</sub> Input Resistance to Ground                                                    | $0V \le V_{PIN} \le 5.5V$                                                    |     |              | 37           |             | kΩ                   |

| VIILIMIT                                  | Resolution                                                                                       |                                                                              |     |              | 3            |             | bits                 |

|                                           | VILIMMAX                                                                                         | Hi Range<br>Lo Range                                                         | •   | 68<br>44     | 75<br>50     | 82<br>56    | mV<br>mV             |

|                                           | V <sub>ILMMIN</sub>                                                                              | Hi Range<br>Lo Range                                                         |     |              | 37.5<br>25   |             | mV<br>mV             |

| Gate Drivers                              |                                                                                                  |                                                                              |     |              |              |             |                      |

| TGO,1<br>t <sub>r</sub><br>t <sub>f</sub> | TG Transition Time (LTC3887/LTC3887-1)<br>Rise Time<br>Fall Time                                 | (Note 4)<br>C <sub>LOAD</sub> = 3300pF<br>C <sub>LOAD</sub> = 3300pF         |     |              | 30<br>30     |             | ns<br>ns             |

| BG0,1<br>t <sub>r</sub><br>t <sub>f</sub> | BG Transition Time:<br>Rise Time<br>Fall Time                                                    | (Note 4)<br>C <sub>LOAD</sub> = 3300pF<br>C <sub>LOAD</sub> = 3300pF         |     |              | 30<br>30     |             | ns<br>ns             |

| TG/BG t <sub>1D</sub>                     | Top Gate Off to Bottom Gate On Delay Time                                                        | (Note 4) C <sub>LOAD</sub> = 3300pF Each Driver                              |     |              | 30           |             | ns                   |

| BG/TG t <sub>2D</sub>                     | Bottom Gate Off to Top Gate On Delay Time                                                        | (Note 4) C <sub>LOAD</sub> = 3300pF Each Driver                              |     |              | 30           |             | ns                   |

| t <sub>ON(MIN)</sub>                      | Minimum On-Time (LTC3887/LTC3887-1)                                                              |                                                                              |     |              | 90           |             | ns                   |

|                                           | oltage Supervisor                                                                                |                                                                              |     |              |              |             |                      |

| Ν                                         | Resolution                                                                                       |                                                                              |     |              | 8            |             | Bits                 |

| V <sub>RANGE0</sub>                       | Voltage Monitoring Range                                                                         | Range Value = 0                                                              |     | 1            |              | 5.6         | V                    |

| V <sub>RANGE1</sub>                       | Voltage Monitoring Range                                                                         | Range Value = 1                                                              |     | 0.5          |              | 2.7         | V                    |

| V <sub>OUSTP0</sub>                       | Threshold Programming Step                                                                       | Range Value = 0                                                              |     |              | 22.5         |             | mV                   |

| V <sub>OUSTP1</sub>                       | Threshold Programming Step                                                                       | Range Value = 1                                                              |     |              | 11.25        |             | mV                   |

| V <sub>THACC0</sub>                       | Threshold Accuracy 2V < V <sub>OUT</sub> < 5V                                                    | Range Value = 0                                                              |     |              |              | ±2          | %                    |

| V <sub>THACC1</sub>                       | Threshold Accuracy 1V < V <sub>OUT</sub> < 2.5V                                                  | Range Value = 1                                                              |     |              |              | ±2          | %                    |

| t <sub>PROPOV</sub>                       | OV Comparator to GPIO Low Time                                                                   | V <sub>OD</sub> = 10% of Threshold                                           |     |              |              | 35          | μs                   |

|                                           |                                                                                                  |                                                                              |     |              |              |             |                      |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 2) V<sub>IN</sub> = 12V, V<sub>RUN0,1</sub> = 3.3V, f<sub>SYNC</sub> = 500kHz (externally driven) unless otherwise specified.

| SYMBOL                         | PARAMETER                                        | CONDITIONS                                                                                                                             |   | MIN | TYP         | MAX      | UNITS     |

|--------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------|----------|-----------|

| UV Output V                    | oltage Supervisor                                |                                                                                                                                        |   |     |             |          |           |

| Ν                              | Resolution                                       |                                                                                                                                        |   |     | 8           |          | bits      |

| V <sub>RANGE0</sub>            | Voltage Range                                    | High Range                                                                                                                             |   | 1   |             | 5.5      | ١         |

| V <sub>RANGE1</sub>            | Voltage Range                                    | Low Range                                                                                                                              |   | 0.5 |             | 2.7      | ١         |

| VOUSTPO                        | Step Size                                        | Range Value = 0, High Range                                                                                                            |   |     | 22          |          | m٧        |

| V <sub>OUSTP1</sub>            | Step Size                                        | Range Value = 1, Low Range                                                                                                             |   |     | 11          |          | m۷        |

| V <sub>THACC0</sub>            | Threshold Accuracy 2V < V <sub>OUT</sub> < 5V    | Range Value = 0, High Range                                                                                                            |   |     |             | ±2       | %         |

| V <sub>THACC1</sub>            | Threshold Accuracy 1V < V <sub>OUT</sub> < 2.5V  | Range Value = 1, Low Range                                                                                                             |   |     |             | ±2       | %         |

| t <sub>PROPUV</sub>            | UV Comparator to GPIO Low Time                   | V <sub>OD</sub> = 10% of Threshold                                                                                                     |   |     |             | 100      | μs        |

| V <sub>IN</sub> Voltage        | Supervisor                                       |                                                                                                                                        |   |     |             |          |           |

| N                              | Resolution                                       |                                                                                                                                        |   |     | 8           |          | bits      |

| VINRANGE                       | Full-Scale Voltage                               |                                                                                                                                        |   | 4.5 |             | 20       | V         |

| VINSTP                         | Step Size                                        |                                                                                                                                        |   |     | 82          |          | mV        |

| VINTHACC                       | Threshold Accuracy 9.0V < V <sub>IN</sub> < 20V  |                                                                                                                                        |   |     |             | ±2.5     | %         |

| V <sub>INTHACC\M</sub>         | Threshold Accuracy $4.5V < V_{IN} \le 9V$        |                                                                                                                                        |   |     |             | ±5       | %         |

| t <sub>PROPVIN</sub>           | Comparator Response Time<br>(VIN_ON and VIN_OFF) | V <sub>OD</sub> = 10% of Threshold                                                                                                     |   |     |             | 100      | μs        |

| Output Volta                   | ge Readback                                      |                                                                                                                                        |   |     |             | 1        |           |

| N                              | Resolution                                       |                                                                                                                                        |   |     | 16          |          | Bits      |

|                                | LSB Step Size                                    |                                                                                                                                        |   |     | 244         |          | μV        |

| V <sub>OFS</sub>               | Full-Scale Voltage                               | (Note 10) V <sub>RUNn</sub> = 0V (Note 8)                                                                                              |   |     | 8           |          | V         |

| V <sub>OUT_TUE</sub>           | Total Unadjusted Error                           | (Note 8) V <sub>OUTn</sub> > 0.6V                                                                                                      |   |     |             | 0.5      | %         |

| V <sub>OS</sub>                | Zero-Code Offset Voltage                         |                                                                                                                                        |   |     |             | ±500     | μV        |

| t <sub>convert</sub>           | Conversion Time                                  | (Note 6)                                                                                                                               |   |     | 100         |          | ms        |

| V <sub>IN</sub> Voltage        | Readback                                         |                                                                                                                                        |   |     |             |          |           |

| N                              | Resolution                                       | (Note 5)                                                                                                                               |   |     | 10          |          | Bits      |

| V <sub>IFS</sub>               | Full-Scale Voltage                               | (Note 11)                                                                                                                              |   |     | 38.91       |          | V         |

| V <sub>IN_TUE</sub>            | Total Unadjusted Error                           | V <sub>VIN</sub> > 4.5V (Note 8)                                                                                                       | • |     |             | 0.5<br>2 | %<br>%    |

| tCONVERT                       | Conversion Time                                  | (Note 6)                                                                                                                               |   |     | 100         |          | ms        |

|                                | ent Readback                                     |                                                                                                                                        |   |     |             |          |           |

| N                              | Resolution                                       | (Note 5)                                                                                                                               |   |     | 10          |          | Bits      |

|                                | LSB Step Size                                    | $\hat{OV} \le  V_{ISENSE}^+ - V_{ISENSE}^-  < 16 \text{mV}$                                                                            |   |     | 15.625      |          | μV        |

|                                |                                                  | $16\text{mV} \leq  V_{\text{ISENSE}^+} - V_{\text{ISENSE}^-}  < 32\text{mV}$                                                           |   |     | 31.25       |          | μV        |

|                                |                                                  | $\begin{array}{l} 32mV \leq  V_{ISENSE}^+ - V_{ISENSE}^-  < 63.9mV \\ 63.9mV \leq  V_{ISENSE}^+ - V_{ISENSE}^-  < 127.9mV \end{array}$ |   |     | 62.5<br>125 |          | μV<br>μV  |

| I <sub>FS</sub>                | Full-Scale Current                               | $\frac{1}{(\text{Note 7}) \text{R}_{\text{ISENSE}} = 1\text{m}\Omega}{(\text{Note 7}) \text{R}_{\text{ISENSE}} = 1\text{m}\Omega}$     |   |     | ±128        |          | μν<br>Α   |

| IOUT_TUE                       | Total Unadjusted Error                           | (Note 8) V <sub>ISENSE</sub> > 6mV                                                                                                     |   |     | 120         | ±1       | %         |

| V <sub>0S</sub>                | Zero-Code Offset Voltage                         | (1000 0) 112EN2E > 0111                                                                                                                |   |     |             | ±28      | μV        |

|                                | Conversion Time                                  | (Note 6)                                                                                                                               |   |     | 100         | 120      | ms        |

| t <sub>CONVERT</sub>           | it and Duty Cycle Readback                       |                                                                                                                                        |   |     | 100         |          | 1113      |

| D_RES                          | Resolution                                       |                                                                                                                                        |   |     | 10          |          | Bits      |

| D_TUE                          | Total Unadjusted Error                           | 16.3% Duty Cycle                                                                                                                       |   | -3  | 10          | 3        | DIIS<br>% |

|                                | Update Rate                                      |                                                                                                                                        |   | -0  | 100         | 5        |           |

| t <sub>CONVERT</sub>           | e Readback (TO, T1, T2)                          | (Note 6)                                                                                                                               |   |     | 100         |          | ms        |

| -                              | Resolution                                       |                                                                                                                                        |   |     | 0.25        |          | °C        |

| T <sub>RES_T</sub><br>T0,1_TUE | External TSNS TUE                                | $\Delta V_{\text{TSNS}} = 72 \text{mV} \text{ (Note 8)}$                                                                               |   |     | 0.25        |          | 0°<br>0°  |

| <u>10,1_10E</u><br>T2_TUE      | Internal TSNS TUE                                |                                                                                                                                        | - |     | .1          | ±3       | 0°<br>0°  |

|                                |                                                  | $V_{\text{RUN0,1}} = 0.0V$ , $f_{\text{SYNC}} = 0$ kHz (Note 8)                                                                        |   |     | ±1          |          |           |

| tconvert_t                     | Update Rate                                      | (Note 6)                                                                                                                               |   |     | 100         |          | ms        |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 2) V<sub>IN</sub> = 12V, V<sub>RUN0,1</sub> = 3.3V, f<sub>SYNC</sub> = 500kHz (externally driven) unless otherwise specified.

| SYMBOL                   | PARAMETER                                                                                     | CONDITIONS                                                                                                                                                                        |   | MIN    | ТҮР                             | MAX  | UNITS                           |

|--------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|---------------------------------|------|---------------------------------|

| INTV <sub>CC</sub> Regu  | lator                                                                                         |                                                                                                                                                                                   |   |        |                                 |      |                                 |

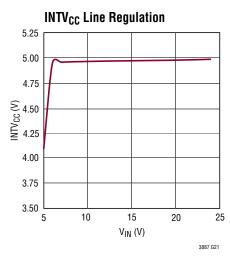

| VINTVCC                  | Internal V <sub>CC</sub> Voltage No Load                                                      | $6V < V_{IN} < 24V$                                                                                                                                                               |   | 4.8    | 5                               | 5.2  | V                               |

| V <sub>LDO INT</sub>     | INTV <sub>CC</sub> Load Regulation                                                            | I <sub>CC</sub> = 0mA to 50mA                                                                                                                                                     |   |        | 0.5                             | ±2   | %                               |

| V <sub>DD33</sub> Regula |                                                                                               |                                                                                                                                                                                   | 1 |        |                                 |      |                                 |

| V <sub>DD33</sub>        | Internal V <sub>DD33</sub> Voltage                                                            | 4.5V < V <sub>INTVCC</sub>                                                                                                                                                        | 1 | 3.2    | 3.3                             | 3.4  | V                               |

| ILIM(VDD33)              | V <sub>DD33</sub> Current Limit                                                               | V <sub>DD33</sub> = GND                                                                                                                                                           |   |        | 70                              |      | mA                              |

| V <sub>DD33</sub> OV     | V <sub>DD33</sub> Overvoltage Threshold                                                       |                                                                                                                                                                                   |   |        | 3.5                             |      | V                               |

| V <sub>DD33</sub> UV     | V <sub>DD33</sub> Undervoltage Threshold                                                      |                                                                                                                                                                                   |   |        | 3.1                             |      | V                               |

| V <sub>DD25</sub> Regula |                                                                                               |                                                                                                                                                                                   |   |        | 0.1                             |      |                                 |

| V <sub>DD25</sub>        | Internal V <sub>DD25</sub> Voltage                                                            |                                                                                                                                                                                   | 1 |        | 2.5                             |      | V                               |

| ILIM(VDD25)              | V <sub>DD25</sub> Current Limit                                                               | $V_{DD25} = GND$                                                                                                                                                                  |   |        | 50                              |      | mA                              |

|                          | d Phase-Locked Loop                                                                           |                                                                                                                                                                                   | I |        |                                 |      |                                 |

| f <sub>OSC</sub>         | Oscillator Frequency Accuracy                                                                 | 250kHz < f <sub>SYNC</sub> < 1MHz Measured Falling<br>Edge-to-Falling Edge of SYNC with SWITCH_<br>FREQUENCY = 250.0 and 1000.0                                                   | • |        |                                 | ±7.5 | %                               |

| V <sub>TH,SYNC</sub>     | SYNC Input Threshold                                                                          | V <sub>CLKIN</sub> Falling<br>V <sub>CLKIN</sub> Rising                                                                                                                           |   |        | 1<br>1.5                        |      | V<br>V                          |

| V <sub>OL,SYNC</sub>     | SYNC Low Output Voltage                                                                       | I <sub>LOAD</sub> = 3mA                                                                                                                                                           |   |        | 0.2                             | 0.4  | V                               |

| LEAKSYNC                 | SYNC Leakage Current in Slave Mode                                                            | $0V \le V_{PIN} \le 3.6V$                                                                                                                                                         |   |        |                                 | ±5   | μA                              |

| θSYNC-θ0                 | SYNC to ChO Phase Relationship Based on<br>the Falling Edge of Sync and Rising Edge of<br>TGO | MFR_PWM_CONFIG_LTC3887[2:0] = 0, 2, 3<br>MFR_PWM_CONFIG_LTC3887[2:0] = 5<br>MFR_PWM_CONFIG_LTC3887[2:0] = 1<br>MFR_PWM_CONFIG_LTC3887[2:0] = 4, 6                                 |   |        | 0<br>60<br>90<br>120            |      | Deg<br>Deg<br>Deg<br>Deg        |

| θSYNC-θ1                 | SYNC to Ch1 Phase Relationship Based on<br>the Falling Edge of Sync and Rising Edge of<br>TG1 | MFR_PWM_CONFIG_LTC3887[2:0] = 3<br>MFR_PWM_CONFIG_LTC3887[2:0] = 0<br>MFR_PWM_CONFIG_LTC3887[2:0] = 2, 4, 5<br>MFR_PWM_CONFIG_LTC3887[2:0] = 1<br>MFR_PWM_CONFIG_LTC3887[2:0] = 6 |   |        | 120<br>180<br>240<br>270<br>300 |      | Deg<br>Deg<br>Deg<br>Deg<br>Deg |

| EEPROM Cha               |                                                                                               |                                                                                                                                                                                   | 1 | ·      |                                 | r    |                                 |

| Endurance                | (Note 13)                                                                                     | 0°C < T <sub>J</sub> < 85°C During EEPROM Write<br>Operations                                                                                                                     | • | 10,000 |                                 |      | Cycles                          |

| Retention                | (Note 13)                                                                                     | T <sub>J</sub> < T <sub>JMAX</sub>                                                                                                                                                |   | 10     |                                 |      | Years                           |

| Mass_Write               | Mass Write Operation Time                                                                     | STORE_USER_ALL, 0°C < TJ < 85°C During<br>EEPROM Write Operations                                                                                                                 | • |        | 440                             | 4100 | ms                              |

| Digital Input            | s SCL, SDA, RUNO, RUN1, GPIOO, GPIO1                                                          |                                                                                                                                                                                   |   |        |                                 |      |                                 |

| V <sub>IH</sub>          | Input High Threshold Voltage                                                                  | SCL, SDA, RUN0, RUN1, GPIOO, GPIO1                                                                                                                                                |   |        |                                 | 2.0  | V                               |

| V <sub>IL</sub>          | Input Low Threshold Voltage                                                                   | SCL, SDA, RUN0, RUN1, GPIOO, GPIO1                                                                                                                                                |   | 1.4    |                                 |      | V                               |

| V <sub>HYST</sub>        | Input Hysteresis                                                                              | SCL, SDA                                                                                                                                                                          |   |        | 0.08                            |      | V                               |

| C <sub>PIN</sub>         | Input Capacitance                                                                             |                                                                                                                                                                                   |   |        |                                 | 10   | pF                              |

| <b>Digital Input</b>     | WP                                                                                            |                                                                                                                                                                                   |   |        |                                 |      |                                 |

| I <sub>PUWP</sub>        | Input Pull-Up Current                                                                         | WP                                                                                                                                                                                |   |        | 10                              |      | μA                              |

|                          | Dutputs SCL, SDA, GPIOO, GPIO1, ALERT, RUN                                                    |                                                                                                                                                                                   |   |        |                                 |      |                                 |

| V <sub>OL</sub>          | Output Low Voltage                                                                            | I <sub>SINK</sub> = 3mA                                                                                                                                                           |   |        |                                 | 0.4  | V                               |

| Digital Input            | s SHARE_CLK, WP                                                                               |                                                                                                                                                                                   |   |        |                                 |      |                                 |

| V <sub>IH</sub>          | Input High Threshold Voltage                                                                  |                                                                                                                                                                                   |   |        | 1.5                             | 1.8  | V                               |

| V <sub>IL</sub>          | Input Low Threshold Voltage                                                                   |                                                                                                                                                                                   |   | 0.6    | 1                               |      | V                               |

| Leakage Cur              | rent SDA, SCL, ALERT, RUNO, RUN1                                                              |                                                                                                                                                                                   |   |        |                                 |      |                                 |

| l <sub>OL</sub>          | Input Leakage Current                                                                         | $0V \le V_{PIN} \le 5.5V$                                                                                                                                                         |   |        |                                 | ±5   | μA                              |

|                          |                                                                                               |                                                                                                                                                                                   |   |        |                                 |      |                                 |

#### **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . (Note 2)  $V_{IN} = 12V$ ,  $V_{RUN0.1} = 3.3V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL                   | PARAMETER                                                                                    | CONDITIONS                               |   | MIN      | ТҮР       | MAX   | UNITS    |

|--------------------------|----------------------------------------------------------------------------------------------|------------------------------------------|---|----------|-----------|-------|----------|

| Leakage Curr             | ent GPIOO, GPIO1                                                                             |                                          |   |          |           |       |          |

| I <sub>GL</sub>          | Input Leakage Current                                                                        | $0V \le V_{PIN} < 3.6V$                  |   |          |           | ±5    | μA       |

| Digital Filteri          | ng of GPIOO, GPIO1                                                                           |                                          |   |          |           |       |          |

| I <sub>FLTG</sub>        | Input Digital Filtering GPIO                                                                 |                                          |   |          | 3         |       | μs       |

| Digital Filteri          | ng of RUNO, RUN1                                                                             |                                          |   |          |           |       |          |

| I <sub>FLTR</sub>        | Input Digital Filtering RUN                                                                  |                                          |   |          | 10        |       | μs       |

| PMBus Interfa            | ace Timing Characteristics                                                                   |                                          |   |          |           |       |          |

| f <sub>SMB</sub>         | Serial Bus Operating Frequency                                                               |                                          |   | 10       |           | 400   | kHz      |

| t <sub>BUF</sub>         | Bus Free Time Between Stop and Start                                                         |                                          |   | 1.3      |           |       | μs       |

| t <sub>HD,STA</sub>      | Hold time After Repeated Start Condition.<br>After this Period, the First Clock is Generated |                                          | • | 0.6      |           |       | μs       |

| t <sub>SU,STA</sub>      | Repeated Start Condition Setup Time                                                          |                                          |   | 0.6      |           |       | μs       |

| t <sub>SU,STO</sub>      | Stop Condition Setup Time                                                                    |                                          |   | 0.6      |           |       | μs       |

| t <sub>hd,dat</sub>      | Data Hold Time<br>Receiving Data<br>Transmitting Data                                        |                                          | • | 0<br>0.3 |           | 0.9   | μs<br>µs |

| t <sub>SU,DAT</sub>      | Data Setup Time<br>Receiving Data                                                            |                                          | • | 0.1      |           |       | μs       |

| t <sub>timeout_smb</sub> | Stuck PMBus Timer Non-Block Reads<br>Stuck PMBus Timer Block Reads                           | Measured from the Last PMBus Start Event |   |          | 32<br>150 |       | ms<br>ms |

| t <sub>LOW</sub>         | Serial Clock Low Period                                                                      |                                          |   | 1.3      |           | 10000 | μs       |

| t <sub>HIGH</sub>        | Serial Clock High Period                                                                     |                                          |   | 0.6      |           |       | μs       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3887/LTC3887-1 are tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3887E/LTC3887E-1 are guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3887I/LTC3887I-1 are guaranteed over the full -40°C to 125°C operating junction temperature range. T<sub>J</sub> is calculated from the ambient temperature T<sub>A</sub> and power dissipation P<sub>D</sub> according to the following formula:

$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA})$

The maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

Note 3: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

Note 4: Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

Note 5: The data format in PMBus is 5 bits exponent (signed) and 11 bits mantissa (signed). This limits the output resolution to 10 bits though the internal ADC is 16 bits and the calculations use 32-bit words.

Note 6: The data conversion is done in round robin fashion. All inputs signals are continuously converted for a typical latency of 100ms. Unless the MFR\_ADC\_CONTROL command is utilized.

Note 7: The IOUT\_CAL\_GAIN =  $1.0m\Omega$  and MFR\_IOUT\_CAL\_GAIN\_TC = 0.0. Value as read from READ\_IOUT in amperes.

Note 8: Part tested with PWM disabled. Evaluation in application demonstrates capability. TUE (%) = ADC Gain Error (%) + 100 • [Zero Code Offset + ADC Linearity Error]/Actual Value.

Note 9: All VOLT commands assume the ADC is used to auto-zero the output to achieve the stated accuracy. LTC3887 is tested in a feedback loop that servos V<sub>OUT</sub> to a specified value.

Note 10: The maximum V<sub>OUT</sub> voltage is 5.5V.

Note 11: The maximum V<sub>IN</sub> voltage is 28V.

Note 12: When  $V_{IN} < 6V$ , INTV<sub>CC</sub> must be tied to  $V_{IN}$ .

Note 13: EEPROM endurance and retention are guaranteed by design, characterization and correlation with statistical process controls. The minimum retention specification applies for devices whose EEPROM has been cycled less than the minimum endurance specification. The RESTORE\_USER\_ALL command (EEPROM read) is valid over the entire operating junction temperature range.

3887 G16

$V_{IN}(V)$

TEMPERATURE (°C)

3887 G17

3887 G18

V<sub>OUT</sub> (V)

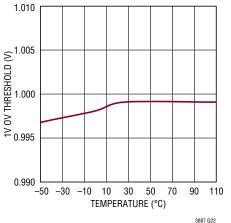

V<sub>OUT</sub> OV Threshold vs Temperature (1V Target)

Vout OV Threshold vs Temperature (2V Target)

50 75 100 125 150

TEMPERATURE (°C)

3887 G23

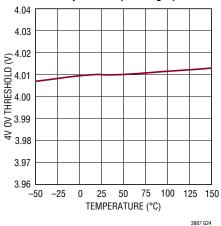

V<sub>OUT</sub> OV Threshold vs Temperature (4V Target)

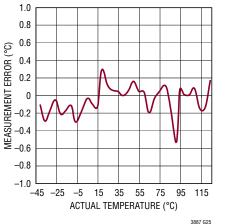

Temperature Error vs Temperature

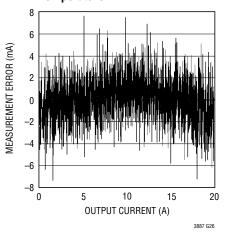

I<sub>OUT</sub> Error vs I<sub>OUT</sub> Room Temperature

25

1.97

-50

-25 0

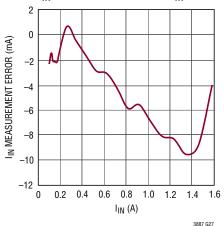

I<sub>IN</sub> Measurement Error vs I<sub>IN</sub>

### PIN FUNCTIONS

VSENSE0<sup>+</sup> (Pin 1): Channel O Positive Voltage Sense Input.

VSENSEO<sup>-</sup> (Pin 2): Channel O Negative Voltage Sense Input.

$I_{TH0}/I_{TH1}$  (Pin 5/Pin 26): Current Control Threshold and Error Amplifier Compensation Nodes. Each associated channel's current comparator tripping threshold increases with its  $I_{TH}$  voltage.

**I**<sub>SENSEO</sub><sup>+</sup>/**I**<sub>SENSE1</sub><sup>+</sup> (**Pins 6/Pin 3**): Current Sense Comparator Inputs. The (+) inputs to the current comparators are normally connected to DCR sensing networks or current sensing resistors.

**I**SENSE0<sup>-</sup>/**I**SENSE1<sup>-</sup> (**Pin 7/Pin 4**): Current Sense Comparator Inputs. The (–) inputs are connected to the low side of the current sense element.

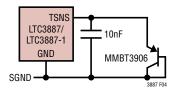

**SYNC (Pin 8):** External Clock Synchronization Input and Open-Drain Output Pin. If an external clock is present at this pin, the switching frequency will be synchronized to the external clock. If the SYNC output is enabled, this pin will pull low at the switching frequency with a 500ns pulse to ground. A resistor pull up to 3.3V is required in the application if the LTC3887 SYNC output is enabled.

**SCL (Pin 9):** Serial Bus Clock Input. Open-drain output, can hold the output low if clock stretching is enabled. A pull-up resistor to 3.3V is required in the application.

**SDA (Pin 10):** Serial Bus Data Input and Output. A pull-up resistor to 3.3V is required in the application.

**ALERT** (Pin 11): Open-Drain Digital Output. Connect the SMBALERT signal to this pin. A pull-up resistor to 3.3V is required in the application.

**GPI00/GPI01 (Pin 12/Pin 13):** Digital Programmable General Purpose Inputs and Outputs. Open-drain output. A pull-up resistor to 3.3V is required in the application.

**RUN0/RUN1 (Pin 14/Pin 15):** Enable Run Input and Output. Logic high on these pins enables the controller. Open-drain output holds the pin low until the LTC3887 is out of reset. A pull-up resistor to 3.3V is required in the application.

**ASELO (Pin 16):** Serial Bus Address Configuration Input. Connect a  $\pm 1\%$  resistor divider between the chip V<sub>DD25</sub> ASELO and SGND in order to select the 4LSBs of the serial bus interface address. A resistor divider on ASELO is recommended if there are more than one LTC3887s on the same board to assure the user can independently program each IC. If the pin is left open, the IC will use the value programmed in the EEPROM. Minimize capacitance when the pin is open to assure accurate detection of the pin state.

**ASEL1 (Pin 17):** Serial Bus Address Configuration Input. Connect a  $\pm 1\%$  resistor divider between the chip V<sub>DD25</sub> ASEL1 and SGND in order to select the 3MSBs of the serial bus interface address. A resistor divider on ASEL1 is recommended if there are more than 16 LTC3887s on the same board to assure the user can independently program each IC. If the pin is left open, the IC will use the value programmed in the EEPROM. Minimize capacitance when the pin is open to assure accurate detection of the pin state.

### PIN FUNCTIONS

**FREQ\_CFG (Pin 20):** Frequency Select Pin. Connect a  $\pm 1\%$  resistor divider between the chip V<sub>DD25</sub> FREQ\_CFG and GND in order to select switching frequency. If the pin is left open, the IC will use the value programmed in the EEPROM. Minimize capacitance when the pin is open to assure accurate detection of the pin state.

**PHAS\_CFG (Pin 21):** Phase Select Pin. Connect a  $\pm 1\%$  resistor divider between the chip V<sub>DD25</sub> PHAS\_CFG and GND in order to select channel phasing. If the pin is left open, the IC will use the value programmed in the EEPROM. Minimize capacitance when the pin is open to assure accurate detection of the pin state.

**Vouto\_CFG/Vout1\_CFG (Pin 18/Pin 19):** Voltage Select Pin. Connect a  $\pm 1\%$  resistor divider between the chip V<sub>DD25</sub> V<sub>OUT</sub>*n\_*CFG and GND in order to adjust the output voltage set point. If the pin is left open, the IC will use EEPROM. Minimize capacitance when the pin is open to assure accurate detection of the pin state.

$V_{DD25}$  (Pin 22): Internally Generated 2.5V power Supply Output Pin. Bypass this pin to GND with a low ESR 1µF capacitor. Do not load this pin with external current except for the ±1% resistor dividers required for the configuration pins.

**WP (Pin 23):** Write Protect Pin Active High. An internal  $10\mu$ A current source pulls the pin to V<sub>DD33</sub>. If WP is high, the PMBus writes are restricted.

**SHARE\_CLK (Pin 24):** Share Clock, Bidirectional Open-Drain Clock Sharing Pin. Nominally 100kHz. Used to synchronize the timing between multiple LTC388Xs. Tie all SHARE\_CLK pins together. All LTC388Xs will synchronize to the fastest clock. A pull-up resistor to 3.3V is required.

**V<sub>DD33</sub> (Pin 25):** Internally Generated 3.3V Power Supply Output Pin. Bypass this pin to GND with a low ESR 1µF capacitor. Do not load this pin with external current except for the pull-up resistors required for GPIO*n*, SCLK, SYNC and possibly RUN*n*, ALERT, SDA and SCL.

**V**<sub>SENSE1</sub> (**Pin 27**): Channel 1 Voltage Sense Input. This input voltage is referenced to the GND pin.

**INTV<sub>CC</sub>** (Pin 33): Internal Regulator 5V Output. The control circuits are powered from this voltage. Decouple this pin to power ground with a minimum of  $4.7\mu$ F low ESR tantalum or ceramic capacitor.

**GNDSNS (Pin 34):** Ground Sense Pin. This pin is connected to the back paddle ground and can be used to

detect if there is a good ground connection between the back paddle and the board.

$V_{IN}$  (Pin 35): Main Input Supply. Decouple this pin to PGND with a capacitor (0.1µF to 1µF). For applications where the main input power is 5V, tie the V<sub>IN</sub> and INTV<sub>CC</sub> pins together.

**BG0/BG1 (Pin 36/Pin 32):** Bottom Gate Driver Outputs. These pins drive the gates of the bottom N-Channel MOSFETs between PGND and  $INTV_{CC}$ . BG0/BG1 are not connected on the LTC3887-1. They may be floated or tied to ground.

**BOOSTO/BOOST1 (LTC3887) (Pin 37/Pin 31):** Boosted Floating Driver Supplies. The (+) terminal of the bootstrap capacitors connect to these pins. These pins swing from a diode voltage drop below  $INTV_{CC}$  up to  $V_{IN} + INTV_{CC}$ .

$V_{CC0}/V_{CC1}$  (LTC3887-1) (Pins 37/31): These pins should be connected to INTV<sub>CC</sub> or V<sub>DD33</sub>.

**TG0/TG1 (LTC3887) (Pin 38/Pin 30):** Top Gate Driver Outputs. These are the outputs of floating drivers with a voltage swing equal to  $INTV_{CC}$  superimposed on the switch node voltages.

**PWM0/PWM1 (LTC3887-1) (Pin 38/Pin 30):** PWM Outputs. These are the three-state control outputs with a voltage swing of GND to  $V_{CC}$  used to control gate drivers. The LTC3887-1 PWM pin is three-state which is required to produce discontinuous operation in some gate driver or DrMOS circuits.

**SW0/SW1 (LTC3887) (Pin 39/Pin 29):** Switch Node Connections to Inductors. Voltage swings at the pins are from a Schottky diode (external) voltage drop below ground to  $V_{IN}$ . In the LTC3887-1 these pins are not connected to internal circuitry. They may be floated or tied to ground.

**TSNS0/TSNS1 (Pin 40/Pin 28):** Channel 0,1 External Diode Temperature Sense. Connect to the anode of a diode connected PNP transistor and directly connect the cathode to SGND in order to sense remote temperature. If external temperature sense elements are not installed, short pin to ground and set the UT\_FAULT\_LIMIT to -275°C, IOUT\_CAL\_GAIN\_TC set to zero and the UT\_FAULT\_RE-SPONSE to ignore.

**GND (Exposed Pad Pin 41):** Ground. Both the smallsignal and compensation components should connect to this ground, which in turn connects to power ground at one point.

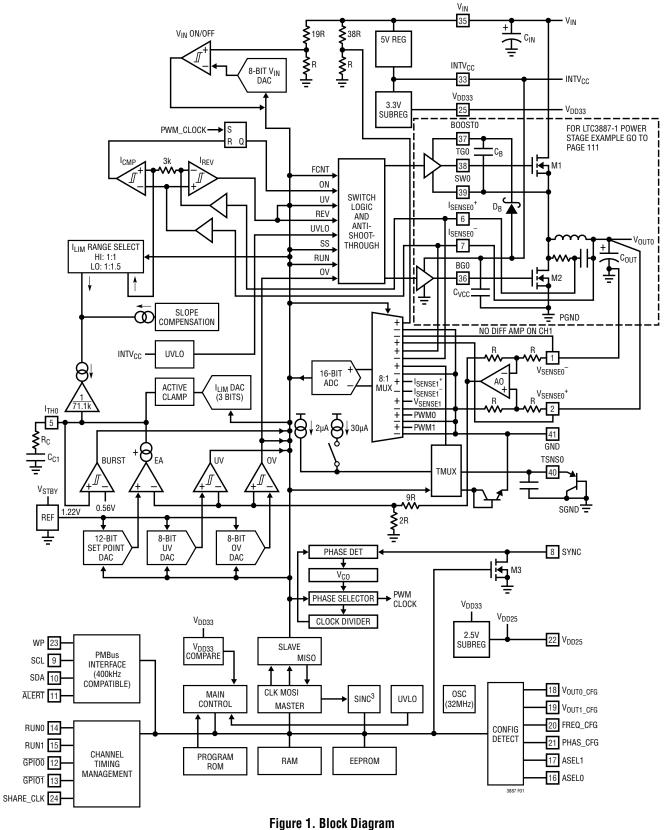

### **BLOCK DIAGRAM** One of two channels (CHO) shown. (LTC3887 application only)

Tigute 1. Diock Diagram

#### OVERVIEW

The LTC3887/LTC3887-1 are a dual channel/dual phase, constant frequency, analog current mode controller for DC/DC step-down applications with a digital interface. The LTC3887 is used in applications where the gate driver is required. The LTC3887-1 is used in applications where the gate driver is external, for example a DrMOS power stage. The LTC3887-1 allows the TG pin to three-state which is required to produce discontinuous operation in some gate driver DrMOS circuits. Discontinuous operation assures the inductor current remains positive and is required to start up into a prebiased load.

The LTC3887 is very similar in features to the LTC3880. The major improvements are as follows:

- T<sub>INIT</sub> start-up time 70ms

- VOUT0/VOUT1 are both programmable up to 5.5 Volts

- PWM synchronization circuit, review Frequency and Phasing section for details

- MFR\_ADC\_CONTROL for fast ADC sampling of one parameter. See PMBus Command Details.

- PMBus compliant to version 1.2 which adds PAGE \_PLUS and SMBALERT mask. See PMBus Command Details.

- Improved fault logging. See PMBus Command Details.

- Share EA for channel 0/1 for 2-phase operation

- Resistor configuration pins modified. There are two Address select pins, VOUTn\_CONFIG, PHAS\_CONFIG and FREQ\_CONFIG. The VOUTn\_TRIM pins were removed.

The LTC3887 digital interface is compatible with PMBus which supports bus speeds of up to 400kHz. A typical application circuit is shown on the first page of this data sheet.

Major features include:

- Programmable Output Voltage

- Programmable Input Voltage Comparator

- Programmable Current Limit

- Programmable Switching Frequency

- Programmable OV and UV Comparators

- Programmable On and Off Delay Times

- Programmable Output Rise/Fall Times

- Phase-Locked Loop for Synchronous, Polyphase Operation (2, 3, 4 or 6 Phases)

- Input and Output Voltage/Current, Temperature and Duty Cycle Telemetry

- Fully Differential Load Sense

- Integrated Gate Drivers (LTC3887)

- Non-Volatile Configuration Memory

- Optional External Configuration Resistors for Key Operating Parameters

- Optional Time-Base Interconnect for Synchronization Between Multiple Controllers

- Fault Logging

- WP Pin to Protect Internal Configuration

- Standalone Operation After User Factory Configuration

- PMBus, 400kHz Compliant Interface

The PMBus interface provides access to important power management data during system operation including:

- Internal Die Temperature

- External System Temperature via Optional Diode Sense Elements

- Average Output Current

- Average PWM Duty Cycle

- Average Output Voltage

- Average Input Voltage

- Average Input Current

- Configurable, Latched and Unlatched Individual Fault and Warning Status

Individual channels are accessed through the PMBus using the PAGE command, i.e., PAGE 0 or 1.

Fault reporting and shutdown behavior are fully configurable. Two individual GPIO outputs are provided (GPIOO, GPI01), both of which can be masked independently. A dedicated pin for ALERT is provided. The shutdown operation also allows all faults to be individually masked and can be operated in either unlatched (hiccup) or latched modes.

Individual status commands enable fault reporting over the serial bus to identify the specific fault event. Fault or warning detection includes the following:

- Output Undervoltage/Overvoltage

- Input Undervoltage/Overvoltage

- Input and Output Overcurrent

- Internal Overtemperature