# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# TECHNOLOGY

LTC4100

# Smart Battery Charger Controller

# FEATURES

- Single Chip Smart Battery Charger Controller

- 100% Compliant (Rev. 1.1) SMBus Support Allows for Operation with or without Host

- SMBus Accelerator Improves SMBus Timing

- Wide Output Voltage Range: 3.5V to 26V

- Hardware Interrupt and SMBAlert Response Eliminate Interrupt Polling

- High Efficiency Synchronous Buck Charger

- 0.5V Dropout Voltage; Maximum Duty Cycle > 98%

- AC Adapter Current Limit Maximizes Charge Rate

- ±0.8% Voltage Accuracy; ±4% Current Accuracy

- Up to 4A Charging Current Capability

- 10-Bit DAC for Charge Current Programming

- 11-Bit DAC for Charger Voltage Programming

- User-Selectable Overvoltage and Overcurrent Limits

- High Noise Immunity SafetySignal Sensor

- Available in a 24-Pin SSOP Package

### **APPLICATIONS**

Portable Instruments and Computers

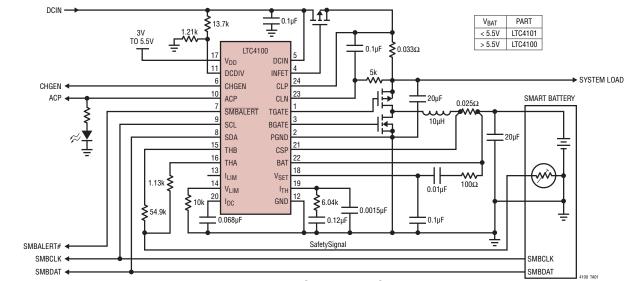

TYPICAL APPLICATION

Data Storage Systems and Battery Backup Servers

LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6650174 and 5723970.

### DESCRIPTION

The LTC®4100 Smart Battery Charger is a single chip charging solution that dramatically simplifies construction of an SBS compliant system. The LTC4100 implements a Level 2 charger function whereby the charger can be programmed by the battery or by the host. A SafetySignal on the battery being charged is monitored for temperature, connectivity and battery type information. The SMBus interface remains alive when the AC power adapter is removed and responds to all SMBus activity directed to it, including SafetySignal status (via the ChargerStatus command). The charger also provides an interrupt to the host whenever a status change is detected (e.g., battery removal, AC adapter connection).

Charging current and voltage are restricted to chemistryspecific limits for improved system safety and reliability. Limits are programmable by two external resistors. Additionally, the maximum average current from the AC adapter is programmable to avoid overloading the adapter when simultaneously supplying load current and charging current. When supplying system load current, charging current is automatically reduced to prevent adapter overload.

#### Figure 1. 4A Smart Battery Charger

# **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| Voltage from V <sub>DD</sub> to GND7V/-0.3V<br>Voltage from CHGEN, DCDIV, SDA, |

|--------------------------------------------------------------------------------|

| SCL and SMBALERT to GND                                                        |

| Voltage from DCIN, CLP, CLN to GND                                             |

| Voltage from CLP to CLN±0.3V                                                   |

| PGND wrt. GND ±0.3V                                                            |

| CSP, BAT to GND 28V/–5V                                                        |

| Operating Ambient Temperature Range (Note 4)<br>-40°C to 85°C                  |

| Junction Temperature Range –40°C to 125°C                                      |

| Storage Temperature Range65°C to 150°C<br>Lead Temperature (Soldering, 10 sec) |

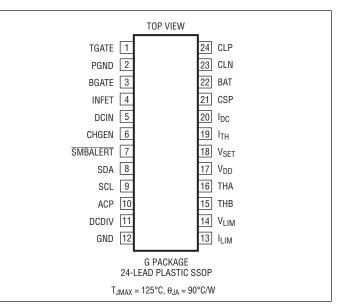

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL   | PART MARKING | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|-------------------|-----------------|--------------|----------------------|-------------------|

| LTC4100EG#PBF     | LTC4100EG#TRPBF | LTC4100EG    | 24-Lead Plastic SSOP | -40°C to 85°C     |

| LEAD BASED FINISH | TAPE AND REEL   | PART MARKING | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

| LTC4100EG         | LTC4100EG#TR    | LTC4100EG    | 24-Lead Plastic SSOP | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>DD</sub> = 3.3V, V<sub>BAT</sub> = 12V unless otherwise noted. (Note 4)

| SYMBOL           | PARAMETER                         |                                                                                   | MIN | ТҮР        | MAX | UNITS    |        |

|------------------|-----------------------------------|-----------------------------------------------------------------------------------|-----|------------|-----|----------|--------|

|                  | DCIN Operating Range              |                                                                                   | •   | 6          |     | 28       | V      |

|                  | DCIN Operating Current            | Charging, Sum of Currents on DCIN, CLP and CLN                                    |     |            | 3   | 5        | mA     |

| V <sub>TOL</sub> | Charge Voltage Accuracy           | (Note 2)                                                                          | •   | -0.8<br>-1 |     | 0.8<br>1 | %<br>% |

| I <sub>TOL</sub> | Charge Current Accuracy (Note 3)  | V <sub>CSP</sub> – V <sub>BAT</sub> Target = 102.3mV<br>I <sub>DAC</sub> = 0xFFFF | •   | -4<br>-5   |     | 4<br>5   | %      |

| V <sub>DD</sub>  | V <sub>DD</sub> Operating Voltage | $0V \le V_{DCIN} \le 28V$                                                         | •   | 3          |     | 5.5      | V      |

| Shutdown         |                                   |                                                                                   |     |            |     |          |        |

|                  | Battery Leakage Current           | $DCIN = 0V, V_{CLP} = V_{CLN} = V_{CSP} = V_{BAT}$                                | •   |            | 15  | 35       | μA     |

| UVLO             | Undervoltage Lockout Threshold    | DCIN Rising, V <sub>BAT</sub> = 0V                                                | •   | 4.2        | 4.7 | 5.5      | V      |

|                  | V <sub>DD</sub> Power-Fail        | Part Held in Reset Until this V <sub>DD</sub> Present                             | •   |            |     | 3        | V      |

|                  | DCIN Current in Shutdown          | V <sub>CHGEN</sub> = 0V                                                           |     |            | 2   | 3        | mA     |

|                  |                                   |                                                                                   |     |            |     |          | 4100fc |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>DD</sub> = 3.3V, V<sub>BAT</sub> = 12V unless otherwise noted. (Note 4)

| SYMBOL            | PARAMETER                                                                    | MIN                                                                              | TYP | MAX | UNITS    |                       |         |

|-------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|----------|-----------------------|---------|

| Current Se        | ense Amplifier, CA1                                                          |                                                                                  |     |     |          |                       |         |

|                   | Input Bias Current into BAT Pin                                              |                                                                                  |     |     | 11.66    |                       | μA      |

| CMSL              | CA1/I <sub>1</sub> Input Common Mode Low                                     |                                                                                  | •   | 0   |          |                       | V       |

| CMSH              | CA1/I <sub>1</sub> Input Common Mode High                                    | $V_{\text{DCIN}} \le 28V$                                                        | •   |     |          | V <sub>CLN</sub> -0.2 | V       |

| Current Co        | mparators I <sub>CMP</sub> and I <sub>REV</sub>                              | 1                                                                                |     |     |          |                       |         |

| I <sub>TMAX</sub> | Maximum Current Sense Threshold (V <sub>CSP</sub> -V <sub>BAT</sub> )        | V <sub>ITH</sub> = 2.5V                                                          |     | 140 | 165      | 200                   | mV      |

| I <sub>TREV</sub> | Reverse Current Threshold (V <sub>CSP</sub> –V <sub>BAT</sub> )              |                                                                                  |     |     | - 30     |                       | mV      |

| Current Se        | ense Amplifier, CA2                                                          |                                                                                  |     |     |          |                       |         |

|                   | Transconductance                                                             |                                                                                  |     |     | 1        |                       | mmho    |

|                   | Source Current                                                               | Measured at I <sub>TH</sub> , V <sub>ITH</sub> = 1.4V                            |     |     | -40      |                       | μA      |

|                   | Sink Current                                                                 | Measured at I <sub>TH</sub> , V <sub>ITH</sub> = 1.4V                            |     |     | 40       |                       | μA      |

| Current Li        | mit Amplifier                                                                | 1                                                                                |     |     |          |                       |         |

|                   | Transconductance                                                             |                                                                                  |     |     | 1.5      |                       | mmho    |

| V <sub>CLP</sub>  | Current Limit Threshold                                                      |                                                                                  | •   | 93  | 100      | 107                   | mV      |

| I <sub>CLN</sub>  | CLN Input Bias Current                                                       |                                                                                  |     |     | 100      |                       | nA      |

| -                 | ror Amplifier, EA                                                            | L                                                                                |     |     |          |                       | <u></u> |

|                   | Transconductance                                                             |                                                                                  |     |     | 1        |                       | mmho    |

|                   | Sink Current                                                                 | Measured at I <sub>TH.</sub> V <sub>ITH</sub> = 1.4V                             |     |     | 36       |                       | μA      |

| OVSD              | Overvoltage Shutdown Threshold as a Percent of<br>Programmed Charger Voltage |                                                                                  | •   | 102 | 107      | 110                   | %       |

| Input P-Ch        | annel FET Driver (INFET)                                                     |                                                                                  |     |     |          |                       |         |

|                   | DCIN Detection Threshold (V <sub>DCIN</sub> -V <sub>CLP</sub> )              | DCIN Voltage Ramping Up from V <sub>CLP</sub> -0.05V                             |     | 0   | 0.17     | 0.25                  | V       |

|                   | Forward Regulation Voltage (V <sub>DCIN</sub> –V <sub>CLP</sub> )            |                                                                                  | •   |     | 25       | 50                    | mV      |

|                   | Reverse Voltage Turn-Off Voltage (V <sub>DCIN</sub> -V <sub>CLP</sub> )      |                                                                                  | •   | -60 | -25      |                       | mV      |

|                   | INFET ON Clamping Voltage (V <sub>DCIN</sub> -V <sub>INFET</sub> )           | I <sub>INFET</sub> = 1μA                                                         | •   | 5   | 5.8      | 6.5                   | V       |

|                   | INFET OFF Clamping Voltage (V <sub>DCIN</sub> –V <sub>INFET</sub> )          | I <sub>INFET</sub> = -25μA                                                       |     |     |          | 0.25                  | V       |

| Oscillator        |                                                                              | -                                                                                |     |     |          |                       |         |

| fosc              | Regulator Switching Frequency                                                |                                                                                  |     | 255 | 300      | 345                   | kHz     |

| f <sub>MIN</sub>  | Regulator Switching Frequency in Drop Out                                    | Duty Cycle ≥ 98%                                                                 |     | 20  | 25       |                       | kHz     |

| DC <sub>MAX</sub> | Regulator Maximum Duty Cycle                                                 | V <sub>CSP</sub> = V <sub>BAT</sub>                                              |     | 98  | 99       |                       | %       |

|                   | ers (TGATE, BGATE)                                                           |                                                                                  |     |     |          | -                     | I       |

|                   | V <sub>TGATE</sub> High (V <sub>CLP</sub> -V <sub>TGATE</sub> )              | I <sub>TGATE</sub> = -1mA                                                        |     |     |          | 50                    | mV      |

|                   | V <sub>BGATE</sub> High                                                      | $C_{LOAD} = 3000 pF$                                                             |     | 4.5 | 5.6      | 10                    | V       |

|                   | V <sub>TGATE</sub> Low (V <sub>CLP</sub> -V <sub>TGATE</sub> )               | $C_{LOAD} = 3000 pF$                                                             |     | 4.5 | 5.6      | 10                    | V       |

|                   | V <sub>BGATE</sub> Low                                                       | I <sub>BGATE</sub> = 1mA                                                         |     |     |          | 50                    | mV      |

| TGTR<br>TGTF      | TGATE Transition Time<br>TGATE Rise Time<br>TGATE Fall Time                  | C <sub>LOAD</sub> = 3000pF, 10% to 90%<br>C <sub>LOAD</sub> = 3000pF, 10% to 90% |     |     | 50<br>50 | 110<br>100            | ns      |

| BGTR<br>BGTF      | BGATE Transition Time<br>BGATE Rise Time<br>BGATE Fall Time                  | C <sub>LOAD</sub> = 3000pF, 10% to 90%<br>C <sub>LOAD</sub> = 3000pF, 10% to 90% |     |     | 40       | 90 80                 | ns      |

|                   | V <sub>TGATE</sub> at Shutdown (V <sub>CLN</sub> -V <sub>TGATE</sub> )       | $I_{\text{TGATE}} = -1\mu\text{A}$                                               |     |     | -10      | 100                   | mV      |

|                   | V <sub>BGATE</sub> at Shutdown (V <sub>CLN</sub> -V <sub>TGATE</sub> )       |                                                                                  |     |     |          | 100                   | mV      |

|                   |                                                                              | I <sub>TGATE</sub> = 1μA                                                         |     |     |          | 100                   |         |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>DD</sub> = 3.3V, V<sub>BAT</sub> = 12V unless otherwise noted. (Note 4)

| SYMBOL           | PARAMETER                                        | CONDITIONS                                                                                                                                     |   | MIN    | ТҮР              | MAX    | UNITS                |

|------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|------------------|--------|----------------------|

| AC Presen        | t Comparator                                     |                                                                                                                                                |   |        |                  |        | 1                    |

| V <sub>ACP</sub> | DCDIV Threshold                                  | V <sub>DCDIV</sub> Rising from 1V to 1.4V                                                                                                      | • | 1.14   | 1.20             | 1.26   | V                    |

|                  | DCDIV Hysteresis                                 |                                                                                                                                                |   |        | 25               |        | mV                   |

|                  | DCDIV Input Bias Current                         | V <sub>DCDIV</sub> = 1.2V                                                                                                                      |   | -1     |                  | 1      | μA                   |

|                  | ACP V <sub>OH</sub>                              | $I_{ACP} = -2mA$                                                                                                                               |   | 2      |                  |        | V                    |

|                  | ACP V <sub>OL</sub>                              | I <sub>ACP</sub> = 1mA                                                                                                                         |   |        |                  | 0.5    | V                    |

|                  | DCDIV to ACP Delay                               | V <sub>DCDIV</sub> = 1.3V                                                                                                                      |   |        |                  | 10     | μs                   |

| SafetySigr       | nal Decoder                                      |                                                                                                                                                | 1 |        |                  |        | 1                    |

|                  | SafetySignal Trip (RES_COLD/RES_OR)              | $ \begin{array}{l} R_{THA} = 1130\Omega \pm 1\%, \ C_{TH} = 1nF \ (Note \ 6) \\ R_{THB} = 54.9 k\Omega \pm 1\% \end{array} $                   | • | 95     | 100              | 105    | kΩ                   |

|                  | SafetySignal Trip (RES_IDEAL/RES_COLD)           | $\begin{array}{l} R_{THA} = 1130\Omega \pm 1\%, \ C_{TH} = 1nF \ (Note \ 6) \\ R_{THB} = 54.9 k\Omega \pm 1\% \end{array}$                     | • | 28.5   | 30               | 31.5   | kΩ                   |

|                  | SafetySignal Trip (RES_HOT/RES_IDEAL)            | $R_{THA}$ = 1130 $\Omega$ ±1%, $C_{TH}$ = 1nF (Note 6) $R_{THB}$ = 54.9k $\Omega$ ±1%                                                          | • | 2.85   | 3                | 3.15   | kΩ                   |

|                  | SafetySignal Trip (RES_UR/RES_HOT)               | $\begin{array}{l} R_{THA} = 1130 \Omega \ \pm 1\%, \ C_{TH} = 1 nF \ (Note \ 6) \\ R_{THB} = 54.9 k \Omega \ \pm 1\% \end{array}$              | • | 425    | 500              | 575    | Ω                    |

|                  | Time Between SafetySignal Measurements           | DCDIV = 1.3V<br>DCDIV = 1V                                                                                                                     |   |        | 32               | 250    | ms<br>ms             |

| DACs             | 1                                                |                                                                                                                                                |   |        |                  |        |                      |

|                  | Charging Current Resolution                      | Guaranteed Monotonic Above I <sub>MAX</sub> /16                                                                                                |   | 10     |                  |        | Bits                 |

|                  | Charging Current Granularity                     | R <sub>ILIM</sub> = 0<br>R <sub>ILIM</sub> = 10k ±1%<br>R <sub>ILIM</sub> = 33k ±1%<br>R <sub>ILIM</sub> = Open (or Short to V <sub>DD</sub> ) |   |        | 1<br>2<br>4<br>4 |        | mA<br>mA<br>mA<br>mA |

|                  | Wake-Up Charging Current (I <sub>WAKE-UP</sub> ) | All Values of R <sub>ILIM</sub><br>All Values of R <sub>VLIM</sub>                                                                             |   |        | 80 (Note 5       | 5)     | mA                   |

|                  | Charging Current Limit<br>CSP – BAT              | R <sub>ILIM</sub> = 0 (0-1A)<br>Charging Current = 0x03FF (0x0400 Note 7)                                                                      |   | 97.3   |                  | 107.3  | mV                   |

|                  |                                                  | $R_{ILIM} = 10k \pm 1\%$ (0-2A)<br>Charging Current = 0x07FE (0x0800 Note 7)                                                                   |   | 97.3   |                  | 107.3  | mV                   |

|                  |                                                  | R <sub>ILIM</sub> = 33k ±1% (0-3A)<br>Charging Current = 0x0BFC (0x0C00 Note 7)                                                                |   | 72.3   |                  | 82.3   | mV                   |

|                  |                                                  | R <sub>ILIM</sub> = Open (or Short to V <sub>DD</sub> ) (0-4A)<br>Charging Current = 0x0FFC (0x1000 Note 7)                                    |   | 97.3   |                  | 107.3  | mV                   |

|                  | Charging Voltage Resolution                      | Guaranteed Monotonic (2.9V $\leq$ V <sub>BAT</sub> $\leq$ 28V)                                                                                 |   | 11     |                  |        | Bits                 |

|                  | Charging Voltage Granularity                     |                                                                                                                                                |   |        | 16               |        | mV                   |

|                  | Charging Voltage Limit                           | R <sub>VLIM</sub> = 0<br>Charging Voltage = 0x2260 (Note 7)                                                                                    |   | 8.730  | 8.800            | 8.870  | V                    |

|                  |                                                  | R <sub>VLIM</sub> = 10k ±1%<br>Charging Voltage = 0x3330 (Note 7)                                                                              |   | 12.999 | 13.104           | 13.209 | V                    |

|                  |                                                  | R <sub>VLIM</sub> = 33k ±1%<br>Charging Voltage = 0x4400 (Note 7)                                                                              |   | 17.269 | 17.408           | 17.547 | V                    |

|                  |                                                  | $\begin{array}{l} R_{VLIM} = 100k \ \pm 1\% \\ Charging \ Voltage = 0x5400 \ DCIN \geq 22V \\ (Note \ 7) \end{array}$                          |   | 21.538 | 21.712           | 21.886 | V                    |

|                  |                                                  | $R_{VLIM}$ = Open (or Short to V <sub>DD</sub> )<br>Charging Voltage = 0x6D60 DCIN $\ge$ 29V<br>(Note 7)                                       |   | 27.781 | 28.006           | 28.231 | V                    |

|                  | •                                                |                                                                                                                                                | l |        |                  |        | 4100fc               |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DCIN</sub> = 20V, V<sub>DD</sub> = 3.3V, V<sub>BAT</sub> = 12V unless otherwise noted. (Note 4)

| SYMBOL               | PARAMETER                                                                        | CONDITIONS                                                                                               |       | MIN   | ТҮР | MAX   | UNITS  |

|----------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------|-------|-----|-------|--------|

| Logic Leve           | els                                                                              | 1                                                                                                        |       |       |     |       |        |

| V <sub>IL</sub>      | SCL/SDA Input Low Voltage                                                        | $V_{DD} = 3V$ and $V_{DD} = 5.5V$                                                                        | •     |       |     | 0.8   | V      |

| VIH                  | SCL/SDA Input High Voltage                                                       | $V_{DD} = 3V$ and $V_{DD} = 5.5V$                                                                        | •     | 2.1   |     |       | V      |

| V <sub>OL</sub>      | SDA Output Low Voltage                                                           | I <sub>PULL-UP</sub> = 350μA                                                                             | •     |       |     | 0.4   | V      |

| IIL                  | SCL/SDA Input Current                                                            | $V_{SDA}, V_{SCL} = V_{IL}$                                                                              |       | -1    |     | 1     | μA     |

| I <sub>IH</sub>      | SCL/SDA Input Current                                                            | $V_{SDA}, V_{SCL} = V_{IH}$                                                                              |       | -1    |     | 1     | μA     |

| V <sub>OL</sub>      | SMBALERT Output Low Voltage                                                      | I <sub>PULL-UP</sub> = 500μA                                                                             | •     |       |     | 0.4   | V      |

|                      | SMBALERT Output Pull-Up Current                                                  | V <sub>SMBALERT</sub> = V <sub>OL</sub>                                                                  |       | -17.5 | -10 | -3.5  | μA     |

| I <sub>LEAK</sub>    | SDA/SCL/SMBALERT Power Down Leakage                                              | $V_{SDA}$ , $V_{SCL}$ , $V_{\overline{SMBALERT}}$ = 5.5V, $V_{DD}$ = OV                                  | •     | -2    |     | 2     | μA     |

| V <sub>OL</sub>      | CHGEN Output Low Voltage                                                         | I <sub>OL</sub> = 100μA                                                                                  | •     |       |     | 0.5   | V      |

|                      | CHGEN Output Pull-Up Current                                                     | V <sub>CHGEN</sub> = V <sub>OL</sub>                                                                     | 1     | -17.5 | -10 | -3.5  | μA     |

| V <sub>IL</sub>      | CHGEN Input Low Voltage                                                          |                                                                                                          | •     |       |     | 0.9   | V      |

| V <sub>IH</sub>      | CHGEN Input High Voltage                                                         | V <sub>DD</sub> = 3V<br>V <sub>DD</sub> = 5.5V                                                           | •     | 2.5   | 3.9 |       | V<br>V |

|                      | Power-On Reset Duration                                                          | V <sub>DD</sub> Ramp from 0V to >3V in <5µs                                                              |       |       | 100 |       | μs     |

| SMBus Tir            | ming (Refer to System Management Bus Specifica                                   | tion, Revision 1.1, Section 2.1 for Timing Dia                                                           | grams | ;)    |     |       |        |

| t <sub>HIGH</sub>    | SCL Serial Clock High Period                                                     | $I_{PULL-UP} = 350\mu A$ , $C_{LOAD} = 250pF$ ,<br>$R_{PU} = 9.31k$ , $V_{DD} = 3V$ and $V_{DD} = 5.5V$  | •     | 4     |     |       | μs     |

| t <sub>LOW</sub>     | SCL Serial Clock Low Period                                                      | $I_{PULL-UP} = 350\mu$ A, $C_{LOAD} = 250p$ F,<br>$R_{PU} = 9.31$ k, $V_{DD} = 3$ V and $V_{DD} = 5.5$ V | •     | 4.7   |     | 15000 | μs     |

| t <sub>R</sub>       | SDA/SCL Rise Time                                                                | $C_{LOAD}$ = 250pF, $R_{PU}$ = 9.31k, $V_{DD}$ = 3V and $V_{DD}$ = 5.5V                                  | •     |       |     | 1000  | ns     |

| t <sub>F</sub>       | SDA/SCL Fall Time                                                                | $C_{LOAD}$ = 250pF, $R_{PU}$ = 9.31k, $V_{DD}$ = 3V and $V_{DD}$ = 5.5V                                  | •     |       |     | 300   | ns     |

| t <sub>SU:STA</sub>  | Start Condition Setup Time                                                       | $V_{DD} = 3V$ and $V_{DD} = 5.5V$                                                                        | •     | 4.7   |     |       | μs     |

| t <sub>HD:STA</sub>  | Start Condition Hold Time                                                        | $V_{DD} = 3V$ and $V_{DD} = 5.5V$                                                                        | •     | 4     |     |       | μs     |

| t <sub>HD:DAT</sub>  | SDA to SCL Falling-Edge Hold Time, Slave<br>Clocking in Data                     | $V_{DD} = 3V$ and $V_{DD} = 5.5V$                                                                        | •     | 300   |     |       | ns     |

| t <sub>timeout</sub> | Time Between Receiving Valid ChargingCurrent()<br>and ChargingVoltage() Commands | $V_{DD} = 3V$ and $V_{DD} = 5.5V$                                                                        | •     | 140   | 175 | 210   | sec    |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: See Test Circuit.

Note 3: Does not include tolerance of current sense resistor.

Note 4: The LTC4100E is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

Note 5: Current accuracy dependent upon circuit compensation and sense resistor.

Note 6:  $C_{TH}$  is defined as the sum of capacitance on THA, THB and SafetySignal.

Note 7: The corresponding overrange bit will be set when a HEX value greater than or equal to this value is used.

4100f

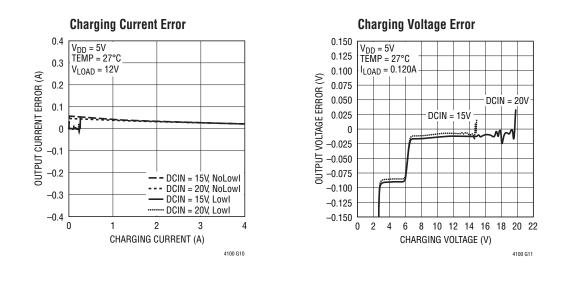

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

**TGATE (Pin 1):** Drives the Top External P-MOSFET of the Battery Charger Buck Converter.

**PGND (Pin 2):** High Current Ground Return for BGATE Driver.

**BGATE (Pin 3):** Drives the Bottom External N-MOSFET of the Battery Charger Buck Converter.

**INFET (Pin 4):** Drives the Gate of the External Input P-MOSFET.

**DCIN (Pin 5):** External DC Power Source Input. Bypass to ground with a  $0.1\mu$ F capacitor.

**CHGEN (Pin 6):** Digital Bidirectional Pin to Enable Charger Function. This pin is connected as a wired AND bus.

The following events will cause the POWER\_FAIL bit in the ChargerStatus register to become set:

1. An external device pulling the CHGEN signal to within 0.9V to GND;

2. The AC adapter voltage is not above the battery voltage.

**SMBALERT** (Pin 7): Active Low Interrupt Output to Host (referred to as the SMBALERT# signal in the SMBus Revision 1.1 specification). Signals host that there has been a

change of status in the charger registers and that the host should read the LTC4100 status registers to determine if any action on its part is required. This signal can be connected to the optional SMBALERT# line of the SMBus. Open drain with weak current source pull-up to  $V_{DD}$  (with Schottky to allow it to be pulled to 5V externally).

**SDA (Pin 8):** SMBus Data Signal from Main (host-controlled) SMBus. External pull-up resistor is required.

**SCL (Pin 9):** SMBus Clock Signal from Main (host-controlled) SMBus. External pull-up resistor is required.

**ACP (Pin 10):** This Output Indicates the Value of the DCDIV Comparator. It can be used to indicate whether AC is present or not.

**DCDIV (Pin 11):** Supply Divider Input. This is a high impedance comparator input with a 1.2V threshold (rising edge) and hysteresis.

GND (Pin 12): Ground for Digital and Analog Circuitry.

**I**<sub>LIM</sub> (**Pin 13**): An external resistor is connected between this pin and GND. The value of the external resistor programs the range and resolution of the programmed charger current. This is a digital, not an analog, function.

# PIN FUNCTIONS

$V_{LIM}$  (Pin 14): An external resistor is connected between this pin and GND. The value of the external resistor programs the range and resolution of the charging voltage. This is a digital, not an analog, function.

**THB (Pin 15):** SafetySignal Force/Sense Pin to Smart Battery. See description of operation for more detail. The maximum allowed combined capacitance on THA, THB and SafetySignal is 1nF (see Figure 4). A series resistor 54.9k needs to be connected between this pin and the battery's SafetySignal for this circuit to work correctly.

**THA (Pin 16):** SafetySignal Force/Sense Pin to Smart Battery. See description of operation for more detail. The maximum allowed combined capacitance on THA, THB and SafetySignal is 1nF (see Figure 4). A series resistor 1130 $\Omega$  needs to be connected between this pin and the battery's SafetySignal for this circuit to work correctly.

$V_{DD}$  (Pin 17): Power Supply Input for the LTC4100 Digital Circuitry. Bypass this pin with 0.1µF. Typically between 3.3V and 5V<sub>DC</sub>.

**V<sub>SET</sub> (Pin 18):** Tap Point of the Programmable Resistor Divider, which Provides Battery Voltage Feedback to the Charger.

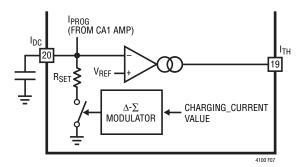

**I**<sub>TH</sub> (**Pin 19**): Control Signal of the Inner Loop of the Current Mode PWM. Higher I<sub>TH</sub> corresponds to higher charging current in normal operation. A  $0.0015\mu$ F capacitor to GND filters out PWM ripple. Typical full-scale output current is 40 $\mu$ A. Nominal voltage range for this pin is 0V to 3V.

IDC (Pin 20): Bypass to GND with a 0.068µF Capacitor.

**CSP (Pin 21):** Current Amplifier CA1 Input. This pin and the BAT pin measure the voltage across the sense resistor,  $R_{SENSE}$ , to provide the instantaneous current signals required for both peak and average current mode operation.

**BAT (Pin 22):** Battery Sense Input and the Negative Reference for the Current Sense Resistor. A bypass capacitor of at least  $10\mu$ F is required.

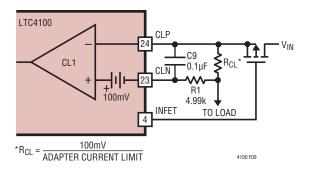

**CLN (Pin 23):** Negative Input to the Input Current Limiting Circuit Block. If no current limit function is desired, connect this pin to CLP. The threshold is set at 100mV below the voltage at the CLP pin. When used to limit supply current, a filter is needed to filter out the switching noise.

**CLP (Pin 24):** Positive Input to the Input Current Limiting Circuit Block. This pin also serves as a power supply for the IC.

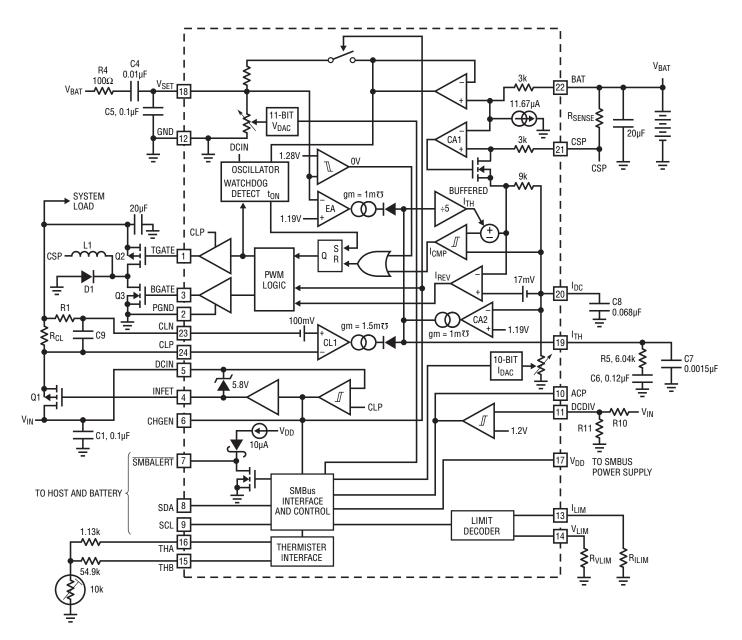

### **BLOCK DIAGRAM**

Figure 2

9

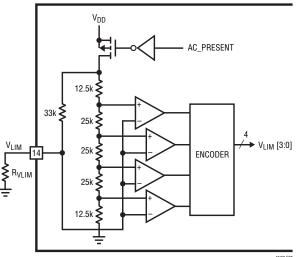

# TEST CIRCUIT

$$V_{TOL} = \frac{V_{BAT} - V_{VDAC}}{V_{VDAC}} \bullet 100$$

FOR V<sub>VDAC</sub> = 17.57V(0x44A0)

DCIN = 21V

CLN = CLP = 20V

# OPERATION

### Overview (Refer to Block Diagram)

The LTC4100 is composed of a battery charger section, a charger controller, a 10-bit DAC to control charger current, an 11-bit DAC to control charger voltage, a SafetySignal decoder, limit decoder and an SMBus controller block. If no battery is present, the SafetySignal decoder indicates a RES\_OR condition and charging is disabled by the charger controller (CHGEN = Low). Charging will also be disabled if DCDIV is low, or the SafetySignal is decoded as RES\_HOT. If a battery is inserted and AC power is connected, the battery will be charged with an 80mA "wake-up" current. The wake-up current is discontinued after t<sub>TIMEOUT</sub> if the SafetySignal is decoded as RES\_UR or RES\_COLD, and the battery or host doesn't transmit charging commands.

The SMBus interface and control block receives ChargingCurrent() and ChargingVoltage() commands via the SMBus. If ChargingCurrent() and ChargingVoltage() command pairs are received within a  $t_{TIMEOUT}$  interval, the values are stored in the current and voltage DACs and the charger controller asserts the CHGEN line if the decoded SafetySignal value will allow charging to commence. ChargingCurrent() and ChargingVoltage() values are compared against limits programmed by the limit decoder block; if the commands exceed the programmed limits these limits are substituted and overrange flags are set.

The charger controller will assert **SMBALERT** whenever a status change is detected, namely: AC\_PRESENT,

BATTERY\_PRESENT, ALARM\_INHIBITED, or V<sub>DD</sub> powerfail. The host may query the charger, via the SMBus, to obtain ChargerStatus() information. SMBALERT will be de-asserted upon a successful read of ChargerStatus() or a successful Alert Response Address (ARA) request.

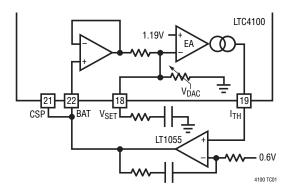

### Battery Charger Controller

The LTC4100 charger controller uses a constant off-time, current mode step-down architecture. During normal operation, the top MOSFET is turned on each cycle when the oscillator sets the SR latch and turned off when the main current comparator  $I_{CMP}$  resets the SR latch. While the top MOSFET is off, the bottom MOSFET is turned on until either the inductor current trips the current comparator  $I_{REV}$ , or the beginning of the next cycle. The oscillator uses the equation,

$$t_{\text{OFF}} = \frac{\left(V_{\text{DCIN}} - V_{\text{BAT}}\right)}{\left(V_{\text{DCIN}} \bullet f_{\text{OSC}}\right)}$$

to set the bottom MOSFET on-time. The result is quasiconstant frequency operation: the converter frequency remains nearly constant over a wide range of output voltages. This activity is diagrammed in Figure 3.

The peak inductor current, at which  $I_{CMP}$  resets the SR latch, is controlled by the voltage on  $I_{TH}$ .  $I_{TH}$  is in turn controlled by several loops, depending upon the situation at hand. The average current control loop converts the

voltage between CSP and BAT to a representative current. Error amp CA2 compares this current against the desired current programmed by the  $I_{DAC}$  at the  $I_{DC}$  pin and adjusts  $I_{TH}$  for the desired voltage across  $R_{SENSE}$ .

The voltage at BAT is divided down by an internal resistor divider set by the  $V_{DAC}$  and is used by error amp EA to decrease  $I_{TH}$  if the divider voltage is above the 1.19V reference.

The amplifier CL1 monitors and limits the input current, normally from the AC adapter, to a preset level (100mV/  $R_{CL}$ ). At input current limit, CL1 will decrease the  $I_{TH}$  voltage to reduce charging current.

An overvoltage comparator, OV, guards against transient overshoots (>7%). In this case, the top MOSFET is turned off until the overvoltage condition is cleared. This feature is useful for batteries that "load dump" themselves by opening their protection switch to perform functions such as calibration or pulse mode charging.

### **PWM Watchdog Timer**

There is a watchdog timer that observes the activity on the TGATE pin. If TGATE stops switching for more than  $40\mu$ s, the watchdog activates and turns off the top MOSFET for about 400ns. The watchdog engages to prevent very low frequency operation in dropout—a potential source of audible noise when using ceramic input and output capacitors.

### Charger Start-Up

When the charger is enabled, it will not begin switching until the  $I_{TH}$  voltage exceeds a threshold that assures initial current will be positive. This threshold is 5% to 15% of the maximum programmed current. After the charger begins switching, the various loops will control the current at a level that is higher or lower than the initial current. The duration of this transient condition depends upon the loop compensation, but is typically less than 1ms.

### **SMBus Interface**

All communications over the SMBus are interpreted by the SMBus interface block. The SMBus interface is a SMBus slave device at address 0x12. All internal LTC4100 registers may be updated and accessed through the SMBus interface, and charger controller as required. The SMBus protocol is a derivative of the I<sup>2</sup>C bus (Reference *I<sup>2</sup>C-Bus and How to Use It, V1.0* by Philips, and *System Management Bus Specification*, Version 1.1, from the SBS Implementers Forum, for a complete description of the bus protocol requirements).

All data is clocked into the shift register on the rising edge of SCL. All data is clocked out of the shift register on the falling edge of SCL. Detection of an SMBus Stop condition, or power-on reset via the  $V_{DD}$  power-fail, will reset the SMBus interface to an initial state at any time.

The LTC4100 command set is interpreted by the SMBus interface and passed onto the charger controller block as control signals or updates to internal registers.

Figure 3

\*http://www.SBS-FORUM.org

### Description of Supported Battery Charger Functions

The functions are described as follows (see Table 1 also):

### FunctionName() 'hnn (command code)

**Description:** A brief description of the function.

**Purpose:** The purpose of the function, and an example where appropriate.

• **SMBus Protocol:** Refer to Section 5 of the Smart Battery Charger specification for more details.

**Input, Output or Input/Output:** A description of the data supplied to or returned by the function.

### ChargerSpecInfo() ('h11)

**Description:** The SMBus Host uses this command to read the LTC4100's extended status bits.

**Purpose:** Allows the System Host to determine the specification revision the charger supports as well as other extended status information.

• SMBus Protocol: Read Word.

**Output:** The CHARGER\_SPEC indicates that the LTC4100 supports Version 1.1 of the Smart Battery Charger Specification. The SELECTOR\_SUPPORT indicates that the LTC4100 does not support the optional Smart Battery Selector Commands.

### ChargerMode() ('h12)

**Description:** The SMBus Host uses this command to set the various charger modes. The default values are set to allow a Smart Battery and the LTC4100 to work in concert without requiring an SMBus Host.

**Purpose:** Allows the SMBus Host to configure the charger and change the default modes. This is a write only function, but the value of the "mode" bit, INHIBIT\_CHARGE may be determined using the ChargerStatus() function.

• SMBus Protocol: Write Word.

**Input:** The INHIBIT\_CHARGE bit allows charging to be inhibited without changing the ChargingCurrent() and ChargingVoltage() values. The charging may be resumed by clearing this bit. This bit is automatically cleared when power is reapplied or when a battery is reinserted.

The ENABLE\_POLLING bit is not supported by the LTC4100. Values written to this bit are ignored.

The POR\_RESET bit sets the LTC4100 to its power-on default condition.

The RESET\_TO\_ZERO bit sets the ChargingCurrent()and ChargingVoltage() values to zero. This function ALWAYS clears the ChargingVoltage() and ChargingCurrent() values to zero even if the INHIBIT\_CHARGE bit is set.

### ChargerStatus() ('h13)

**Description:** The SMBus Host uses this command to read the LTC4100's status bits.

**Purpose:** Allows the SMBus Host to determine the status and level of the LTC4100.

### • SMBus Protocol: Read Word.

**Output:** The CHARGE\_INHIBITED bit reflects the status of the LTC4100 set by the INHIBIT\_CHARGE bit in the ChargerMode() function.

The POLLING\_ENABLED, VOLTAGE\_NOTREG, and CURRENT\_NOTREG are not supported by the LTC4100.

The LTC4100 always reports itself as a Level 2 Smart Battery Charger.

CURRENT\_OR bit is set only when ChargingCurrent() is set to a value outside the current regulation range of the LTC4100. This bit may be used in conjunction with the INHIBIT\_CHARGE bit of the ChargerMode() and ChargingCurrent() to determine the current capability of the LTC4100. When ChargingCurrent() is set to the  $I_{LIM}$  + 1, the CURRENT\_OR bit will be set.

VOLTAGE\_OR bit is set only when ChargingVoltage() is set to a value outside the voltage regulation range of the LTC4100. This bit may be used in conjunction with the INHIBIT\_CHARGE bit of the ChargerMode() and ChargingVoltage() to determine the voltage capability of the LTC4100. When ChargingVoltage() is set to the  $V_{LIM}$ , the VOLTAGE\_OR bit will be set.

The RES\_OR bit is set only when the SafetySignal resistance value is greater than  $95k\Omega$ . This indicates that the SafetySignal is to be considered as an open circuit.

| Function                  | Access       | SMBus<br>Address      | Command<br>Code | Data<br>Type        | D15                                                 | D14                    | D13            | D12             | D11                       | D10      | D9                       | D8                   | D7          | D6          | D5            | D4               | D3             | D2             | D1              | DO               |

|---------------------------|--------------|-----------------------|-----------------|---------------------|-----------------------------------------------------|------------------------|----------------|-----------------|---------------------------|----------|--------------------------|----------------------|-------------|-------------|---------------|------------------|----------------|----------------|-----------------|------------------|

| ChargerSpecInfo()         |              | 7'b0001_001<br>(0x12) | 8'h11           | Info                | Reserved CHARGER                                    |                        |                |                 |                           | ER_S     | PEC                      |                      |             |             |               |                  |                |                |                 |                  |

|                           | Read         |                       |                 | Return<br>Values    | 0                                                   | 0                      | 0              | 0               | 0                         | 0        | 0                        | 0                    | 0           | 0           | 0             | 0                | 0              | 0              | 1               | 0                |

| ChargerMode()             |              | 7'b0001_001           | 8'h12           | Control             |                                                     |                        |                |                 |                           | Rese     | erved                    |                      |             |             |               |                  | RESET_T0_ZER0  | POR_RESET      | ENABLE_POLLING  | INHIBIT_CHARGE   |

|                           | Write        |                       |                 | Permitted<br>Values |                                                     |                        |                |                 |                           | Igno     | red                      |                      |             |             |               |                  | 1/0            | 1/0            | lgn             | 1/0              |

| ChargerStatus()           |              | 7'b0001_001           | 8'h13           | Status              | AC_PRESENT                                          | BATTERY_PRESENT        | POWER_FAIL     | ALARM_INHIBITED | RES_UR                    | RES_HOT  | RES_COLD                 | RES_OR               | VOLTAGE_OR  | CURRENT_OR  |               | LEVEL:3/LEVEL:2  | CURRENT_NOTREG | VOLTAGE_NOTREG | POLLING_ENABLED | CHARGE_INHIBITED |

|                           | Read         |                       |                 | Return<br>Values    | 1/0                                                 | 1/0                    | 1/0            | 1/0             | 1/0                       | 1/0      | 1/0                      | 1/0                  | 1/0         | 1/0         | 0             | 1                | 0              | 0              | 0               | 1/0              |

| ChargingCurrent()         |              | 7'b0001_001           | 8'h14           | Value               |                                                     |                        |                |                 |                           | CH       | ARGII                    | NG_C                 | URRI        | ENT[1       | 5:0]          |                  |                |                |                 |                  |

|                           | Write        |                       |                 | Permitted<br>Values |                                                     |                        |                | ι               | Jnsigi                    | ned ir   | iteger                   | r repr               | esent       | ing cı      | urrent        | t in m           | A              |                |                 |                  |

| ChargingVoltage()         |              | 7'b0001_001           | 8'h15           | Value               |                                                     |                        |                |                 |                           | СН       | ARGI                     | NG_\                 | /OLTA       | AGE[1       | 5:0]          |                  |                |                |                 |                  |

|                           | Write        |                       |                 | Permitted<br>Values |                                                     |                        |                |                 | Unsig                     | ned i    | ntege                    | r rep                | resen       | ting v      | oltag         | e in n           | ۱V             |                |                 |                  |

| AlarmWarning()            |              | 7'b0001_001           | 8'h16           | Control             | OVER_CHARGED_ALARM                                  | TERMINATE_CHARGE_ALARM | RESERVED_ALARM | OVER_TEMP_ALARM | TERMINATE_DISCHARGE_ALARM | Reserved | REMAINING_CAPACITY_ALARM | REMAINING_TIME_ALARM | INITIALIZED | DISCHARGING | FULLY_CHARGED | FULLY DISCHARGED |                | ERROR          |                 |                  |

|                           | Write        |                       |                 | Permitted<br>Values | 1/0                                                 | 1/0                    | 1/0            | 1/0             |                           |          |                          |                      | I           | gnore       | d             |                  |                |                |                 |                  |

| LTCO()                    |              | 7'b0001_001           | 8'h3C           | Register            | Reserved B<br>g<br>LTC4100's Version Identification |                        |                |                 |                           |          |                          |                      |             |             |               |                  |                |                |                 |                  |

|                           | Write        | 1                     |                 | Permitted<br>Values | l                                                   | gnore                  | d              | 1/0             |                           |          |                          |                      | lg          | inorec      | 4             |                  |                |                |                 |                  |

|                           | Read         |                       |                 | Return<br>Values    | 0                                                   | 0                      | 0              | 1/0             | 0                         | 0        | 1                        | 0                    | 0           | 0           | 0             | 0                | 0              | 0              | 1               | 0                |

| Alert Response<br>Address |              | 7'b0001_100<br>(0x18) | N/A             | Status              | LTC4100's Address                                   |                        |                |                 |                           |          | Undefined                |                      |             |             |               |                  |                |                |                 |                  |

|                           | Read<br>Byte |                       |                 | Return<br>Values    |                                                     |                        |                |                 |                           |          |                          |                      | 0           | 0           | 0             | 1                | 0              | 0              | 1               | x                |

The RES\_COLD bit is set only when the SafetySignal resistance value is greater than  $28.5k\Omega$ . The SafetySignal indicates a cold battery. The RES\_COLD bit will be set whenever the RES\_OR bit is set.

The RES\_HOT bit is set only when the SafetySignal resistance is less than  $3150\Omega$ , which indicates a hot battery. The RES\_HOT bit will be set whenever the RES\_UR bit is set.

The RES\_UR bit is set only when the SafetySignal resistance value is less than  $575\Omega$ .

ALARM\_INHIBITED bit is set if a valid AlarmWarning() message has been received and charging is inhibited as a result. This bit is cleared if both ChargingVoltage() and ChargingCurrent() are rewritten to the LTC4100, power is removed (DCDIV <  $V_{ACP}$ ), or if a battery is removed. The setting of the ALARM\_INHIBITED will activate the LTC4100 SMBALERT pull-down.

POWER\_FAIL bit is set if the LTC4100 does not have sufficient DCIN voltage to charge the battery or if an external device is pulling the CHGEN input signal low. Charging is disabled whenever this bit is set. The setting of this bit does not clear the values in the ChargingVoltage() and ChargingCurrent() function values, nor does it necessarily affect the charging modes of the LTC4100.

BATTERY\_PRESENT is set if a battery is present otherwise it is cleared. The LTC4100 uses the SafetySignal in order to determine battery presence. If the LTC4100 detects a RES\_OR condition, the BATTERY\_PRESENT bit is cleared immediately. The LTC4100 will not set the BATTERY\_PRESENT bit until it successfully samples the SafetySignal twice and does not detect a RES\_OR condition on either sampling. If AC is not present (e.g. DCDIV <  $V_{ACP}$ ), this bit may not be set for up to one-half second after the battery is connected to the SafetySignal. The ChargingCurrent() and ChargingVoltage() function values are immediately cleared whenever this bit is cleared. Charging will never be allowed if this bit is cleared. A change in BATTERY\_PRESENT will activate the LTC4100 SMBALERT pull-down.

AC\_PRESENT is set if the voltage on DCDIV is greater than  $V_{ACP}$ . This does not necessarily indicate that the voltage on DCIN is sufficient to charge the battery. A change in AC\_PRESENT will activate the LTC4100 SMBALERT pull-down.

### ChargingCurrent() ('h14)

**Description:** The Battery, System Host or other master device sends the desired charging current (mA) to the LTC4100.

**Purpose:** The LTC4100 uses  $R_{ILIM}$ , the granularity of the  $I_{DAC}$ , and the value of the ChargingCurrent() function to determine its charging current supplied to the battery. The charging current will never exceed the maximum current permitted by  $R_{ILIM}$ . The ChargingCurrent() value will be truncated to the granularity of the  $I_{DAC}$ . The charging current will also be reduced if the battery voltage exceeds the programmed charging voltage.

• SMBus Protocol: Write Word.

**Input:** The CHARGING\_CURRENT is an unsigned 16 bit integer specifying the requested charging current in mA. The following table defines the maximum permissible value of CHARGING\_CURRENT that will not set the CURRENT\_OR in the ChargerStatus() function for a given value of the R<sub>ILIM</sub>:

| R <sub>ILIM</sub>                   | ChargingCurrent()     | Current            |  |  |  |

|-------------------------------------|-----------------------|--------------------|--|--|--|

| Short to GND                        | 0x0000 through 0x03FF | 0mA through 1023mA |  |  |  |

| 10kΩ ±1%                            | 0x0000 through 0x07FF | 0mA through 2047mA |  |  |  |

| 33kΩ ±1%                            | 0x0000 through 0x0BFF | 0mA through 3071mA |  |  |  |

| Open (or Short to V <sub>DD</sub> ) | 0x0000 through 0x0FFF | 0mA through 4095mA |  |  |  |

### ChargingVoltage() ('h15)

**Description:** The Battery, SMBus Host or other master device sends the desired charging voltage (mV) to the LTC4100.

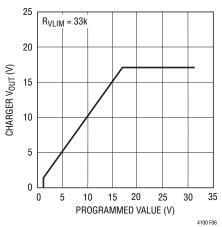

**Purpose:** The LTC4100 uses  $R_{VLIM}$ , the granularity of the  $V_{DAC}$ , and the value of the ChargingVoltage() function to determine its charging voltage supplied to the battery. The charging voltage will never be forced beyond the voltage permitted by  $R_{VLIM}$ . The ChargingVoltage() value will be truncated to the granularity of the  $V_{DAC}$ . The charging voltage will also be reduced if the battery current exceeds the programmed charging current.

• SMBus Protocol: Write Word.

Input: The CHARGING\_VOLTAGE is an unsigned 16-bit integer specifying the requested charging voltage in mV.

The LTC4100 considers any value from 0x0001 through 0x049F the same as writing 0x0000. The following table defines the maximum permissible value of CHARGING\_VOLTAGE that will not set the VOLTAGE\_OR in the ChargerStatus() function for a given value of R<sub>VLIM</sub>:

| R <sub>VLIM</sub>                   | Maximum ChargingVoltage() |

|-------------------------------------|---------------------------|

| Short to GND                        | 0x225F (8796mV)           |

| 10kΩ ±1%                            | 0x332F (13100mV)          |

| 33kΩ ±1%                            | 0x43FF (17404mV)          |

| 100kΩ ±1%                           | 0x54CF (21708mV)          |

| Open (or Short to V <sub>DD</sub> ) | 0x6D5F (27996mV)          |

### AlarmWarning() ('h16)

**Description:** The Smart Battery, acting as a bus master device, sends the AlarmWarning() message to the LTC4100 to notify it that one or more alarm conditions exist. Alarm indications are encoded as bit fields in the Battery's Status register, which is then sent to the LTC4100 by this function.

**Purpose:** The LTC4100 will use the information sent by this function to properly charge the battery. The LTC4100 will only respond to certain alarm bits. Writing to this function does not necessarily cause an alarm condition that inhibits battery charging.

### • SMBus Protocol: Write Word.

**Input:** Only the OVER\_CHARGED\_ALARM, TERMINATE \_CHARGE\_ALARM, reserved (0x2000), and OVER \_TEMP\_ALARM bits are supported by the LTC4100. Writing a one to any of these specified bits will inhibit the charging by the LTC4100 and will set the ALARM\_ INHIBITED bit in the ChargerStatus() function. The TERMINATE\_DISCHARGE\_ALARM, REMAINING\_ CAPACITY\_ALARM, REMAINING\_TIME\_ALARM, and the ERROR bits are ignored by the LTC4100.

### LTCO() ('h3C)

**Description:** The SMBus Host uses this command to determine the version number of the LTC4100 and set extended operation modes not defined by the Smart Battery Charger Specification.

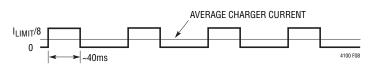

**Purpose:** This function allows the SMBus Host to determine if the battery charger is an LTC4100. Identifying the manufacturer and version of the Smart Battery Charger permits software to perform tasks specific to a given charger. The LTC4100 also provides a means of disabling the LOWI current mode of the I<sub>DAC</sub>.

### • SMBus Protocol: Write Word.

**Input:** The NO\_LOWI is the only bit recognized by this function. The default value of NO\_LOWI is zero. The LTC4100 LOWI current mode provides a more accurate average charge current when the charge current is less than 1/16 of the full scale  $I_{DAC}$  value. When the NO\_LOWI is set, a less accurate  $I_{DAC}$  algorithm is used to generate the charging current, but because the charger is not pulsed on and off, it may be preferred.

### • SMBus Protocol: Read Word.

**Output:** The NO\_LOWI indicates the  $I_{DAC}$  mode of operation. If clear, then the LOWI current mode will be used when the charging current is less than 1/16 of the full-scale  $I_{DAC}$  value.

The LTC Version Identification will always be 0x202 for the LTC4100.

### Alert Response Address (ARA)

**Description:** The SMBus system host uses the Alert Response Address to quickly identify the generator of an SMBALERT# event.

**Purpose:** The LTC4100 will respond to an ARA address 0x18 if the SMBALERT signal is actively pulling down the SMBALERT# bus. The LTC4100 will follow the prioritization reporting as defined in the System Management Bus Specification, Version 1.1, from the SBS Implementers Forum.

# • **SMBus Protocol:** A 7-bit Addressable Device Responds to an ARA.

**Output:** The Device Address will be sent to the SMBus system host. The LTC4100 Device address is 0x12.

The following events will cause the LTC4100 to pull-down the SMBALERT# bus through the SMBALERT pin:

• Change of AC\_PRESENT in the ChargerStatus() function.

- Change of BATTERY\_PRESENT in the ChargerStatus() function.

- Setting ALARM\_INHIBITED in the ChargerStatus() function.

- Internal power-on reset condition.

### SMBus Accelerator Pull-Ups

Both SCL and SDA have SMBus accelerator circuits which reduce the rise time on systems with significant capacitance on the two SMBus signals. The dynamic pull-up circuitry detects a rising edge on SDA or SCL and applies 1mA to 10mA pull-up to V<sub>DD</sub> when V<sub>IN</sub> > 0.8V until V<sub>IN</sub> < V<sub>DD</sub> – 0.8V (external pull-up resistors are still required to supply DC current). This action allows the bus to meet SMBus rise time requirements with as much as 250pF on each SMBus signal. The improved rise time will benefit all of the devices which use the SMBus, especially those devices that use the l<sup>2</sup>C logic levels. Note that the dynamic pull-up circuits only pull to V<sub>DD</sub>, so some SMBus devices that are not compliant to the SMBus specifications may still have rise time compliance problems if the SMBus pull-up resistors are terminated with voltages higher than V<sub>DD</sub>.

### The Control Block

The LTC4100 charger operations are handled by the control block. This block is capable of charging the selected battery autonomously or under SMBus Host control. The control block can request communications with the system management host (SMBus Host) by asserting SMBALERT = 0; this will cause the SMBus Host, if present, to poll the LTC4100.

The control block receives SMBus slave commands from the SMBus interface block.

The control block allows the LTC4100 to meet the following Smart Battery-controlled (Level 2) charger requirements:

- 1. Implements the Smart Battery's critical warning messages over the SMBus.

- 2. Operates as an SMBus slave device that responds to ChargingVoltage() and ChargingCurrent() commands and adjusts the charger output parameters accordingly.

- 3. The host may control charging by disabling the Smart Battery's ability to transmit ChargingCurrent() and

ChargingVoltage() request functions and broadcasting the charging commands to the LTC4100 over the SMBus.

4. The LTC4100 will still respond to Smart Battery critical warning messages without host intervention.

### Wake-Up Charging Mode

The following conditions must be met in order to allow wake-up charging of the battery:

- 1. The SafetySignal must be RES\_COLD, RES\_IDEAL, or RES\_UR.

- 2. AC must be present. This is qualified by DCDIV >  $V_{ACP}$ .

Wake-up charging initiates when a newly inserted battery does not send ChargingCurrent() and ChargingVoltage() functions to the LTC4100.

The following conditions will terminate the wake-up charging mode.

- 1. A T<sub>TIMEOUT</sub> period is reached when the SafetySignal is RES\_COLD or RES\_UR.

- 2. The SafetySignal is registering RES\_OR.

- 3. The successful writing of the ChargingCurrent() AND ChargingVoltage() function. The LTC4100 will proceed to the controlled charging mode after these two functions are written.

- 4. The SafetySignal is registering RES\_HOT.

- 5. The AC power is no longer present. (DCDIV <  $V_{ACP}$ )

- 6. The ALARM\_INHIBITED becomes set in the Charger-Status() function.

- 7. The INHIBIT\_CHARGE is set in the ChargerMode() function.

- The CHGEN pin is pulled low by an external device. The LTC4100 will resume wake-up charging, if the CHGEN pin is released by the external device. Toggling the CHGEN pin will not reset the T<sub>TIMEOUT</sub> timer.

- There is insufficient DCIN voltage to charge the battery. The LTC4100 will resume wake-up charging when there is sufficient DCIN voltage to charge the battery. This condition will not reset the T<sub>TIMEOUT</sub> timer.

### **Controlled Charging Algorithm Overview**

The following conditions must be met in order to allow controlled charging to start on the LTC4100:

- 1. The ChargingVoltage() AND ChargingCurrent() function must be written to non-zero values.

- 2. The SafetySignal must be RES\_COLD, RES\_IDEAL, or RES\_UR.

- 3. AC must be present. This is qualified by DCDIV >  $V_{ACP}$ .

The following conditions will stop the controlled charging algorithm and will cause the battery charger controller to stop charging:

- 1. The ChargingCurrent() AND ChargingVoltage() functions have not been written for  $T_{TIMEOUT}$ .

- 2. The SafetySignal is registering RES\_OR.

- 3. The SafetySignal is registering RES\_HOT.

- 4. The AC power is no longer present. (DCDIV  $< V_{ACP}$ )

- 5. ALARM\_INHIBITED is set in the ChargerStatus() function.

- 6. INHIBIT\_CHARGE is set in the ChargerMode() function. Clearing INHIBIT\_CHARGE will cause the LTC4100 to resume charging using the previous

ChargingVoltage() AND ChargingCurrent() function values.

- 7. RESET\_TO\_ZERO is set in the ChargerMode() function.

- 8. CHGEN pin is pulled low by an external device. The LTC4100 will resume charging using the previous ChargingVoltage() AND ChargingCurrent() function values, if the CHGEN pin is released by the external device.

- 9. Insufficient DCIN voltage to charge the battery. The LTC4100 will resume charging using the previous ChargingVoltage() AND ChargingCurrent() function values, when there is sufficient DCIN voltage to charge the battery.

- 10. Writing a zero value to ChargingVoltage() function.

- 11. Writing a zero value to ChargingCurrent() function.

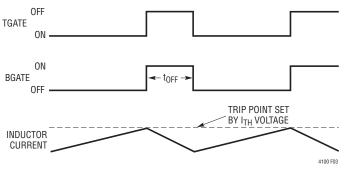

### The SafetySignal Decoder Block

This block measures the resistance of the SafetySignal and features high noise immunity at critical trip points. The low power standby mode supports only battery presence SMB charger reporting requirements when AC is not present. The SafetySignal decoder is shown in Figure 4. The value of  $R_{THA}$  is 1.13k and  $R_{THB}$  is 54.9k.

Figure 4. SafetySignal Decoder Block

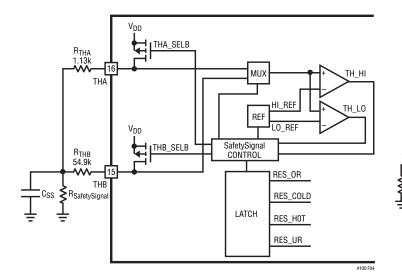

Figure 5. Simplified  $V_{LIM}$  Circuit Concept (I<sub>LIM</sub> is Similar)

SafetySignal sensing is accomplished by a state machine that reconfigures the switches of Figure 4 using THA\_SELB and THB\_SELB, a selectable reference generator, and two comparators. This circuit has two modes of operation based upon whether AC is present.

When AC is present, the LTC4100 samples the value of the SafetySignal and updates the ChargerStatus register approximately every 32ms. The state machine successively samples the SafetySignal value starting with the RES OR  $\geq$  RES COLD threshold, then RES COLD  $\geq$  RES IDEAL threshold, RES IDEAL  $\geq$  RES HOT threshold, and finally the RES HOT  $\geq$  RES UR threshold. Once the SafetySignal range is determined, the lower value thresholds are not sampled. The SafetySignal decoder block uses the previously determined SafetySignal value to provide the appropriate adjustment in threshold to add hysteresis. The R<sub>THB</sub> resistor value is used to measure the RES\_OR  $\geq$  RES\_COLD and RES\_COLD  $\geq$  RES\_IDEAL thresholds by connecting the THB pin to  $V_{DD}$  and measuring the voltage resultant on the THA pin. The R<sub>THA</sub> resistor value is used to measure the RES\_IDEAL  $\geq$  RES\_HOT and RES\_HOT  $\geq$ RES UR thresholds by connecting the THA pin to  $V_{DD}$  and measuring the voltage resultant on the THB pin.

The SafetySignal decoder block uses a voltage divider network between  $V_{DD}$  and GND to determine SafetySignal range thresholds. Since the THA and THB inputs are sequentially connected to  $V_{DD}$ , this provides  $V_{DD}$  noise immunity during SafetySignal measurement.

When AC power is not available the SafetySignal block supports the following low power operating features:

- 1. The SafetySignal is sampled every 250ms or less, instead of 32ms.

- 2. A full SafetySignal status is sampled every 30s or less, instead of every 32ms.

The SafetySignal impedance is interpreted according to Table 4.

Table 4. SafetySignal State Ranges

|                               | 5 5                                  |             |  |  |

|-------------------------------|--------------------------------------|-------------|--|--|

| SafetySignal<br>RESISTANCE    | CHARGE STATUS BITS                   | DESCRIPTION |  |  |

| 0Ω to 500Ω                    | RES_UR<br>RES_HOT<br>BATTERY_PRESENT | Underrange  |  |  |

| 500 $\Omega$ to 3k $\Omega$   | RES_HOT<br>BATTERY_PRESENT           | Hot         |  |  |

| 3kΩ to 30kΩ                   | BATTERY_PRESENT                      | Ideal       |  |  |

| 30k $\Omega$ to 100k $\Omega$ | RES_COLD<br>BATTERY_PRESENT          | Cold        |  |  |

| Above 100k $\Omega$           | RES_OR RES_COLD                      | Overrange   |  |  |

|                               |                                      |             |  |  |

**Note:** The underrange detection scheme is a very important feature of the LTC4100. The  $R_{THA}/R_{SafetySignal}$  divider trip point of 0.333 •  $V_{DD}$  (1V) is well above the 0.047 •  $V_{DD}$  (140mV) threshold of a system using a 10k pull-up. A system using a 10k pull-up would not be able to resolve the important underrange to hot transition point with a modest 100mV of ground offset between battery and SafetySignal detection circuitry. Such offsets are anticipated when charging at normal current levels.

The required values for  $R_{THA}$  and  $R_{THB}$  are shown in Table 5.

#### Table 5. SafetySignal External Resistor Values

| EXTERNAL RESISTOR | VALUE (Ω) |

|-------------------|-----------|

| R <sub>THA</sub>  | 1130 ±1%  |

| R <sub>THB</sub>  | 54.9k ±1% |

$C_{SS}$  represents the capacitance between the SafetySignal and GND.  $C_{SS}$  may be added to provide additional noise immunity from transients in the application.  $C_{SS}$  cannot exceed 1nF if the LTC4100 is to properly sense the value of  $R_{SafetySignal}$ .

### The I<sub>LIM</sub> Decoder Block

The value of an external resistor connected from this pin to GND determines one of four current limits that are used for maximum charging current value. These limits provide a measure of safety with a hardware restriction on charging current which cannot be overridden by software.

| EXTERNAL<br>RESISTOR<br>(R <sub>ILIM</sub> )  | I <sub>LIM</sub> VOLTAGE                                           | CONTROLLED<br>Charging<br>Current Range | GRANULARITY |

|-----------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|-------------|

| Short to GND                                  | $V_{ILIM} < 0.09V_{DD}$                                            | 0 < l < 1023mA                          | 1mA         |

| 10k ±1%                                       | 0.17V <sub>VDD</sub> <<br>V <sub>ILIM</sub> < 0.34V <sub>VDD</sub> | 0 < I < 2046mA                          | 2mA         |

| 33k ±1%                                       | 0.42V <sub>VDD</sub> <<br>V <sub>ILIM</sub> < 0.59V                | 0 < I < 3068mA                          | 4mA         |

| Open (>250k,<br>or Short to V <sub>DD</sub> ) | 0.66V <sub>VDD</sub> <<br>V <sub>ILIM</sub>                        | 0 < I < 4092mA                          | 4mA         |

### Table 6. I<sub>LIM</sub> Trip Points and Ranges

### The V<sub>LIM</sub> Decoder Block

The value of an external resistor connected from this pin to GND determines one of five voltage limits that are applied to the charger output value. These limits provide a measure of safety with a hardware restriction on charging voltage which cannot be overridden by software.

| iable 7. vlim ilip rullis allu nallyes (see rigule 5) |                                                                          |                                                             |             |  |

|-------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------|-------------|--|