Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## -48V Hot Swap Controller with Sequencer

### **FEATURES**

- Allows Safe Board Insertion and Removal from a Live –48V Backplane

- Floating Topology Permits Very High Voltage Operation

- Adjustable Analog Current Limit with Breaker Timer Ideal for Two Battery Feeds

- Fast Response Time Limits Peak Fault Current

- Three Sequenced Power Good Outputs

- Improved Ruggedness Shunt Regulator

- Adjustable Soft-Start Current Limit

- Adjustable Timer with Drain Voltage Accelerated Response

- Latchoff After Fault

- Available in a 16-Pin SSOP Package

### **APPLICATIONS**

- -48V Distributed Power Systems

- Negative Power Supply Control

- Central Office Switching

- High Availability Servers

- Disk Arrays

∠7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## DESCRIPTION

The LTC®4253B negative voltage Hot Swap™ controller allows a board to be safely inserted and removed from a live backplane. Output current is controlled by three stages of current-limiting: a timed circuit breaker, active current limiting and a fast feedforward path that limits peak current under worst-case catastrophic fault conditions. The LTC4253B latches off after a circuit fault.

Adjustable undervoltage and overvoltage detectors disconnect the load whenever the input supply exceeds the desired operating range. The LTC4253B's supply input is shunt-regulated, allowing safe operation with very high supply voltages. A multifunction timer delays initial start-up and controls the circuit breaker's response time. The circuit breaker's response time can be accelerated by sensing excessive MOSFET drain voltage, keeping the MOSFET within its safe operating area (SOA). An adjustable soft-start circuit controls MOSFET inrush current at start-up.

Three power good outputs are sequenced by an adjustable timer and two ENABLE inputs to enable external power modules at start-up or disable them if the circuit breaker trips. The LTC4253B improves the ruggedness of the LTC4253 shunt regulator.

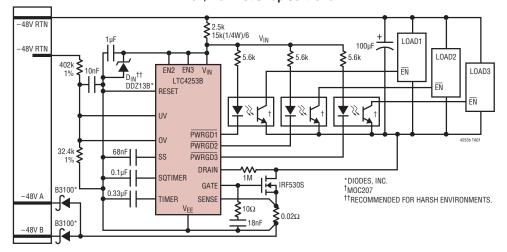

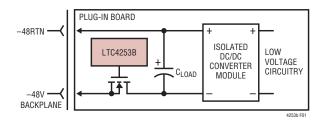

## TYPICAL APPLICATION

-48V/2.5A Hot Swap Controller

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1), All voltages referred to VEE

| Current into V <sub>IN</sub> (100µs Pulse) | 100mA          |

|--------------------------------------------|----------------|

| Current into DRAIN (100µs Pulse)           | 20mA           |

| V <sub>IN</sub> , DRAIN Minimum Voltage    | 0.3V           |

| Input/Output (Except SENSE                 |                |

| and DRAIN) Voltage                         | –0.3V to 16V   |

| SENSE Voltage                              | –0.6V to 16V   |

| Current Out of SENSE (20µs Pulse)          | –200mA         |

| Maximum Junction Temperature               | 125°C          |

| Operating Temperature Range                |                |

| LTC4253BC                                  | 0°C to 70°C    |

| LTC4253BI                                  | 40°C to 85°C   |

| Storage Temperature Range                  | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)       | 300°C          |

|                                            |                |

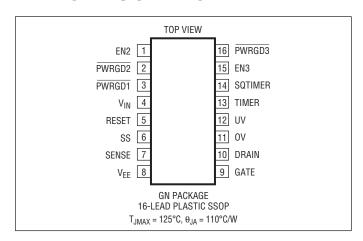

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|------------------|-------------------|---------------|----------------------|-------------------|

| LTC4253BCGN#PBF  | LTC4253BCGN#TRPBF | 4253B         | 16-Lead Plastic SSOP | 0°C to 70°C       |

| LTC4253BIGN#PBF  | LTC4253BIGN#TRPBF | 4253B         | 16-Lead Plastic SSOP | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . (Note 2)

| SYMBOL                            | PARAMETER                                                 | CONDITIONS                                                                                                                                                                                  |   | MIN   | TYP         | MAX        | UNITS    |

|-----------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-------------|------------|----------|

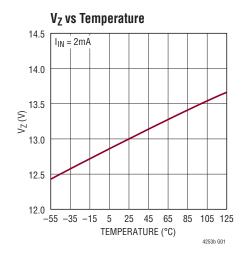

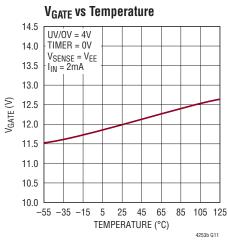

| $V_Z$                             | V <sub>IN</sub> – V <sub>EE</sub> Zener Voltage           | I <sub>IN</sub> = 2mA                                                                                                                                                                       | • | 11.5  | 13          | 14.5       | V        |

| $R_Z$                             | V <sub>IN</sub> – V <sub>EE</sub> Zener Dynamic Impedance | I <sub>IN</sub> = (2mA to 30mA)                                                                                                                                                             |   |       | 5           |            | Ω        |

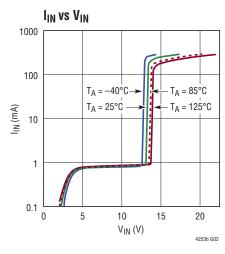

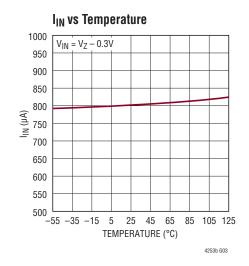

| I <sub>IN</sub>                   | V <sub>IN</sub> Supply Current                            | $UV = OV = 4V, V_{IN} = (V_Z - 0.3V)$                                                                                                                                                       | • |       | 0.8         | 2          | mA       |

| $V_{LKO}$                         | V <sub>IN</sub> Undervoltage Lockout                      | Coming Out of UVLO (Rising V <sub>IN</sub> )                                                                                                                                                | • |       | 9.2         | 11.5       | V        |

| $V_{LKH}$                         | V <sub>IN</sub> Undervoltage Lockout Hysteresis           |                                                                                                                                                                                             | • | 0.5   | 1           | 1.5        | V        |

| $V_{IH}$                          | TTL Input High Voltage                                    |                                                                                                                                                                                             | • | 2     |             |            | V        |

| $V_{IL}$                          | TTL Input Low Voltage                                     |                                                                                                                                                                                             | • |       |             | 0.8        | V        |

| V <sub>HYST</sub>                 | TTL Input Buffer Hysteresis                               |                                                                                                                                                                                             |   |       | 600         |            | mV       |

| I <sub>RESET</sub>                | RESET Input Current                                       | V <sub>EE</sub> ≤ V <sub>RESET</sub> ≤ V <sub>IN</sub>                                                                                                                                      | • |       | ±0.1        | ±10        | μА       |

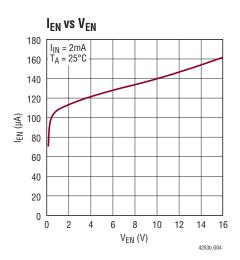

| I <sub>EN</sub>                   | EN2, EN3 Input Current                                    | V <sub>EN</sub> = 4V<br>V <sub>EN</sub> = 0V                                                                                                                                                | • | 60    | 120<br>±0.1 | 180<br>±10 | μA<br>μA |

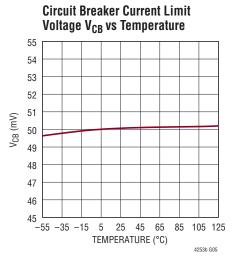

| $\overline{V_{CB}}$               | Circuit Breaker Current Limit Voltage                     | V <sub>CB</sub> = (V <sub>SENSE</sub> - V <sub>EE</sub> )                                                                                                                                   | • | 40    | 50          | 60         | mV       |

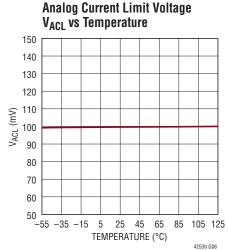

| V <sub>ACL</sub>                  | Analog Current Limit Voltage                              | $V_{ACL} = (V_{SENSE} - V_{EE})$ , SS = Open or 2.2V                                                                                                                                        | • | 80    | 100         | 120        | mV       |

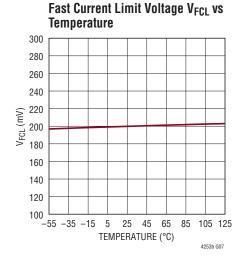

| V <sub>FCL</sub>                  | Fast Current Limit Voltage                                | $V_{FCL} = (V_{SENSE} - V_{EE})$                                                                                                                                                            | • | 150   | 200         | 300        | mV       |

| $V_{SS}$                          | SS Voltage                                                | After End of SS Timing Cycle                                                                                                                                                                | • | 2     | 2.2         | 2.4        | V        |

| I <sub>SS</sub>                   | SS Pin Current                                            | UV = OV = 4V, V <sub>SENSE</sub> = V <sub>EE</sub> ,<br>V <sub>SS</sub> = OV (Sourcing)                                                                                                     | • | 12    | 22          | 32         | μА       |

|                                   |                                                           | $UV = 0V = 0V$ , $V_{SENSE} = V_{EE}$ , $V_{SS} = 1V$ (Sinking)                                                                                                                             |   |       | 28          |            | mA       |

| R <sub>SS</sub>                   | SS Output Impedance                                       |                                                                                                                                                                                             |   |       | 100         |            | kΩ       |

| $V_{0S}$                          | Analog Current Limit Offset Voltage                       |                                                                                                                                                                                             |   |       | 10          |            | mV       |

| $\frac{V_{ACL} + V_{OS}}{V_{SS}}$ | Ratio (V <sub>ACL</sub> + V <sub>OS</sub> ) to SS Voltage |                                                                                                                                                                                             |   |       | 0.05        |            | V/V      |

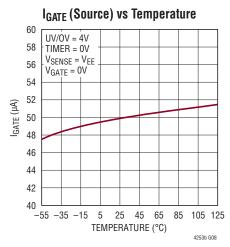

| I <sub>GATE</sub>                 | GATE Pin Output Current                                   | UV = 0V = 4V, V <sub>SENSE</sub> = V <sub>EE</sub> ,<br>V <sub>GATE</sub> = 0V (Sourcing)                                                                                                   | • | 30    | 50          | 70         | μА       |

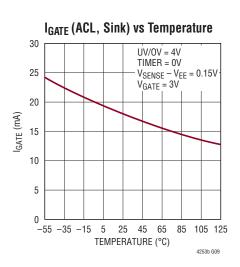

|                                   |                                                           | $UV = 0V = 4V, V_{SENSE} - V_{EE} = 0.15V,$ $V_{GATE} = 3V \text{ (Sinking)}$                                                                                                               |   |       | 17          |            | mA       |

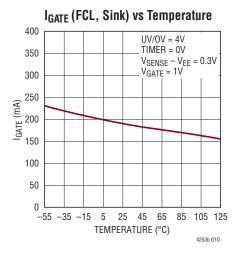

|                                   |                                                           | $\begin{aligned} \text{UV} &= \text{OV} = \text{4V},  \text{V}_{\text{SENSE}} - \text{V}_{\text{EE}} = 0.3\text{V}, \\ \text{V}_{\text{GATE}} &= \text{1V}  \text{(Sinking)} \end{aligned}$ |   |       | 190         |            | mA       |

| $V_{GATE}$                        | External MOSFET Gate Drive                                | V <sub>GATE</sub> – V <sub>EE</sub> , I <sub>IN</sub> = 2mA                                                                                                                                 | • | 10    | 12          | $V_{Z}$    | V        |

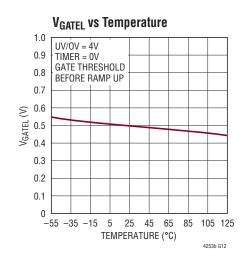

| $V_{GATEL}$                       | Gate Low Threshold                                        | Before Gate Ramp Up                                                                                                                                                                         |   |       | 0.5         |            | V        |

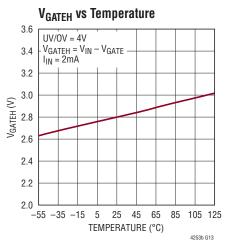

| $V_{GATEH}$                       | Gate High Threshold                                       | $V_{GATEH} = V_{IN} - V_{GATE}$ , for $\overline{PWRGD1}$ , $\overline{PWRGD2}$ , $\overline{PWRGD2}$ Status                                                                                |   |       | 2.8         |            | V        |

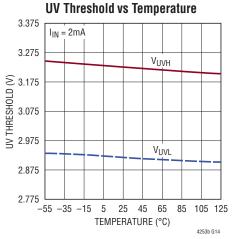

| $V_{UVHI}$                        | UV Pin Threshold HIGH                                     | UV Low to High                                                                                                                                                                              | • | 3.075 | 3.225       | 3.375      | V        |

| $V_{\text{UVLO}}$                 | UV Pin Threshold LOW                                      | UV High to Low                                                                                                                                                                              | • | 2.775 | 2.925       | 3.075      | V        |

| V <sub>UVHST</sub>                | UV Pin Hysteresis                                         |                                                                                                                                                                                             |   | 230   | 300         | 350        | mV       |

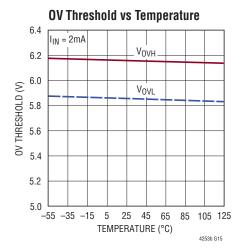

| V <sub>OVHI</sub>                 | OV Pin Threshold HIGH                                     | OV Low to High                                                                                                                                                                              | • | 5.85  | 6.15        | 6.45       | V        |

| V <sub>OVLO</sub>                 | OV Pin Threshold LOW                                      | OV High to Low                                                                                                                                                                              | • | 5.55  | 5.85        | 6.15       | V        |

| V <sub>OVHST</sub>                | OV Pin Hysteresis                                         |                                                                                                                                                                                             |   | 230   | 300         | 350        | mV       |

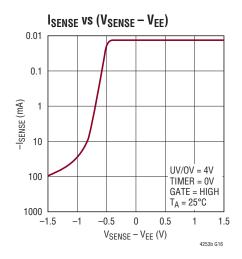

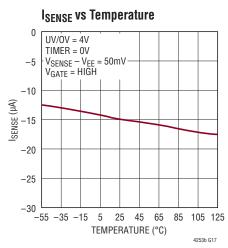

| I <sub>SENSE</sub>                | SENSE Pin Input Current                                   | UV = 0V = 4V, V <sub>SENSE</sub> = 50mV (Sourcing)                                                                                                                                          | • |       | 15          | 30         | μА       |

| I <sub>INP</sub>                  | UV, OV Pin Input Current                                  | UV = 0V = 4V                                                                                                                                                                                | • |       | ±0.1        | ±1         | μА       |

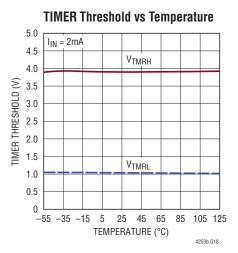

| $V_{TMRH}$                        | TIMER Pin Voltage High Threshold                          |                                                                                                                                                                                             | • | 3.5   | 4           | 4.5        | V        |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ .

| SYMBOL                                     | PARAMETER TIMER Pin Voltage Low Threshold                                                                        | CONDITIONS                                                                           |   | MIN | TYP  | MAX        | UNITS    |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---|-----|------|------------|----------|

| $V_{TMRL}$                                 |                                                                                                                  |                                                                                      | • | 0.8 | 1    | 1.2        | V        |

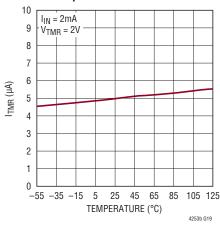

| I <sub>TMR</sub>                           | TIMER Pin Current                                                                                                | Timer On (Initial Cycle/Latchoff,<br>Sourcing), V <sub>TMR</sub> = 2V                | • | 3   | 5    | 7          | μА       |

|                                            |                                                                                                                  | Timer Off (Initial Cycle, Sinking), V <sub>TMR</sub> = 2V                            |   |     | 28   |            | mA       |

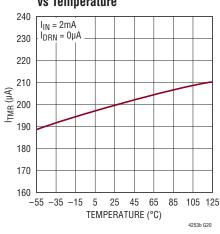

|                                            |                                                                                                                  | Timer On (Circuit Breaker, Sourcing, I <sub>DRN</sub> = 0µA), V <sub>TMR</sub> = 2V  | • | 120 | 200  | 280        | μА       |

|                                            |                                                                                                                  | Timer On (Circuit Breaker, Sourcing, I <sub>DRN</sub> = 50μA), V <sub>TMR</sub> = 2V |   |     | 600  |            | μА       |

|                                            |                                                                                                                  | Timer Off (Circuit Breaker, Sinking), V <sub>TMR</sub> = 2V                          | • | 3   | 5    | 7          | μА       |

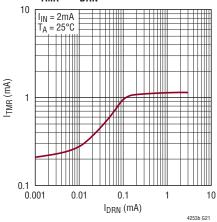

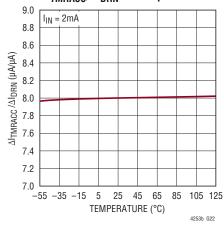

| $\frac{\Delta I_{TMRACC}}{\Delta I_{DRN}}$ | $\frac{I_{TMR} \text{ at } I_{DRN} = 50\mu\text{A} - I_{TMR} \text{ at } I_{DRN} = 0\mu\text{A}}{50\mu\text{A}}$ | Timer On (Circuit Breaker with I <sub>DRN</sub> = 50μA)                              | • | 7   | 8    | 9          | μΑ/μΑ    |

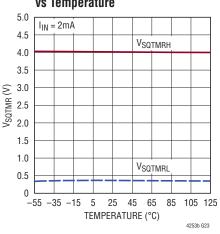

| V <sub>SQTMRH</sub>                        | SQTIMER Pin Voltage High Threshold                                                                               |                                                                                      | • | 3.5 | 4    | 4.5        | V        |

| V <sub>SQTMRL</sub>                        | SQTIMER Pin Voltage Low Threshold                                                                                |                                                                                      |   |     | 0.33 |            | V        |

| I <sub>SQTMR</sub>                         | SQTIMER Pin Current                                                                                              | SQTIMER On (Power Good<br>Sequence, Sourcing), V <sub>SQTMR</sub> = 2V               | • | 3   | 5    | 7          | μА       |

|                                            |                                                                                                                  | SQTIMER Off (Power Good<br>Sequence, Sinking), V <sub>SQTMR</sub> = 2V               |   |     | 28   |            | mA       |

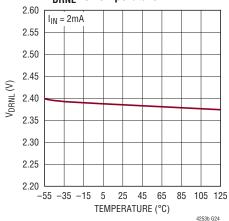

| V <sub>DRNL</sub>                          | DRAIN Pin Voltage Low Threshold                                                                                  | For PWRGD1, PWRGD2, PWRGD3 Status                                                    | • | 2   | 2.39 | 3          | V        |

| I <sub>DRNL</sub>                          | DRAIN Leakage Current                                                                                            | V <sub>DRAIN</sub> = 5V<br>V <sub>DRAIN</sub> = 4V                                   |   |     | ±0.1 | ±1         | μA<br>μA |

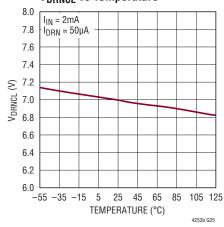

| V <sub>DRNCL</sub>                         | DRAIN Pin Clamp Voltage                                                                                          | I <sub>DRN</sub> = 50μA                                                              | • | 6   | 7    | 8.5        | V        |

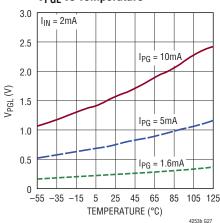

| V <sub>PGL</sub>                           | PWRGD1, PWRGD2, PWRGD3 Output Low Voltage                                                                        | I <sub>PG</sub> = 1.6mA<br>I <sub>PG</sub> = 5mA                                     | • |     | 0.25 | 0.4<br>1.2 | V        |

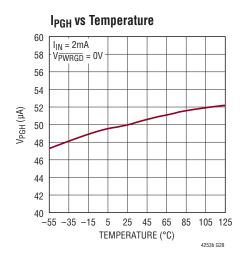

| I <sub>PGH</sub>                           | PWRGD1, PWRGD2, PWRGD3<br>Output High Current                                                                    | V <sub>PG</sub> = 0V (Sourcing)                                                      | • | 30  | 50   | 70         | μА       |

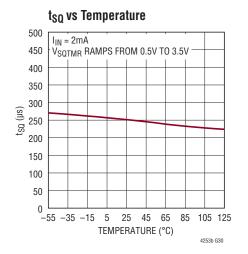

| t <sub>SQ</sub>                            | SQTIMER Default Ramp Period                                                                                      | SQTIMER Pin Floating,<br>V <sub>SQTMR</sub> Ramps from 0.5V to 3.5V                  |   |     | 250  |            | μs       |

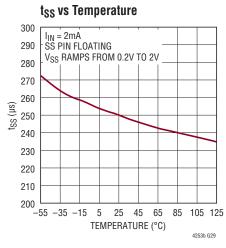

| t <sub>SS</sub>                            | SS Default Ramp Period                                                                                           | SS Pin Floating, V <sub>SS</sub> Ramps from 0.2V to 2V                               |   |     | 250  |            | μs       |

| t <sub>PLLUG</sub>                         | UV Low to GATE Low                                                                                               |                                                                                      | • |     | 0.4  | 5          | μs       |

| t <sub>PHLOG</sub>                         | OV High to GATE Low                                                                                              |                                                                                      | • |     | 0.4  | 5          | μs       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to  $V_{\text{EE}}$  unless otherwise specified.

TECHNOLOGY TECHNOLOGY

## I<sub>TMR</sub> (Initial Cycle, Sourcing) vs Temperature

## I<sub>TMR</sub> (Circuit Breaker, Sourcing) vs Temperature

#### ΔI<sub>TMRACC</sub>/ΔI<sub>DRN</sub> vs Temperature

## SQTIMER Threshold vs Temperature

### **V<sub>DRNL</sub> vs Temperature**

### **V<sub>DRNCL</sub>** vs Temperature

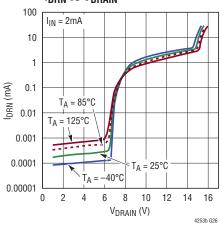

### I<sub>DRN</sub> vs V<sub>DRAIN</sub>

#### **V<sub>PGL</sub>** vs Temperature

## PIN FUNCTIONS

**EN2 (Pin 1):** Power Good Status Output Two Enable. This is a TTL compatible input that is used to control  $\overline{PWRGD2}$  and  $\overline{PWRGD3}$  outputs. When EN2 is driven low, both  $\overline{PWRGD2}$  and  $\overline{PWRGD3}$  will go high. When EN2 is driven high,  $\overline{PWRGD2}$  will go low provided  $\overline{PWRGD1}$  has been active for more than one power good sequence delay ( $t_{SQT}$ ) provided by the sequencing timer. EN2 can be used to control the power good sequence. This pin is internally pulled low by a 120µA current source.

PWRGD2 (Pin 2): Power Good Status Output Two. Power good sequence starts with PWRGD1 latching active low. PWRGD2 will latch active low after EN2 goes high and after one power good sequence delay t<sub>SQT</sub> provided by the sequencing timer from the time PWRGD1 goes low, whichever comes later. PWRGD2 is reset by PWRGD1 going high or EN2 going low. This pin is internally pulled high by a 50µA current source.

**PWRGD1** (**Pin 3**): Power Good Status Output One. At start-up, PWRGD1 latches active low and starts the power good sequence when the DRAIN pin is below 2.39V and GATE is within 2.8V of  $V_{IN}$ . PWRGD1 status is reset by UV,  $V_{IN}$  (UVLO), RESET going high or circuit breaker fault time-out. This pin is internally pulled high by a 50μA current source.

$V_{IN}$  (Pin 4): Positive Supply Input. Connect this pin to the positive side of the supply through a dropping resistor. A shunt regulator clamps  $V_{IN}$  at 13V above  $V_{EE}$ . An internal undervoltage lockout (UVLO) circuit holds GATE low until the  $V_{IN}$  pin is greater than  $V_{LKO}$ , overriding UV and OV. If UV is high, OV is low and  $V_{IN}$  comes out of UVLO, TIMER starts an initial timing cycle before initiating GATE ramp up. If  $V_{IN}$  drops below approximately 8.2V, GATE pulls low immediately.

## PIN FUNCTIONS

**RESET (Pin 5):** Circuit Breaker Reset Pin. This is an asynchronous TTL compatible input. RESET going high will pull GATE, SS, TIMER, SQTIMER low and the PWRGD outputs high. The RESET pulse must be wide enough to discharge any voltage on the TIMER pin below V<sub>TMRL</sub>. After the reset of a latched fault, the chip waits for the interlock conditions before recovering as described in Interlock Conditions in the Operation section.

**SS (Pin 6):** Soft-Start Pin. This pin is used to ramp inrush current during start up, thereby effecting control over di/dt. A 20X attenuated version of the SS pin voltage is presented to the current limit amplifier. This attenuated voltage limits the MOSFET's drain current through the sense resistor during the soft-start current limiting. At the beginning of the start-up cycle, the SS capacitor (C<sub>SS</sub>) is ramped by a 22µA current source. The GATE pin is held low until SS exceeds 20 •  $V_{OS} = 0.2V$ . SS is internally shunted by a 100k R<sub>SS</sub> which limits the SS pin voltage to 2.2V. This corresponds to an analog current limit SENSE voltage of 100mV. If the SS capacitor is omitted, the SS pin ramps up in about 250µs. The SS pin is pulled low under any of the following conditions: UVLO at V<sub>IN</sub>, UV, OV, during the initial timing cycle, a circuit breaker fault time-out or the RESET pin going high.

**SENSE (Pin 7):** Circuit Breaker/Current Limit Sense Pin. Load current is monitored by a sense resistor  $R_S$  connected between SENSE and  $V_{EE}$ , and controlled in three steps. If SENSE exceeds  $V_{CB}$  (50mV), the circuit breaker comparator activates a (200 $\mu$ A + 8 •  $I_{DRN}$ ) TIMER pull-up current. If SENSE exceeds  $V_{ACL}$ , the analog current-limit amplifier pulls GATE down to regulate the MOSFET current at  $V_{ACL}/R_S$ . In the event of a catastrophic short-circuit, SENSE may overshoot  $V_{ACL}$ . If SENSE reaches  $V_{FCL}$  (200mV), the fast current-limit comparator pulls GATE low with a strong pull-down. To disable the circuit breaker and current limit functions, connect SENSE to  $V_{EE}$ .

**V<sub>EE</sub> (Pin 8):** Negative Supply Voltage Input. Connect this pin to the negative side of the power supply.

**GATE (Pin 9):** N-channel MOSFET Gate Drive Output. This pin is pulled high by a  $50\mu\text{A}$  current source. GATE is pulled low by invalid conditions at  $V_{IN}$  (UVLO), UV, OV, during the initial timing cycle, a circuit breaker fault time-out or the RESET pin going high. GATE is actively servoed to control the fault current as measured at SENSE. Compensation capacitor,  $C_C$ , at GATE stabilizes this loop. A comparator monitors GATE to ensure that it is low before allowing an initial timing cycle, then the GATE ramps up after an overvoltage event or restart after a current limit fault. During GATE start-up, a second comparator detects GATE within 2.8V of  $V_{IN}$  before  $\overline{PWRGD1}$  can be set and power good sequencing starts.

**DRAIN (Pin 10):** Drain Sense Input. Connecting an external resistor,  $R_D$  between this pin and the MOSFET's drain  $(V_{OUT})$  allows voltage sensing below 6.15V and current feedback to TIMER. A comparator detects if DRAIN is below 2.39V and together with the GATE high comparator, sets the  $\overline{PWRGD1}$  flag. If  $V_{OUT}$  is above  $V_{DRNCL}$ , the DRAIN pin is clamped at approximately  $V_{DRNCL}$ .  $R_D$  current is internally multiplied by 8 and added to TIMER's 200 $\mu$ A during a circuit breaker fault cycle. This reduces the fault time and MOSFET heating.

**OV** (**Pin 11**): Overvoltage Input. For the LTC4253B, the threshold at the OV pin is set at 6.15V with 0.3V hysteresis. If OV > 6.15V, GATE pulls low. When OV returns below 5.85V, GATE start-up begins without an initial timing cycle. If OV occurs in the middle of an initial timing cycle, the initial timing cycle is restarted after OV goes away. OV does not reset the latched fault or  $\overline{PWRGD1}$  flag. The internal UVLO at  $V_{IN}$  always overrides OV. A 1nF to 10nF capacitor at OV prevents transients and switching noise from affecting the OV thresholds and prevents glitches at the GATE.

## PIN FUNCTIONS

**UV (Pin 12):** Undervoltage Input. For the LTC4253B, the threshold at the UV pin is set at 3.225V with 0.3V hysteresis. If UV < 2.925V,  $\overline{PWRGD1}$  pulls high, both GATE and TIMER pull low. If UV rises above 3.225V, this initiates an initial timing cycle followed by GATE start-up. The internal UVLO at V<sub>IN</sub> always overrides UV. A low at UV resets an internal fault latch. A 1nF to 10nF capacitor at UV prevents transients and switching noise from affecting the UV thresholds and prevents glitches at the GATE pin.

**TIMER (Pin 13):** Timer Input. Timer is used to generate an initial timing delay at start-up, and to delay shutdown in the event of an output overload (circuit breaker fault). Timer starts an initial timing cycle when the following conditions are met: RESET is low, UV is high, OV is low,  $V_{IN}$  clears UVLO, TIMER pin is low, GATE pin is lower than  $V_{GATEL}$ , SS < 0.2V, and  $V_{SENSE} - V_{EE} < V_{CB}$ . A pull-up current of 5µA then charges  $C_T$ , generating a time delay. If  $C_T$  charges to  $V_{TMRH}$  (4V), the timing cycle terminates. TIMER quickly pulls low and GATE is activated.

If SENSE exceeds 50mV while GATE is high, a circuit breaker cycle begins with a 200 $\mu$ A pull-up current charging  $C_T$ . If DRAIN is approximately 7V during this cycle, the timer pull-up has an additional current of 8 •  $I_{DRN}$ . If SENSE drops below 50mV before TIMER reaches 4V, a 5 $\mu$ A pull-down current slowly discharges the  $C_T$ . In the event that  $C_T$  eventually integrates up to the  $V_{TMRH}$  (4V) threshold, the circuit breaker trips, GATE quickly pulls low and  $\overline{PWRGD1}$  pulls high. TIMER latches high with a 5 $\mu$ A

pull-up source. This latched fault may be cleared by driving RESET high until TIMER is pulled low. Other ways of clearing the fault include pulling the  $V_{IN}$  pin momentarily below ( $V_{LKO}-V_{LKH}$ ), pulling TIMER low with an external device or pulling UV below 2.925V.

**SQTIMER (Pin 14):** Sequencing Timer Input. The sequencing timer provides a delay  $t_{SQT}$  for the power good sequencing. This delay is adjusted by connecting an appropriate capacitor to this pin. If the SQTIMER capacitor is omitted, the SQTIMER pin ramps from 0V to 4V in about 300 $\mu$ s.

EN3 (Pin 15): Power Good Status Output Three Enable. This is a TTL compatible input that is used to control the PWRGD3 output. When EN3 is driven low, PWRGD3 will go high. When EN3 is driven high, PWRGD3 will go low provided PWRGD2 has been active for for more than one power good sequence delay ( $t_{SQT}$ ). EN3 can be used to control the power good sequence. This pin is internally pulled low by a 120 $\mu$ A current source.

**PWRGD3** (Pin 16): Power Good Status Output Three. Power good sequence starts with PWRGD1 latching active low. PWRGD3 will latch active low after EN3 goes high and after one power good sequence delay t<sub>SQT</sub> provided by the sequencing timer from the time PWRGD2 goes low, whichever comes later. PWRGD3 is reset by PWRGD1 going high or EN3 going low. This pin is internally pulled high by a 50µA current source.

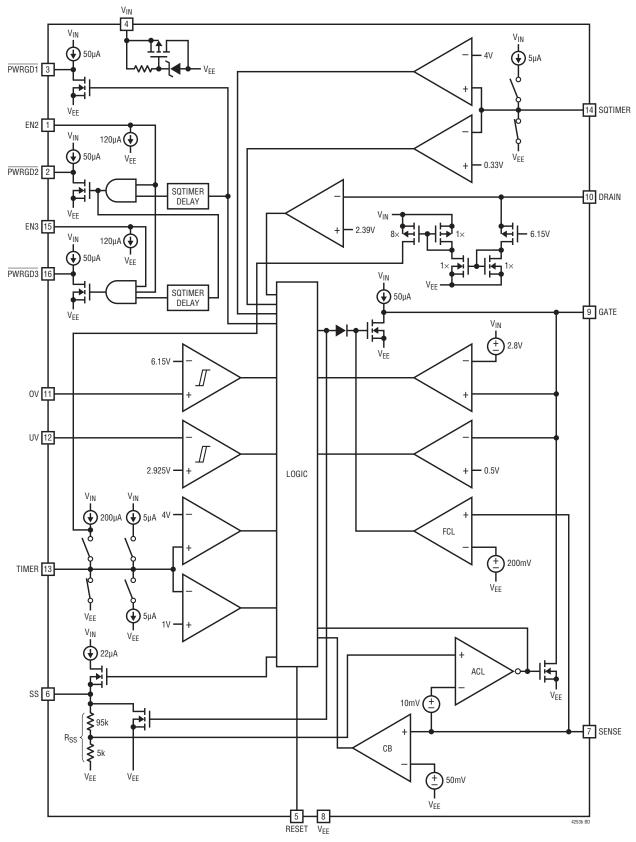

## **BLOCK DIAGRAM**

## **OPERATION**

#### **Hot Circuit Insertion**

When circuit boards are inserted into a live backplane. the supply bypass capacitors can draw huge transient currents from the power bus as they charge. The flow of current damages the connector pins and glitches the power bus, causing other boards in the system to reset. The LTC4253B is designed to turn on a circuit board supply in a controlled manner, allowing insertion or removal without glitches or connector damage.

#### Initial Start-Up

The LTC4253B resides on a removable circuit board and control the path between the connector and load or power conversion circuitry with an external MOSFET switch (see Figure 1). Both inrush control and short-circuit protection are provided by the MOSFET.

A detailed schematic is shown in Figure 2. -48V and -48RTN receive power through the longest connector pins and are the first to connect when the board is inserted. The GATE pin holds the MOSFET off during this time. UV/OV determines whether or not the MOSFET should be turned on based upon internal high accuracy thresholds and an external divider. UV/OV does double duty by also monitoring whether or not the connector is seated. The top of the divider detects -48RTN by way of a short connector pin that is the last to mate during the insertion sequence.

Figure 1. Basic LTC4253B Hot Swap Topology

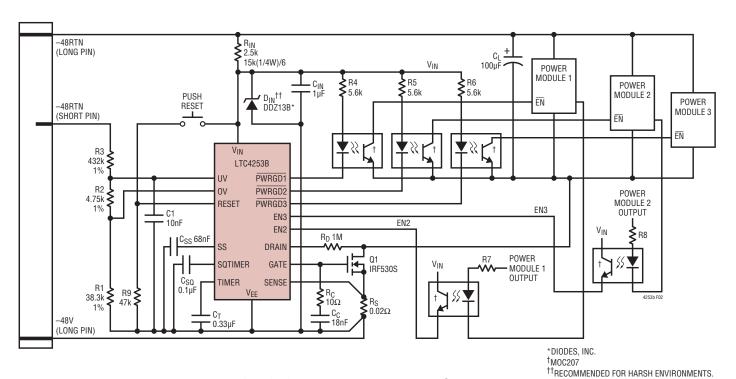

Figure 2. -48V/2.5A Application with a Wider Operating Range

4253hf

## **OPERATION**

#### Interlock Conditions

A start-up sequence commences once these "interlock" conditions are met:

- 1. The input voltage  $V_{IN}$  exceeds  $V_{LKO}$  (UVLO).

- 2. The voltage at  $UV > V_{UVHI}$ .

- 3. The voltage at  $OV < V_{OVLO}$ .

- 4. The input voltage at RESET < 0.8V.

- 5. The (SENSE  $V_{EE}$ ) voltage < 50mV ( $V_{CB}$ )

- 6. The voltage at SS is  $< 0.2V (20 \bullet V_{OS})$

- The voltage on the TIMER capacitor (C<sub>T</sub>) is < 1V (V<sub>TMRL</sub>).

- 8. The voltage at GATE is < 0.5V ( $V_{GATEL}$ )

The first four conditions are continuously monitored and the latter four are checked prior to initial timing or GATE ramp-up. Upon exiting an OV condition, the TIMER pin voltage requirement is inhibited. Details are described in the Applications Information, Timing Waveforms section.

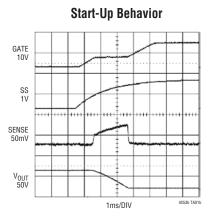

If RESET < 0.8V occurs after the LTC4253B comes out of UVLO (interlock condition 1) and undervoltage (interlock condition 2), GATE and SS are released without an initial TIMER cycle once the other interlock conditions are met (see Figure 12a). If not, TIMER begins the start-up sequence by sourcing 5µA into C<sub>T</sub>. If V<sub>IN</sub>, UV or OV falls out of range or RESET asserts, the start-up cycle stops and TIMER discharges  $C_T$  to less than 1V, then waits until the aforementioned conditions are once again met. If C<sub>T</sub> successfully charges to 4V, TIMER pulls low and both SS and GATE pins are released. GATE sources 50µA (IGATE), charging the MOSFET gate and associated capacitance. The SS voltage ramp limits V<sub>SENSE</sub> to control the inrush current. PWRGD1 pulls active low when GATE is within 2.8V of  $V_{IN}$  and DRAIN is lower than  $V_{DRNL}$ . This sets off the power good sequence in which PWRGD2 and then PWRGD3 is subsequently pulled low after a delay, adjustable through the SQTIMER capacitor C<sub>SQ</sub> or by external control inputs EN2 and EN3. In this way, external loads or power modules controlled by the three PWRGD signals are turned on in a controlled manner without overloading the power bus.

Two modes of operation are possible during the time the MOSFET is first turned on, depending on the values of external components, MOSFET characteristics and nominal design current. One possibility is that the MOS-FET will turn on gradually so that the inrush into the load capacitance remains a low value. The output will simply ramp to -48V and the LTC4253B will fully enhance the MOSFET. A second possibility is that the load current exceeds the soft-start current limit threshold of [V<sub>SS</sub>(t)/  $20 - V_{OS}$ ]/R<sub>S</sub>. In this case the LTC4253B ramps the output by sourcing soft-start limited current into the load capacitance. If the soft-start voltage is below 1.2V, the circuit breaker TIMER is held low. Above 1.2V. TIMER ramps up. It is important to set the timer delay so that, regardless of which start-up mode is used, the TIMER ramp is less than one circuit breaker delay time. If this condition is not met, the LTC4253B may shut down after one circuit breaker delay time.

#### **Board Removal**

When the board is withdrawn from the card cage, the UV/ OV divider is the first to lose connection. This shuts off the MOSFET and commutates the flow of current in the connector. When the power pins subsequently separate there is no arcing.

#### **Current Control**

Three levels of protection handle short-circuit and overload conditions. Load current is monitored by SENSE and resistor  $R_S$ . There are three distinct thresholds at SENSE: 50mV for a timed circuit breaker function; 100mV for an analog current limit loop; and 200mV for a fast, feedforward comparator which limits peak current in the event of a catastrophic short-circuit.

If, due to an output overload, the voltage drop across  $R_S$  exceeds 50mV, TIMER sources 200 $\mu$ A into  $C_T$ .  $C_T$  eventually charges to a 4V threshold and the LTC4253B shuts off. If the overload goes away before  $C_T$  reaches 4V and SENSE measures less than 50mV,  $C_T$  slowly discharges (5 $\mu$ A). In this way the LTC4253B's circuit breaker function responds to low duty cycle overloads, and accounts for the fast heating and slow cooling characteristic of the MOSFET.

## **OPERATION**

Higher overloads are handled by an analog current limit loop. If the drop across  $R_S$  reaches  $V_{ACL},$  the current limiting loop servos the MOSFET gate and maintains a constant output current of  $V_{ACL}/R_S.$  In current limit mode,  $V_{OUT}$  (MOSFET drain-source voltage drop) typically rises and this increases MOSFET heating. If  $V_{OUT} > V_{DRNCL},$  connecting an external resistor,  $R_D$  between  $V_{OUT}$  and DRAIN allows the fault timing cycle to be shortened by accelerating the charging of the TIMER capacitor. The TIMER pull-up current is increased by 8  $\bullet$   $I_{DRN}.$  Note that because SENSE > 50 mV, TIMER charges  $C_T$  during this time, and the LTC4253B eventually shuts down.

Low impedance failures on the load side of the LTC4253B, coupled with 48V or more driving potential, can produce current slew rates well in excess of  $50A/\mu s$ . Under these conditions, overshoot is inevitable. A fast SENSE comparator with a threshold of 200mV detects overshoot and pulls GATE low much harder and hence much faster than the weaker current limit loop. The  $V_{ACL}/R_S$  current limit loop then takes over and servos the current as previously described. As before, TIMER runs and shuts down the LTC4253B when  $C_T$  reaches 4V.

If  $C_T$  reaches 4V, the LTC4253B latches off with a  $5\mu A$  pull-up current source. The LTC4253B circuit breaker latch is reset by either pulling the RESET pin active high until TIMER goes low, pulling UV momentarily low, dropping the input voltage  $V_{IN}$  below the internal UVLO threshold or pulsing TIMER momentarily low with a switch.

Although short-circuits are the most obvious fault type, several operating conditions may invoke overcurrent protection. Noise spikes from the backplane or load, input steps caused by the connection of a second, higher voltage supply, transient currents caused by faults on adjacent circuit boards sharing the same power bus or the insertion of non-hot swappable products could cause higher than anticipated input current and temporary detection of an overcurrent condition. The action of TIMER and  $C_T$  rejects these events allowing the LTC4253B to "ride out" temporary overloads and disturbances that could trip a simple current comparator and, in some cases, blow a fuse.

## **APPLICATIONS INFORMATION** (Refer to Block Diagram)

#### SHUNT REGULATOR

A fast responding shunt regulator clamps the  $V_{IN}$  pin to 13V ( $V_Z$ ). Power is derived from –48RTN by an external current limiting resistor,  $R_{IN}$ . A 1 $\mu$ F decoupling capacitor,  $C_{IN}$  filters supply transients and contributes a short delay at start-up.

To meet creepage requirements R<sub>IN</sub> may be split into two or more series connected units. This introduces a wider total spacing than is possible with a single component while at the same time ballasting the potential across the gap under each resistor. The LTC4253B is fundamentally a low voltage device that operates with –48V as its reference ground. To further protect against arc discharge into

its pins, the area in and around the LTC4253B and all associated components should be free of any other planes such as chassis ground, return, or secondary-side power and ground planes.

$V_{IN}$  may be biased with additional current up to 30mA, to accommodate external loading such as the  $\overline{PWRGD}$  opto-couplers shown in Figure 2. As an alternative to running higher current, simply buffer  $V_{IN}$  with an emitter follower. A method that cascodes the  $\overline{PWRGD}$  outputs is shown in Figure 16.

$V_{\text{IN}}$  is rated to handle 30mA within the thermal limits of the package, and is tested to survive a 100 $\mu$ s, 100mA

TECHNOLOGY TECHNOLOGY

pulse. To protect  $V_{IN}$  against damage from higher amplitude spikes, clamp  $V_{IN}$  to  $V_{EE}$  with a 13V Zener diode. Star connect  $V_{EE}$  and all  $V_{EE}$ -referred components to the sense resistor Kelvin terminal as illustrated in Figure 2, keeping trace lengths between  $V_{IN}$ ,  $C_{IN}$ ,  $D_{IN}$  and  $V_{EE}$  as short as possible.

### INTERNAL UNDERVOLTAGE LOCKOUT (UVLO)

A hysteretic comparator, UVLO, monitors  $V_{IN}$  for undervoltage. The thresholds are defined by  $V_{LKO}$  and its hysteresis  $V_{LKH}$ . When  $V_{IN}$  rises above  $V_{LKO}$ , the chip is enabled; below ( $V_{LKO} - V_{LKH}$ ), it is disabled and GATE is pulled low. The UVLO function at  $V_{IN}$  should not be confused with the UV and OV pins. These are completely separate functions.

#### **UV/OV COMPARATORS**

A UV hysteretic comparator detects undervoltage conditions at the UV pin, with the following thresholds:

UV low-to-high  $(V_{UVHI}) = 3.225V$

UV high-to-low  $(V_{UVI,0}) = 2.925V$

An OV hysteretic comparator detects overvoltage conditions at the OV pin, with the following thresholds:

OV low-to-high  $(V_{OVHI}) = 6.150V$

OV high-to-low  $(V_{OVLO}) = 5.850V$

The UV and OV trip point ratio is designed to match the standard telecom operating range of 43V to 82V when connected together as in the Typical Application. A resistive divider is used to scale the supply voltage. Using 402k and 32.4k gives a typical operating range of 43.2V to 82.5V. The undervoltage shutdown and overvoltage recovery thresholds are then 39.2V and 78.4V. 1% divider resistors are recommended to preserve threshold accuracy.

The resistive divider values shown set a standing current of slightly more than  $100\mu A$  and define an impedance at UV/OV of  $30k\Omega$ . In most applications,  $30k\Omega$  impedance coupled with 300mV UV hysteresis make the LTC4253B insensitive to noise. If more noise immunity is desired, add a 1nF to 10nF filter capacitor from UV/OV to V<sub>FF</sub>.

The separate UV and OV pins can be used for wider operating range such as 35.6V to 76.3V range as shown in Figure 2. Other combinations are possible with different resistors arrangement.

#### **UV/OV OPERATION**

A low input to the UV comparator will reset the chip and pull the GATE and TIMER pins low. A low-to-high UV transition will initiate an initial timing sequence if the other interlock conditions are met. A high-to-low transition in the UV comparator immediately shuts down the LTC4253B, pulls the MOSFET gate low and resets the three latched PWRGD signals high.

An overvoltage condition is detected by the OV comparator and pulls GATE low, thereby shutting down the load, but it will not reset the circuit breaker TIMER and PWRGD flags. Returning from the overvoltage condition will restart the GATE pin if all the interlock conditions except TIMER are met. Only during the initial timing cycle does OV condition have an effect of resetting TIMER.

#### DRAIN

Connecting an external resistor,  $R_D$ , to this dual function DRAIN pin allows  $V_{OUT}$  (MOSFET drain-source voltage drop) sensing without it being damaged by large voltage transients. Below 5V, negligible pin leakage allows a DRAIN low comparator to detect  $V_{OUT}$  less than 2.39V ( $V_{DRNL}$ ). This, together with the GATE low comparator, sets the  $\overline{PWRGD}$  flag.

When  $V_{OUT} > V_{DRNCL}$ , the DRAIN pin is clamped at  $V_{DRNCL}$  and the current flowing in  $R_D$  is given by:

$$I_{DRN} \approx \frac{V_{OUT} - V_{DRNCL}}{R_{D}} \tag{1}$$

This current is scaled up 8 times during a circuit breaker fault before being added to the nominal  $200\mu A$ . This accelerates the fault TIMER pull-up when the MOSFET's drain-source voltage exceeds  $V_{DRNCL}$  and effectively shortens the MOSFET heating duration.

#### **TIMER**

The operation of the TIMER pin is somewhat complex as it handles several key functions. A capacitor  $C_T$  is used at TIMER to provide timing for the LTC4253B. Four different charging and discharging modes are available at TIMER:

- 1. 5µA slow charge; initial timing delay.

- 2. (200µA + 8 I<sub>DRN</sub>) fast charge; circuit breaker delay.

- 3. 5µA slow discharge; circuit breaker "cool-off."

- Low impedance switch; resets the TIMER capacitor after an initial timing delay, in UVLO, in UV and in OV during initial timing and when RESET is high.

For initial timing delay, the  $5\mu A$  pull-up is used. The low impedance switch is turned off and the  $5\mu A$  current source is enabled when the interlock conditions are met.  $C_T$  charges to 4V in a time period given by:

$$t = \frac{4V \cdot C_T}{5\mu A} \tag{2}$$

When  $C_T$  reaches  $V_{TMRH}$  ( 4V), the low impedance switch turns on and discharges  $C_T$ . A GATE start-up cycle begins and both SS and GATE outputs are released.

#### **CIRCUIT BREAKER TIMER OPERATION**

If the SENSE pin detects more than 50mV drop across  $R_S$ , the TIMER pin charges  $C_T$  with (200 $\mu$ A + 8 • IDRN). If  $C_T$  charges to 4V, the GATE pin pulls low and the LTC4253B latches off. The LTC4253B remains latched off until the RESET pin is momentarily pulsed high, the UV pin is momentarily pulsed low, the TIMER pin is momentarily discharged low by an external switch or  $V_{IN}$  dips below UVLO and is then restored. The circuit breaker timeout period is given by:

$$t = \frac{4V \cdot C_T}{200\mu A + 8 \cdot I_{DRN}}$$

(3)

If  $V_{OUT}$  < 5V, an internal PMOS isolates DRAIN pin leakage current and this makes  $I_{DRN}$  = 0 in Equation (3). If  $V_{OUT}$  is above  $V_{DRNCL}$  during the circuit breaker fault period, the charging of  $C_T$  is accelerated by 8 •  $I_{DRN}$  of Equation (1).

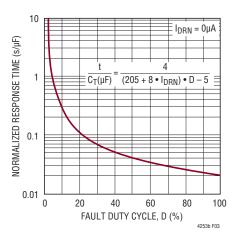

Intermittent overloads may exceed the 50mV threshold at SENSE but, if their duration is sufficiently short, TIMER will not reach 4V and the LTC4253B will not shut the external MOSFET off. To handle this situation, the TIMER discharges  $C_T$  slowly with a  $5\mu A$  pull-down whenever the SENSE voltage is less than 50mV. Therefore, any intermittent overload with  $V_{OUT} < 5V$  and an aggregate duty cycle of more than 2.5% will eventually trip the circuit breaker and shut down the LTC4253B. Figure 3 shows the circuit breaker response time in seconds normalized to  $1\mu F$ . The asymmetric charging and discharging of  $C_T$  is a fair gauge of MOSFET heating.

The normalized circuit response time is estimated by:

$$\frac{t}{C_T(\mu F)} = \frac{4}{\left[ (205 + 8 \bullet I_{DRN}) \bullet D - 5 \right]} \text{ for } D > 2.5\%$$

(4)

Figure 3. Circuit Breaker Response Time

LINEAR TECHNOLOGY

#### POWER GOOD SEQUENCING

After the initial TIMER cycle, GATE ramps up to turn on the external MOSFET which in turn pulls DRAIN low.

When GATE is within 2.8V of  $V_{IN}$  and DRAIN is lower than  $V_{DRNL}$ , the power good sequence starts with  $\overline{PWRGD1}$  pulling active low. This starts off a 5µA pull-up on the SQTIMER pin which ramps up until it reaches the 4V threshold then pulls low. When the SQTIMER pin floats, this delay  $t_{SQT}$  is about 300µs. Connecting an external capacitor  $C_{SQ}$  from SQTIMER to  $V_{EE}$  modifies the delay to:

$$t_{SQT} = \frac{4V \cdot C_{SQ}}{5\mu A} \tag{5}$$

PWRGD2 asserts when EN2 goes high and PWRGD1 has asserted for more than one t<sub>SQT</sub>. When PWRGD2 successfully pulls low, SQTIMER ramps up on another delay cycle. PWRGD3 asserts when EN2 and EN3 go high and PWRGD2 has asserted for more than one t<sub>SQT</sub>.

All three PWRGD signals are reset in UVLO, in UV condition, if RESET is high or when C<sub>T</sub> charges up to 4V. In addition, PWRGD2 is reset by EN2 going low. PWRGD3 is reset by EN2 or EN3 going low. An overvoltage condition has no effect on the PWRGD flags. A 50µA current pulls each PWRGD pin high when reset. As power modules signal common are different from PWRGD, optoisolation is recommended. These three pins can sink an optodiode current. Figure 16 shows an NPN configuration for the PWRGD interface. A limiting base resistor should be used for each NPN and the module enable input should have protection from negative bias current.

#### **SOFT-START**

Soft-start is effective in limiting the inrush current during GATE start-up. Unduly long soft-start intervals can exceed the MOSFET's SOA duration if powering-up into an active load. When the SS pin floats, an internal current source ramps SS from 0V to 2.2V in about 300 $\mu$ s. Connecting an external capacitor, CSS, from SS to ground modifies the ramp to approximate an RC response of:

$$V_{SS}(t) \approx V_{SS} \left( 1 - e^{\frac{-t}{R_{SS}C_{SS}}} \right)$$

(6)

An internal resistor divider (95k/5k) scales  $V_{SS}(t)$  down by 20 times to give the analog current limit threshold:

$$V_{ACL}(t) = \frac{V_{SS}(t)}{20} - V_{OS}$$

(7)

This allows the inrush current to be limited to  $V_{ACL}(t)/R_S$ . The offset voltage,  $V_{OS}$  (10mV), ensures  $C_{SS}$  is sufficiently discharged and the ACL amplifier is in current limit mode before GATE start-up. SS is discharged low during UVLO at  $V_{IN}$ , UV, OV, during the initial timing cycle, a latched circuit breaker fault or the RESET pin going high.

#### **GATE**

GATE is pulled low to  $V_{EE}$  under any of the following conditions: in UVLO, when RESET pulls high, in an undervoltage condition, in an overvoltage condition, during the initial timing cycle or a latched circuit breaker fault. When GATE turns on, a  $50\mu A$  current source charges the MOSFET gate and any associated external capacitance.  $V_{IN}$  limits the gate drive to no more than 14.5V.

Gate-drain capacitance ( $C_{GD}$ ) feedthrough at the first abrupt application of power can cause a gate-source voltage sufficient to turn on the MOSFET. A unique circuit pulls GATE low with practically no usable voltage at  $V_{IN}$  and eliminates current spikes at insertion. A large external gate-source capacitor is thus unnecessary for the purpose of compensating  $C_{GD}$ . Instead, a smaller value ( $\geq 10nF$ ) capacitor  $C_C$  is adequate.  $C_C$  also provides compensation for the analog current limit loop.

GATE has two comparators: the GATE low comparator looks for <0.5V threshold prior to initial timing; the GATE high comparator looks for <2.8V relative to  $V_{IN}$  and, together with DRAIN low comparator, sets  $\overline{PWRGD1}$  output during GATE start-up.

#### Sense

The SENSE pin is monitored by the circuit breaker (CB) comparator, the analog current limit (ACL) amplifier, and the fast current limit (FCL) comparator. Each of these three measures the potential of SENSE relative to  $V_{EE}$ . When SENSE exceeds 50mV, the CB comparator activates the 200 $\mu$ A TIMER pull-up. At 100mV the ACL amplifier servos the MOSFET current, and at 200mV the FCL comparator abruptly pulls GATE low in an attempt to bring the MOSFET current under control. If any of these conditions persists long enough for TIMER to charge  $C_T$  to 4V (see Equation 3), the LTC4253B shuts down and pulls GATE low.

If the SENSE pin encounters a voltage greater than  $V_{ACL}$ , the ACL amplifier will servo GATE downwards in an attempt to control the MOSFET current. Since GATE overdrives the MOSFET in normal operation, the ACL amplifier needs time to discharge GATE to the threshold of the MOSFET. For a mild overload the ACL amplifier can control the MOSFET current, but in the event of a severe overload the current may overshoot. At SENSE = 200mV the FCL comparator takes over, quickly discharging the GATE pin to near  $V_{EE}$  potential. FCL then releases, and the ACL amplifier takes over. All the while TIMER is running. The effect of FCL is to add a nonlinear response to the control loop in favor of reducing MOSFET current.

Owing to inductive effects in the system, FCL typically overcorrects the current limit loop, and GATE undershoots. A zero in the loop (resistor  $R_{\text{C}}$  in series with the gate capacitor) helps the ACL amplifier to recover.

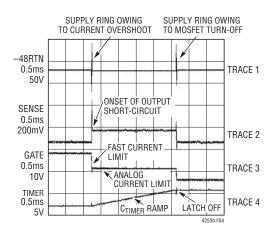

#### SHORT-CIRCUIT OPERATION

Circuit behavior arising from a load side low impedance short is shown in Figure 4. Initially the current overshoots the analog current limit level of  $V_{SENSE} = 200 \text{mV}$  (trace 2) as the GATE pin works to bring  $V_{GS}$  under control (trace 3). The overshoot glitches the backplane in the negative direction and when the current is reduced to  $100 \text{mV/R}_S$ , the backplane responds by glitching in the positive direction.

TIMER commences charging  $C_T$  (trace 4) while the analog current limit loop maintains the fault current at  $100 \text{mV/R}_S$ , which in this case is 5A (trace 2). Note that the backplane voltage (trace 1) sags under load. Timer pull-up is accelerated by  $V_{OUT}$ . When  $C_T$  reaches 4V, GATE turns off, the  $\overline{PWRGD}$  signals pull high, the load current drops to zero and the backplane rings up to over 100 V. The transient associated with the GATE turn-off can be controlled with a snubber to reduce ringing and a transient voltage suppressor (such as Diodes Inc. SMAT70A) to clip off large spikes. The choice of RC for the snubber is usually done experimentally. The value of the snubber capacitor is usually chosen between 10 to 100 times the MOSFET  $C_{OSS}$ . The value of the snubber resistor is typically between  $3\Omega$  to  $100\Omega$ .

A low impedance short on one card may influence the behavior of others sharing the same backplane. The initial glitch and backplane sag as seen in Figure 4 trace 1, can rob charge from output capacitors on the adjacent card. When the faulty card shuts down, current flows in to refresh the capacitors. If LTC4253B is used by the other cards, they respond by limiting the inrush current to a value of  $V_{ACL}/R_S$ . If  $C_T$  is sized correctly, the capacitors will recharge long before  $C_T$  times out.

Figure 4. Output Short-Circuit Behavior of LTC4253B

LINEAR TECHNOLOGY

#### **MOSFET SELECTION**

The external MOSFET switch must have adequate safe operating area (SOA) to handle short-circuit conditions until TIMER times out. These considerations take precedence over DC current ratings. A MOSFET with adequate SOA for a given application can always handle the required current but the opposite may not be true. Consult the manufacturer's MOSFET data sheet for safe operating area and effective transient thermal impedance curves.

MOSFET selection is a 3-step process by assuming the absence of soft-start capacitor. First,  $R_S$  is calculated and then the time required to charge the load capacitance is determined. This timing, along with the maximum short-circuit current and maximum input voltage, defines an operating point that is checked against the MOSFET's SOA curve.

To begin a design, first specify the required load current and load capacitance,  $I_L$  and  $C_L$ . The circuit breaker current trip point ( $V_{CB}/R_S$ ) should be set to accommodate the maximum load current. Note that maximum input current to a DC/DC converter is expected at  $V_{SUPPLY(MIN)}$ .  $R_S$  is given by:

$$R_{S} = \frac{V_{CB(MIN)}}{I_{L(MAX)}}$$

(8)

where  $V_{CB(MIN)} = 40 \text{mV}$  represents the guaranteed minimum circuit breaker threshold.

During the initial charging process, the LTC4253B may operate the MOSFET in current limit, forcing ( $V_{ACL}$ ) between 80mV to 120mV across  $R_S$ . The minimum inrush current is given by:

$$I_{\text{INRUSH(MIN)}} = \frac{V_{\text{ACL(MIN)}}}{R_{\text{S}}} \tag{9}$$

Maximum short-circuit current limit is calculated using the maximum  $V_{SENSE}$ . This gives

$$I_{SHORTCIRCUIT(MAX)} = \frac{V_{ACL(MAX)}}{R_S}$$

(10)

The TIMER capacitor  $C_T$  must be selected based on the slowest expected charging rate; otherwise TIMER might time out before the load capacitor is fully charged. A value for  $C_T$  is calculated based on the maximum time it takes the load capacitor to charge. That time is given by:

$$t_{\text{CL(CHARGE)}} = \frac{C \cdot V}{I} = \frac{C_L \cdot V_{\text{SUPPLY(MAX)}}}{I_{\text{INRUSH(MIN)}}}$$

(11)

The maximum current flowing in the DRAIN pin is given by:

$$I_{DRN(MAX)} = \frac{V_{SUPPLY(MAX)} - V_{DRNCL}}{R_{D}}$$

(12)

Approximating a linear charging rate,  $I_{DRN}$  drops from  $I_{DRN(MAX)}$  to zero, the  $I_{DRN}$  component in Equation (3) can be approximated with 0.5 •  $I_{DRN(MAX)}$ . Rearranging the equation, TIMER capacitor  $C_T$  is given by:

$$C_{T} = \frac{t_{CL(CHARGE)} \cdot (200\mu A + 4 \cdot I_{DRN(MAX)})}{4V}$$

(13)

Returning to Equation (3), the TIMER period is calculated and used in conjunction with  $V_{SUPPLY(MAX)}$  and  $I_{SHORTCIRCUIT(MAX)}$  to check the SOA curves of a prospective MOSFET.

As a numerical design example for the LTC4253B, consider a 30W load, which requires 1A input current at 36V. If  $V_{SUPPLY(MAX)} = 72V$  and  $C_L = 100\mu F$ ,  $R_D = 1M\Omega$ , Equation (8) gives  $R_S = 40m\Omega$ ; Equation (13) gives  $C_T = 414nF$ . To account for errors in  $R_S$ ,  $C_T$ , TIMER current (200 $\mu$ A), TIMER threshold (4V),  $R_D$ , DRAIN current multiplier and DRAIN voltage clamp ( $V_{DRNCL}$ ), the calculated value should be multiplied by 1.5, giving the nearest standard value of  $C_T = 680nF$ .

If a short-circuit occurs, a current of up to 120mV/40m $\Omega$ =3A will flow in the MOSFET for 6.3ms as dictated by C<sub>T</sub>=680nF in Equation (3). The MOSFET must be selected based on this criterion. The IRF530S can handle 100V and 3A for 10ms and is safe to use in this application.

Computing the maximum soft-start capacitor value during soft-start to a load short is complicated by the nonlinear MOSFET's SOA characteristics and the  $R_{SS}C_{SS}$  response. An overconservative but simple approach begins with the maximum circuit breaker current, given by:

$$I_{CB(MAX)} = \frac{V_{CB(MAX)}}{R_S}$$

(14)

where  $V_{CB(MAX)}$  is 60mV.

From the SOA curves of a prospective MOSFET, determine the time allowed,  $t_{SOA(MAX)}$ .  $C_{SS}$  is given by:

$$C_{SS} = \frac{t_{SOA(MAX)}}{0.916 \cdot R_{SS}} \tag{15}$$

In the above example,  $60\text{mV}/40\text{m}\Omega$  gives 1.5A.  $t_{SOA(MAX)}$  for the IRF530S is 40ms. From Equation (15),  $C_{SS} = 437\text{nF}$ . Actual board evaluation showed that  $C_{SS} = 100\text{nF}$  was appropriate. The ratio ( $R_{SS} \bullet C_{SS}$ ) to  $t_{CL(CHARGE)}$  is a good gauge as large ratios may result in the time-out period expiring prematurely. This gauge is determined empirically with board level evaluation.

#### **SUMMARY OF DESIGN FLOW**

To summarize the design flow, consider the Typical Application shown on the front page. It was designed for 80W and  $C_1 = 100 \mu F$ .

Calculate maximum load current: 80W/43V = 1.86A.

Calculate  $R_S$ : from Equation (8)  $R_S = 20m\Omega$ .

Calculate  $I_{SHORTCIRCUIT(MAX)}$ : from Equation (10)  $I_{SHORTCIRCUIT(MAX)} = 6A$ .

Select a MOSFET that can handle 6A at 82V: IRF530S.

Calculate  $C_T$ : from Equation (13)  $C_T$  = 256nF. Select  $C_T$  = 330nF, which gives the circuit breaker time-out period  $t_{MAX}$  = 1.65ms.

Consult MOSFET SOA curves: the IRF530S can handle 6A at 100V for 2.5ms, so it is safe to use in this application.

Calculate  $C_{SS}$ : using Equations (14) and (15) select  $C_{SS} = 68nF$ .

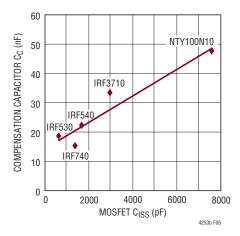

#### FREQUENCY COMPENSATION

The LTC4253B typical frequency compensation network for the analog current limit loop is a series  $R_{C}$  (10 $\Omega$ ) and  $C_{C}$  connected from GATE to  $V_{EE}$ . Figure 5 depicts the relationship between the compensation capacitor  $C_{C}$  and the MOSFET's  $C_{ISS}$ . The line in Figure 5 is used to select a starting value for  $C_{C}$  based upon the MOSFET's  $C_{ISS}$  specification. Optimized values for  $C_{C}$  are shown for several popular MOSFETs. Differences in the optimized value of  $C_{C}$  versus the starting value are small. Nevertheless, compensation values should be verified by board level short-circuit testing.

As seen in Figure 4, at the onset of a short-circuit event, the input supply voltage can ring dramatically due to series inductance. If this voltage avalanches the MOSFET, current continues to flow through the MOSFET to the output. The analog current limit loop cannot control this current flow and therefore the loop undershoots. This effect cannot be eliminated by frequency compensation. A Zener diode is required to clamp the input supply voltage and prevent MOSFET avalanche.

Figure 5. Recommended Compensation Capacitor  $\text{C}_{\text{C}}$  vs MOSFET  $\text{C}_{\text{ISS}}$  for the LTC4253B

LINEAR TECHNOLOGY

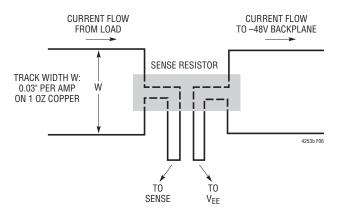

#### SENSE RESISTOR CONSIDERATIONS

For proper circuit breaker operation, Kelvin-sense PCB connections between the sense resistor and the LTC4253B's  $V_{\text{EE}}$  and SENSE pins are strongly recommended. The drawing in Figure 6 illustrates the correct way of making connections between the LTC4253B and the sense resistor. PCB layout should be balanced and symmetrical to minimize wiring errors. In addition, the PCB layout for the sense resistor should include good thermal management techniques for optimal sense resistor power dissipation.

Figure 6. Making PCB Connections to the Sense Resistor

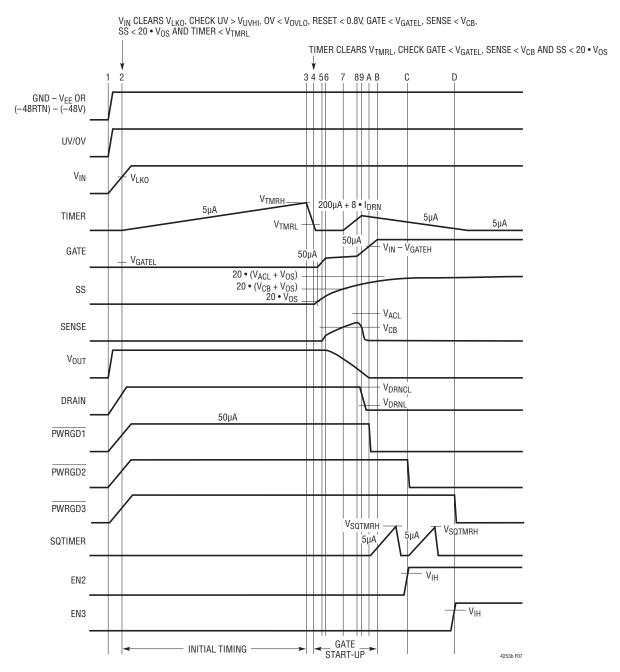

#### TIMING WAVEFORMS

#### System Power-Up

Figure 7 details the timing waveforms for a typical power-up sequence in the case where a board is already installed in the backplane and system power is applied abruptly. At time point 1, the supply ramps up, together with UV/OV,  $V_{OUT}$  and DRAIN.  $V_{IN}$  and the  $\overline{PWRGD}$  signals follow at a slower rate as set by the  $V_{IN}$  bypass capacitor. At time point 2,  $V_{IN}$  exceeds  $V_{LKO}$  and the internal logic checks for UV >  $V_{UVHI}$ , OV <  $V_{OVLO}$ , RESET < 0.8V, GATE <  $V_{GATEL}$ , SENSE <  $V_{CB}$ , SS < 20 •  $V_{OS}$ , and TIMER <  $V_{TMRL}$ . When all conditions are met, initial timing starts and the TIMER capacitor is charged by a 5µA current source pull-up. At

time point 3, TIMER reaches the V<sub>TMRH</sub> threshold and the initial timing cycle terminates. The TIMER capacitor is quickly discharged. At time point 4, the V<sub>TMRI</sub> threshold is reached and the conditions of GATE < V<sub>GATEL</sub>, SENSE < V<sub>CB</sub> and SS < 20 • V<sub>OS</sub> must be satisfied before the GATE start-up cycle begins. SS ramps up as dictated by Rss • Css (as in Equation 6); GATE is held low by the analog current limit (ACL) amplifier until SS crosses 20 •  $V_{OS}$ . Upon releasing GATE, 50µA sources into the external MOSFET gate and compensation network. When the GATE voltage reaches the MOSFET's threshold, current flows into the load capacitor at time point 5. At time point 6, load current reaches SS control level and the analog current limit loop activates. Between time points 6 and 8, the GATE voltage is servoed, the SENSE voltage is regulated at  $V_{ACI}$  (t) (Equation 7) and soft-start limits the slew rate of the load current. If the SENSE voltage  $(V_{SENSE} - V_{EE})$ reaches the V<sub>CB</sub> threshold at time point 7, circuit breaker TIMER activates. The TIMER capacitor,  $C_T$ , is charged by a (200µA + 8 • I<sub>DBN</sub>) current pull-up. As the load capacitor nears full charge, load current begins to decline. At time point 8, the load current falls and the SENSE voltage drops below V<sub>ACL</sub>(t). The analog current limit loop shuts off and the GATE pin ramps further. At time point 9, the SENSE voltage drops below  $V_{CB}$ , the fault TIMER ends, followed by a 5µA discharge cycle (cool-off). The duration between time points 7 and 9 must be shorter than one circuit breaker delay to avoid fault time-out during GATE ramp-up. When GATE ramps past the V<sub>GATEH</sub> threshold at time point A, PWRGD1 pulls low. At time point B, GATE reaches its maximum voltage as determined by V<sub>IN</sub>. At time point A, SQTIMER starts its ramp-up to 4V. Having satisfied the requirement that PWRGD1 is low for more than one t<sub>SOT</sub>, PWRGD2 pulls low after EN2 pulls high above the  $V_{IH}$  threshold at time point C. This sets off the second SQTIMER ramp-up. Having satisfied the requirement that PWRGD2 is low for more than one t<sub>SOT</sub>, PWRGD3 pulls low after EN3 pulls high at time point D.

Figure 7. System Power-Up Timing (All Waveforms Are Referenced to VEE)

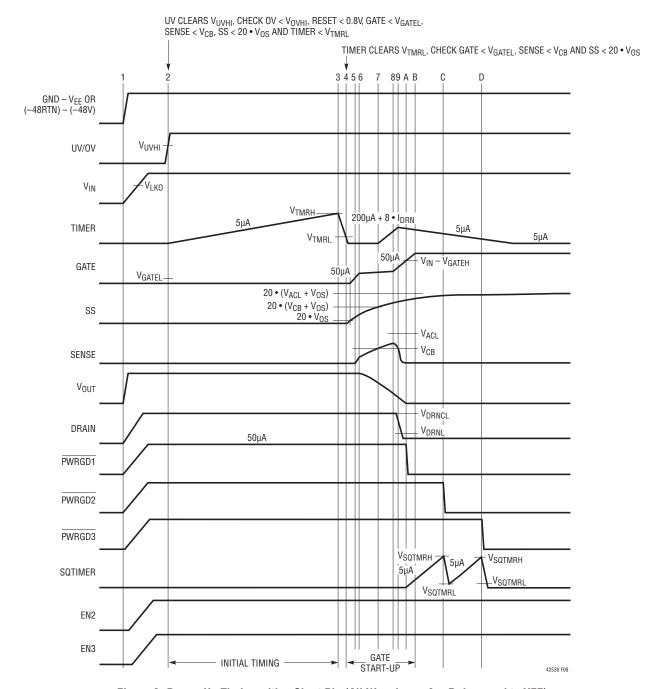

#### Live Insertion with Short Pin Control of UV/OV

In the example shown in Figure 8, power is delivered through long connector pins whereas the UV/OV divider makes contact through a short pin. This ensures the power

connections are firmly established before the LTC4253B is activated. At time point 1, the power pins make contact and  $V_{IN}$  ramps through  $V_{LKO}$ . At time point 2, the UV/OV divider makes contact and its voltage exceeds  $V_{UVHI}$ . In

Figure 8. Power-Up Timing with a Short Pin (All Waveforms Are Referenced to VEE)

addition, the internal logic checks for OV < V<sub>OVHI</sub>, RESET < 0.8V, GATE  $< V_{GATEL}$ , SENSE  $< V_{CB}$ , SS  $< 20 \cdot V_{OS}$  and TIMER < V<sub>TMRL</sub>. When all conditions are met, initial timing starts and the TIMER capacitor is charged by a 5µA current source pull-up. At time point 3, TIMER reaches the  $V_{TMRH}$ threshold and the initial timing cycle terminates. The TIMER capacitor is quickly discharged. At time point 4, the V<sub>TMRI</sub> threshold is reached and the conditions of GATE  $< V_{GATEL}$ , SENSE < V<sub>CB</sub> and SS < 20 • V<sub>OS</sub> must be satisfied before the GATE start-up cycle begins. SS ramps up as dictated by RSS • CSS; GATE is held low by the analog current limit amplifier until SS crosses 20 • V<sub>OS</sub>. Upon releasing GATE, 50µA sources into the external MOSFET gate and compensation network. When the GATE voltage reaches the MOSFET's threshold, current begins flowing into the load capacitor at time point 5. At time point 6, load current reaches SS control level and the analog current limit loop activates. Between time points 6 and 8, the GATE voltage is servoed and the SENSE voltage is regulated at V<sub>ACI</sub> (t) and soft-start limits the slew rate of the load current. If the SENSE voltage ( $V_{SENSE} - V_{EE}$ ) reaches the  $V_{CB}$  threshold at time point 7, the circuit breaker TIMER activates. The TIMER capacitor,  $C_T$  is charged by a (200 $\mu$ A + 8 •  $I_{DRN}$ ) current pull-up. As the load capacitor nears full charge, load current begins to decline. At point 8, the load current falls and the SENSE voltage drops below  $V_{ACI}(t)$ . The analog current limit loop shuts off and the GATE pin ramps further. At time point 9, the SENSE voltage drops below  $V_{CB}$  and the fault TIMER ends, followed by a  $5\mu A$ discharge current source (cool-off). When GATE ramps past V<sub>GATEH</sub> threshold at time point A, PWRGD1 pulls low, starting off the PWRGD sequence. PWRGD2 pulls low at time point C when EN2 is high and PWRGD1 is low for more than one t<sub>SOT</sub>. PWRGD3 pulls low at time point D when EN2 and EN3 is high and PWRGD2 is low for more than one t<sub>SOT</sub>. At time point B, GATE reaches its maximum voltage as determined by V<sub>IN</sub>.

#### **Undervoltage Timing**

In Figure 9 when the UV pin drops below  $V_{UVLO}$  at time point 1, the LTC4253B shuts down with TIMER, SS and GATE pulled low. If current has been flowing, the SENSE pin voltage decreases to zero as GATE collapses. When UV recovers and clears  $V_{UVHI}$  at time point 2, an initial time cycle begins followed by a start-up cycle.

## VIN Undervoltage Lockout Timing

$V_{IN}$  undervoltage lockout comparator, UVLO has a similar timing behavior as the UV pin timing except it looks at  $V_{IN} < (V_{LKO} - V_{LKH})$  to shut down and  $V_{IN} > V_{LKO}$  to start. In an undervoltage lockout condition, both UV and OV comparators are held off. When  $V_{IN}$  exits undervoltage lockout, the UV and OV comparators are enabled.

#### **Overvoltage Timing**

During normal operation, if the OV pin exceeds  $V_{OVHI}$  as shown at time point 1 of Figure 10, the TIMER and PWRGD status are unaffected; SS and GATE pull down; load disconnects. At time point 2, OV recovers and drops below the  $V_{OVLO}$  threshold; GATE start-up begins. If the overvoltage glitch is long enough to deplete the load capacitor, time points 4 through 7 may occur.

### **Circuit Breaker Timing**

In Figure 11a, the TIMER capacitor charges at  $200\mu A$  if the SENSE pin exceeds  $V_{CB}$  but  $V_{DRN}$  is less than 5V. If the SENSE pin returns below  $V_{CB}$  before TIMER reaches the  $V_{TMRH}$  threshold, TIMER is discharged by  $5\mu A$ . In Figure 11b, when TIMER exceeds  $V_{TMRH}$ , GATE pulls down immediately and the chip shuts down. In Figure 11c, multiple momentary faults cause the TIMER capacitor to integrate and reach  $V_{TMRH}$  followed by GATE pull down and the chip shuts down. During chip shutdown, the LTC4253B latches TIMER high with a  $5\mu A$  pull-up current source.

UV DROPS BELOW  $V_{UVLO}$ . Gate, SS and timer are pulled down,  $\overline{PWRGD}$  releases UV CLEARS  $V_{UVHI}$ , CHECK OV CONDITION, RESET < 0.8V, GATE <  $V_{GATEL}$ , SENSE <  $V_{CB}$ , SS < 20 •  $V_{OS}$  AND TIMER <  $V_{TMRL}$ TIMER CLEARS  $V_{TMRL}$ , CHECK GATE <  $V_{GATEL}$ , SENSE <  $V_{CB}$  AND SS < 20 •  $V_{OS}$ 7 89 A B C  $V_{\text{UVHI}}$ U٧  $V_{UVLO}$  $V_{\text{TMRH}}$ 200μA + 8 • I<sub>DRN</sub> TIMER 5μΑ 5μΑ  $V_{\mathsf{TMRL}}$ 5μΑ 50μA  $V_{\text{IN}} - V_{\text{GATEH}}$ GATE 50µA V<sub>GATEL</sub>  $20 \bullet (\mathsf{V}_{\mathsf{ACL}} + \mathsf{V}_{\mathsf{OS}})$ 20 • (V<sub>CB</sub> + V<sub>OS</sub>) 20 • V<sub>OS</sub> SS  $V_{\mathsf{ACL}}$  $V_{CB}$  $V_{DRNCL}$ DRAIN  $V_{DRNL}$ 50μΑ PWRGD1 PWRGD2 PWRGD3 V<sub>SQTMRH</sub> 5μΑ SQTIMER  $V_{\text{SQTMRL}}$ V<sub>SQTMRL</sub> EN2 EN3 GATE INITIAL TIMING -4253b F09

Figure 9. Undervoltage Timing (All Waveforms Are Referenced to V<sub>EE</sub>)