Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## I ECHNOLOGY High Current Hot Swap Controller with I<sup>2</sup>C Compatible Monitoring

## **FEATURES**

- Allows Safe Board Insertion Into Live Backplane

- 12-/16-Bit ADC with ±0.7% Total Unadjusted Error

- Monitors Current, Voltage, Power and Energy

- Controls Two Parallel N-Channel MOSFETs for High Current Applications

- Internal EEPROM for Nonvolatile Configuration

- Wide Operating Voltage Range: 2.9V to 33V

- I<sup>2</sup>C/SMBus Digital Interface (Coexists with PMBus Devices)

- 12V Gate Drive for Lower MOSFET R<sub>DS(ON)</sub>

- Programmable Current Limit with 2% Accuracy

- MOSFET Power Limiting with Current Foldback

- Continuously Monitors MOSFET Health

- Stores Minimum and Maximum Measurements

- Alerts When Alarm Thresholds Exceeded

- Input Overvoltage/Undervoltage Protection

- Three General Purpose Input/Outputs

- Internal ±5% or External Timebases

- 32-Pin 5mm × 5mm QFN Package

## **APPLICATIONS**

- Enterprise Servers and Data Storage Systems

- Network Routers and Switches

- Base Stations

- Platform Management

## DESCRIPTION

The LTC®4282 Hot Swap™ controller allows a board to be safely inserted and removed from a live backplane. Using one or more external N-channel pass transistors, board supply voltage and inrush current are ramped up at an adjustable rate. An I²C interface and onboard ADC allows for monitoring of board current, voltage, power, energy and fault status.

The device features analog foldback current limiting and supply monitoring for applications from 2.9V to 33V. Dual 12V gate drive allows high power applications to either share safe operating area across parallel MOSFETs or support a 2-stage start-up that first charges the load capacitance followed by enabling a low on-resistance path to the load.

The LTC4282 is well suited to high power applications because the precise monitoring capability and accurate current limiting reduce the extremes in which both loads and power supplies must safely operate. Non-volatile configuration allows for flexibility in the autonomous generation of alerts and response to faults.

T, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Patents pending.

## TYPICAL APPLICATION

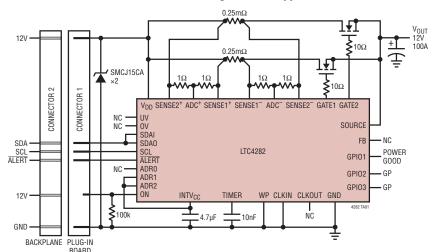

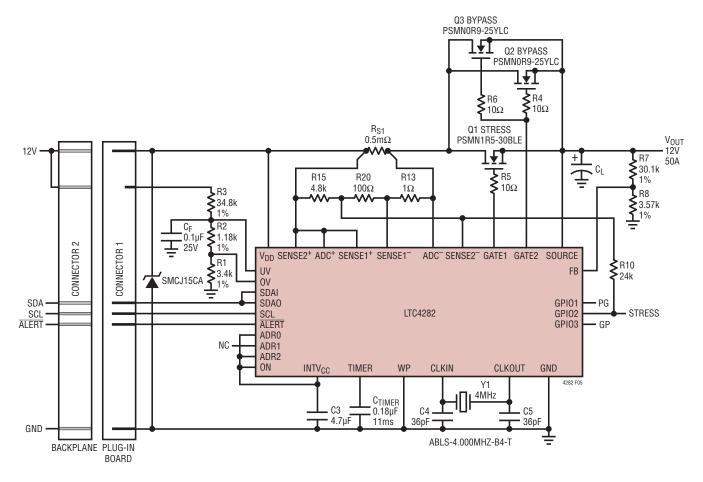

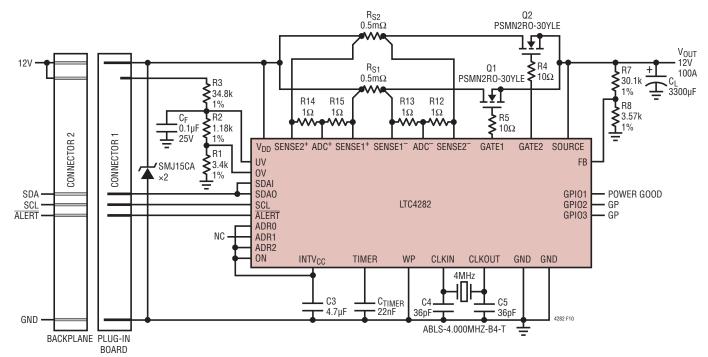

#### 12V, 100A Plug-In Board Application

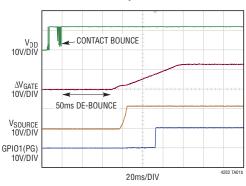

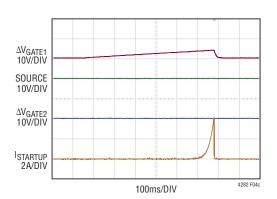

#### Start-Up Waveforms

## **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2)

| Supply Voltage (V <sub>DD</sub> )0.3V to 45V Input Voltages                                   |

|-----------------------------------------------------------------------------------------------|

| GATE <i>n</i> – SOURCE (Note 3) –0.3V to 10V SENSE <i>n</i> <sup>+</sup> , ADC <sup>+</sup> , |

| SENSE1 <sup>-</sup> V <sub>DD</sub> - 4.5V to V <sub>DD</sub> + 0.3V                          |

| SENSE2 <sup>-</sup> , ADC <sup>-</sup> 0.3V to V <sub>DD</sub> + 0.3V                         |

| SOURCE0.3V to 45V                                                                             |

| ADR0-2, TIMER–0.3V to INTV <sub>CC</sub> + 0.3V                                               |

| CLKIN–0.3V to 5.5V                                                                            |

| UV, OV, FB, WP, ON, GPIO1-3,                                                                  |

| SCL, SDAI0.3V to 45V                                                                          |

| Output Voltages                                                                               |

| INTV <sub>CC</sub> 0.3V to 5.5V                                                               |

| GATE1,2, GPI01-3, ALERT, SDA00.3V to 45V                                                      |

| CLKOUT0.3 to INTV <sub>CC</sub> + 0.3V                                                        |

| Output Current INTV <sub>CC</sub> (V <sub>DD</sub> > 4V)25mA                                  |

| Operating Ambient Temperature Range                                                           |

| LTC4282C                                                                                      |

| LTC4282I40°C to 85°C                                                                          |

| Storage Temperature Range65°C to 125°C                                                        |

| otorago romporataro riango minimini oo o to 120 o                                             |

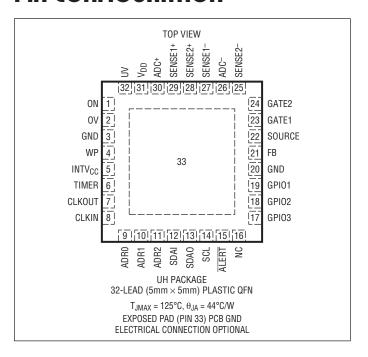

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LTC4282CUH#PBF   | LTC4282CUH#TRPBF | 4282          | 32-Lead (5mm × 5mm) Plastic QFN | 0°C to 70°C       |

| LTC4282IUH#PBF   | LTC4282IUH#TRPBF | 4282          | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{DD} = 12V$ unless otherwise noted.

| tomporatare range, emerines epermeanent are at r <sub>A</sub> = 20 er r <sub>DD</sub> = 121 amose emerines metear |                                                 |                        |   |      |     |      |       |  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|---|------|-----|------|-------|--|

| SYMBOL                                                                                                            | PARAMETER                                       | CONDITIONS             |   | MIN  | TYP | MAX  | UNITS |  |

| Supplies                                                                                                          |                                                 |                        |   |      |     |      |       |  |

| $\overline{V_{DD}}$                                                                                               | Input Supply Range                              |                        | • | 2.9  |     | 33   | V     |  |

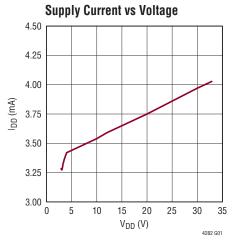

| I <sub>DD</sub>                                                                                                   | Input Supply Current                            |                        | • |      | 3.5 | 8    | mA    |  |

| $V_{\rm DD(UVL)}$                                                                                                 | Input Supply Undervoltage Lockout               | V <sub>DD</sub> Rising | • | 2.65 | 2.7 | 2.75 | V     |  |

| V <sub>DD(HYST)</sub>                                                                                             | Input Supply Undervoltage Lockout<br>Hysteresis |                        | • | 15   | 40  | 75   | mV    |  |

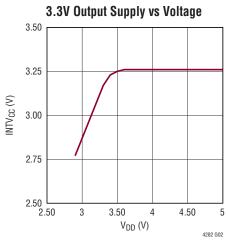

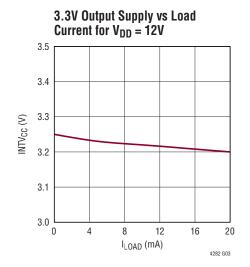

| INTV <sub>CC</sub>                                                                                                | Internal Regulator Voltage                      |                        | • | 3.1  | 3.3 | 3.5  | V     |  |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{DD} = 12 V$ unless otherwise noted.

| SYMBOL                                    | PARAMETER                                                                       | CONDITIONS                                                                                     |   | MIN               | TYP                     | MAX               | UNITS       |

|-------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---|-------------------|-------------------------|-------------------|-------------|

| INTV <sub>CC(UVL)</sub>                   | INTV <sub>CC</sub> Undervoltage Lockout                                         | INTV <sub>CC</sub> Rising                                                                      | • | 2.45              | 2.6                     | 2.7               | V           |

| INTV <sub>CC(HYST)</sub>                  | INTV <sub>CC</sub> Undervoltage Lockout Hysteresis                              |                                                                                                | • | 50                | 110                     | 175               | mV          |

| Current Limit                             | ·                                                                               |                                                                                                |   |                   |                         |                   |             |

| $\Delta V_{SENSE1}$ - $\Delta V_{SENSE2}$ | Offset Between Channel 1 and Channel 2                                          | V <sub>SENSE1,2</sub> <sup>+</sup> = 12V                                                       | • |                   | 0                       | ±0.25             | mV          |

| $\Delta V_{SENSE}$                        | Current Limit Voltage DAC Zero-Scale                                            | V <sub>FB</sub> = 1.3V, I <sub>LIM</sub> = 000<br>V <sub>FB</sub> = 0V, I <sub>LIM</sub> = 000 | • | 12.25<br>3.4      | 12.5<br>3.75            | 12.75<br>4.1      | mV<br>mV    |

|                                           | Current Limit Voltage DAC Full-Scale                                            | V <sub>FB</sub> = 1.3V, I <sub>LIM</sub> = 111<br>V <sub>FB</sub> = 0V, I <sub>LIM</sub> = 111 | • | 32.88<br>8.81     | 34.37<br>10.31          | 35.87<br>11.81    | mV<br>mV    |

|                                           | Current Limit Voltage DAC INL                                                   |                                                                                                | • | -0.05             | 0                       | 0.05              | LSB         |

|                                           | Fast Current Limit Comparator Offset                                            |                                                                                                | • |                   | 0                       | ±15               | mV          |

| I <sub>SENSE</sub> -                      | SENSE <sup>-</sup> Pin Input Current                                            | V <sub>SENSE</sub> <sup>-</sup> = 12V                                                          | • |                   | 0                       | ±1                | μА          |

| I <sub>SENSE</sub> <sup>+</sup>           | SENSE <sup>+</sup> Pin Input Current                                            | V <sub>SENSE</sub> <sup>+</sup> = 12V                                                          | • | 0                 | 45                      | 60                | μА          |

| Gate Drive                                | ,                                                                               |                                                                                                |   |                   |                         |                   |             |

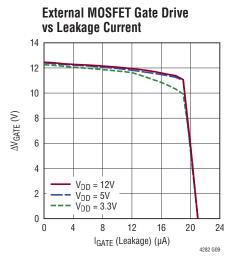

| $\Delta V_{GATE\_OUT}$                    | Gate Drive (V <sub>GATE</sub> – V <sub>SOURCE</sub> ) (Note 3)                  | $V_{DD} = 2.9V \text{ to } 33V, I_{GATE} = -1\mu\text{A}$                                      | • | 10                | 12.5                    | 13.5              | V           |

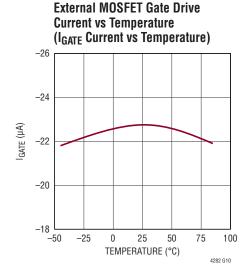

| I <sub>GATE</sub>                         | Gate Pull-Up Current                                                            | Gate On, V <sub>GATE</sub> = 0V                                                                | • | -15               | -20                     | -30               | μА          |

|                                           | Gate Pull-Down Current                                                          | Gate Off, V <sub>GATE</sub> = 10V                                                              | • | 0.5               | 1.3                     | 3                 | mA          |

|                                           | Gate Fast Pull-Down Current                                                     | $\Delta V_{SENSE} = 100 \text{mV}, \ \Delta V_{GATE} = 10 \text{V}$                            |   | 0.3               | 0.6                     | 1.5               | А           |

| t <sub>PHL_FAST</sub>                     | SENSE1,2+-SENSE1,2- Overcurrent to<br>GATE1,2 Low                               | $\Delta V_{SENSE}$ =0mV Step to 100mV, C = 10nF                                                | • |                   | 0.5                     | 1                 | μs          |

| ΔV <sub>GATE TH</sub>                     | ΔV <sub>GATE</sub> FET Off Threshold                                            |                                                                                                | • | 5                 | 8                       | 10                | V           |

| Comparator Inputs                         |                                                                                 |                                                                                                |   |                   |                         |                   |             |

| V <sub>TH-R</sub>                         | V <sub>DD</sub> , SOURCE Rising Threshold Voltages for UV, Power Good           | 5%<br>10%                                                                                      | • | −5<br>−10         | −7.5<br>−12.5           | −10<br>−15        | %<br>%      |

|                                           | (Note 6)                                                                        | 15%                                                                                            | • | -15               | -17.5                   | -20               | %           |

| V <sub>TH-F</sub>                         | V <sub>DD</sub> , SOURCE Falling Threshold Voltages for UV, Power Good (Note 6) | 5%<br>10%<br>15%                                                                               | • | -10<br>-15<br>-20 | -12.5<br>-17.5<br>-22.5 | –15<br>–20<br>–25 | %<br>%<br>% |

| V <sub>TH-R</sub>                         | V <sub>DD</sub> Rising Threshold Voltages for OV (Note 6)                       | 5%<br>10%<br>15%                                                                               | • | 10<br>15<br>20    | 12.5<br>17.5<br>22.5    | 15<br>20<br>25    | %<br>%<br>% |

| V <sub>TH-F</sub>                         | V <sub>DD</sub> Falling Threshold Voltages for OV (Note 6)                      | 5%<br>10%<br>15%                                                                               | • | 5<br>10<br>15     | 7.5<br>12.5<br>17.5     | 10<br>15<br>20    | %<br>%<br>% |

| $\overline{V_{TH}}$                       | UV, OV, FB, ON Rising Threshold                                                 |                                                                                                | • | 1.26              | 1.28                    | 1.3               | V           |

| V <sub>HYST</sub>                         | UV, OV, FB, ON Hysteresis                                                       |                                                                                                | • | 23                | 43                      | 63                | mV          |

| I <sub>IN</sub>                           | UV, OV, FB, ON, WP Input Current                                                | V = 1.2V                                                                                       | • |                   | 0                       | ±1                | μА          |

| V <sub>TH</sub>                           | FET-Bad Fault V <sub>DS</sub> Threshold                                         |                                                                                                | • | 150               | 200                     | 270               | mV          |

| $\overline{V_TH}$                         | WP Threshold Voltage                                                            | Falling                                                                                        | • | 1.26              | 1.28                    | 1.3               | V           |

| V <sub>HYST</sub>                         | WP Hysteresis                                                                   |                                                                                                | • | 2                 | 20                      | 35                | mV          |

| t <sub>PHL</sub>                          | Turn-Off Propagation Delay                                                      | ON, UV, OV Turn Off                                                                            | • | 10                | 25                      | 45                | μs          |

| t <sub>D</sub>                            | Fast Turn-On Propagation Delay                                                  | ON Pin Turn On                                                                                 | • | 10                | 25                      | 45                | μs          |

|                                           | Debounced Turn-On Propagation Delay                                             | UV, OV Pin Turn On                                                                             | • | 45                | 50                      | 55                | ms          |

| Crystal Oscillator Pin                    | Functions                                                                       |                                                                                                |   |                   |                         |                   |             |

| V <sub>TH</sub>                           | CLKIN Rising Threshold                                                          |                                                                                                | • | 0.4               | 1                       | 2                 | V           |

| f <sub>MAX</sub>                          | Maximum CLKIN Pin Input Frequency                                               |                                                                                                | • |                   | ,                       | 25                | MHz         |

| I <sub>CLKIN</sub>                        | CLKIN Input Current                                                             | V = 0V to 3.3V                                                                                 | • | -10               |                         | 10                | μA          |

|                                           |                                                                                 |                                                                                                | _ |                   |                         |                   | <del></del> |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD} = 12V$ unless otherwise noted.

| SYMBOL                     | PARAMETER                                    | CONDITIONS                                                           |   | MIN                | TYP                | MAX                | UNITS    |

|----------------------------|----------------------------------------------|----------------------------------------------------------------------|---|--------------------|--------------------|--------------------|----------|

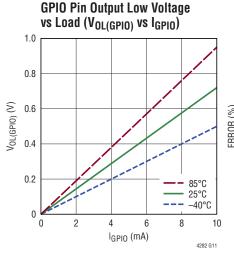

| <b>GPIO</b> Pin Functions  |                                              |                                                                      |   |                    |                    |                    |          |

| $V_{TH}$                   | GPIO, ALERT Threshold                        | Falling                                                              | • | 1.26               | 1.28               | 1.31               | V        |

| V <sub>HYST</sub>          | GPIO, ALERT Hysteresis                       |                                                                      | • | 2                  | 20                 | 35                 | mV       |

| $V_{OL}$                   | GPIO, ALERT Output Low Voltage               | I = 3mA                                                              | • |                    | 0.3                | 0.4                | V        |

| I <sub>OH</sub>            | GPIO, ALERT Leakage Current                  | V = 33V                                                              | • |                    | 0                  | ±1                 | μА       |

| t <sub>PHL_GPI02</sub>     | Stress Condition to GPIO2 Low Propagation    | GATE Low or V <sub>DS</sub> = 1V                                     | • | 5                  | 13                 | 30                 | μs       |

| TIMER Pin Functions        |                                              |                                                                      |   |                    |                    |                    |          |

| V <sub>TH</sub>            | TIMER Low Threshold                          | Falling                                                              | • | 0.11               | 0.15               | 0.19               | V        |

|                            | TIMER High Threshold                         | Rising                                                               | • | 1.25               | 1.28               | 1.31               | V        |

| I <sub>TIMER</sub>         | TIMER Pull-Up Current                        | V = 0V                                                               | • | -18                | -20                | -22                | μA       |

|                            | TIMER Pull-Down Current                      | V = 1.3V                                                             | • | 3                  | 5                  | 7                  | μA       |

| D <sub>OC</sub>            | Overcurrent Auto-Retry Duty Cycle            |                                                                      | • | 0.045              | 0.08               | 0.11               | %        |

| SOURCE, ADC Pin Cu         | rrents                                       |                                                                      |   |                    |                    |                    |          |

| I <sub>SOURCE</sub>        | SOURCE Input Current                         | V = 12V                                                              | • | 70                 | 180                | 350                | μA       |

| I <sub>ADC</sub> -         | ADC <sup>-</sup> Input Current               | V = 33V                                                              | • |                    | 0                  | ±1                 | μA       |

| I <sub>ADC</sub> +         | ADC+ Input Current                           | V = 33V                                                              | • |                    | 25                 | 110                | μA       |

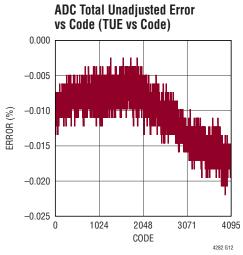

| ADC                        | Resolution (No Missing Codes)                |                                                                      |   | 12/16              |                    |                    | Bits     |

| $V_{OS}$                   | ADC Offset Error, Percent of Full-Scale      |                                                                      | • |                    |                    | ±0.25              | %        |

| TUE                        | ADC Total Unadjusted Error (Note 5)          | ΔV <sub>ADC</sub> , SOURCE, V <sub>DD</sub> , GPIO                   | • |                    |                    | ±0.7               | %        |

|                            |                                              | POWER ENERGY (Internal Timebase)                                     |   |                    |                    | ±1.0<br>±5.1       | %<br>%   |

|                            |                                              | ENERGY (Crystal/External Timebase)                                   |   |                    |                    | ±5.1<br>±1.0       | /º<br>%  |

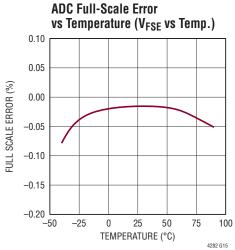

| FSE                        | ADC Full-Scale Error                         | ΔV <sub>ADC</sub> , SOURCE, V <sub>DD</sub> , GPIO                   | • |                    | 1                  | ±0.7               | %        |

|                            |                                              | POWER                                                                | • |                    |                    | ±1.0               | %        |

|                            |                                              | ENERGY (Internal Timebase) ENERGY (Crystal/External Timebase)        |   |                    |                    | ±5.1<br>±1.0       | %<br>%   |

| $\overline{V_{FS}}$        | ADC Full-Scale Range                         | ΔV <sub>ADC</sub>                                                    | + |                    | 40                 |                    | mV       |

| • 13                       | 7.50 Fair Goale Hange                        | SOURCE/V <sub>DD</sub> 24V Range                                     |   |                    | 33.28              |                    | V        |

|                            |                                              | SOURCE/V <sub>DD</sub> 12V Range                                     |   |                    | 16.64              |                    | V        |

|                            |                                              | SOURCE/V <sub>DD</sub> 5V Range<br>SOURCE/V <sub>DD</sub> 3.3V Range |   |                    | 8.32<br>5.547      |                    | V<br>V   |

|                            |                                              | GPIO                                                                 |   |                    | 1.28               |                    | v        |

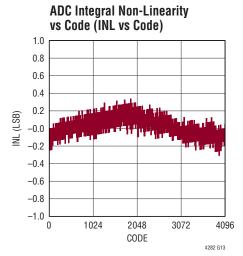

| INL                        | ADC Integral Nonlinearity, 12-Bit Mode       |                                                                      | • |                    | 0.2                | 5                  | LSB      |

| V <sub>FS</sub>            | Alarm Threshold Full-Scale Range             | $\Delta V_{ADC}$                                                     |   |                    | 40                 |                    | mV       |

|                            | (256 • V <sub>LSB</sub> )                    | SOURCE/V <sub>DD</sub> 24V Range<br>SOURCE/V <sub>DD</sub> 12V Range |   |                    | 33.28<br>16.64     |                    | V<br>V   |

|                            |                                              | SOURCE/V <sub>DD</sub> 5V Range                                      |   |                    | 8.32               |                    | v        |

|                            |                                              | SOURCE/V <sub>DD</sub> 3.3V Range                                    |   |                    | 5.547              |                    | V        |

|                            |                                              | GPIO                                                                 |   |                    | 1.28               |                    | V        |

| R <sub>GPIO</sub>          | GPIO ADC Sampling Resistance                 | V = 1.28                                                             | • | 1                  | 2                  |                    | MΩ       |

| $f_{CONV} = 1/t_{CONV}$    | Conversion Rate, All ADC Channels            | 12-Bit Mode, Internal Clock<br>16-Bit Mode, Internal Clock           |   | 14.5<br>0.906      | 15.26<br>0.954     | 16<br>1            | Hz<br>Hz |

| I <sup>2</sup> C Interface |                                              | TO-DIL Wode, Internal Glock                                          |   | 0.300              | 0.334              | 1                  | 112      |

| V <sub>ADR(H)</sub>        | ADR <i>n</i> Input High Threshold            |                                                                      |   | INTV <sub>CC</sub> | INTV <sub>CC</sub> | INTV <sub>CC</sub> | ΙV       |

| VAUK(H)                    | 7,5117 input riigii riiiosiiolu              |                                                                      |   | - 0.8              | - 0.5              | - 0.2              |          |

| V <sub>ADR(L)</sub>        | ADR <i>n</i> Input Low Threshold             |                                                                      | • | 0.2                | 0.5                | 0.8                | V        |

| I <sub>ADR(IN)</sub>       | ADR <i>n</i> Input Current                   | ADR = 0V, ADR = INTV <sub>CC</sub>                                   | • |                    | -                  | ±80                | μА       |

| I <sub>ADR(IN,Z)</sub>     | ADR <i>n</i> Allowable Leakage in Open State |                                                                      | • |                    |                    | ±3                 | μA       |

| V <sub>SDA,SCL(TH)</sub>   | SDAI, SCL Input Threshold                    |                                                                      | • | 1.5                | 1.7                | 2.0                | V        |

|                            | ·                                            |                                                                      |   |                    |                    |                    | 4282f    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{DD} = 12V$ unless otherwise noted.

| SYMBOL                            | PARAMETER                                       | CONDITIONS                     |   | MIN    | TYP  | MAX | UNITS  |

|-----------------------------------|-------------------------------------------------|--------------------------------|---|--------|------|-----|--------|

| I <sub>SDA,SCL(OH)</sub>          | SDAI, SCL Input Current                         | SCL, SDA = 5V                  | • |        |      | ±1  | μА     |

| V <sub>SDAO(OL)</sub>             | SDAO Output Low Voltage                         | I = 3mA                        | • |        | 0.3  | 0.4 | V      |

| I <sub>SDAO(OH)</sub>             | SDAO Pin Input Leakage Current                  | V <sub>SDAO</sub> = 33V        | • |        | 0    | ±1  | μА     |

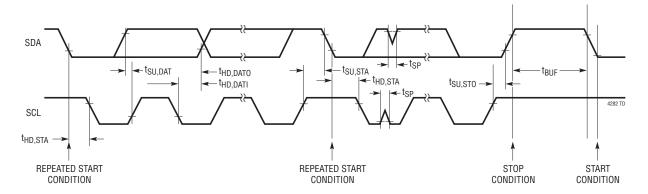

| I <sup>2</sup> C Interface Timing | ]                                               |                                |   |        |      |     |        |

| f <sub>SCL(MAX)</sub>             | Maximum SCL Clock Frequency                     |                                | • | 400    | 1000 |     | kHz    |

| t <sub>BUF(MIN)</sub>             | Bus Free Time Between START and STOP Conditions |                                | • |        | 0.12 | 1.3 | μѕ     |

| t <sub>HD,STA(MIN)</sub>          | Hold Time After (Repeated) START Condition      |                                | • |        | 30   | 600 | μs     |

| t <sub>SU,STA(MIN)</sub>          | Repeated START Condition Set-Up Time            |                                | • |        | 30   | 600 | ns     |

| t <sub>SU,STO(MIN)</sub>          | STOP Condition Set-Up Time                      |                                | • |        | 140  | 600 | ns     |

| t <sub>HD,DATI(MIN)</sub>         | Data Hold Time (Input)                          |                                | • |        | 30   | 100 | ns     |

| t <sub>HD,DATO</sub>              | Data Hold Time (Output)                         |                                | • | 300    | 500  | 900 | ns     |

| t <sub>SU,DAT(MIN)</sub>          | Data Set-Up Time                                |                                | • |        | 30   | 600 | ns     |

| t <sub>SP(MAX)</sub>              | Suppressed Spike Pulse Width Maximum            |                                | • | 50     | 110  | 250 | ns     |

| $\overline{C_X}$                  | SCL, SDA Input Capacitance                      | (Note 4)                       | • |        |      | 10  | pF     |

| t <sub>D-STUCK</sub>              | I <sup>2</sup> C Stuck Bus Timeout              |                                | • | 25     | 30   | 35  | ms     |

| EEPROM Characteri                 | stics                                           |                                | · |        |      |     |        |

| Endurance                         |                                                 | 1 Cycle = 1 Write (Notes 7, 8) | • | 10,000 |      |     | Cycles |

| Retention                         |                                                 | (Notes 7, 8)                   | • | 20     |      |     | Years  |

| t <sub>WRITE</sub>                | Write Operation Time                            |                                | • | 1      | 2.2  | 4   | ms     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive. All voltages are referenced to GND unless otherwise specified.

**Note 3:** An internal clamp limits the GATE pin to a minimum of 10V above SOURCE. Driving this pin to voltages beyond the clamp may damage the device.

Note 4: Guaranteed by design and not subject to test.

**Note 5:** TUE is the maximum ADC error for any code, given as a percentage of full scale.

**Note 6:** UV, OV and FB internal thresholds are given as a percent difference from the configured operating voltage.

**Note 7:** EEPROM endurance and retention are guaranteed by design, characterization and correlation with statistical process controls.

**Note 8:** EEPROM endurance and retention will be degraded when  $T_J > 85$ °C.

## **TIMING DIAGRAM**

4282

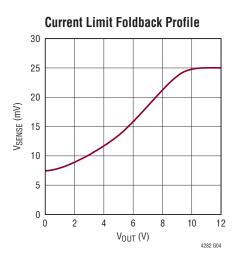

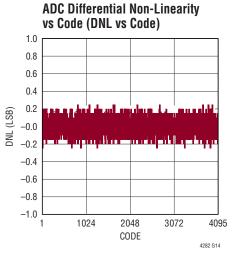

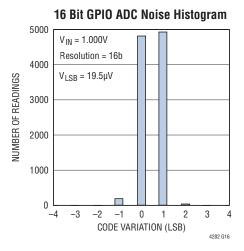

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{DD} = 12V$ unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

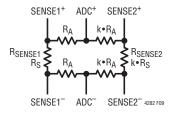

**ADC+:** Positive Kelvin ADC Current Sense Input. Use a resistive divider between the two SENSE+ pins to measure the average of the two SENSE+ voltages. Tie to SENSE1+ when using a single sense resistor. Must be connected to the same trace as  $V_{DD}$  or a resistive averaging network which adds up to  $1\Omega$  to  $V_{DD}$ .

**ADC**<sup>-</sup>: Negative Kelvin ADC Current Sense Input. Use a resistive divider between the two SENSE<sup>-</sup> pins to measure the average of the two SENSE<sup>-</sup> voltages. Tie to SENSE1<sup>-</sup> when using a single sense resistor.

**ADR0-ADR2:** Serial Bus Address Inputs. Tying these pins to ground (L), open (NC), or INTV $_{CC}$  (H) configures one of 27 possible addresses. See Table 1 in Applications Information.

ALERT: I<sup>2</sup>C Bus ALERT Output or General Purpose Input/ Output. Configurable to ALERT output, general purpose output or logic input. Tie to ground if unused.

**CLKIN:** Clock Input. Connect to an optional external crystal oscillator circuit or drive with an external clock. Connect to ground if unused.

**CLKOUT:** Clock Output. Connect to an optional external crystal oscillator circuit. Can be configured in non-volatile memory to output the internal clock or a low pulse when the ADC finishes a conversion. Float if unused.

**FB:** Foldback Current Limit and Power Good Input. A resistive divider from the output is tied to this pin. When the voltage at this pin drops below 1.28V, power is not considered good. The power bad condition may result in the GPIO1 pin pulling low or going high impedance depending on the configuration of GPIO\_CONFIG register 0x07 bits 4 and 5, also a power bad fault is logged in this condition if the GATE pin is high. The start-up current limit folds back to 30% as the FB pin voltage drops from 1.3V to 0V.

**GATE1**, **GATE2**: Gate Drives for External N-Channel MOSFETs. Internal 20μA current sources charge the gates of the MOSFETs. No compensation capacitors are required on the GATE pins, but a resistor and capacitor network from these pins to ground may be used to set the turn-on output voltage slew rate. During turn-off there is a 1mA pull-down current. During a short-circuit or undervoltage lockout (V<sub>DD</sub> or INTV<sub>CC</sub>), a 600mA pull-down between GATE1/GATE2 and SOURCE is activated. Tie both GATE pins together if only one MOSFET is used and SENSE2<sup>-</sup> is grounded.

**GND:** Device Ground.

**GPI01:** General Purpose Input/Open-Drain Output. Configurable to general purpose output, logic input, and power good or power bad signal. Tie to ground if unused.

**GPI02:** General Purpose Input/Open-Drain Output. Configurable to general purpose output, logic input, MOSFET stress output, and data converter input. Tie to ground if unused.

**GPIO3:** General Purpose Input/Open-Drain Output. Configurable to general purpose output, logic input, and data converter input. Tie to ground if unused.

**INTV**<sub>CC</sub>: 3.3V Supply Decoupling Output. Connect a 1 $\mu$ F capacitor from this pin to ground. To ensure fault logging after power is lost a 4.7 $\mu$ F capacitor should be used. 25mA may be drawn from this pin to power 3.3V application circuitry. Increase capacitance by 1 $\mu$ F/mA external load when fault logging is used. This pin should not be driven and is not current limited.

NC: No Connect.

**ON:** On Control Input. Used to monitor a connection sense pin on the backplane connector. The default polarity is high = on, but may be reconfigured to low = on by setting CONTROL1 register 0x00 bit 5 low. An on-to-off transition on this pin clears the fault register if CONTROL1 register 0x00 bit 7 is set high. The ON pin has a precise 1.28V threshold, allowing it to double as a supply monitor.

LINEAR

## PIN FUNCTIONS

**OV:** Overvoltage Input Pin. An overvoltage condition is present whenever this pin is above the configured threshold. Connect a resistive divider when the internal divider is disabled, otherwise leave open.

**SCL:** Serial Bus Clock Input. Data at the SDA pin is shifted in or out on rising edges of SCL. This is a high impedance pin that is driven by an open-drain output from a master controller. An external pull-up resistor or current source is required.

**SDAI:** Serial Bus Data Input. A high impedance input for shifting in address, command or data bits. Normally tied to SDAO to form the SDA line.

**SDAO:** Serial Bus Data Output. Open-drain output for sending data back to the master controller or acknowledging a write operation. Normally tied to SDAI to form the SDA line. An external pull-up resistor or current source is required.

**SENSE1+, SENSE2+:** Positive Kelvin Current Sense Input. Connect this pin to the input side of the current sense resistor or an averaging network in the case of multiple sense resistors. The parallel resistance of an averaging network should not exceed  $1\Omega$ . Must operate at the same potential as  $V_{DD}$ .

**SENSE1**<sup>-</sup>, **SENSE2**<sup>-</sup>: Negative Kelvin Current Sense Input. Connect this pin to the output side of the current sense resistor. The current limit circuit controls the GATE pin to limit the sense voltage between the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins to the value selected in the ILIM register or less. Tie SENSE2<sup>-</sup> to GND when unused.

**SOURCE:** N-Channel MOSFET Source and ADC Input. Connect this pin to the source of the external N-channel MOSFET. This pin provides a return for the GATE pull-down circuit and also serves as the ADC input to monitor the output voltage.

**TIMER:** Current Limit and Retry Timer Input. Connect a capacitor between this pin and ground to set a 64ms/μF duration for current limit, after which an overcurrent fault is logged and GATE is pulled low. The duration of the off time is 73s/μF when overcurrent auto-retry is enabled, resulting in a 0.08% duty cycle.

**UV:** Undervoltage Input Pin. Connect a resistive divider when the internal divider is disabled. A capacitor may be placed on this pin to filter brief UV glitches on the input supply.

**V<sub>DD</sub>:** Supply Voltage Input and UV/OV Input. This pin has an undervoltage lockout threshold of 2.7V. The UV and OV thresholds are also measured at this pin, and the ADC may be configured to read the voltage at this pin.

**WP:** EEPROM Write Protect. All writes to the EEPROM except fault logging are blocked when WP is high.

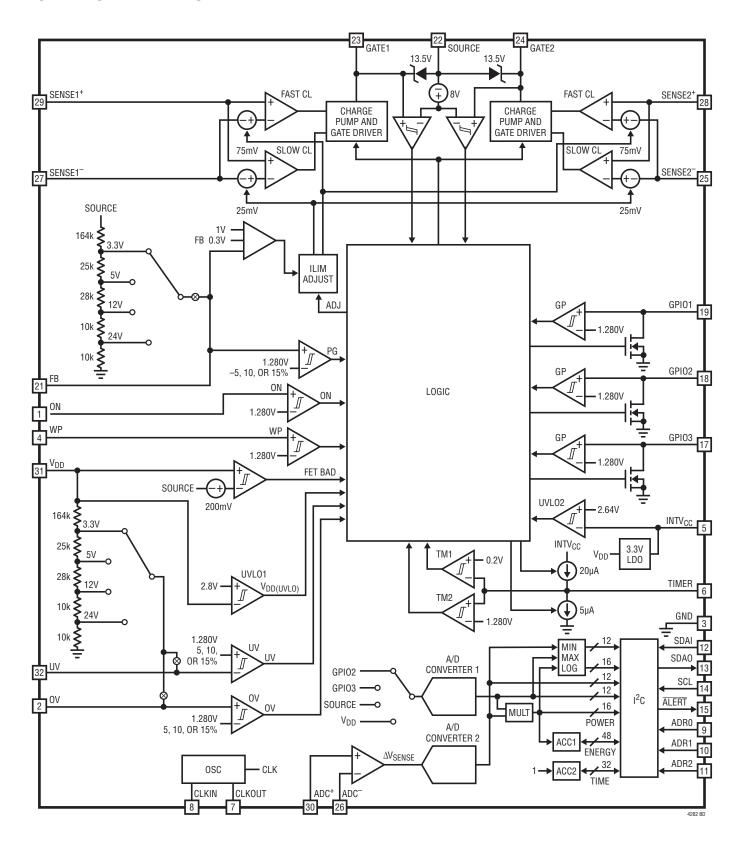

## **FUNCTIONAL DIAGRAM**

## **OPERATION**

The LTC4282 is designed to turn a board's supply voltage on and off in a controlled manner, allowing the board to be safely inserted or removed from a live backplane. During normal operation, the gate drivers turn on a pair of parallel external N-channel MOSFETs to pass power to the load. The gate driver charge pumps derive their power from the  $V_{DD}$  pin. Also included in the gate drivers are 12.5V GATE-to-SOURCE clamps to protect the oxide of external MOSFETs. During start-up the inrush current is tightly balanced and controlled by using current limit foldback.

Two MOSFETs are used to double the SOA and halve the R<sub>DS(ON)</sub> as compared to a single MOSFET. The current limit (CL) amplifiers monitor the load current with current sense resistors connected between the SENSE1+, SENSE2+ and SENSE1-, SENSE2- pins. The CL amplifiers limit the current in the load by pulling back on the GATE-to-SOURCE voltages in an active control loop when the sense voltages exceed the commanded value.

An overcurrent fault at the output may result in excessive MOSFET power dissipation during active current limiting. To limit this power, the CL amplifiers regulate the voltage between the SENSE1+, SENSE2+ and SENSE1-, SENSE2-pins at the value set in the ILIM register. When the output (SOURCE pin) is low, power dissipation is further reduced by folding back the current limit to 30% of nominal.

The TIMER pin ramps up with  $20\mu A$  when both current limit circuits are active. The LTC4282 turns off both GATEs and registers a fault when the TIMER pin reaches its 1.28V threshold. At this point the TIMER pin ramps down using a  $5\mu A$  current source until the voltage drops below 0.2V (comparator TM1). The TIMER pin will then ramp up and down 256 times with  $20\mu A/5\mu A$  before indicating that the external MOSFET has cooled and it is safe to turn on again, provided overcurrent auto-retry is enabled.

The output voltage is monitored using the SOURCE pin and the power good (PG) comparator to determine if the power is available for the load. The power good condition can be signaled by the GPIO1 pin. The GPIO1 pin may also be configured to signal power bad, as a general purpose input (GP comparator), or a general purpose open-drain output.

GPIO2 and GPIO3 may also be configured as general purpose inputs or general purpose open-drain outputs. Additionally the ADC measures these pins with a 1.28V full-scale. GPIO2 may be configured to pull low to indicate that the external MOSFETs are in a state of stress when the MOSFETs are commanded to be on and either the gate voltages are lower than they should be, or the drain-to-source voltage exceeds 200mV.

The Functional Diagram shows the monitoring blocks of the LTC4282. The group of comparators on the left side includes the undervoltage (UV), overvoltage (OV), and (ON) comparators. These comparators determine if the external conditions are valid prior to turning on the GATEs. But first the two undervoltage lockout circuits, UVLO1 and UVLO2, validate the input supply and the internally generated 3.3V supply, INTV<sub>CC</sub>. UVLO2 also generates the power-up initialization to the logic circuits and copies the contents of the EEPROM to operating memory after INTV<sub>CC</sub> crosses this rising threshold.

Included in the LTC4282 is a pair of 12-/16-bit A/D converters. One data converter continuously monitors the ADC+ to ADC- voltage, sampling every 16µs and producing a 12-bit result of the average current sense voltage every 65ms. The other data converter is synchronized to the first one and measures the GPIO voltage and SOURCE voltage during the same time period. Every time the ADCs finish taking a measurement, the current sense voltage is multiplied by the measurement of the SOURCE pin to provide a power measurement. Every time power is measured, it is added to an energy accumulator which keeps track of how much energy has been transmitted to the load. The energy accumulator can generate an optional alert upon overflow, and can be pre-set to allow it to overflow after a given amount of energy has been transmitted. A time accumulator also keeps track of how many times the power meter has been incremented; dividing the results of the energy accumulator by the time accumulator gives the average system power. The minimum and maximum measurements of GPIO, SOURCE, ADC+ to ADC- and power are stored, and optional alerts may be generated if a measurement is above or below user configurable 8-bit thresholds.

## **OPERATION**

An internal EEPROM provides nonvolatile configuration of the LTC4282's behavior, records fault information and provides 4 bytes of uncommitted memory for general purpose storage.

An I<sup>2</sup>C interface is provided to read the A/D data registers. It also allows the host to poll the device and determine

if faults have occurred. If the  $\overline{ALERT}$  pin is configured as an  $\overline{ALERT}$  interrupt, the host is enabled to respond to faults in real time. The I<sup>2</sup>C device address is decoded using the ADR0-ADR2 pins. These inputs have three states each that decode into a total of 27 device addresses, as shown in Table 1.

## APPLICATIONS INFORMATION

A typical LTC4282 application is a high availability system in which a positive voltage supply is distributed to power individual hot-swapped cards. The device measures card voltages and currents and records past and present fault conditions. The LTC4282 stores min and max ADC measurements, calculates power and energy, and can be configured to generate alerts based on measurement results, avoiding the need for the system to poll the device on a regular basis. The LTC4282 is configured with nonvolatile EEPROM memory, allowing it to be configured during board level testing and avoid having to configure the Hot Swap controller at every insertion.

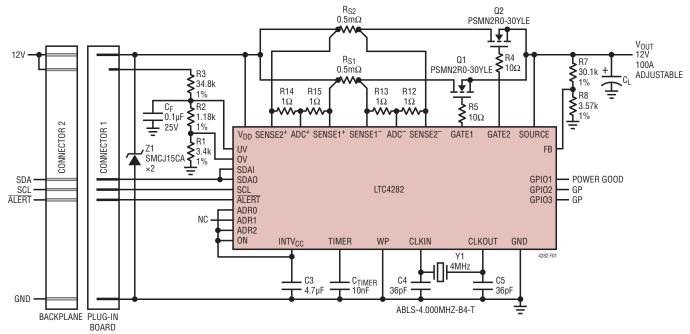

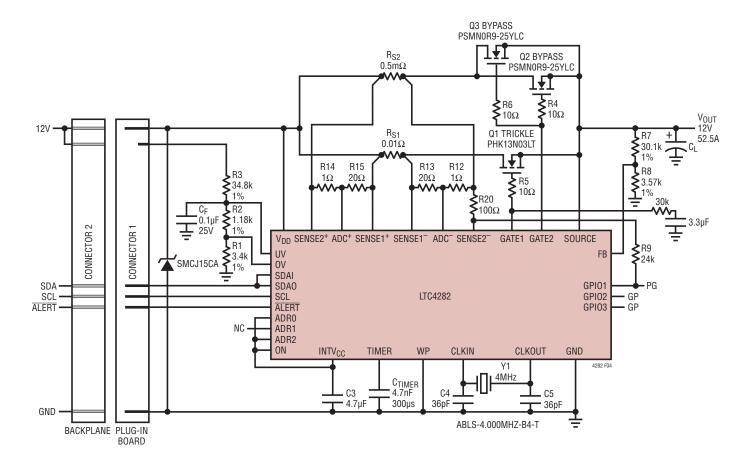

A basic LTC4282 application circuit is shown in Figure 1. The following sections cover turn-on, turn-off and various

faults that the LTC4282 detects and acts upon. External component selection is discussed in detail in the Design Example section.

#### **Turn-On Sequence**

The power supply on a board is controlled by using a pair of N-channel pass transistors, Q1 and Q2, placed in the power path. Resistors  $R_{S1}$  and  $R_{S2}$  sense current through Q1 and Q2. Resistors R12 to R15 provide a weighted average of the two sense voltages for ADC measurements. Resistors R1, R2 and R3 define undervoltage and overvoltage levels. R4 and R5 prevent high frequency self-oscillations in Q1 and Q2. Capacitors C4 and C5 form a resonator network with crystal Y1 to provide an accurate time base.

Figure 1. Typical Application

Several conditions must be present before the external MOSFET turns on. First the external supply,  $V_{DD}$ , must exceed its 2.7V undervoltage lockout level. Next the internally generated supply, INTV<sub>CC</sub>, must cross its 2.6V undervoltage threshold. This generates a 1ms power-on-reset pulse. During reset the fault registers are cleared and the control registers are loaded with the data held in the corresponding EEPROM registers.

After a power-on-reset pulse, the UV and OV pins verify that input power is within the acceptable range. The state of the UV and OV comparators is indicated by STATUS register 0x1E bits 1 and 2 and must be stable for at least 50ms to qualify for turn-on. The ON pin is checked to see that a connection sense ("short") pin has asserted to the correct state. By default the ON pin has no delay, but a 50ms de-bounce delay may be added by setting CON-TROL register 0x00 bit 6 high. When these conditions are satisfied, turn-on is initiated. Figure 7 shows connection sense configurations for both high- and low-going short pins. The ON pin has a precise 1.28V threshold, allowing it to also monitor a voltage through the short pin, such as a house-keeping or auxiliary supply delivered by the backplane. Use of the UV/OV divider for short pin detection in high current applications is not recommended, as voltage drops in the connector and fuse will impair the accuracy of the intended function.

The MOSFETs are then turned on by charging up the GATE pins with  $20\mu A$  current sources. When the GATE pin voltage reaches the MOSFET threshold voltage, the MOSFET begins to turn on and the SOURCE voltage then follows the GATE voltages as it increases.

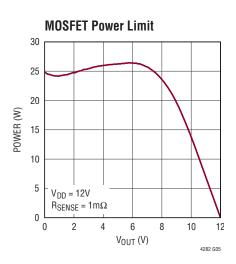

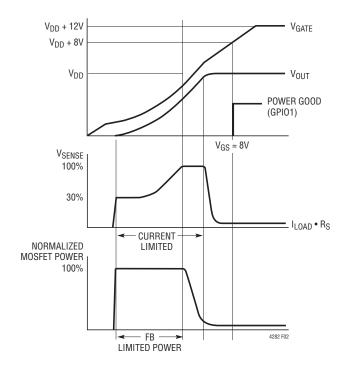

While the MOSFETs are turning on, the power dissipation in current limit for each MOSFET is limited to a fixed value by the foldback profile as shown in Figure 2. As the SOURCE voltage rises, the FB pin follows as set by R7 and R8. Once one of the GATE pins crosses its 8V  $V_{\rm GATE}$  threshold and the FB pin has exceeded its 1.28V threshold, the GPIO1 pin (in its power-good configuration) releases high to indicate power is good and the load may be activated.

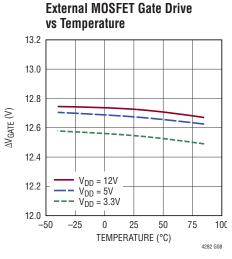

At the minimum input supply voltage of 2.9V, the minimum GATE-to-SOURCE drive voltage is 10V. The GATE-to-SOURCE voltage is clamped below 13.5V to protect the gates of 20V N-channel MOSFETs. A curve of

Figure 2. Power-Up Waveforms

GATE-to-SOURCE drive ( $\Delta V_{GATE}$ ) versus  $V_{DD}$  is shown in the Typical Performance Characteristics.

#### **Turn-Off Sequence**

A normal turn-off sequence is initiated by card withdrawal when the backplane connector short pin opens, causing the ON pin to change state. Turn-off may be also initiated by writing a 0 to control register 0x00 bit 3. Additionally, several fault conditions turn off the GATE pins. These include an input overvoltage, input undervoltage, overcurrent or FET-BAD fault. Setting high any of the UV, OV, OC or FET-BAD fault bits 0-2 and 6 of the FAULT\_LOG register 0x04, also latches off the GATE pins if the associated auto-retry bits are set low.

The MOSFETs are turned off with 1mA currents pulling down the GATE pins to ground. With the MOSFET turned off, the SOURCE and FB voltages drop as the load capacitance discharges. When the FB voltage crosses below its threshold, GPIO1 pulls low to indicate that the output power is no longer good if configured to indicate power good. If the  $V_{DD}$  pin falls below 2.6V for greater than 2µs or INTV<sub>CC</sub> drops below 2.49V for greater than 2µs, a fast shut down of the MOSFET is initiated. The GATE pins are then pulled down with 600mA currents to the SOURCE pin.

#### **Current Limit Adjustment**

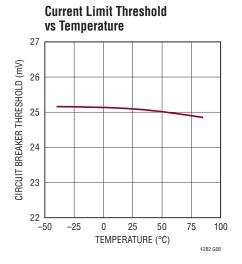

The current limit sense voltage of the LTC4282 is adjustable between 12.5mV and 34.4mV in 3.1mV steps via the I<sup>2</sup>C interface with bits 7-5 of the ILIM ADJUST register 0x11. Default values are stored in the onboard EEPROM. This can be used to adjust the sense voltage to achieve a given current limit using the limited selection of standard sense resistor values available around  $1 \text{m}\Omega$ . It also allows the LTC4282 to reduce available current for light loads or increase it in anticipation of a surge. This feature also enables the use of board-trace as sense resistors by trimming the sense voltage to match measured copper resistance during final test. The measured copper resistance may be written to the undedicated scratch pad area of the EEPROM so that it is available to scale ADC current measurements.

## **Current Limit Stability**

For most applications the LTC4282 current limit loop is stable without additional components. However there are certain conditions where additional components may be needed to improve stability. The dominant pole of the current limit circuit is set by the capacitance at the gate of the external MOSFET, and larger gate capacitance makes the current limit loop more stable. Usually a total of 8nF GATE-to-SOURCE capacitance is sufficient for stability and is provided by inherent MOSFET C<sub>GS</sub>. The stability of the loop is degraded by reducing the size of the resistor on a gate RC network if one is used, which may necessitate additional GATE-to-SOURCE capacitance. Board level short-circuit testing is highly recommended as board layout can also affect transient performance. The worstcase condition for current limit stability occurs when the output is shorted to ground after a normal start-up.

#### Parasitic MOSFET Oscillations

Not all circuit oscillations can be ascribed to the current limit loop. Some higher frequency oscillations can arise from the MOSFETs themselves. There are two possible parasitic oscillation mechanisms. The first type of oscillation occurs at high frequencies, typically above 1MHz. This high frequency oscillation is easily damped with gate resistors R4 and R5 as shown in Figure 1. In some applications, one may find that these resistors help in short-circuit transient recovery as well. However, too large of a resistor will slow down the turn-off time. The recommended R4 and R5 range is between  $5\Omega$  and  $500\Omega$ .  $10\Omega$ provides stability without affecting turn-off time. These resistors must be located at the MOSFET package with no other components connected to the MOSFET gate pin.

A second type of parasitic oscillation occurs at frequencies between 200kHz and 800kHz when the MOSFET source is loaded with less than 10µF, and the drain is fed with an inductive impedance such as contributed by wiring inductance. To prevent this second type of oscillation load the source with more than 10µF and bypass the input supply with a series  $10\Omega$ , 100nF snubber to ground.

#### **Overcurrent Fault**

The LTC4282 features an adjustable current limit with foldback that protects the MOSFETs from excessive load current. To protect the MOSFETs during active current limit, the available current is reduced as a function of the output voltage sensed by the FB pin such that the power dissipated by the MOSFET is constant. A graph in the Typical Performance Characteristics shows the current limit and power versus FB voltage.

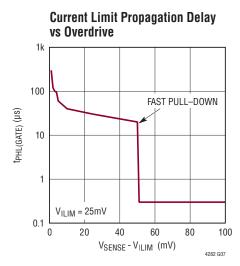

An overcurrent fault occurs when the current limit circuitry has been engaged for both MOSFETs for longer than the timeout delay set by the TIMER capacitor. Current limiting begins when the current sense voltage between the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins reaches the current limit level (which depends on foldback and the current limit configuration). The corresponding GATE pin is then pulled down and regulated in order to limit the current sense voltage to the current limit value. If this is only happening with one GATE, the other MOSFET is still low impedance and is allowed to carry additional current. When both GATE pins are regulated in current limit, the circuit breaker time delay starts by charging the external timer capacitor from the TIMER pin with a 20µA pull-up current. If the TIMER pin reaches its 1.28V threshold, the external switches turn off with 1mA currents from GATE to ground. If one of the GATE pins stops current limiting before the TIMER pin reaches the 1.28V threshold, the TIMER pin will discharge with 5μA. For a given circuit breaker time delay, t<sub>CB</sub>, the equation for setting the timing capacitor's value is as follows:

$C_T = t_{CB} \cdot 0.016 [\mu F/ms]$

If an overcurrent fault is detected the MOSFET is turned off and the TIMER pin begins discharging with a  $5\mu$ A pull-down current. When the TIMER pin reaches its 0.15V threshold, it will cycle up and down with  $20\mu$ A and  $5\mu$ A 256 times to allow the MOSFETs time to cool down. When automatically retrying, the resulting overcurrent duty cycle is 1:1140. The final time the TIMER pin falls below its 0.14V lower threshold the switches are allowed to turn on again if the overcurrent auto-retry bit is set or the overcurrent fault bit has been reset by the  $I^2$ C interface.

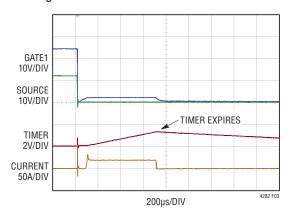

The waveform in Figure 3 shows how the output turns off following a short circuit.

Figure 3. Short-Circuit Waveform

#### **Advantages of Dual Gate Drivers**

The LTC4282 features two gate drivers to improve SOA performance of power MOSFETs in high current applications. Often high current applications feature several MOSFETs in parallel to reach a target  $R_{DS(ON)}$  under  $1m\Omega$  that is unavailable in a single MOSFET. In such cases several parallel sense resistors are also used to get small values that are not available as a single resistor. Further, by dividing the load current amongst multiple devices, the PCB current crowding attendant with the use of a single MOSFET is alleviated.

Parallel MOSFETs share current well when their GATE-to-SOURCE voltages are fully enhanced, however when the MOSFETs are limiting current the offset mismatch between gate thresholds will cause the MOSFET with the lowest threshold to carry more current than the others. As this MOSFET gets hot it carries even more current since threshold voltage has a negative temperature coefficient.

Eventually all the load current may be carried by a single MOSFET. For this reason, when a group of MOSFETs are operated in parallel they only provide SOA of a single MOSFET.

The second current limit circuit on the LTC4282 allows a group of parallel MOSFETs to be divided into two banks. During current limiting the independent gate control of the two banks divides the current evenly between them, resulting in twice the SOA performance of a Hot Swap controller with a single current limit circuit. This allows the use of smaller, less expensive MOSFETs, gives it the capability to start up a load twice as big, or makes the design easier with respect to SOA due to increased margins.

The two GATE driver circuits also allow the two banks of MOSFETs to be started up in a staged manner. There are two architectures for doing this, the first is called 'low stress staged start' and the second is called 'high stress staged start'.

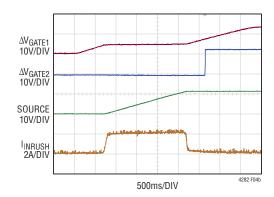

Figure 4 shows an example of low stress staged start, where the power-good signal is used to hold GATE2 off until GATE1 has powered up the load. The start-up trickle MOSFET Q1 is a compact, inexpensive device with small SOA and is configured for a low current limit with a GATE capacitor to limit inrush current. When the load is fully charged and the start-up MOSFET is fully enhanced, the power-good signal is asserted and the second bypass side is enabled. The second side has a high current limit to deliver the full load current, and uses low R<sub>DS(ON)</sub>, low SOA switching regulator class MOSFETs Q2 and Q3. The TIMER capacitor is selected for a short time within the SOA of the shunt MOSFETs. This architecture minimizes the cost of MOSFETs to achieve a given load current and R<sub>DS(ON)</sub>. However, with the brief TIMER time for current limit, it has limited ability to ride through a load surge in current limit, or input voltage steps, and due to the low startup current cannot start up a resistive load such as a heating element or incandescent lamp.

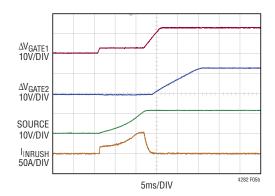

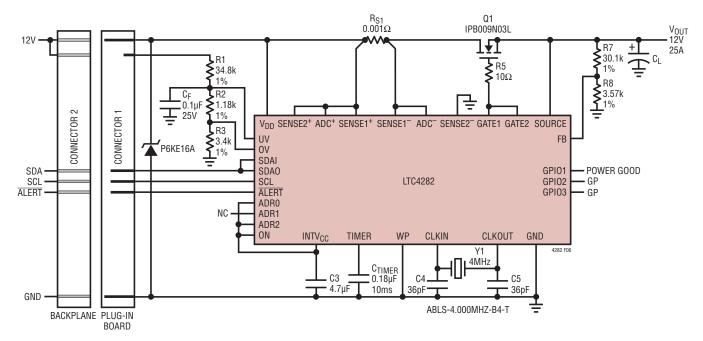

Figure 5 shows an example of high stress staged start. With high stress staged start the second bypass side is gated by the STRESS signal from GPIO2 so that one or more low  $R_{DS(ON)}$ , low SOA MOSFETs can be used to achieve the required  $R_{DS(ON)}$ . The bypass MOSFET(s) are turned off whenever SOA stress is encountered, while a single

Figure 4a. Low Stress Staged Start Application

Figure 4b. Normal Start-Up with Low Stress Staged Start

Figure 4c. Start-Up Into Short-Circuit with Low Stress Staged Start

LINEAR TECHNOLOGY

Figure 5a. High Stress Staged Start

Figure 5b. Start-Up Waveform

Figure 6. Single MOSFET Configuration

high SOA stress MOSFET is used for inrush and to ride through transients with a long TIMER time. During inrush the V<sub>DS</sub> of the MOSFETs is high and the GATE of the stress MOSFET is not fully enhanced, so the GPIO2 pin is held low to indicate STRESS, which holds the bypass MOSFET(s) off. The stress MOSFET starts up the load alone, either with a GATE capacitor or in current limit. When start-up is complete and the stress MOSFET is fully enhanced (V<sub>DS</sub> low and V<sub>GS</sub> high), the STRESS condition is removed and the GPIO2 pin goes high to enable the bypass MOSFETs to turn on. This architecture uses the stress MOSFET to ride through current limiting load surges as well as input voltage steps and can also start up a resistive load. The high SOA stress MOSFET is more expensive than the trickle MOSFET in the low stress staged start circuit, but may be cheaper than two or more intermediate SOA MOSFETs used in the parallel configuration (Figure 1).

Figure 6 demonstrates a single MOSFET application. The SENSE2<sup>-</sup> pin is grounded to disable the second current limit circuit and GATE driver so that the part behaves the same as other single Hot Swap controllers like the LTC4280. The GATE2 pin may be left open, or tied to the GATE1 pin to double the GATE pull-down currents for faster turn-off times in response to faults.

#### **Overvoltage Fault**

An overvoltage fault occurs when the OV pin rises above the OV threshold for longer than 15 $\mu$ s. This shuts off the GATE pins with 1mA currents to ground and sets the overvoltage present and overvoltage fault bits (Bit 0) in STATUS and FAULT\_LOG registers 0x1E and 0x04. If the voltage subsequently falls back below the threshold for 50ms, the GATE pins are allowed to turn on again unless overvoltage auto-retry has been disabled by clearing the OV auto-retry bit (Bit 0) in CONTROL register 0x00. If an external resistive divider is used, the OV threshold is 1.28V on the OV pin. When using the internal dividers the OV threshold is referenced to the V<sub>DD</sub> pin.

## **Undervoltage Fault**

An undervoltage fault occurs when the UV pin falls below its 1.28V threshold for longer than 15µs. This shuts off the GATE pins with 1mA currents to ground and sets the undervoltage present and undervoltage fault bits (Bit 1) STATUS and FAULT\_LOG in registers 0x1E and 0x04. If the voltage subsequently rises back above the threshold for 50ms, the GATE pins are allowed to turn on again unless undervoltage auto-retry has been disabled by clearing the UV auto-retry bit in CONTROL register 0x00.

42021

For the internal thresholds, the UV and OV signals may be filtered by placing a capacitor on the UV pin.

#### **ON/OFF Control**

The ON pin can be configured active high or active low with CONTROL register 0x00 bit 5 (1 for active high). In the active high configuration it is a true ON input, in the active low configuration it can be used as an ENABLE input to detect card insertion with a short pin. The delay from the ON pin commanding the part to turn on until the GATE pins begin to rise is set by CONTROL register 0x00 bit 6. If this bit is low the GATE pins turn on immediately, and if it is high they turn on after a 50ms debounce delay. Whenever the ON pin toggles, bit 4 in FAULT\_LOG register 0x04 is set to indicate a change of state and the other bits in FAULT register 0x04 are reset unless the ON\_FAULT\_MASK bit 7 in CONTROL register 0x00 is set.

The FET\_ON bit, bit 3 of CONTROL register 0x00, is set or reset by the rising and falling edges of the ON pin and by I<sup>2</sup>C write commands. When the LTC4282 comes out of UVLO the default state for bit 3 is read out of the EEPROM. If it is a 0, the part is configured to stay off after power-up and ignore the state of the ON pin. If it is a 1 the condition of the ON pin will be latched to bit 3 after the debounce period and the part will turn the GATEs on if the ON pin is in the ON state.

If the system shuts down due to a fault, it may be desirable to restart the system simply by removing and reinserting a load card. In cases where the LTC4282 and the switch reside on a backplane or midplane and the load resides on a plug-in card, the ON pin detects when the plug-in card is removed. Figure 7 shows an example where the ON pin is used to detect insertion. Once the plug-in card is reinserted the FAULT\_LOG register 0x04 is cleared (except for bit 5, which indicates the ON pin changed state). After the ON pin turn-on delay, the system is allowed to start up again.

If a connection sense on the plug-in card is driving the ON pin, insertion or removal of the card may cause the pin voltage to bounce. This results in clearing the FAULT\_LOG register when the card is removed. The pin may be debounced using a filter capacitor,  $C_{ON}$ , on the ON pin as shown in Figure 7. Note that the polarity of the ON pin is inverted with CONTROL register 0x00 bit 5 set to 0.

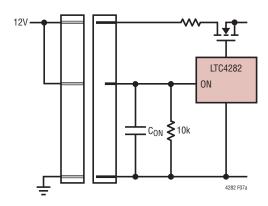

(a) ON Configured Active High (Default) CONTROL Register 0x00 Bit 5=1

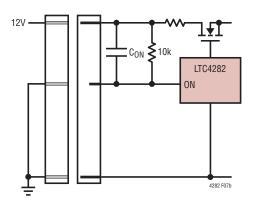

(b) ON Configured Active Low CONTROL Register 0x00 Bit 5=0

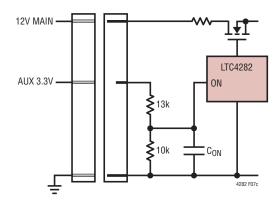

(c) ON Pin Sensing of AUX Supply ON Pin Configured Active High (Default)

Figure 7. Connection Sense Configurations with the ON Pin

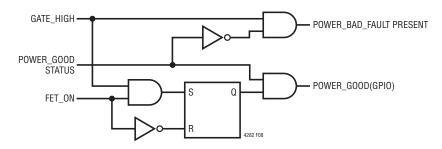

Figure 8. POWER\_GOOD Logic

#### **FET-Bad Fault**

In a Hot Swap application several possible faults can prevent the MOSFETs from turning on and reaching a low impedance state. A damaged MOSFET may have leakage from gate to drain or have degraded  $R_{DS(ON)}$ . Debris on the board may also produce leakage or a short from the GATE pin to the SOURCE pin, the MOSFET drain, or to ground. In these conditions the LTC4282 may not be able to pull the GATE pin high enough to fully enhance the MOSFET, or the MOSFET may not reach the intended  $R_{DS(ON)}$  when the GATE pin is fully enhanced. This can put the MOSFET in a condition where the power in the MOSFET is higher than its continuous power capability, even though the current is below the current limit. The LTC4282 monitors the integrity of the MOSFETs in two ways, and acts on both of them in the same manner.

First, the LTC4282 monitors the voltage between the  $V_{DD}$  and SOURCE pins. A comparator detects a bad DRAIN-to-SOURCE voltage ( $V_{DS}$ ) whenever the  $V_{DS}$  is greater than 200mV.

Second, the LTC4282 monitors the GATE voltage. The GATE voltage may not fully enhance with a damaged MOSFET, and a severely damaged MOSFET most often has GATE, DRAIN and SOURCE all shorted together. If the LTC4282 is in the ON state, but neither GATE pin comes up to their 8V threshold above SOURCE, a FET-bad condition is detected.

When either FET-bad condition is present while the MOSFETs are commanded on, an internal FET-bad fault timer starts. When the timer reaches the threshold set in register 0x06 (1ms per LSB for a max of 255ms), a FET-bad fault condition is set, the part turns off, and the GATE pins are pulled low with 1mA currents. In the case of a gate-to-drain short, it may be impossible for the LTC4282

to turn off the MOSFET. In this case the LTC4282 can be configured to signal power-bad to the load so the load goes into a low current state and send a FET-bad fault alert to the controller that may be able to shut down upstream supplies and/or flag the card for service.

The LTC4282 treats a FET-bad fault similar to an overcurrent fault, and will auto-retry after 256 timer cycles if the overcurrent auto-retry bit is set. Note that during start-up, the FET-bad condition is present because the voltage from drain to source is greater than 200mV and the GATE pins are not fully enhanced, thus the FET-bad timeout must be long enough to allow for the largest allowable load to start up. FET-bad faults are disabled by setting the FET\_BAD\_FAULT\_TIMER value to 0x00.

#### **FET Short Fault**

A FET short fault is reported if the data converter measures a current sense voltage greater than or equal to 0.25mV while the GATE pins are turned off. This condition sets FET\_SHORT bit 5 in STATUS register 0x1E, and FET\_SHORT\_FAULT bit 5 in FAULT\_LOG register 0x04.

#### **Power Bad Fault**

The POWER\_GOOD status bit, bit 3 in STATUS register 0x1E, is set when the FB pin voltage rises above its 1.28V threshold. To indicate POWER\_GOOD on the GPI01 pin, one or both GATE pins must first exceed their 8V  $V_{GS}$  thresholds after start-up; this requirement prevents POWER\_GOOD from asserting during start-up when the FB pin first crosses its threshold. After start-up the GPI01 pin will output the value of the FB comparator so that POWER\_GOOD stays high even in cases such as an input voltage step that causes the GATE pins to briefly dip below 8V  $V_{GS}$ . See Figure 8.

A power-bad fault is generated when the FB pin is low and one or both GATE pins are high, preventing powerbad faults when both GATE-to-SOURCE voltages are low during power-up or power-down.

#### **Fault Alerts**

A fault condition sets the corresponding fault bit in FAULT LOG register 0x04. ADC ALERT LOG register 0x05, and TIMER\_OVERFLOW\_PRESENT (Bit 1) and METER OVERFLOW PRESENT (Bit 2) in the STATUS register 0x1F. Fault bits are reset by writing a 0 and the overflow status bits are reset by resetting the energy meter by setting and resetting ADC CONTROL register 0x1D bit 6. A fault condition can also generate an alert (ALERT asserts low) by setting the corresponding bit in the alert mask registers: ALERT registers 0x02 and 0x03, and GPIO CONFIG register bit 0. A low on ALERT may be generated upon completion of an ADC measurement by setting bit 2 in the GPIO CONFIG register 0x07. This condition does not have a corresponding fault bit. Faults with enabled alerts set bit 7 in the ALERT CONTROL register 0x1C, which controls the state of the ALERT pin. Clearing this bit will cause the ALERT pin to go high and setting this bit causes it to go low. Alert masking stored in EEPROM is transferred into registers at power up.

After the bus master controller broadcasts the Alert Response Address, the LTC4282 responds with its address on the SDA line and releases  $\overline{\text{ALERT}}$  as shown in Figure 17. If there is a collision between two LTC4282s responding with their addresses simultaneously, then the device with the lower address wins arbitration and releases its  $\overline{\text{ALERT}}$  pin. The devices that lost arbitration will still hold the  $\overline{\text{ALERT}}$  pin low and will respond with their addresses and release  $\overline{\text{ALERT}}$  as the I $^2$ C master executes additional Alert Response protocols until  $\overline{\text{ALERT}}$  is release by all devices. The  $\overline{\text{ALERT}}$  pin can also be released by clearing ALERT\_CONTROL bit 7 in register 0x1C with the I $^2$ C interface.

The ALERT pin can also be used as a GPIO pin, which pulls low by setting ALERT bit 6 in register 0x1C, and the ALERT pin input status is stored in STATUS register 0x1F bit 4.

Once the ALERT signal has been released from a fault, it will pull low again if the corresponding fault reoccurs, but not if the fault remains continuously present.

#### Resetting Faults in FAULT LOG

The faults in FAULT\_LOG register 0x04 may cause the part to latch off if their corresponding auto-retry bits are not set. In backplane resident applications it is desirable to latch off if a card has produced a failure and start up normally if the card is replaced. To allow this function the ON pin must be used as a connection sense input. When CONTROL bit 7 in register 0x00 is not set, a turn-off signal from the ON pin (card removed) will clear the FAULT\_LOG register except for bit 4 (ON changed state). The entire FAULT\_LOG register also cleared when the INTV<sub>CC</sub> pin falls below it's 2.49V threshold (UVLO), and individual bits may be cleared manually via that I<sup>2</sup>C interface. Note that faults that are still present, as indicated in STATUS register 0x1E, cannot be cleared.

The FAULT\_LOG register is not cleared when auto-retrying. When auto-retry is disabled the existence of a logged fault keeps the MOSFETs off. As soon as the FAULT\_LOG is cleared, the MOSFETs turns on. If auto-retry is enabled, then a high STATUS bit keeps the MOSFETs off and the FAULT\_LOG bit is ignored. Subsequently, when the status bit is cleared by removal of the fault condition, the MOSFETs is allowed to turn on again even though the fault bit remains set as a record of the previous fault conditions.

#### Reboot

The LTC4282 features a reboot command bit, located in bit 7 of ADC\_CONTROL register 0x1D. Setting this bit will cause the LTC4282 to reset and copy the contents of the EEPROM to operating memory the same as after initial power up. The 50ms debounce before the part restarts is lengthened to 3.2s for reboot in order to allow load capacitance to discharge and reset before the LTC4282 turns back on. On systems where the Hot Swap controller supplies power to the I<sup>2</sup>C master, this allows the master to issue a command that power cycles the entire board, including itself.

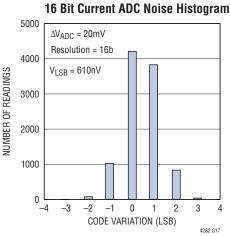

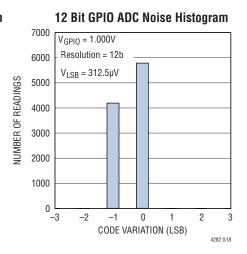

#### **Data Converters**

The LTC4282 incorporates a pair of sigma delta A/D converters that are configurable to 12 or 16 bits. One converter continuously samples the current sense voltage, while the other monitors the input/output voltage and the voltage

on a GPIO input. The sigma-delta architecture inherently averages signal noise during the measurement period.

The data converters may be run in a 12-bit or 16-bit mode, as selected by bit 1 in ILIM\_ADJUST register 0x11. The second data converter may be configured to measure  $V_{IN}$  at the  $V_{DD}$  pin or  $V_{OUT}$  at the SOURCE pin by setting bit 2, and can select between measuring GPI02 or GPI03 with bit 1. The data converter full scale is 40mV for the current sense voltage, a choice of 33.28V, 16.64V, 8.32V or 5.547V for  $V_{DD}$  and  $V_{SOURCE}$ , and 1.28V for GPI0.

The ADC+ and ADC- input pins allow the ADC to measure the average voltage across the two sense resistors using resistive dividers. Some applications may use parallel sense resistors to achieve a specific resistance, in which case the averaging resistors can be selected with the same ratio as the sense resistors they connect to, which allows the ADC to still measure current accurately. See Figure 9. In this case the effective ADC sense resistor is  $R_S$  in parallel with  $k \cdot R_S$  for the current limit. Scaling the averaging resistors,  $R_A$ , by the same scaling factor, k, allows the ADC to measure the correct sense voltage for this effective sense resistor. The smallest averaging resistor should not exceed  $1\Omega$ .

Figure 9. Weighted Averaging Sense Voltages

The two data converters are synchronized, and after each current measurement conversion, the measured current is multiplied by the measured  $V_{DD}$  or  $V_{SOURCE}$  to yield input or output power. After each conversion the measurement results and power are compared to the recorded min and

max values. If the measurement is a new min or max, then those registers are updated. The measurements are also compared to the min/max alarm thresholds in registers 0x08 to 0x0F and will set the corresponding ADC alert bit in ADC\_ALERT\_LOG register 0x05 and generate an alert if configured to do so in ALERT register 0x03.