Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Dual Matched 1.3GHz Differential Amplifiers/ADC Drivers

#### **FEATURES**

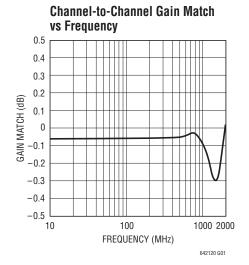

- Matched Gain ±0.1dB

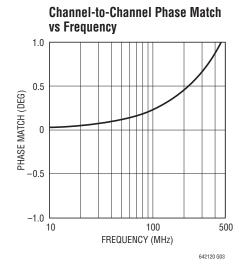

- Matched Phase ±0.2° at 100MHz

- Channel Separation 80dB at 100MHz

- 1.3GHz –3dB Bandwidth; Fixed Gain of 10V/V (20dB)

- $IMD_3 = -76 dBc$  at 100 MHz,  $2V_{P-P}$

- Equivalent OIP<sub>3</sub> = 42dBm at 100MHz

- 1nV/√Hz Internal Op Amp Noise

- 6.2dB Noise Figure

- Differential Inputs and Outputs

- Rail-to-Rail Output Swing

- 40mA Supply Current (120mW) per Amplifier

- 1V to 1.6V Output Common Mode Voltage, Adjustable

- DC- or AC-Coupled Operation

- 20-Lead 3mm × 4mm × 0.75mm QFN Package

### **APPLICATIONS**

- Differential ADC Driver

- Single Ended to Differential Conversion

- IF Sampling (Diversity) Receivers

- Broadband I/Q Amplifiers

- Satellite Communications

### DESCRIPTION

The LTC®6421-20 is a dual high speed differential amplifier targeted at processing signals from DC to 140MHz. The part has been specifically designed to drive 12-, 14- and 16-bit ADCs with low noise and low distortion, but can also be used as a general-purpose broadband gain block.

The LTC6421-20 is easy to use, with minimal support circuitry required. The output common mode voltage is set using an external pin, independent of the inputs, which eliminates the need for transformers or AC-coupling capacitors in many applications. The gain is internally fixed at 20dB (10V/V).

The LTC6421-20 saves space and power compared to alternative solutions using IF gain blocks and transformers. The LTC6421-20 is packaged in a compact 20-lead  $3\text{mm} \times 4\text{mm}$  QFN package and operates over the  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  temperature range.

T, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

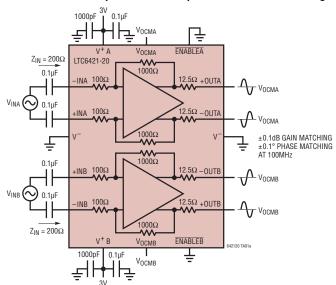

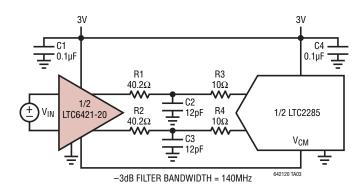

## TYPICAL APPLICATION

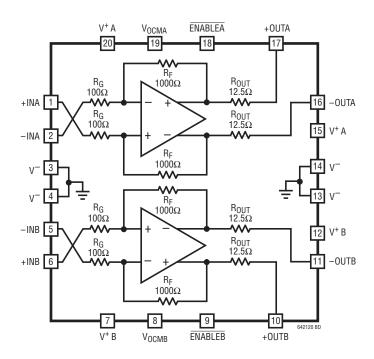

**Matched Dual Amplifiers with Output Common Mode Biasing**

#### Distribution of Gain Match

642120fb

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) | 3.6V     |

|---------------------------------------------------|----------|

| Input Current (Note 2)                            | ±10mA    |

| Operating Temperature Range (Note 3)40°C          | to 85°C  |

| Specified Temperature Range (Note 4) – 40°C       | to 85°C  |

| Storage Temperature Range65°C to                  | 150°C    |

| Maximum Junction Temperature                      | . 150°C  |

| Output Short-Circuit Duration In                  | definite |

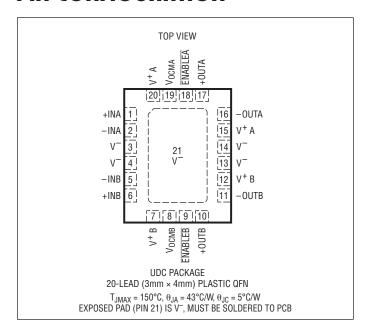

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH   | TAPE AND REEL        | PART MARKING* | PACKAGE DESCRIPTION             | SPECIFIED TEMPERATURE RANGE |

|--------------------|----------------------|---------------|---------------------------------|-----------------------------|

| LTC6421CUDC-20#PBF | LTC6421CUDC-20#TRPBF | LDDN          | 20-Lead (3mm × 4mm) Plastic QFN | 0°C to 70°C                 |

| LTC6421IUDC-20#PBF | LTC6421IUDC-20#TRPBF | LDDN          | 20-Lead (3mm × 4mm) Plastic QFN | -40°C to 85°C               |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

## **SELECTOR GUIDE**

| PART NUMBER |            | GAIN | GAIN  | Z <sub>IN</sub> (DIFFERENTIAL) |                   |

|-------------|------------|------|-------|--------------------------------|-------------------|

| SINGLE      | DUAL       | (dB) | (V/V) | $(\Omega)$                     | COMMENT           |

| LTC6400-8   |            | 8    | 2.5   | 400                            | Lowest Distortion |

| LTC6400-14  |            | 14   | 5     | 200                            | Lowest Distortion |

| LTC6400-20  | LTC6420-20 | 20   | 10    | 200                            | Lowest Distortion |

| LTC6400-26  |            | 26   | 20    | 50                             | Lowest Distortion |

| LTC6401-8   |            | 8    | 2.5   | 400                            | Lowest Power      |

| LTC6401-14  |            | 14   | 5     | 200                            | Lowest Power      |

| LTC6401-20  | LTC6421-20 | 20   | 10    | 200                            | Lowest Power      |

| LTC6401-26  |            | 26   | 20    | 50                             | Lowest Power      |

**DC ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which <u>apply over the full operating temperature range</u>, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 3V$ ,  $V^- = 0V$ ,  $+IN = -IN = V_{OCM} = 1.25V$ , <u>ENABLE</u> = 0V, No R<sub>L</sub> unless otherwise noted.

| SYMBOL                  | PARAMETER                                           | CONDITIONS                                         |   | MIN  | TYP    | MAX   | UNITS            |

|-------------------------|-----------------------------------------------------|----------------------------------------------------|---|------|--------|-------|------------------|

| Input/Output (          | Characteristic                                      |                                                    |   |      |        |       |                  |

| G <sub>DIFF</sub>       | Gain                                                | V <sub>IN</sub> = ±100mV Differential              | • | 19.6 | 20     | 20.4  | dB               |

| $\Delta G$              | Gain Matching                                       | Channel-to-Channel                                 | • |      | ±0.1   | ±0.25 | dB               |

| TC <sub>GAIN</sub>      | Gain Temperature Drift                              | V <sub>IN</sub> = ±100mV Differential              | • |      | 0.0015 |       | dB/°C            |

| V <sub>SWINGMIN</sub>   | Output Swing Low (V <sub>OCM</sub> = 1.5V)          | Each Output, V <sub>IN</sub> = ±400mV Differential | • |      | 0.1    | 0.25  | V                |

| V <sub>SWINGMAX</sub>   | Output Swing High (V <sub>OCM</sub> = 1.5V)         | Each Output, V <sub>IN</sub> = ±400mV Differential | • | 2.75 | 2.9    |       | V                |

| V <sub>OUTDIFFMAX</sub> | Maximum Differential Output Swing                   |                                                    | • | 5    | 5.6    |       | V <sub>P-P</sub> |

| I <sub>OUT</sub>        | Output Current Drive                                | 2V <sub>P-P, OUT</sub> (Note 10)                   | • | 10   |        |       | mA               |

| V <sub>OS</sub>         | Input Offset Voltage                                | Differential                                       | • | -2   | ±0.4   | 2     | mV               |

| TCV <sub>OS</sub>       | Input Offset Voltage Drift                          | Differential                                       | • |      | 1.4    |       | μV/°C            |

| I <sub>VRMIN</sub>      | Input Common Mode Voltage Range, MIN                |                                                    | • |      |        | 1     | V                |

| I <sub>VRMAX</sub>      | Input Common Mode Voltage Range, MAX                |                                                    | • | 1.6  |        |       | V                |

| R <sub>INDIFF</sub>     | Input Resistance (+IN, -IN)                         | Differential                                       | • | 170  | 200    | 230   | Ω                |

| $\Delta R_{IN}$         | Input Impedance Matching                            | Channel-to-Channel                                 | • |      | ±1     | ±2.5  | %                |

| CINDIFF                 | Input Capacitance (+IN, -IN)                        | Differential, Includes Parasitic                   |   |      | 1      |       | pF               |

| Routdiff                | Output Resistance (+OUT, -OUT)                      | Differential                                       | • | 20   | 25     | 36    | Ω                |

| CMRR                    | Common Mode Rejection Ratio                         | Input Common Mode Voltage 1V to 1.6V               | • | 45   | 68     |       | dB               |

| Output Comm             | on Mode Voltage Control                             |                                                    |   |      |        |       |                  |

| G <sub>CM</sub>         | Common Mode Gain                                    | $V_{OCM} = 1V$ to 1.6V                             |   |      | 1      |       | V/V              |

| V <sub>OCMMIN</sub>     | Output Common Mode Range, MIN                       |                                                    | • |      |        | 1     | V                |

| V <sub>OCMMAX</sub>     | Output Common Mode Range, MAX                       |                                                    | • | 1.6  |        |       | V                |

| V <sub>OSCM</sub>       | Common Mode Offset Voltage                          | V <sub>OCM</sub> = 1.25V to 1.5V                   | • | -10  | ±2     | 10    | mV               |

| TCV <sub>OSCM</sub>     | Common Mode Offset Voltage Drift                    |                                                    | • |      | 6      |       | μV/°C            |

| IV <sub>OCM</sub>       | V <sub>OCM</sub> Input Current                      |                                                    | • | -15  | -3     | 0     | μА               |

| ENABLEX Pins            | S(X = A, B)                                         |                                                    |   |      |        |       |                  |

| V <sub>IL</sub>         | ENABLEx Input Low Voltage                           |                                                    | • |      |        | 0.8   | V                |

| V <sub>IH</sub>         | ENABLEx Input High Voltage                          |                                                    | • | 2.4  |        |       | V                |

|                         | ENABLEx Input Current                               | ENABLEX ≤ 0.8V<br>ENABLEX ≥ 2.4V                   | • |      | 1.5    | ±0.5  | μΑ<br>μΑ         |

| Power Supply            |                                                     |                                                    |   |      |        |       |                  |

| $\overline{V_{S}}$      | Operating Supply Range                              |                                                    | • | 2.85 | 3      | 3.5   | V                |

| I <sub>S</sub>          | Supply Current                                      | ENABLEx ≤ 0.8V; per Amplifier                      | • |      | 40     | 50    | mA               |

| I <sub>SHDN</sub>       | Shutdown Supply Current                             | ENABLEx ≥ 2.4V; per Amplifier, Inputs Floating     | • |      | 1      | 3     | mA               |

| PSRR                    | Power Supply Rejection Ratio (Differential Outputs) | V+ = 2.85V to 3.5V                                 | • | 55   | 86     |       | dB               |

# **AC ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V^+ = 3V$ , $V^- = 0V$ , $V_{OCM} = 1.25V$ , ENABLE = 0V, No $R_L$ unless otherwise noted.

| SYMBOL                 | PARAMETER                                 | CONDITIONS                                                                                                 |   | MIN | TYP      | MAX   | UNITS      |

|------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------|---|-----|----------|-------|------------|

| $\Delta G$             | Gain Matching                             | f = 100MHz (Note 9)                                                                                        | • |     | ±0.1     | ±0.25 | dB         |

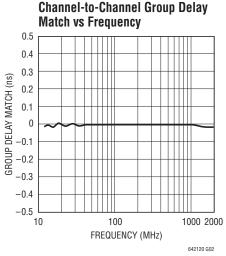

| $\Delta P$             | Phase Matching                            | f = 100MHz                                                                                                 |   |     | ±0.2     |       | deg        |

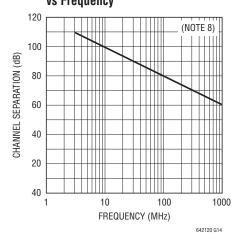

|                        | Channel Separation (Note 8)               | f = 100MHz                                                                                                 |   |     | 80       |       | dB         |

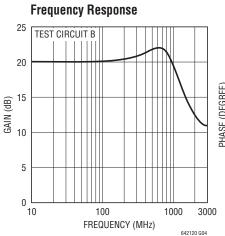

| -3dBBW                 | -3dB Bandwidth                            | 200mV <sub>P-P, OUT</sub> (Note 6)                                                                         |   |     | 1.3      |       | GHz        |

| 0.5dBBW                | Bandwidth for 0.5dB Flatness              | 200mV <sub>P-P, OUT</sub> (Note 6)                                                                         |   |     | 250      |       | MHz        |

| 0.1dBBW                | Bandwidth for 0.1dB Flatness              | 200mV <sub>P-P, OUT</sub> (Note 6)                                                                         |   |     | 130      |       | MHz        |

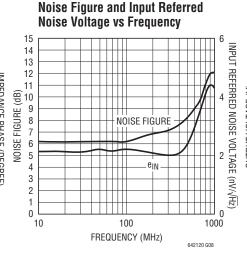

| NF                     | Noise Figure                              | $R_L = 375\Omega$ (Note 5), f = 100MHz                                                                     |   |     | 6.2      |       | dB         |

| e <sub>IN</sub>        | Input Referred Voltage Noise Density      | Includes Resistors (Short Inputs), f = 100MHz                                                              |   |     | 2.2      |       | nV/√Hz     |

| e <sub>ON</sub>        | Output Referred Voltage Noise Density     | Includes Resistors (Short Inputs), f = 100MHz                                                              |   |     | 22       |       | nV/√Hz     |

| 1/f                    | 1/f Noise Corner                          |                                                                                                            |   |     | 12.5     |       | kHz        |

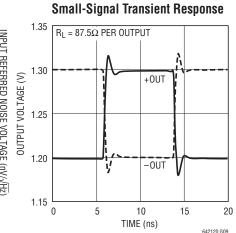

| SR                     | Slew Rate                                 | Differential (Note 6)                                                                                      |   |     | 4500     |       | V/µs       |

| t <sub>S1%</sub>       | 1% Settling Time                          | 2V <sub>P-P, OUT</sub> (Note 6)                                                                            |   |     | 2        |       | ns         |

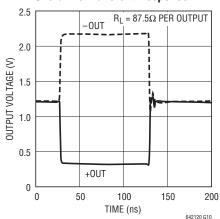

| t <sub>OVDR</sub>      | Overdrive Recovery Time                   | 1.9V <sub>P-P, OUT</sub> (Note 6) Single Ended                                                             |   |     | 7        |       | ns         |

| $\overline{P_{1dB}}$   | 1dB Compression Point                     | $R_L = 375\Omega$ (Notes 5, 7), $f = 100MHz$                                                               |   |     | 18       |       | dBm        |

| t <sub>ON</sub>        | Turn-On Time                              | +OUT, -OUT Within 10% of Final Values                                                                      |   |     | 80       |       | ns         |

| t <sub>OFF</sub>       | Turn-Off Time                             | I <sub>CC</sub> Falls to 10% of Nominal                                                                    |   |     | 150      |       | ns         |

| -3dBBW <sub>VOCM</sub> | V <sub>OCM</sub> Pin Small Signal –3dB BW | 0.1V <sub>P-P</sub> at V <sub>OCM</sub> , Measured Single-Ended at Output (Note 6)                         |   |     | 15       |       | MHz        |

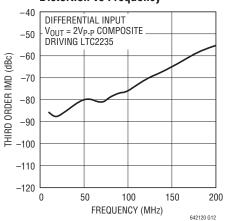

| IMD <sub>3</sub>       | 3rd Order Intermodulation Distortion      | f = 100MHz (1MHz Spacing),<br>V <sub>OUT</sub> = 2V <sub>P-P</sub> Composite                               |   |     | -76      |       | dBc        |

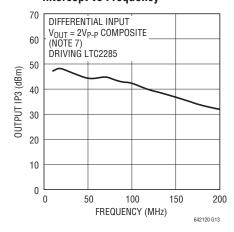

| OIP <sub>3</sub>       | 3rd Order Output Intercept                | f = 100MHz (Note 7)                                                                                        |   |     | 42       |       | dBc        |

| IIP <sub>3</sub>       | 3rd Order Input Intercept                 | $ f = 100 \text{MHz} \ (Z_{\text{IN}} = 50 \Omega) $ $ f = 100 \text{MHz} \ (Z_{\text{IN}} = 200 \Omega) $ |   |     | 22<br>16 |       | dBc<br>dBc |

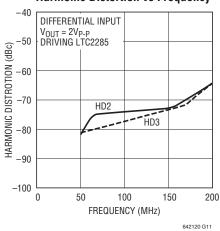

| HD <sub>2</sub>        | 2nd Order Harmonic Distortion             | f = 100MHz, V <sub>OUT</sub> = 2V <sub>P-P</sub>                                                           |   |     | -74      |       | dBc        |

| HD <sub>3</sub>        | 3rd Order Harmonic Distortion             | f = 100MHz, V <sub>OUT</sub> = 2V <sub>P-P</sub>                                                           |   |     | -78      |       | dBc        |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Input pins (+IN, -IN) are protected by steering diodes to either supply. If the inputs go beyond either supply rail, the input current should be limited to less than 10mA.

**Note 3:** The LTC6421C and LTC6421I are guaranteed functional over the operating temperature range of  $-40^{\circ}$ C to 85°C.

**Note 4:** The LTC6421C is guaranteed to meet specified performance from  $0^{\circ}$ C to  $70^{\circ}$ C. It is designed, characterized and expected to meet specified performance from  $-40^{\circ}$ C to  $85^{\circ}$ C but is not tested or QA sampled at these temperatures. The LTC6421I is guaranteed to meet specified performance from  $-40^{\circ}$ C to  $85^{\circ}$ C.

Note 5: Input and output baluns used. See Test Circuit A.

**Note 6:** Measured using Test Circuit B.  $R_L = 87.5\Omega$  on each output.

Note 7: Since the LTC6421-20 is a feedback amplifier with low output impedance, a resistive load is not required when driving an AD converter. Therefore, typical output power is very small. In order to compare the LTC6421-20 with amplifiers that require  $50\Omega$  output load, the output voltage swing driving a given  $R_L$  is converted to  $\text{OIP}_3$  and  $\text{P}_{1dB}$  as if it were driving a  $50\Omega$  load. Using this modified convention,  $2V_{P-P}$  is by definition equal to 10dBm, regardless of actual  $R_L$ .

**Note 8:** Channel separation (the inverse of crosstalk) is measured by driving a signal into one input, while terminating the other input. Channel separation is the ratio of the resulting output signal at the driven channel to the channel that is not driven.

**Note 9:** Not production tested. Guaranteed by design and by correlation to production tested parameters.

**Note 10:** The output swing range is at least  $2V_{P-P}$  differential even when sourcing or sinking 20mA. Tested at  $V_{OCM} = 1.5V$ .

TECHNOLOGY TECHNOLOGY

### TYPICAL PERFORMANCE CHARACTERISTICS

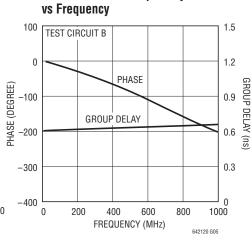

**S21 Phase and Group Delay**

642120fb

## TYPICAL PERFORMANCE CHARACTERISTICS

## **Overdrive Transient Response**

#### **Harmonic Distortion vs Frequency**

## Third Order Intermodulation Distortion vs Frequency

## Equivalent Output Third Order Intercept vs Frequency

## Channel Separation vs Frequency

### PIN FUNCTIONS

**+INA**, **-INA**, **-INB**, **+INB** (**Pins 1**, **2**, **5**, **6**): Differential Inputs of A and B channel respectively.

**V**<sup>-</sup> (**Pins 3, 4, 13, 14, 21**): Negative Power Supply. All four pins, as well as the exposed back, must be connected to same voltage/ground.

**ENABLEA**, **ENABLEB** (**Pins 9, 18**): Logic inputs. If low, the amplifier is enabled. If high, the amplifier is disabled and placed in a low-power shutdown mode, making the amplifier outputs high impedance. These pins are internally separate. These pins should not be left floating.

V<sup>+</sup> A, V<sup>+</sup> B (Pins 15, 20, 7, 12): Positive Power Supply (Normally tied to 3V or 3.3V). Supply pins of A and B channels are internally separate. Bypass each pin with 1000pF and 0.1µF capacitors as close to the pins as possible.

-OUTA, +OUTA, -OUTB, +OUTB (Pins 16, 17, 11, 10): Differential Outputs of channels A and B respectively.

$V_{OCMA}$ ,  $V_{OCMB}$  (Pins 19, 8): These pins set the output common mode voltage for the respective channel. They are internally separate. A  $0.1\mu F$  external bypass capacitor is recommended.

**Exposed Pad (Pin 21):** V<sup>-</sup>. The Exposed Pad must be connected to same voltage/ground as pins 3, 4, 13, 14.

## **BLOCK DIAGRAM**

#### **Circuit Operation**

Each of the two channels of the LTC6421-20 is composed of a fully differential amplifier with on chip feedback and output common mode voltage control circuitry. Differential gain and input impedance are set by  $100\Omega/1000\Omega$  resistors in the feedback network. Small output resistors of  $12.5\Omega$  improve the circuit stability over various load conditions.

The LTC6421-20 is very flexible in terms of I/O coupling. It can be AC- or DC-coupled at the inputs, the outputs or both. If the inputs are AC-coupled, the input common mode voltage is automatically biased close to  $V_{\rm OCM}$  and thus no external circuitry is needed for bias. The LTC6421-20 provides an output common mode voltage set by  $V_{\rm OCM}$ , which allows driving an ADC directly without external components such as a transformer or AC coupling capacitors. The input signal can be either single-ended or differential with only minor differences in distortion performance.

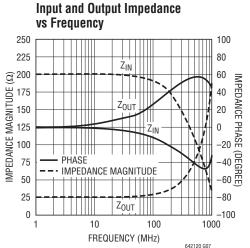

#### **Input Impedance and Matching**

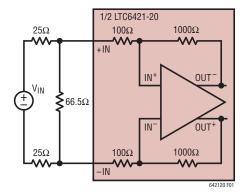

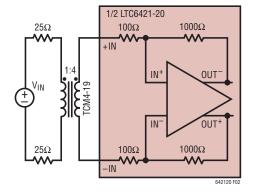

The differential input impedance of the LTC6421-20 is  $200\Omega$ . If a  $200\Omega$  source impedance is unavailable, then the differential inputs may need to be terminated to a lower value impedance, e.g.  $50\Omega$ , in order to provide an impedance match for the source. Several choices are available. One approach is to use a differential shunt resistor (Figure 1). Another approach is to employ a wide band transformer (Figure 2). Both methods provide a wide band impedance match. The termination resistor or the transformer must be placed close to the input pins in order to minimize the reflection due to input mismatch. Alternatively, one could apply a narrowband impedance match at the inputs of the LTC6421-20 for frequency selection and/or noise reduction.

Figure 1. Input Termination for Differential 50  $\!\Omega$  Input Impedance Using Shunt Resistor

Figure 2. Input Termination for Differential 50  $\!\Omega$  Input Impedance Using a 1:4 Balun

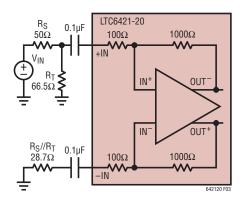

Referring to Figure 3, LTC6421-20 can be easily configured for single-ended input and differential output without a balun. The signal is fed to one of the inputs through a matching network while the other input is connected to the same matching network and a source resistor. Because the return ratios of the two feedback paths are equal, the two outputs have the same gain and thus symmetrical swing. In general, the single-ended input impedance and termination resistor  $R_T$  are determined by the combination of  $R_S,\,R_G$  and  $R_F.$  For example, when  $R_S$  is  $50\Omega$ , it is found that the single-ended input impedance is  $202\Omega$  and  $R_T$  is  $66.5\Omega$  in order to match to a  $50\Omega$  source impedance.

The LTC6421-20 is unconditionally stable. However, the overall differential gain is affected by both source impedance and load impedance as follows:

$$A_{V} = \left| \frac{V_{OUT}}{V_{IN}} \right| = \frac{2000}{R_{S} + 200} \cdot \frac{R_{L}}{25 + R_{I}}$$

#### **Output Impedance Match**

The LTC6421-20 can drive an ADC directly without external output impedance matching. Alternatively, the differential output impedance of  $25\Omega$  can be matched to a higher value impedance, e.g.  $50\Omega$ , by series resistors or an LC network.

#### **Output Common Mode Adjustment**

The output common mode voltage is set by the  $V_{OCM}$  pin, which is a high impedance input. The output common mode voltage is capable of tracking  $V_{OCM}$  in a range from 1V to 1.6V. The bandwidth of  $V_{OCM}$  control is typically 15MHz, which is dominated by a low pass filter connected to the  $V_{OCM}$  pin and is aimed to reduce common mode noise generation at the outputs. The internal common mode feedback loop has a -3dB bandwidth of 300MHz, allowing fast rejection of any common mode output voltage disturbance. The  $V_{OCM}$  pin should be tied to a DC bias

Figure 3. Input Termination for Single-Ended 50 $\Omega$  Input Impedance

voltage with a  $0.1\mu F$  bypass capacitor. When interfacing with A/D converters such as the LTC22xx families, the  $V_{OCM}$  pin can be connected to the  $V_{CM}$  pin of the ADC.

#### **Driving A/D Converters**

The LTC6421-20 has been specifically designed to interface directly with high speed A/D converters. The back page of this data sheet shows the LTC6421-20 driving an LTC2285, which is a dual 14-bit, 125Msps ADC.

The  $V_{OCM}$  pins of the LTC6421-20 are connected to the  $V_{CM}$  pins of the LTC2285, which provide a DC voltage level of 1.5V. Both ICs are powered from the same 3V supply voltage.

The inputs to the LTC6421-20 can be configured in various ways, as described in the Input Impedance and Matching section of this data sheet. The outputs of the LTC6421-20 may be connected directly to the analog inputs of an ADC, or a simple lowpass or bandpass filter network may be inserted to reduce out-of-band noise.

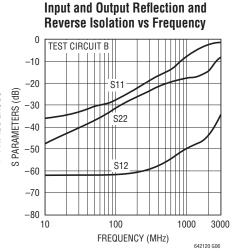

#### **Test Circuits**

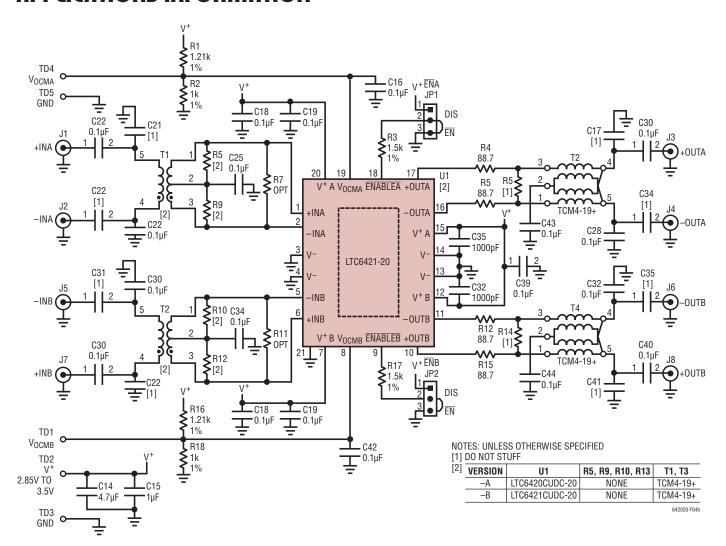

Due to the fully-differential design of the LTC6421 and its usefulness in applications with differing characteristic specifications, two test circuits are used to generate the information in this data sheet. Test Circuit A is DC1299, a two-port demonstration circuit for the LTC6420/LTC6421 family. The schematic and silkscreen are shown in Figure 4. This circuit includes input and output transformers (baluns) for single-ended-to-differential conversion and impedance transformation, allowing direct hook-up to a 2-port network analyzer. There are also series resistors at the output to avoid loading the amplifier directly with a  $50\Omega$  load. Due to the input and output transformers, the -3dB bandwidth is reduced from 1.3GHz to approximately 1.1GHz.

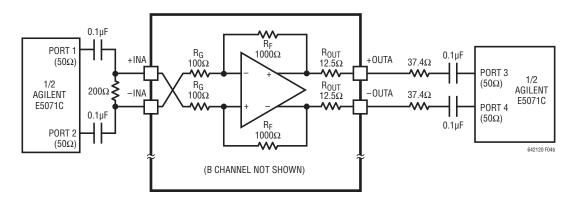

Test Circuit B uses a 4-port network analyzer to measure S-parameters and gain/phase response. This removes the effects of the wideband baluns and associated circuitry, for a true picture of the >1GHz S-parameters and AC characteristics.

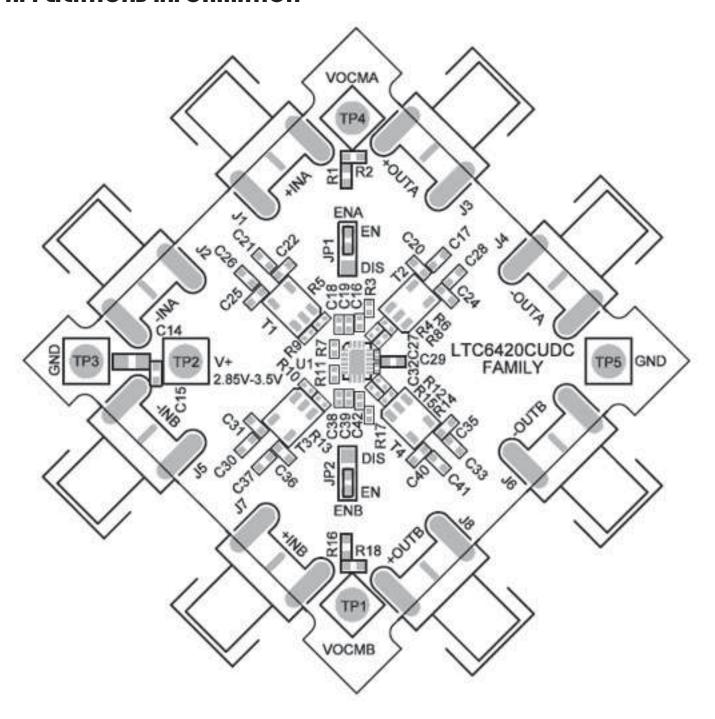

Figure 4a. Top Silkscreen of DC1299 (Test Circuit A)

Figure 4b. Demo Circuit 1299 Schematic (Test Circuit A)

## TYPICAL APPLICATIONS

## Test Circuit B, 4-Port Measurements (Only the Signal-Path Connections Are Shown)

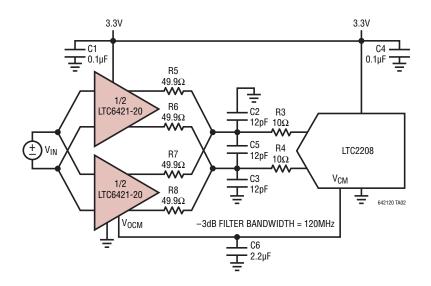

#### **Parallel ADC Drivers to Reduce Wideband Noise**

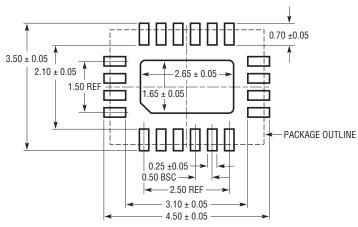

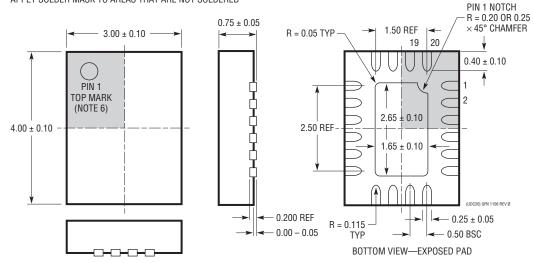

### PACKAGE DESCRIPTION

#### **UDC** Package 20-Lead Plastic QFN (3mm × 4mm)

(Reference LTC DWG # 05-08-1742 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

#### NOTE:

- 1. DRAWING IS NOT A JEDEC PACKAGE OUTLINE

2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON THE TOP AND BOTTOM OF PACKAGE

## **REVISION HISTORY** (Revision history begins at Rev B)

| REV | DATE | DESCRIPTION              | PAGE NUMBER |

|-----|------|--------------------------|-------------|

| В   | 3/10 | Changes to Applications  | 1           |

|     |      | Changes to Related Parts | 16          |

## TYPICAL APPLICATION

#### **Dual ADC Driver for Wideband Direct-Conversion Receivers**

## **RELATED PARTS**

| PART NUMBER                                            | DESCRIPTION                                                                        | COMMENTS                                                                 |

|--------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| High-Speed Diffe                                       | erential Amplifiers/Differential Op Amps                                           |                                                                          |

| LT®1993-2                                              | 800MHz Differential Amplifier/ADC Driver                                           | $A_V = 2V/V$ , OIP3 = 38dBm at 70MHz                                     |

| LT1993-4                                               | 900MHz Differential Amplifier/ADC Driver                                           | $A_V = 4V/V$ , OIP3 = 40dBm at 70MHz                                     |

| LT1993-10                                              | 700MHz Differential Amplifier/ADC Driver                                           | $A_V = 10V/V$ , OIP3 = 40dBm at 70MHz                                    |

| LT1994                                                 | Low Noise, Low Distortion Differential Op Amp                                      | 16-Bit SNR and SFDR at 1MHz, Rail-to-Rail Outputs                        |

| LT5514                                                 | Ultralow Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain         | OIP3 = 47dBm at 100MHz, Gain Control Range 10.5dB to 33dB                |

| LT5524                                                 | Low Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain              | OIP3 = 40dBm at 100MHz, Gain Control Range 4.5dB to 37dB                 |

| LTC6400-8/<br>LTC6400-14/<br>LTC6400-20/<br>LTC6400-26 | Low Noise, Low Distortion, Differential ADC Drivers                                | $A_V = 8dB/14dB/20dB/26dB$ , Single Amplifier per IC, High Performance   |

| LTC6401-8/<br>LTC6401-14/<br>LTC6401-20/<br>LTC6401-26 | Low Noise, Low Distortion, Differential ADC Drivers                                | $A_V = 8dB/14dB/20dB/26dB$ , Single Amplifier per IC, Low Power          |

| LT6402-6                                               | 300MHz Differential Amplifier/ADC Driver                                           | $A_V = 6dB$ , Distortion < $-80dBc$ at 25MHz                             |

| LT6402-12                                              | 300MHz Differential Amplifier/ADC Driver                                           | A <sub>V</sub> = 12dB, Distortion < -80dBc at 25MHz                      |

| LT6402-20                                              | 300MHz Differential Amplifier/ADC Driver                                           | A <sub>V</sub> = 20dB, Distortion < -80dBc at 25MHz                      |

| LTC6404-1                                              | 600MHz, Low Noise, AC Precision, Fully Differential Input/Output Amplifier/Driver  | $A_V$ = Unity Gain, $e_n$ = 1.5nV/Hz, Distortion < $-90$ dBc at 10MHz    |

| LTC6404-2                                              | 900MHz, Low Noise, AC Precision, Fully Differential Input/Output Amplifier/Driver  | $A_V = 2V/V$ , $e_n = 1.5$ nV/Hz, Distortion < $-95$ dBc at 10MHz        |

| LTC6404-4                                              | 1800MHz, Low Noise, AC Precision, Fully Differential Input/Output Amplifier/Driver | $A_V = 4V/V$ , $e_n = 1.5$ nV/Hz, Distortion < $-98$ dBc at 10MHz        |

| LTC6406                                                | 3GHz Rail-to-Rail Input Differential Op Amp                                        | 1.6nV/√Hz Noise, −72dBc Distortion at 50MHz, 18mA                        |

| LT6411                                                 | Low Power Differential ADC Driver/Dual Selectable Gain<br>Amplifier                | 16mA Supply Current, IMD3 = -83dBc at 70MHz, A <sub>V</sub> = 1, -1 or 2 |