# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# LTC6954

### FEATURES

- Low Noise Clock Distribution: Suitable for High Speed/High Resolution ADC Clocking

- Additive Jitter < 20fs<sub>RMS</sub> (12kHz to 20MHz)

- Additive Jitter < 85fs<sub>RMS</sub> (10Hz to Nyquist)

- 1.8GHz Maximum Input Frequency (LTC6954-1 When DELAY = 0)

- 1.4GHz Maximum Input Frequency (LTC6954-1 When DELAY > 0, LTC6954-2, -3, -4)

- EZSync<sup>™</sup> Clock Synchronization Compatible

- Three Independent, Low Noise Outputs

- Four Output Combinations Available

- Three Independent Programmable Dividers Covering All Integers From 1 to 63

- Three Independent Programmable Delays Covering All Integers From 0 to 63

- –40°C to 105°C Junction Temperature Range

### **APPLICATIONS**

- Clocking High Speed, High Resolution ADCs, DACs and Data Acquisition Systems

- Low Jitter Clock Distribution

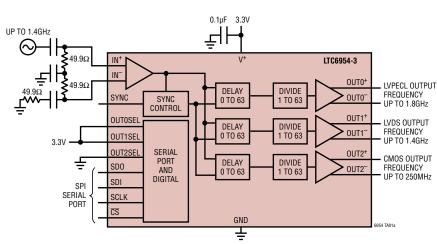

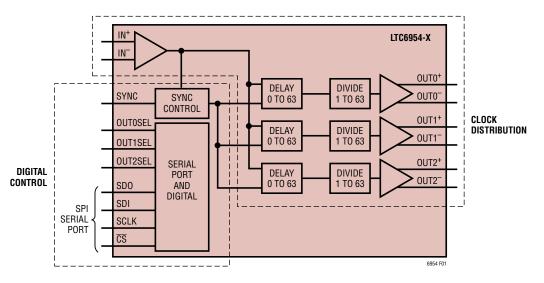

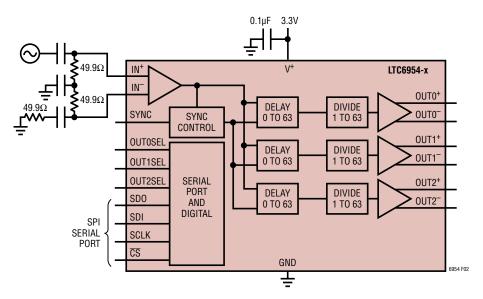

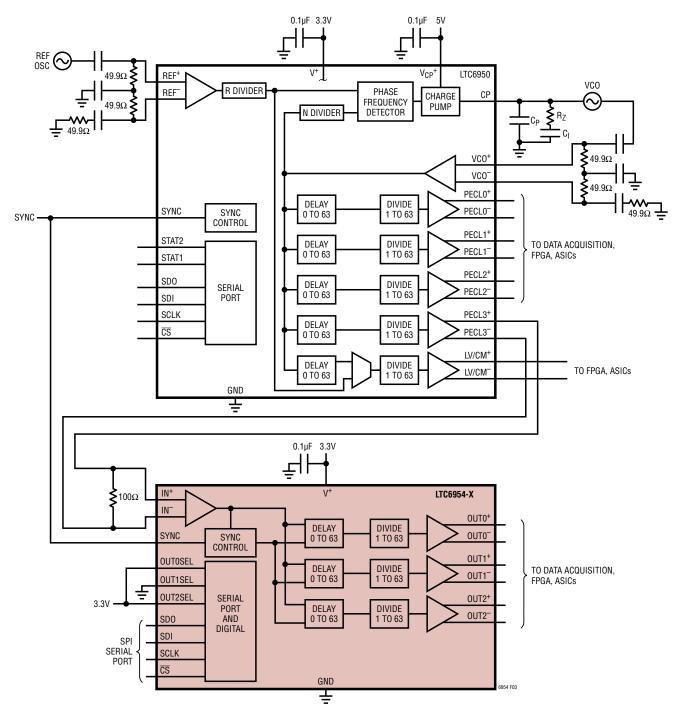

# TYPICAL APPLICATION

## Low Phase Noise, Triple Output Clock Distribution Divider/Driver **DESCRIPTION**

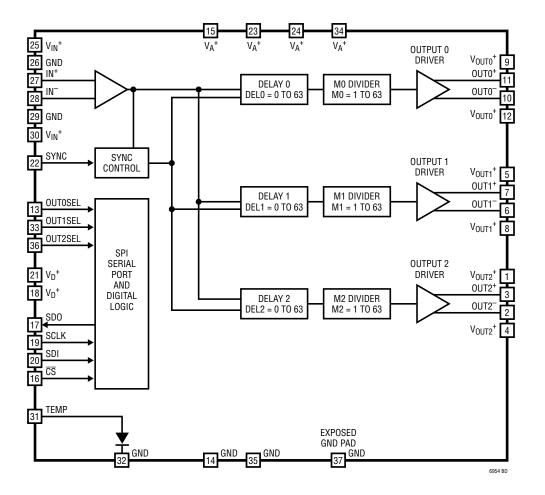

The LTC<sup>®</sup>6954 is a family of very low phase noise clock distribution parts. Each part has three outputs and each output has an individually programmable frequency divider and delay. There are four members of the family, differing in their output logic signal type:

LTC6954-1: Three LVPECL outputs

LTC6954-2: Two LVPECL and one LVDS/CMOS outputs

LTC6954-3: One LVPECL and two LVDS/CMOS outputs

#### LTC6954-4: Three LVDS/CMOS outputs

Each output is individually programmable to divide the input frequency by any integer from 1 to 63, and to delay each output by 0 to 63 input clock cycles. The output duty cycle is always 50%, regardless of the divide number. The LVDS/CMOS outputs are jumper selectable via the OUTxSEL pins to provide either an LVDS logic output or a CMOS logic output.

The LTC6954 also features Linear Technology's EZSync system for perfect clock synchronization and alignment every time.

All device settings are controlled through an SPI-compatible serial port.

TECHNOLOGY

# ABSOLUTE MAXIMUM RATINGS

#### (Note 1)

| Supply Voltages                                               |

|---------------------------------------------------------------|

| $(V_A^+, V_D^+, V_{IN}^+, V_{OUT0}^+, V_{OUT1}^+$ and         |

| V <sub>OUT2</sub> <sup>+</sup> to GND)                        |

| LTC6954-1, -2, -3 LVPECL Outputs                              |

| OUTx Output Voltage HighV <sub>OUT</sub> + + 0.3V             |

| OUTx Output Voltage Low Source 25mA                           |

| LTC6954-2, -3, -4 LVDS/CMOS Outputs                           |

| OUTx0.3V to (V <sub>A</sub> <sup>+</sup> +0.3V)               |

| TEMP Input Current10mA                                        |

| TEMP Low Voltage0.3V                                          |

| Voltage on All Other Pins $-0.3V$ to $(V_A^+ + 0.3V)$         |

| Operating Junction Temperature Range, T <sub>J</sub> (Note 2) |

| LTC6954I–40°C to 105°C                                        |

| Junction Temperature, T <sub>JMAX</sub> 150°C                 |

| Storage Temperature Range –65°C to 150°C                      |

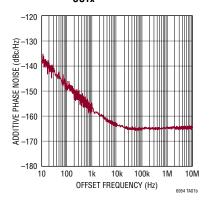

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION             | JUNCTION TEMPERATURE RANGE |

|-------------------|---------------------|--------------|---------------------------------|----------------------------|

| LTC6954IUFF-1#PBF | LTC6954IUFF-1#TRPBF | 69541        | 36-Lead (4mm × 7mm) Plastic QFN | –40°C to 105°C             |

| LTC6954IUFF-2#PBF | LTC6954IUFF-2#TRPBF | 69542        | 36-Lead (4mm × 7mm) Plastic QFN | -40°C to 105°C             |

| LTC6954IUFF-3#PBF | LTC6954IUFF-3#TRPBF | 69543        | 36-Lead (4mm × 7mm) Plastic QFN | -40°C to 105°C             |

| LTC6954IUFF-4#PBF | LTC6954IUFF-4#TRPBF | 69544        | 36-Lead (4mm × 7mm) Plastic QFN | -40°C to 105°C             |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part markings, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

6954f

| SYMBOL             | PARAMETER                                                              | CONDITIONS                                                                     |   | MIN                           | ТҮР                           | MAX                           | UNITS            |

|--------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|---|-------------------------------|-------------------------------|-------------------------------|------------------|

| Input (IN+, I      | N <sup>-</sup> )                                                       |                                                                                |   | 1                             |                               |                               |                  |

| f <sub>IN</sub>    | Input Frequency                                                        | LTC6954-1, DELx = 0<br>LTC6954-1 (DELx > 0), LTC6954-2, -3, -4                 | • |                               |                               | 1800<br>1400                  | MHz<br>MHz       |

| V <sub>IN</sub>    | Input Signal Level                                                     | Single-Ended                                                                   |   | 0.2                           | 0.8                           | 1.5                           | V <sub>P-P</sub> |

|                    | Input Slew Rate                                                        |                                                                                |   | 100                           |                               |                               | V/µs             |

| DCIN               | Input Duty Cycle                                                       |                                                                                |   |                               | 50                            |                               | %                |

|                    | Self-Bias Voltage                                                      |                                                                                |   | 1.9                           | 2.05                          | 2.2                           | V                |

|                    | Minimum Common Mode Level                                              | 400mV <sub>P-P</sub> Differential Input                                        |   |                               | 1.8                           |                               | V                |

|                    | Maximum Common Mode Level                                              | 400mV <sub>P-P</sub> Differential Input                                        |   |                               | 2.3                           |                               | V                |

|                    | Input Resistance                                                       | Differential                                                                   |   | 1.8                           | 2.2                           | 2.7                           | kΩ               |

|                    | Input Capacitance                                                      | Differential                                                                   |   |                               | 0.5                           |                               | pF               |

| Output Divid       | ier (M)                                                                |                                                                                |   |                               |                               |                               |                  |

| Mx[5:0]            | Divider Range<br>M0[5:0], M1[5:0], M2[5:0]                             | All Integers Included                                                          | • | 1                             |                               | 63                            | Cycles           |

| DELx[5:0]          | Divider Delay in Input Clock Cycles<br>DEL0[5:0], DEL1[5:0], DEL2[5:0] | All Integers Included                                                          | • | 0                             |                               | 63                            | Cycles           |

| LVPECL Clo         | ck Outputs                                                             |                                                                                |   |                               |                               |                               |                  |

| f <sub>OUT</sub>   | Frequency                                                              | LTC6954-1, DELx = 0<br>LTC6954-1 (DELx > 0), LTC6954-2, -3, -4                 | • |                               |                               | 1800<br>1400                  | MHz<br>MHz       |

| V <sub>OD</sub>    | Differential Voltage                                                   | Single-Ended Termination = $50\Omega$ to (V <sub>OUTx</sub> <sup>+</sup> - 2V) | • | 640                           | 775                           | 950                           | mV <sub>PK</sub> |

|                    | (Output Static)                                                        | Differential Termination = $100\Omega$ , Internal Bias On                      |   | 640                           | 780                           | 950                           | mV <sub>PK</sub> |

| V <sub>CM</sub>    | Common Mode Voltage<br>(Output Static)                                 | Single-Ended Termination = $50\Omega$ to (V <sub>OUTx</sub> <sup>+</sup> - 2V) | • | V <sub>OUTx</sub> +<br>- 1.67 | V <sub>OUTx</sub> +<br>- 1.42 | V <sub>OUTx</sub> +<br>- 1.14 | V                |

|                    |                                                                        | Differential Termination = $100\Omega$ , Internal Bias On                      | • | V <sub>OUTx</sub> +<br>- 1.67 | V <sub>OUTx</sub> +<br>- 1.42 | V <sub>OUTx</sub> +<br>- 1.14 | V                |

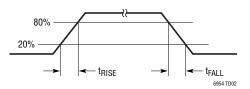

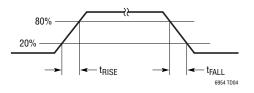

| t <sub>RISE</sub>  | Rise Time, 20% to 80%                                                  | Single-Ended Termination = $50\Omega$ to (V <sub>OUTx</sub> <sup>+</sup> - 2V) |   |                               | 110                           |                               | ps               |

|                    |                                                                        | Differential Termination = $100\Omega$ , Internal Bias On                      |   |                               | 110                           |                               | ps               |

| t <sub>FALL</sub>  | Fall Time, 80% to 20%                                                  | Single-Ended Termination = $50\Omega$ to (V <sub>OUTx</sub> <sup>+</sup> - 2V) |   |                               | 110                           |                               | ps               |

|                    |                                                                        | Differential Termination = $100\Omega$ , Internal Bias On                      |   |                               | 110                           |                               | ps               |

| DCLVPECL           | Duty Cycle                                                             | Mx[5:0] = 1                                                                    |   |                               | DCIN                          |                               | %                |

|                    |                                                                        | Mx[5:0] > 1 (Even or Odd)                                                      |   | 45                            | 50                            | 55                            | %                |

| CMOS Clock         | c Outputs                                                              |                                                                                |   |                               |                               |                               |                  |

| f <sub>OUT</sub>   | Frequency                                                              |                                                                                |   |                               |                               | 250                           | MHz              |

| V <sub>OH</sub>    | High Voltage (Output Static)                                           | 2.5mA Load                                                                     |   | V <sup>+</sup> - 0.4          |                               |                               | V                |

| V <sub>OL</sub>    | Low Voltage (Output Static)                                            | 2.5mA Load                                                                     |   |                               |                               | 0.4                           | V                |

| t <sub>RISE</sub>  | Rise Time, 20% to 80%                                                  | $C_{LOAD} = 2pF, CMSINV = 1$                                                   |   |                               | 200                           |                               | ps               |

| t <sub>FALL</sub>  | Fall Time, 80% to 20%                                                  | $C_{LOAD} = 2pF, CMSINV = 1$                                                   |   |                               | 170                           |                               | ps               |

| DC <sub>CMOS</sub> | Duty Cycle                                                             | Mx[5:0] = 1                                                                    |   |                               | DCIN                          |                               | %                |

|                    |                                                                        | Mx[5:0] > 1 (Even or Odd)                                                      |   | 45                            | 50                            | 55                            | %                |

| SYMBOL                              | PARAMETER                                                                  | CONDITIONS                                          |   | MIN  | ТҮР              | MAX  | UNITS            |

|-------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------|---|------|------------------|------|------------------|

| LVDS Clock                          | Outputs                                                                    |                                                     |   |      |                  |      |                  |

| f <sub>OUT</sub>                    | Frequency                                                                  | Differential Termination = $100\Omega$ , 3.5mA Mode |   |      |                  | 800  | MHz              |

|                                     |                                                                            | Differential Termination = $50\Omega$ , 7mA Mode    | • |      |                  | 1400 | MHz              |

| V <sub>OD</sub>                     | Differential Voltage                                                       | Differential Termination = $100\Omega$ , 3.5mA Mode | • | 290  | 370              | 450  | mV <sub>PK</sub> |

|                                     | (Output Static)                                                            | Differential Termination = $50\Omega$ , 7mA Mode    | • | 290  | 370              | 450  | mV <sub>PK</sub> |

| ΔV <sub>OD</sub>                    | Delta V <sub>OD</sub> (Output Static)                                      | Differential Termination = $100\Omega$ , 3.5mA Mode |   | -30  |                  | 30   | mV               |

|                                     |                                                                            | Differential Termination = $50\Omega$ , 7mA Mode    |   | -30  |                  | 30   | mV               |

| V <sub>OS</sub>                     | Offset Voltage (Output Static)                                             | Differential Termination = $100\Omega$ , 3.5mA Mode |   | 1.16 | 1.23             | 1.32 | V                |

|                                     |                                                                            | Differential Termination = $50\Omega$ , 7mA Mode    | • | 1.15 | 1.23             | 1.32 | V                |

| $ \Delta V_{OS} $                   | Delta V <sub>OS</sub> (Output Static)                                      | Differential Termination = $100\Omega$ , 3.5mA Mode | • | -15  |                  | 15   | mV               |

|                                     |                                                                            | Differential Termination = $50\Omega$ , 7mA Mode    |   | -15  |                  | 15   | mV               |

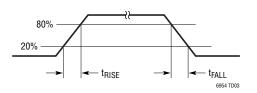

| t <sub>RISE</sub>                   | Rise Time, 20% to 80%                                                      | Differential Termination = $100\Omega$ , 3.5mA Mode |   |      | 240              |      | ps               |

|                                     |                                                                            | Differential Termination = $50\Omega$ , 7mA Mode    |   |      | 120              |      | ps               |

| t <sub>FALL</sub>                   | Fall Time, 80% to 20%                                                      | Differential Termination = $100\Omega$ , 3.5mA Mode |   |      | 240              |      | ps               |

|                                     |                                                                            | Differential Termination = $50\Omega$ , 7mA Mode    |   |      | 120              |      | ps               |

| I <sub>SA</sub>  ,  I <sub>SB</sub> | Short-Circuit Current to Common                                            | Shorted to GND, 3.5mA Mode                          |   |      | 16               |      | mA               |

|                                     |                                                                            | Shorted to GND, 7mA Mode                            |   |      | 25               |      | mA               |

| I <sub>SAB</sub>                    | Short-Circuit Current to                                                   | 3.5mA Mode                                          |   |      | 4                |      | mA               |

|                                     | Complementary                                                              | 7mA Mode                                            |   |      | 8                |      | mA               |

| DC <sub>LVDS</sub>                  | Duty Cycle                                                                 | Mx[5:0] = 1                                         |   |      | DC <sub>IN</sub> |      | %                |

|                                     |                                                                            | Mx[5:0] > 1 (Even or Odd)                           | • | 45   | 50               | 55   | %                |

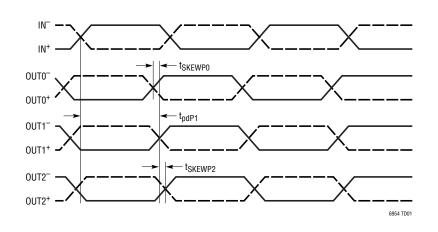

| Output Propa                        | agation Delays                                                             |                                                     |   |      |                  |      |                  |

| t <sub>PD(LVPECL)</sub>             | Propagation Delay From IN to                                               | Mx[5:0] = 1                                         | ٠ | 290  | 360              | 480  | ps               |

|                                     | Any LVPECL Output<br>Temperature Variation of the                          | Mx[5:0] > 1                                         | ٠ | 360  | 430              | 550  | ps               |

|                                     |                                                                            | Mx[5:0] = 1                                         | ٠ |      | 0.65             |      | ps/°C            |

|                                     | Propagation Delay From IN to<br>Any LVPECL Output                          | Mx[5:0] > 1                                         | • |      | 0.68             |      | ps/°C            |

| t <sub>pd(LVDS)</sub>               | Propagation Delay From IN to                                               | Mx[5:0] = 1                                         | • | 350  | 420              | 545  | ps               |

|                                     | Any LVDS Output,<br>LVCSx = 1 (7mA Mode)                                   | Mx[5:0] > 1                                         | • | 415  | 480              | 625  | ps               |

|                                     | Temperature Variation of the                                               | Mx[5:0] = 1                                         | • |      | 0.8              |      | ps/°C            |

|                                     | Propagation Delay From IN to<br>Any LVDS Output,<br>LVCSx = 1 (7mA Mode)   | Mx[5:0] > 1                                         | • |      | 0.85             |      | ps/°C            |

|                                     | Propagation Delay From IN to                                               | Mx[5:0] = 1                                         | _ |      | 480              |      | ps               |

|                                     | Any LVDS Output,<br>LVCSx = 0 (3.5mA Mode)                                 | Mx[5:0] > 1                                         |   |      | 550              |      | ps               |

|                                     | Temperature Variation of the                                               | Mx[5:0] = 1                                         | • |      | 0.8              |      | ps/°C            |

|                                     | Propagation Delay From IN to<br>Any LVDS Output,<br>LVCSx = 0 (3.5mA Mode) | Mx[5:0] > 1                                         | • |      | 0.85             |      | ps/°C            |

| t <sub>pd(CMOS)</sub>               | Propagation Delay From IN to                                               | Mx[5:0] = 1                                         |   |      | 1.25             |      | ns               |

| -2(000)                             | Any CMOS Output, Complementary<br>Outputs (CMSINVx = 1)                    | Mx[5:0] > 1                                         |   |      | 1.32             |      | ns               |

|                                     | Temperature Variation of the                                               | Mx[5:0] = 1                                         | • |      | 1.3              |      | ps/°C            |

|                                     | Propagation Delay From IN to                                               | [Mix[0:0] = 1                                       | - |      |                  |      |                  |

6954f

| SYMBOL            | PARAMETER                                                                                                           | CONDITIONS                                                                                                                                                     |   | MIN | ТҮР | MAX | UNITS |

|-------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|-------|

| Output Ske        | ews                                                                                                                 |                                                                                                                                                                |   |     |     |     |       |

|                   | Skew: Any LVPECL Output to<br>Any LVPECL Output                                                                     | Mx[5:0], My[5:0] Both = 1 or Both > 1<br>IBIASx = 0 or 1                                                                                                       | • | -50 |     | 50  | ps    |

|                   | Skew: Any LVPECL Output to<br>Any LVDS Output                                                                       | M <sub>LVPECL</sub> [5:0], M <sub>LVDS</sub> [5:0] Both = 1 or Both > 1<br>IBIASx = 0 or 1, LVCSy = 1                                                          |   |     | 65  |     | ps    |

|                   | Skew: Any LVPECL Output to<br>Any LVDS Output                                                                       | $ \begin{aligned} M_{\text{LVPECL}}[5:0] &= M_{\text{LVDS}}[5:0] = 1 \text{ or Both} > 1 \\ \text{IBIASx} &= 0 \text{ or } 1, \text{LVCSx} = 0 \end{aligned} $ |   |     | 120 |     | ps    |

|                   | Skew: Any LVPECL Output to<br>Any CMOS Output                                                                       | $M_{LVPECL}[5:0]$ , $M_{CMOS}[5:0]$ Both = 1 or Both > 1<br>IBIASx = 0 or 1, CMSINVy = 1                                                                       |   |     | 875 |     | ps    |

|                   | Skew: Any LVDS Output to<br>Any LVDS Output                                                                         | Mx[5:0], My[5:0] Both = 1 or Both > 1<br>LVCSx = 1 for Both Outputs                                                                                            | • | -50 |     | 50  | ps    |

| t <sub>SKEW</sub> | Skew: Any LVDS Output to<br>Any LVDS Output                                                                         | Mx[5:0], My[5:0] Both = 1 or Both > 1<br>LVCSx = 0 for Both Outputs                                                                                            |   |     | 5   |     | ps    |

| SKEW              | Skew: Any LVDS Output (LVCSx = 1) to<br>Any LVDS Output (LVCSy = 0)                                                 | Mx[5:0], My[5:0] Both = 1 or Both > 1<br>LVCSx = 1, LVCSy = 0                                                                                                  |   |     | 50  |     | ps    |

|                   | Skew: Any LVDS Output to<br>Any CMOS Output                                                                         | M <sub>LVDS</sub> [5:0], M <sub>CMOS</sub> [5:0] Both = 1 or Both > 1<br>LVCSx = 1, CMSINV = 1                                                                 |   |     | 800 |     | ps    |

|                   | Skew: Any CMOS Output to<br>Any CMOS Output                                                                         | Mx[5:0], My[5:0] Both = 1 or Both > 1<br>CMSINV = 1                                                                                                            |   |     | 5   |     | ps    |

|                   | Skew: Any CMOS Output to<br>Any CMOS Output, the First Output is<br>Complementary, the Second Output is<br>In-Phase | CMSINVx = 1, CMSINVy = 0                                                                                                                                       |   |     | 30  |     | ps    |

|                   | Additional Skew: Any Output to Any<br>Output, Dividers Not the Same                                                 | Mx[5:0] = 1, My[5:0] > 1                                                                                                                                       | • | 35  | 70  | 120 | ps    |

| SYMBOL    | PARAMETER                                                                                                                 | CONDITIONS                                                                                                                                                                                                                                                                        |   | MIN  | ТҮР | MAX  | UNITS |

|-----------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----|------|-------|

| Supply Vo | oltages                                                                                                                   |                                                                                                                                                                                                                                                                                   |   |      |     |      | ·     |

|           | V <sub>A</sub> <sup>+</sup> Supply Range                                                                                  |                                                                                                                                                                                                                                                                                   | • | 3.15 | 3.3 | 3.45 | V     |

|           | V <sub>D</sub> <sup>+</sup> Supply Range                                                                                  |                                                                                                                                                                                                                                                                                   | • | 3.15 | 3.3 | 3.45 | V     |

|           | V <sub>IN</sub> <sup>+</sup> Supply Range                                                                                 |                                                                                                                                                                                                                                                                                   | ٠ | 3.15 | 3.3 | 3.45 | V     |

|           | V <sub>OUTO</sub> <sup>+</sup> , V <sub>OUT1</sub> <sup>+</sup> , V <sub>OUT2</sub> <sup>+</sup> Supply<br>Range          |                                                                                                                                                                                                                                                                                   | • | 3.15 | 3.3 | 3.45 | V     |

| Supply Cu | irrent (Sum of V <sub>A</sub> <sup>+</sup> , V <sub>D</sub> <sup>+</sup> , V <sub>IN</sub> <sup>+</sup> , V <sub>OU</sub> | T0 <sup>+</sup> , V <sub>OUT1</sub> <sup>+</sup> , V <sub>OUT2</sub> <sup>+</sup> Supply Currents)                                                                                                                                                                                |   |      |     |      |       |

|           | LTC6954-1                                                                                                                 | $f_{IN}$ = 1400MHz, Power-Up Default Configuration,<br>OUTOSEL = OUT1SEL = OUT2SEL = V <sub>A</sub> <sup>+</sup> ,<br>IBIAS On for All Outputs,<br>Outputs Terminated with 100 $\Omega$ Differential                                                                              | • |      | 300 | 335  | mA    |

|           |                                                                                                                           | $f_{IN}$ = 1400MHz, Power-Up Default Configuration,<br>OUT0SEL = OUT1SEL = OUT2SEL = GND,<br>IBIAS Off for All Outputs,<br>Outputs Terminated with 50 $\Omega$ to (V <sub>OUTx</sub> <sup>+</sup> - 2V)                                                                           | • |      | 310 | 350  | mA    |

|           | LTC6954-2                                                                                                                 | $f_{IN} = 1400MHz$ , Power-Up Default Configuration,<br>OUTOSEL = OUT1SEL = OUT2SEL = V <sub>A</sub> <sup>+</sup> ,<br>IBIAS On for LVPECL Outputs,<br>LVDS/CMOS = LVDS,<br>Outputs Terminated with 100 $\Omega$ Differential                                                     | • |      | 290 | 325  | mA    |

|           |                                                                                                                           | $f_{IN}$ = 1400MHz, Power-Up Default Configuration,<br>OUT0SEL = OUT1SEL = V <sub>A</sub> <sup>+</sup> , OUT2SEL = GND,<br>IBIAS On for LVPECL Outputs,<br>LVDS/CMOS = CMOS, M2[5:0] = 28, f <sub>OUT2</sub> = 50MHz,<br>LVPECL Outputs Terminated with 100 $\Omega$ Differential | • |      | 280 | 320  | mA    |

|           | LTC6954-3                                                                                                                 | $f_{IN} = 1400MHz$ , Power-Up Default Configuration,<br>OUTOSEL = OUT1SEL = OUT2SEL = $V_A^+$ ,<br>IBIAS On for LVPECL Output,<br>LVDS/CMOS = LVDS,<br>Outputs Terminated with 100 $\Omega$ Differential                                                                          | • |      | 280 | 320  | mA    |

|           |                                                                                                                           | $      f_{IN} = 1400 MHz, Power-Up Default Configuration, \\ OUTOSEL = V_A^+, OUT1SEL = OUT2SEL = GND, \\ IBIAS On for LVPECL Output, \\ LVDS/CMOS = CMOS, M1[5:0] = M2[5:0] = 28, \\ f_{OUT1} = f_{OUT2} = 50 MHz, \\ LVPECL Output Terminated with 100 \Omega Differential $    |   |      | 278 | 315  | mA    |

|           | LTC6954-4                                                                                                                 | $ \begin{array}{l} f_{IN} = 1400 \text{MHz}, \text{ Power-Up Default Configuration, OUTOSEL} \\ = 0 \text{UT1SEL} = 0 \text{UT2SEL} = \text{V}_{\text{A}}^+, \\ \text{LVDS/CMOS} = \text{LVDS}, \\ \text{Outputs Terminated with 100} \Omega \text{ Differential} \end{array} $   | • |      | 270 | 315  |       |

|           |                                                                                                                           | $      f_{\text{IN}} = 1400 \text{MHz}, \text{Power-Up Default Configuration, OUTOSEL} \\ = 0UT1SEL = 0UT2SEL = GND, \\ \text{LVDS/CMOS} = CMOS, M0[5:0], M1[5:0] = M2[5:0] = 28, \\ f_{\text{OUT0}} = f_{\text{OUT1}} = f_{\text{OUT2}} = 50 \text{MHz}      $                   | • |      | 282 | 310  | mA    |

|           | ALL LTC6954 Variants                                                                                                      | $P_{D(ALL)} = 1$                                                                                                                                                                                                                                                                  |   |      | 0.8 |      | mA    |

| SYMBOL             | PARAMETER                                   | CONDITIONS                                                                     |   | MIN  | ТҮР  | MAX  | UNITS    |

|--------------------|---------------------------------------------|--------------------------------------------------------------------------------|---|------|------|------|----------|

| Supply Cu          | irrent Delta (Note 3)                       | · ·                                                                            |   |      |      | -    | <u> </u> |

|                    | Output Divider On, LVPECL                   | PD_DIVx = 0, Mx[5:0] = 1, PD_0UTx = 1                                          | • |      | 28   | 32   | mA       |

|                    | Output                                      | PD_DIVx = 0, Mx[5:0] > 1, PD_OUTx = 1                                          | • |      | 46   | 54   | mA       |

|                    | Output Driver Only, LVPECL                  | PD_OUTx = 0, Termination = $50\Omega$ to (V <sub>OUTx</sub> <sup>+</sup> - 2V) | • |      | 43   | 50   | mA       |

|                    |                                             | PD_OUTx = 0, IBIASx = 1 (Internal Bias On)                                     | • |      | 39   | 46   | mA       |

|                    |                                             | PD_OUTx = 0, No Internal/External Bias                                         | • |      | 19   | 24   | mA       |

|                    | Output Driver Only, LVDS                    | PD_OUTx = 0, 3.5mA Mode, LVCSx = 0                                             | • |      | 31   | 37   | mA       |

|                    |                                             | PD_OUTx = 0, 7mA Mode, LVCSx = 1                                               | • |      | 48   | 58   | mA       |

|                    | Output Driver Only, CMOS                    | PD_OUTx = 0, CMOS at 50MHz                                                     | • |      | 35   | 43   | mA       |

| Digital In         | puts ( <del>CS</del> , SDI, SCLK, SYNC, OUT | OSEL, OUT1SEL, OUT2SEL)                                                        |   |      |      |      |          |

| V <sub>IH</sub>    | Input High Voltage                          |                                                                                | • | 1.55 |      |      | V        |

| V <sub>IL</sub>    | Input Low Voltage                           |                                                                                | • |      |      | 0.8  | V        |

| V <sub>IHYS</sub>  | Input Voltage Hysteresis                    | CS, SDI and SCLK Only                                                          |   |      | 250  |      | mV       |

|                    | Input Current                               |                                                                                | • | -1   |      | 1    | μA       |

| Digital Ou         | ıtputs (SDO)                                |                                                                                |   |      |      |      |          |

| I <sub>OH</sub>    | High Level Output Current                   | SDO, $V_{OH} = V_{D}^{+} - 400 \text{mV}$                                      | • |      | -2.4 | -1.5 | mA       |

| I <sub>OL</sub>    | Low Level Output Current                    | SD0, V <sub>0L</sub> = 400mV                                                   | • | 2.2  | 3.4  |      | mA       |

|                    | SDO Hi-Z Current                            |                                                                                | • | -1   |      | 1    | μA       |

| Digital Ti         | ming Specifications (See Figure             | 11 and Figure 12)                                                              |   |      |      |      |          |

| t <sub>CKH</sub>   | SCLK HIGH Pulse Width                       |                                                                                | • | 25   |      |      | ns       |

| t <sub>CKL</sub>   | SCLK LOW Pulse Width                        |                                                                                | • | 25   |      |      | ns       |

| t <sub>CSS</sub>   | CS Setup Time                               |                                                                                | • | 10   |      |      | ns       |

| t <sub>CSH</sub>   | CS HIGH Pulse Width                         |                                                                                | • | 10   |      |      | ns       |

| t <sub>CS</sub>    | SDI to SCLK Setup Time                      |                                                                                | • | 6    |      |      | ns       |

| t <sub>CH</sub>    | SDI to SCLK Hold Time                       |                                                                                | • | 6    |      |      | ns       |

| t <sub>DO</sub>    | SDO Propagation Delay                       | C <sub>LOAD</sub> = 10pF                                                       |   |      | 16   |      | ns       |

| t <sub>SYNCH</sub> | SYNC HIGH Pulse Width                       |                                                                                | • | 1    |      |      | ms       |

| t <sub>SYNCL</sub> | Minimum SYNC LOW Pulse<br>Width             | Before Next SYNC HIGH Pulse                                                    |   |      | 1    |      | ms       |

For more information www.linear.com/LTC6954

| MBOL   | PARAMETER                                                                        | CONDITIONS                              | MIN TYP MAX | UNITS            |

|--------|----------------------------------------------------------------------------------|-----------------------------------------|-------------|------------------|

| PECL / | Additive Phase Noise/Time Jitter (Note 5)                                        |                                         |             |                  |

|        | Phase Noise:                                                                     | 10Hz Offset                             | -130        | dBc/H            |

|        | $f_{IN} = 622.08MHz, Mx[5:0] = 1, f_{OUT} = 622.08MHz$                           | 100Hz Offset                            | -139        | dBc/H            |

|        |                                                                                  | 1kHz Offset                             | -148        | dBc/H            |

|        |                                                                                  | 10kHz Offset                            | -156        | dBc/H            |

|        |                                                                                  | 100kHz Offset                           | -158        | dBc/H            |

|        |                                                                                  | >1MHz Offset                            | -158        | dBc/H            |

|        | Jitter:                                                                          | 12kHz to 20MHz Integration Bandwidth    | 20          | fs <sub>RM</sub> |

|        | $f_{IN} = 622.08MHz, Mx[5:0] = 1, f_{OUT} = 622.08MHz$                           | 10Hz to 311.04MHz Integration Bandwidth | 80          | fs <sub>RM</sub> |

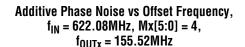

|        | Phase Noise:                                                                     | 10Hz Offset                             | -138        | dBc/H            |

|        | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 155.52MHz           | 100Hz Offset                            | -147        | dBc/H            |

|        | 1ki                                                                              | 1kHz Offset                             | -156        | dBc/H            |

|        |                                                                                  | 10kHz Offset                            | -163        | dBc/H            |

|        |                                                                                  | 100kHz Offset                           | -165        | dBc/H            |

|        |                                                                                  | >1MHz Offset                            | -165        | dBc/H            |

|        | Jitter:                                                                          | 12kHz to 20MHz Integration Bandwidth    | 36          | fs <sub>RM</sub> |

|        | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 155.52MHz           | 10Hz to 77.75MHz Integration Bandwidth  | 72          | fs <sub>RM</sub> |

|        | Phase Noise:                                                                     | 10Hz Offset                             | -147        | dBc/H            |

|        | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 16, f <sub>OUT</sub> = 38.88MHz           | 100Hz Offset                            | -159        | dBc/H            |

|        |                                                                                  | 1kHz Offset                             | -167        | dBc/H            |

|        |                                                                                  | 10kHz Offset                            | -170        | dBc/H            |

|        |                                                                                  | 100kHz Offset                           | -171        | dBc/H            |

|        |                                                                                  | >1MHz Offset                            | -171        | dBc/H            |

|        | Phase Noise:                                                                     | 10Hz Offset                             | -137        | dBc/H            |

|        | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 245.76MHz           | 100Hz Offset                            | -147        | dBc/H            |

|        |                                                                                  | 1kHz Offset                             | -156        | dBc/H            |

|        |                                                                                  | 10kHz Offset                            | -161        | dBc/H            |

|        |                                                                                  | 100kHz Offset                           | -162        | dBc/H            |

|        |                                                                                  | >1MHz Offset                            | -162        | dBc/H            |

|        | Jitter:                                                                          | 12kHz to 20MHz Integration Bandwidth    | 33          | fs <sub>RM</sub> |

|        | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 245.76MHz           | 10Hz to 122.88MHz Integration Bandwidth | 81          | fs <sub>RM</sub> |

|        | Phase Noise:                                                                     | 10Hz Offset                             | -140        | dBc/H            |

|        | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 61.44MHz            | 100Hz Offset                            | -153        | dBc/H            |

|        |                                                                                  | 1kHz Offset                             | -161        | dBc/H            |

|        |                                                                                  | 10kHz Offset                            | -166        | dBc/H            |

|        |                                                                                  | 100kHz Offset                           | -168        | dBc/H            |

|        |                                                                                  | >1MHz Offset                            | -168        | dBc/H            |

|        | Jitter:<br>f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 61.44MHz | 12kHz to 20MHz Integration Bandwidth    | 65          | fs <sub>RM</sub> |

6954f

| SYMBOL  | PARAMETER                                                              | CONDITIONS                              | MIN TYP MAX | UNITS              |

|---------|------------------------------------------------------------------------|-----------------------------------------|-------------|--------------------|

| VPECL / | Additive Phase Noise/Time Jitter (Note 5)                              |                                         |             | -                  |

|         | Phase Noise:                                                           | 10Hz Offset                             | -126        | dBc/Hz             |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 1400MHz     | 100Hz Offset                            | -132        | dBc/Hz             |

|         |                                                                        | 1kHz Offset                             | -143        | dBc/Hz             |

|         |                                                                        | 10kHz Offset                            | -149        | dBc/H              |

|         |                                                                        | 100kHz Offset                           | -152.5      | dBc/Hz             |

|         |                                                                        | >1MHz Offset                            | -152.5      | dBc/H              |

|         | Jitter:                                                                | 12kHz to 20MHz Integration Bandwidth    | 17          | fs <sub>RMS</sub>  |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 1400MHz     | 10Hz to 700MHz Integration Bandwidth    | 100         | fs <sub>RM</sub> s |

|         | Phase Noise:                                                           | 10Hz Offset                             | -132        | dBc/H              |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 350MHz      | 100Hz Offset                            | -139        | dBc/H              |

|         |                                                                        | 1kHz Offset                             | -151        | dBc/Hz             |

|         |                                                                        | 10kHz Offset                            | -157        | dBc/H              |

|         |                                                                        | 100kHz Offset                           | -160        | dBc/H              |

|         |                                                                        | >1MHz Offset                            | -160        | dBc/H              |

|         | Jitter:                                                                | 12kHz to 20MHz Integration Bandwidth    | 29          | fs <sub>RM</sub>   |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 350MHz      | 10Hz to 175MHz Integration Bandwidth    | 85          | fs <sub>RM</sub>   |

| DS Ad   | ditive Phase Noise/Time Jitter LVCS = 1 (Note 5)                       | · · · · · ·                             |             |                    |

|         | Phase Noise:                                                           | 10Hz Offset                             | -130        | dBc/H              |

|         | $f_{IN} = 622.08MHz, Mx[5:0] = 1, f_{OUT} = 622.08MHz$                 | 100Hz Offset                            | -138        | dBc/H              |

|         |                                                                        | 1kHz Offset                             | -148        | dBc/H              |

|         |                                                                        | 10kHz Offset                            | -156        | dBc/H              |

|         |                                                                        | 100kHz Offset                           | -157.5      | dBc/H              |

|         |                                                                        | >1MHz Offset                            | -157.5      | dBc/H              |

|         | Jitter:                                                                | 12kHz to 20MHz Integration Bandwidth    | 21          | fs <sub>RM</sub>   |

|         | $f_{IN} = 622.08MHz, Mx[5:0] = 1, f_{OUT} = 622.08MHz$                 | 10Hz to 311.04MHz Integration Bandwidth | 83          | fs <sub>RMS</sub>  |

|         | Phase Noise:                                                           | 10Hz Offset                             | -140        | dBc/H              |

|         | $f_{IN} = 622.08MHz, Mx[5:0] = 4, f_{OUT} = 155.52MHz$                 | 100Hz Offset                            | -147        | dBc/H              |

|         |                                                                        | 1kHz Offset                             | -157        | dBc/H              |

|         |                                                                        | 10kHz Offset                            | -163        | dBc/H              |

|         |                                                                        | 100kHz Offset                           | -165        | dBc/H              |

|         |                                                                        | >1MHz Offset                            | -165        | dBc/H              |

|         | Jitter:                                                                | 12kHz to 20MHz Integration Bandwidth    | 36          | fs <sub>RM</sub>   |

|         | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 155.52MHz | 10Hz to 77.75MHz Integration Bandwidth  | 72          | fs <sub>RMS</sub>  |

|         | Phase Noise:                                                           | 10Hz Offset                             | -147        | dBc/H              |

|         | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 16, f <sub>OUT</sub> = 38.88MHz | 100Hz Offset                            | -159        | dBc/Hz             |

|         |                                                                        | 1kHz Offset                             | -166        | dBc/H              |

|         |                                                                        | 10kHz Offset                            | -170        | dBc/Hz             |

|         |                                                                        | 100kHz Offset                           | -170        | dBc/Hz             |

|         |                                                                        | >1MHz Offset                            | -170        | dBc/Hz             |

| SYMBOL  | PARAMETER                                                                       | CONDITIONS                              | MIN TYP MAX | UNITS             |

|---------|---------------------------------------------------------------------------------|-----------------------------------------|-------------|-------------------|

| LVDS Ad | ditive Phase Noise/Time Jitter LVCS = 1 (Note 5)                                |                                         | ·           |                   |

|         | Phase Noise:                                                                    | 10Hz Offset                             | -138        | dBc/Hz            |

|         | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 245.76MHz          | 100Hz Offset                            | -146        | dBc/Hz            |

|         |                                                                                 | 1kHz Offset                             | -155        | dBc/Hz            |

|         |                                                                                 | 10kHz Offset                            | -160        | dBc/Hz            |

|         |                                                                                 | 100kHz Offset                           | -162        | dBc/Hz            |

|         |                                                                                 | >1MHz Offset                            | -162        | dBc/Hz            |

|         | Jitter:                                                                         | 12kHz to 20MHz Integration Bandwidth    | 34          | fs <sub>RMS</sub> |

|         | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 245.76MHz          | 10Hz to 122.88MHz Integration Bandwidth | 83          | fs <sub>RMS</sub> |

|         | Phase Noise:                                                                    | 10Hz Offset                             | -142        | dBc/Hz            |

|         | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 61.44MHz           | 100Hz Offset                            | -153        | dBc/Hz            |

|         |                                                                                 | 1kHz Offset                             | -162        | dBc/Hz            |

|         |                                                                                 | 10kHz Offset                            | -167        | dBc/Hz            |

|         |                                                                                 | 100kHz Offset                           | -168        | dBc/Hz            |

|         |                                                                                 | >1MHz Offset                            | -168        | dBc/Hz            |

|         | Jitter:<br>f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 61.4MHz | 12kHz to 20MHz Integration Bandwidth    | 65          | fs <sub>RMS</sub> |

|         | Phase Noise:                                                                    | 10Hz Offset                             | -121        | dBc/Hz            |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 1400MHz              | 100Hz Offset                            | -133        | dBc/Hz            |

|         |                                                                                 | 1kHz Offset                             | -142        | dBc/Hz            |

|         |                                                                                 | 10kHz Offset                            | -148        | dBc/Hz            |

|         |                                                                                 | 100kHz Offset                           | -152        | dBc/Hz            |

|         |                                                                                 | >1MHz Offset                            | -152        | dBc/Hz            |

|         | Jitter:                                                                         | 12kHz to 20MHz Integration Bandwidth    | 18          | fs <sub>RMS</sub> |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 1, f <sub>OUT</sub> = 1400MHz              | 10Hz to 700MHz Integration Bandwidth    | 109         | fs <sub>RMS</sub> |

|         | Phase Noise:                                                                    | 10Hz Offset                             | -129        | dBc/Hz            |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 350MHz               | 100Hz Offset                            | -137        | dBc/Hz            |

|         |                                                                                 | 1kHz Offset                             | -148        | dBc/Hz            |

|         |                                                                                 | 10kHz Offset                            | -156        | dBc/Hz            |

|         |                                                                                 | 100kHz Offset                           | -159        | dBc/Hz            |

|         |                                                                                 | >1MHz Offset                            | -160        | dBc/Hz            |

|         | Jitter:                                                                         | 12kHz to 20MHz Integration Bandwidth    | 30          | fs <sub>RMS</sub> |

|         | f <sub>IN</sub> = 1400MHz, Mx[5:0] = 4, f <sub>OUT</sub> = 350MHz               | 10Hz to 175MHz Integration Bandwidth    | 90          | fs <sub>RMS</sub> |

6954f

| SYMBOL   | PARAMETER                                              | CONDITIONS                              | M | IN TY | Р  | MAX | UNITS             |

|----------|--------------------------------------------------------|-----------------------------------------|---|-------|----|-----|-------------------|

| LVDS Add | ditive Phase Noise/Time Jitter LVCS = 0 (Note 5)       |                                         |   |       |    |     | <u> </u>          |

|          | Phase Noise:                                           | 10Hz Offset                             |   | -12   | 23 |     | dBc/Hz            |

|          | $f_{IN} = 622.08MHz, Mx[5:0] = 1, f_{OUT} = 622.08MHz$ | 100Hz Offset                            |   | -13   | 35 |     | dBc/Hz            |

|          |                                                        | 1kHz Offset                             |   | -14   | 46 |     | dBc/Hz            |

|          |                                                        | 10kHz Offset                            |   | -15   | 51 |     | dBc/Hz            |

|          |                                                        | 100kHz Offset                           |   | -15   | 53 |     | dBc/Hz            |

|          |                                                        | >1MHz Offset                            |   | -15   | 53 |     | dBc/Hz            |

|          |                                                        | 12kHz to 20MHz Integration Bandwidth    |   | 36    | 3  |     | fs <sub>RMS</sub> |

|          | $f_{IN} = 622.08MHz, Mx[5:0] = 1, f_{OUT} = 622.08MHz$ | 10Hz to 311.04MHz Integration Bandwidth |   | 14    | 0  |     | fs <sub>RMS</sub> |

|          | Phase Noise:                                           | 10Hz Offset                             |   | -13   | 35 |     | dBc/Hz            |

|          | $f_{IN} = 622.08MHz, Mx[5:0] = 4, f_{OUT} = 155.52MHz$ | 100Hz Offset                            |   | -14   | 16 |     | dBc/Hz            |

|          |                                                        | 1kHz Offset                             |   | -15   | 54 |     | dBc/Hz            |

|          |                                                        | 10kHz Offset                            |   | -16   | 30 |     | dBc/Hz            |

|          |                                                        | 100kHz Offset                           |   | -16   | 31 |     | dBc/Hz            |

|          |                                                        | >1MHz Offset                            |   | -16   | 31 |     | dBc/Hz            |

|          | Jitter:                                                | 12kHz to 20MHz Integration Bandwidth    |   | 29    | )  |     | fs <sub>RMS</sub> |

|          | $f_{IN} = 622.08MHz, Mx[5:0] = 4, f_{OUT} = 155.52MHz$ | 10Hz to 77.75MHz Integration Bandwidth  |   | 11    | 4  |     | fs <sub>RMS</sub> |

|          | Phase Noise:                                           | 10Hz Offset                             |   | -14   | 17 |     | dBc/Hz            |

|          | $f_{IN} = 622.08MHz, Mx[5:0] = 16, f_{OUT} = 38.88MHz$ | 100Hz Offset                            |   | -15   | 57 |     | dBc/Hz            |

|          | 1                                                      | 1kHz Offset                             |   | -16   | 35 |     | dBc/Hz            |

|          |                                                        | 10kHz Offset                            |   | -16   | 37 |     | dBc/Hz            |

|          |                                                        | 100kHz Offset                           |   | -16   | 37 |     | dBc/Hz            |

|          |                                                        | >1MHz Offset                            |   | -16   | 37 |     | dBc/Hz            |

### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full operating

junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_A^+ = V_D^+ = V_{IN}^+ = V_{OUT0}^+ = V_{OUT1}^+ = V_{OUT2}^+ = 3.3V$ , unless otherwise specified. All voltages are with respect to GND. (Note 2)

| SYMBOL  | PARAMETER                                                                 | CONDITIONS                              | MIN TYP MAX | UNITS             |

|---------|---------------------------------------------------------------------------|-----------------------------------------|-------------|-------------------|

| CMOS Ad | ditive Phase Noise/Time Jitter (Note 5)                                   |                                         | L           | ·                 |

|         | Phase Noise:                                                              | 10Hz Offset                             | -129        | dBc/Hz            |

|         | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 4,<br>f <sub>OUT</sub> = 155.52MHz | 100Hz Offset                            | -143        | dBc/Hz            |

|         |                                                                           | 1kHz Offset                             | -158        | dBc/Hz            |

|         |                                                                           | 10kHz Offset                            | -161        | dBc/Hz            |

|         |                                                                           | 100kHz Offset                           | -162        | dBc/Hz            |

|         |                                                                           | >1MHz Offset                            | -162        | dBc/Hz            |

|         | Jitter:                                                                   | 12kHz to 20MHz Integration Bandwidth    | 52          | fs <sub>RMS</sub> |

|         | f <sub>IN</sub> = 622.08MHz, Mx[5:0] = 4,<br>f <sub>OUT</sub> = 155.52MHz | 10Hz to 77.75MHz Integration Bandwidth  | 102         | fs <sub>RMS</sub> |

|         | Phase Noise:                                                              | 10Hz Offset                             | -129        | dBc/Hz            |

|         | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 1,<br>f <sub>OUT</sub> = 245.76MHz | 100Hz Offset                            | -139        | dBc/Hz            |

|         |                                                                           | 1kHz Offset                             | -146        | dBc/Hz            |

|         |                                                                           | 10kHz Offset                            | -155        | dBc/Hz            |

|         |                                                                           | 100kHz Offset                           | -159        | dBc/Hz            |

|         |                                                                           | >1MHz Offset                            | -160        | dBc/Hz            |

|         | Jitter:                                                                   | 12kHz to 20MHz Integration Bandwidth    | 42          | fs <sub>RMS</sub> |

|         | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 1,<br>f <sub>OUT</sub> = 245.76MHz | 10Hz to 122.88MHz Integration Bandwidth | 102         | fs <sub>RMS</sub> |

|         | Phase Noise:                                                              | 10Hz Offset                             | -135        | dBc/Hz            |

|         | f <sub>IN</sub> = 245.76MHz, Mx[5:0] = 4,<br>f <sub>OUT</sub> = 61.44MHz  | 100Hz Offset                            | -147        | dBc/Hz            |

|         |                                                                           | 1kHz Offset                             | -156        | dBc/Hz            |

|         |                                                                           | 10kHz Offset                            | -163        | dBc/Hz            |

|         |                                                                           | 100kHz Offset                           | -166        | dBc/Hz            |

|         |                                                                           | >1MHz Offset                            | -166        | dBc/Hz            |

|         | Jitter:<br>$f_{IN} = 245.76MHz$ , Mx[5:0] = 4,<br>$f_{OUT} = 61.44MHz$    | 12kHz to 20MHz Integration Bandwidth    | 82          | fs <sub>RMS</sub> |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC6954I is guaranteed to meet specified performance limits over the full operating junction temperature range of  $-40^{\circ}$ C to  $105^{\circ}$ C. Under maximum operating conditions, air flow or heat sinking may be required to maintain a junction temperature of  $105^{\circ}$ C or lower. It is strongly recommended that the exposed pad (pin 37) be soldered directly to the ground plane with an array of thermal vias as described in the Applications Information section.

**Note 3:** The supply current delta specifications refer to the amount of supply current that each individual block consumes. Powering on or off this circuit block adds or subtracts this much current from the total supply current consumed in any given configuration.

**Note 4:** The skews are defined as the second listed output's transition relative to the first listed output's transition. If the second listed output transitions after the first listed output, the skew is positive.

For the same divider setting, LVPECL outputs have nominally the same skew regardless of the IBIAS setting (IBIASx = 0 or 1), for the same divider setting, all LVDS and CMOS outputs transition after the LVPECL outputs, thus these skews are positive. For the same divider setting, all CMOS outputs transition after all LVDS outputs, thus these skews are positive. For the same divider setting, LVDS outputs with the 3.5mA current setting (LVCS = 0) transition after LVDS outputs with the 7mA current setting (LVCS = 1), thus these skews are positive. For the same divider setting, in-phase CMOS outputs (CMSINVx = 0) transition after complementary outputs (CMSINVx = 1), thus this skew is positive. For the same output type, outputs with the divider setting greater than one (Mx[5:0] > 1) transition after outputs with the divider equal to one (Mx[5:0] = 1), thus this additional skew is positive.

**Note 5:** Additive phase noise and jitter are the phase noise added by the LTC6954. It does not include noise from the external signal source.

$V_{A}^{+} = V_{D}^{+} = V_{IN}^{+} = V_{OUT0}^{+} = V_{OUT1}^{+} = V_{OUT2}^{+} = 3.3V.$

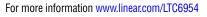

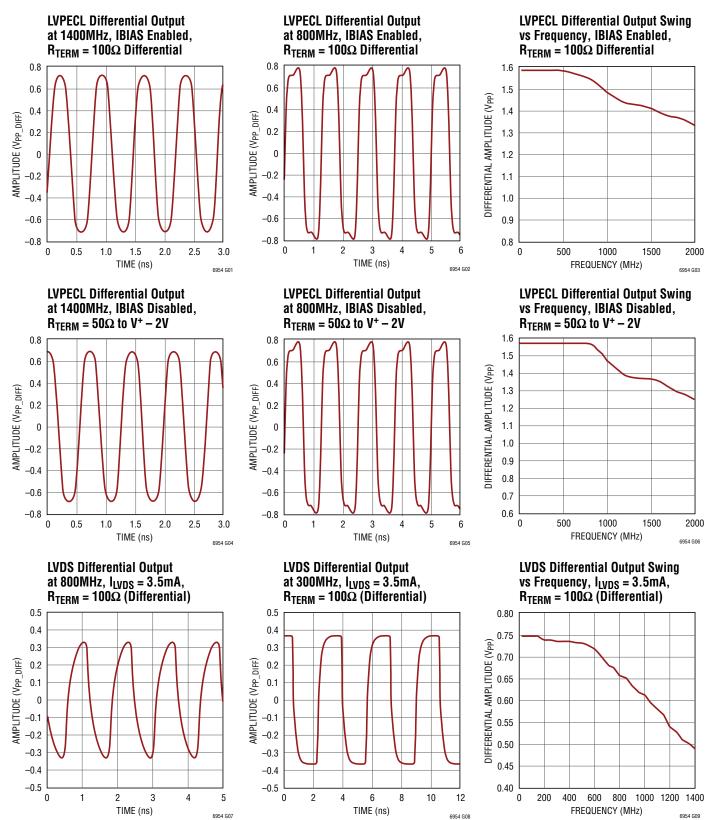

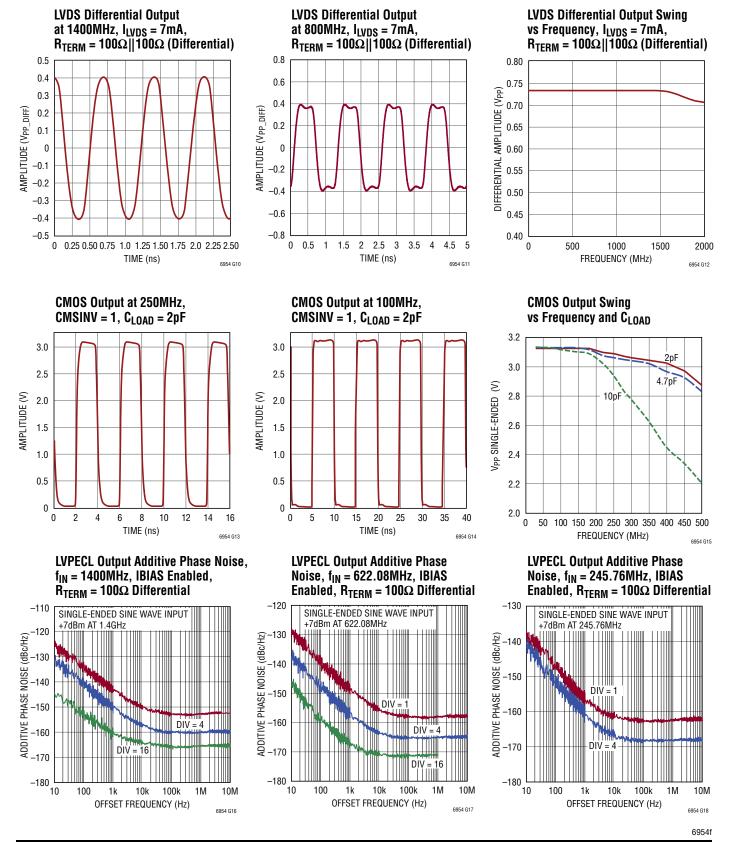

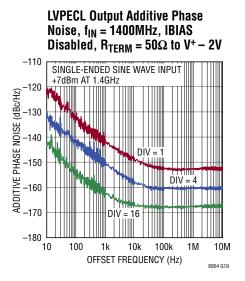

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise specified. All voltages are with respect to GND.

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise specified. All voltages are with respect to GND.

$V_{A}^{+} = V_{D}^{+} = V_{IN}^{+} = V_{OUT0}^{+} = V_{OUT1}^{+} = V_{OUT2}^{+} = 3.3V.$

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^{\circ}C$ , unless otherwise specified. All voltages are with respect to GND.

LVDS Output Additive Phase Noise,  $f_{IN} = 622.08MHz, I_{LVDS} = 3.5mA,$  $R_{\text{TERM}} = 100\Omega$  Differential

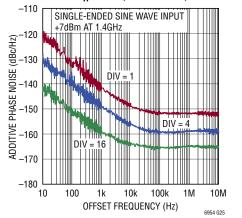

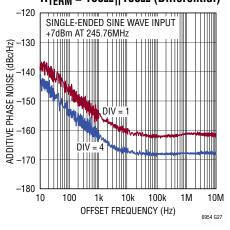

LVDS Output Additive Phase Noise,  $f_{IN} = 1400 MHz$ ,  $I_{LVDS} = 7 mA$ ,  $R_{TERM}$ =  $100\Omega || 100\Omega$  (Differential)

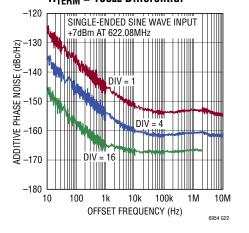

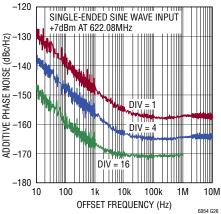

Noise,  $f_{IN} = 622.08MHz$ , IBIAS Disabled,  $R_{TERM} = 50\Omega$  to V<sup>+</sup> – 2V -120SINGLE-ENDED SINE WAVE INPUT +7dBm AT 622.08MHz -130 ADDITIVE PHASE NOISE (dBc/Hz) 140 -150 -160 DIV = 4-170 DIV = 16-18010k 100k 10 100 1k 1M 10M OFFSET FREQUENCY (Hz)

LVPECL Output Additive Phase

LVDS Output Additive Phase Noise,  $f_{IN} = 245.76MHz, I_{LVDS} = 3.5mA,$  $R_{\text{TERM}} = 100\Omega$  Differential

LVDS Output Additive Phase Noise,  $f_{IN} = 622.08 MHz, I_{LVDS} = 7 mA,$  $R_{\text{TERM}} = 100\Omega || 100\Omega$  (Differential)

$V_{A}^{+} = V_{D}^{+} = V_{IN}^{+} = V_{OUT0}^{+} = V_{OUT1}^{+} = V_{OUT2}^{+} = 3.3V.$

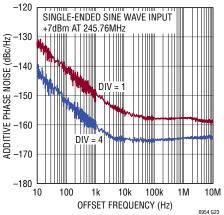

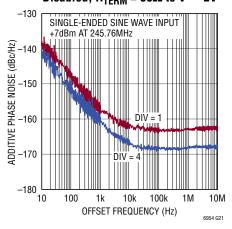

LVPECL Output Additive Phase Noise, f<sub>IN</sub> = 245.76MHz, IBIAS Disabled,  $R_{TERM} = 50\Omega$  to V<sup>+</sup> – 2V

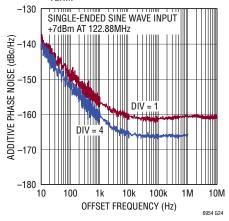

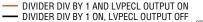

LVDS Output Additive Phase Noise, f<sub>IN</sub> = 122.88MHz, I<sub>LVDS</sub> = 3.5mA,  $R_{\text{TERM}} = 100\Omega$  Differential

LVDS Output Additive Phase Noise,  $f_{IN} = 245.76 MHz, I_{LVDS} = 7 mA,$  $R_{\text{TERM}} = 100\Omega || 100\Omega$  (Differential)

-120

-130

140

-150

-160

-170

-180

10

100

ADDITIVE PHASE NOISE (dBc/Hz)

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise specified. All voltages are with respect to GND.

$V_{A}^{+} = V_{D}^{+} = V_{IN}^{+} = V_{OUT0}^{+} = V_{OUT1}^{+} = V_{OUT2}^{+} = 3.3V.$

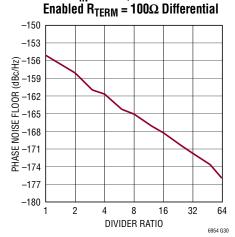

Additive Phase Noise Floor vs Divider Ratio FIN = 1GHz, LVPECL IBIAS

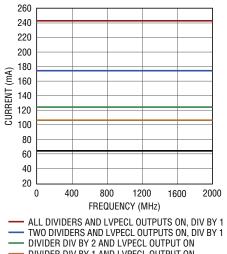

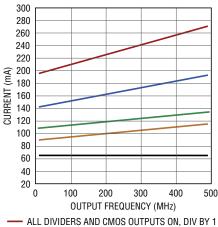

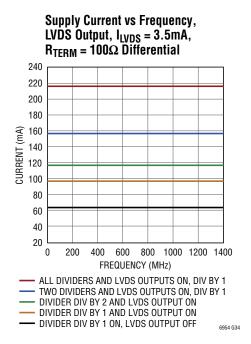

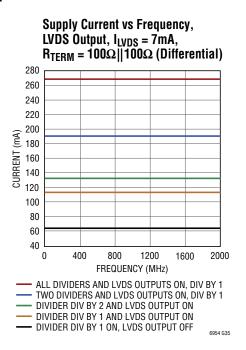

Supply Current vs Frequency, LVPECL Output, IBIAS Enabled,  $R_{\text{TERM}} = 100\Omega$  Differential

10k

**OFFSET FREQUENCY (Hz)**

100k

1M

10M

6954 G28

6954 G31

**CMOS Output Additive Phase**

SINGLE-ENDED SINE WAVE INPUT +7dBm AT 245.76MHz

DIV

DIV

1k

Noise,  $f_{IN} = 245.76MHz$

**CMOS Output Additive Phase**

Noise,  $f_{IN} = 122.88MHz$

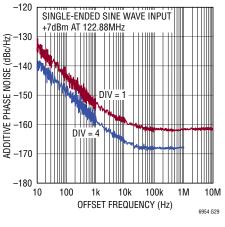

Supply Current vs Frequency, LVPECL Output, IBIAS Disabled,  $R_{\text{TERM}} = 50\Omega \text{ to } V^+ - 2V$

ALL DIVIDERS AND LVPECL OUTPUTS ON, DIV BY 1 TWO DIVIDERS AND LVPECL OUTPUTS ON, DIV BY 1

- DIVIDER DIV BY 2 AND LVPECL OUTPUT ON DIVIDER DIV BY 1 AND LVPECL OUTPUT ON

- DIVIDER DIV BY 1 ON, LVPECL OUTPUT OFF 6954 G32

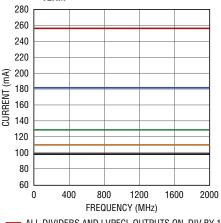

#### Supply Current vs Frequency, **CMOS** Output

- TWO DIVIDERS AND CMOS OUTPUTS ON, DIV BY 1

- DIVIDER DIV BY 2 AND CMOS OUTPUT ON

- DIVIDER DIV BY 1 AND CMOS OUTPUT ON

DIVIDER DIV BY 1 ON, CMOS OUTPUT OFF 6954 G33

6954f

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise specified. All voltages are with respect to GND.

$V_{A}^{+} = V_{D}^{+} = V_{IN}^{+} = V_{OUT0}^{+} = V_{OUT1}^{+} = V_{OUT2}^{+} = 3.3V.$

## PIN FUNCTIONS

### LTC6954

**V<sub>OUT0</sub><sup>+</sup>**, **V<sub>OUT1</sub><sup>+</sup>**, **V<sub>OUT2</sub><sup>+</sup>** (Pins 1, 4, 5, 8, 9, 12): Output Supply Voltages. The supply range is from 3.15V to 3.45V. This supply should be kept free of noise and ripple. The use of a low impedance power plane is recommended. All  $V_{OUTx}^+$  pins must be connected to the same supply voltage as the V<sub>A</sub><sup>+</sup>, V<sub>D</sub><sup>+</sup> and V<sub>IN</sub><sup>+</sup> pins. Each pin, or in some cases pin pairs, must be separately bypassed directly to GND with a 0.01µF ceramic capacitor as close to the pin as possible. Refer to the Applications Information section for more details on supply connections and bypassing.

**GND** (Pins 14, 26, 29, 32, 35): Ground Connections. Should be tied directly to the exposed pad (pin 37) and to a low impedance ground plane for best performance. Refer to the Applications Information section for more details on grounding for signal integrity and thermal considerations.