Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Hybrid Step-Down Synchronous Controller

#### **FEATURES**

- Wide V<sub>IN</sub> Range: 10V to 72V (80V ABS Max)

- Soft Switching for Low Noise Operation

- Phase-Lockable Fixed Frequency 200kHz to 1.5MHz

- ±1% Output Voltage Accuracy

- R<sub>SENSE</sub> or DCR Current Sensing

- Programmable CCM, DCM, or Burst Mode® Operation

- CLKOUT Pin for Multiphase Operation

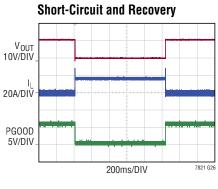

- Short Circuit Protected

- EXTV<sub>CC</sub> Input for Improved Efficiency

- Monotonic Output Voltage Start-Up

- Optional External Reference

- 32-Pin (5mm × 5mm) QFN

#### **APPLICATIONS**

- Intermediate Bus Converters

- High Current Distributed Power Systems

- Telecom, Datacom, and Storage Systems

- Automotive Applications

#### DESCRIPTION

The LTC®7821 uses a proprietary architecture that merges a soft switching charge pump topology with a synchronous step-down converter to provide superior efficiency and EMI performance compared to traditional switching architectures.

In a typical 48V to 12V application, efficiency of greater than 97% is attainable with the LTC7821 switching at 500kHz. The same efficiency can only be achieved with a traditional controller switching at one-third the frequency. Higher switching frequencies allow the use of smaller inductances that yield faster transient response and smaller solution size.

The LTC7821 can be easily paralleled to provide higher output currents with its accurate current sharing capability and frequency synchronization function.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, Including 9484799.

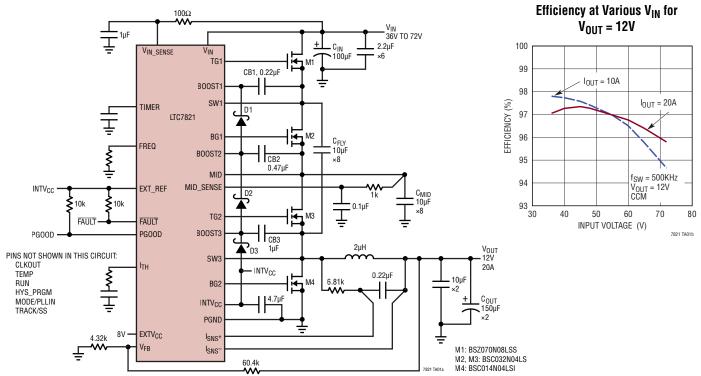

#### TYPICAL APPLICATION

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| ,                                                                |             |

|------------------------------------------------------------------|-------------|

| Input Supply Voltage (V <sub>IN</sub> , V <sub>IN_SENSE</sub> )  | 0.3V to 80V |

| Top Side Driver Voltages                                         |             |

| B00ST1                                                           |             |

| BOOST2, BOOST3                                                   | 0.3V to 46V |

| Switch Voltages                                                  |             |

| SW1                                                              | 0V to 80V   |

| SW3                                                              | 0.3V to 40V |

| MID, MID_SENSE                                                   | 0.3V to 40V |

| (BOOST1-SW1), (BOOST2-MID),                                      |             |

| (BOOST3-SW3)                                                     | 0.3V to 6V  |

| I <sub>SNS</sub> +, I <sub>SNS</sub>                             |             |

| (I <sub>SNS</sub> <sup>+</sup> - I <sub>SNS</sub> <sup>-</sup> ) |             |

| EXTV <sub>CC</sub>                                               | 0.3V to 40V |

| TEMP, FREQ, EXT_REF, V <sub>FB</sub>                             |             |

| HYS_PRGM, I <sub>TH</sub> , RUN, TRACK/SS                        |             |

| FAULT, PGOOD                                                     |             |

| TIMER, MODE/PLLIN                                                |             |

| INTV <sub>CC</sub> Peak Output Current                           |             |

| Operating Junction Temperature Range                             |             |

| (Notes 2, 3, 9)                                                  |             |

| Storage Temperature Range                                        |             |

|                                                                  |             |

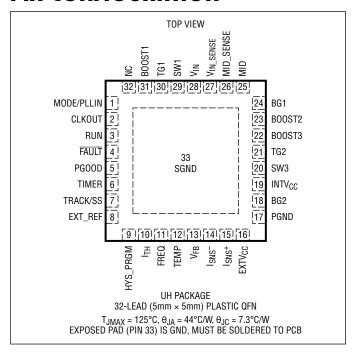

#### PIN CONFIGURATION

## ORDER INFORMATION http://www.linear.com/product/LTC7821#orderinfo

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LTC7821EUH#PBF   | LTC7821EUH#TRPBF | 7821          | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC7821IUH#PBF   | LTC7821IUH#TRPBF | 7821          | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ (Note 2). $V_{IN} = V_{IN\_SENSE} = 48\text{V}$ , $V_{RUN} = 5\text{V}$ , EXTV<sub>CC</sub> = 9V, EXT\_REF = 5.6V unless otherwise noted.

| SYMBOL                      | PARAMETER                                                                          | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | MIN   | TYP                    | MAX                      | UNITS          |

|-----------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------------------------|--------------------------|----------------|

| Main Control Loo            | ps                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       |                        |                          |                |

| V <sub>IN</sub>             | Input Voltage Range                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 10    |                        | 72                       | V              |

|                             | Output Voltage Range                                                               | (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 0.9   |                        | $\frac{V_{1N}}{2} - 2.5$ | V              |

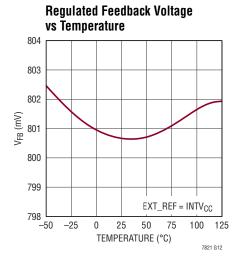

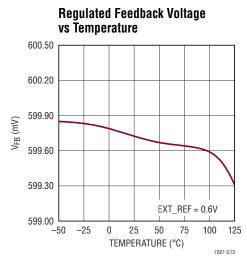

| $\overline{V_{FB}}$         | Regulated Feedback Voltage                                                         | I <sub>TH</sub> Voltage (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 0.792 | 0.8                    | 0.808                    | V              |

| I <sub>FB</sub>             | Feedback Current                                                                   | (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |       | ±10                    | ±50                      | nA             |

| V <sub>REFLNREG</sub>       | Reference Voltage Line Regulation                                                  | V <sub>IN</sub> = 36V to 72V (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |       | 0.003                  | 0.02                     | %/V            |

| V <sub>LOADREG</sub>        | Output Voltage Load Regulation                                                     | (Note 5) $\Delta I_{TH}$ Voltage = 1.2V to 0.7V $\Delta I_{TH}$ Voltage = 1.2V to 1.6V                                                                                                                                                                                                                                                                                                                                                                                       | • |       | 0.016<br>-0.016        | 0.1<br>-0.1              | %<br>%         |

| g <sub>m</sub>              | Transconductance Amplifier g <sub>m</sub>                                          | I <sub>TH</sub> = 1.2V; Sink/Source 5μA (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                             |   |       | 2                      |                          | mmho           |

| Ivin                        | Input DC Supply Current<br>Normal Mode<br>Shutdown<br>Precharging Phase            | $ \begin{aligned} & \text{(Note 6)} \\ & \text{V}_{\text{RUN}} = \text{OV, EXTV}_{\text{CC}} = \text{OV} \\ & \text{V}_{\text{IN}} = 20\text{V, V}_{\text{MID}} = \text{V}_{\text{MID\_SENSE}} = 9\text{V,} \\ & \text{V}_{\text{SW1}} = 15\text{V, V}_{\text{SW3}} = 10\text{V} \\ & \text{V}_{\text{IN}} = 48\text{V, V}_{\text{MID}} = \text{V}_{\text{MID\_SENSE}} = 20\text{V,} \\ & \text{V}_{\text{SW1}} \geq 36\text{V, V}_{\text{SW3}} = 12\text{V} \end{aligned} $ |   |       | 0.5<br>240<br>40<br>84 |                          | mA<br>μA<br>mA |

| I <sub>VIN_SENSE</sub>      | Input DC Supply Current<br>Normal Mode<br>Shutdown                                 | (Note 6) V <sub>RUN</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |       | 1<br>45                |                          | mA<br>μA       |

| I <sub>EXTVCC</sub>         | Input DC Supply Current                                                            | (Note 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |       | 2.2                    |                          | mA             |

| I <sub>MID</sub>            | MID Pin Current                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 45                     |                          | μA             |

| I <sub>MID_SENSE</sub>      | MID_SENSE Pin Current                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 4                      |                          | μA             |

| V <sub>UVLO</sub>           | V <sub>IN</sub> Undervoltage Lockout                                               | V <sub>IN</sub> Ramping Up                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • |       | 8.8                    | 9.4                      | V              |

| V <sub>UVLO_HYST</sub>      | UVLO Hysteresis                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 0.28                   |                          | V              |

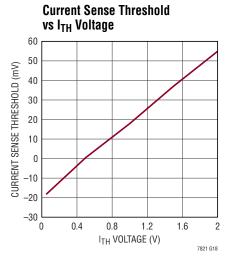

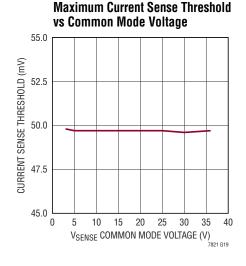

| V <sub>SENSE</sub>          | Current Sense Threshold                                                            | V <sub>ISNS</sub> <sup>-</sup> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | 45    | 50                     | 55                       | mV             |

| I <sub>SNS</sub> +/-        | ISNS <sup>+</sup> and ISNS <sup>-</sup> Pin Current                                | $V_{ISNS}^+ = V_{ISNS}^- = 12V$                                                                                                                                                                                                                                                                                                                                                                                                                                              | • |       |                        | 1.2                      | μА             |

| I <sub>TRACK/SS</sub>       | Soft-Start Charge Current                                                          | V <sub>TRACK/SS</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | -9    | -10                    | -11                      | μA             |

| V <sub>RUN_ON</sub>         | RUN Pin On Threshold                                                               | V <sub>RUN</sub> Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | 1.1   | 1.3                    | 1.6                      | V              |

| I <sub>RUN</sub>            | RUN Pin Current                                                                    | V <sub>RUN</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |       | 1                      |                          | μA             |

| V <sub>RUN_HYST</sub>       | RUN Pin Hysteresis                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 0.1                    |                          | V              |

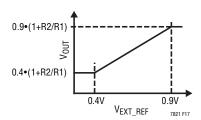

| V <sub>EXT_REF_UC</sub>     | EXT_REF Upper Clamp Limit                                                          | (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | 0.85  | 0.9                    |                          | V              |

| V <sub>EXT_REF_LC</sub>     | EXT_REF Lower Clamp Limit                                                          | (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • |       | 0.40                   | 0.45                     | V              |

| V <sub>SEL_EXT_REF</sub>    | EXT_REF De-Select Threshold (Ramping Up)                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 1.3                    |                          | V              |

| I <sub>EXT_REF</sub>        | EXT_REF Pin Current                                                                | V <sub>EXT_REF</sub> = 0.6V                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | -150  |                        |                          | nA             |

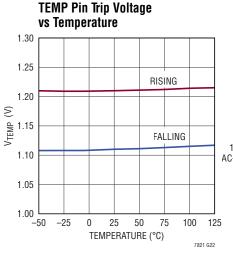

| V <sub>TEMP_TRIP</sub>      | TEMP Pin Trip Point, Rising                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • |       | 1.22                   | 1.25                     | V              |

| V <sub>TEMP_TRIP_HYST</sub> | TEMP Pin Trip Point Hysteresis                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 100                    |                          | mV             |

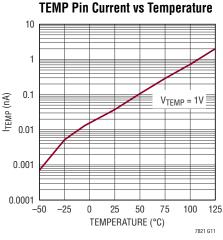

| I <sub>TEMP</sub>           | TEMP Pin Current                                                                   | V <sub>TEMP</sub> = 1V                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |       | 1                      |                          | nA             |

| V <sub>BSTUVLO</sub>        | Undervoltage Lockout of (B00ST1-SW1), (B00ST2- V <sub>MID</sub> ) and (B00ST3-SW3) | Difference Voltage, Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |       | 4.4                    |                          | V              |

| V <sub>BSTUVLO_HYST</sub>   | Bootstrap Undervoltage Lockout Hysteresis                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 1.4                    |                          | V              |

| T <sub>OUT</sub>            | TEMP Trip TimeOut                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       | 100                    |                          | ms             |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{IN} = V_{IN\_SENSE} = 48V$ , $V_{RUN} = 5V$ , EXTV $_{CC} = 9V$ , EXT\_REF = 5.6V unless otherwise noted.

| SYMBOL                      | PARAMETER                                            | CONDITIONS                                                                                                                                                 |   | MIN       | TYP                  | MAX        | UNITS       |

|-----------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|----------------------|------------|-------------|

| INTV <sub>CC</sub> Linear F | Regulator                                            |                                                                                                                                                            |   |           |                      |            |             |

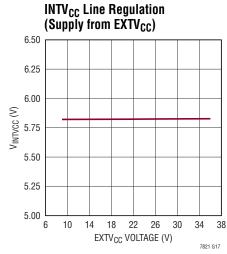

| V <sub>INTVCC</sub>         | Internal V <sub>CC</sub> Regulator                   | 10V < V <sub>IN</sub> < 72V, V <sub>EXTVCC</sub> = 0V                                                                                                      |   | 5.65      | 5.8                  | 5.95       | V           |

| $V_{LDOINT}$                | INTV <sub>CC</sub> Load Regulation                   | I <sub>CC</sub> = 1mA to 50mA, V <sub>IN</sub> = 12V, V <sub>EXTVCC</sub> = 0V                                                                             |   |           | -0.6                 | -2         | %           |

| V <sub>EXTVCC</sub>         | EXTV <sub>CC</sub> Switchover Voltage                | EXTV <sub>CC</sub> Ramping Positive, I <sub>CC</sub> = 1mA                                                                                                 |   |           | 7                    |            | V           |

| V <sub>EXTVCC_HYS</sub>     | EXTV <sub>CC</sub> Switchover Voltage Hysteresis     |                                                                                                                                                            |   |           | 200                  |            | mV          |

| V <sub>LDOEXT</sub>         | EXTV <sub>CC</sub> Load Regulation                   | V <sub>EXTVCC</sub> = 12V, I <sub>CC</sub> = 1mA to 50mA                                                                                                   |   |           | -0.6                 | -2         | %           |

| Oscillator and F            | Phase Lock Loop                                      |                                                                                                                                                            |   |           |                      |            |             |

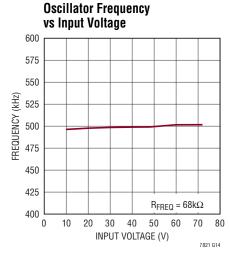

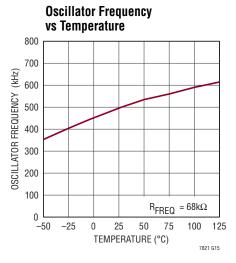

| f <sub>NOM</sub>            | Nominal Frequency                                    | $R_{FREQ} = 68k\Omega$                                                                                                                                     |   | 440       | 490                  | 550        | kHz         |

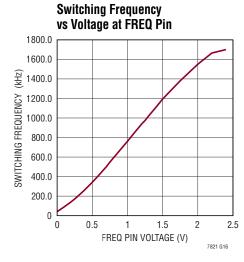

| $f_{LOW}$                   | Lowest Frequency                                     | V <sub>FREQ</sub> = 0V                                                                                                                                     |   | 20        | 50                   | 100        | kHz         |

| f <sub>HIGH</sub>           | Highest Frequency                                    | V <sub>FREQ</sub> = INTV <sub>CC</sub>                                                                                                                     |   | 1400      | 1700                 | 2000       | kHz         |

| f <sub>SYNC_LOW</sub>       | Lowest Synchronizing Frequency                       |                                                                                                                                                            |   | 200       |                      |            | kHz         |

| f <sub>SYNC_HIGH</sub>      | Highest Synchronizing Frequency                      |                                                                                                                                                            |   |           |                      | 1500       | KHz         |

| I <sub>FREQ</sub>           | Frequency Setting Current                            | V <sub>FREQ</sub> = 0V                                                                                                                                     | • | -9        | -10                  | -11        | μА          |

| R <sub>MODE/PLLIN</sub>     | MODE/PLLIN Resistance                                |                                                                                                                                                            |   |           | 250                  |            | kΩ          |

| CLKOUT <sub>HIGH</sub>      | CLKOUT High Amplitude                                |                                                                                                                                                            |   |           | 2.4                  |            | V           |

| CLKOUT <sub>LOW</sub>       | CLKOUT Low Amplitude                                 |                                                                                                                                                            |   |           | 0                    | -          | V           |

| PGOOD Output                |                                                      |                                                                                                                                                            |   |           |                      |            |             |

| V <sub>PG1</sub>            | PGOOD 1st Trip Level (with Delay)                    | V <sub>FB</sub> with Respect to Regulated Voltage V <sub>FB</sub> Ramping Up (Overvoltage 1st Level) V <sub>FB</sub> Ramping Down (Undervoltage 1st Level) |   | 6<br>-5.5 | 8.5<br>-7.5          | 11<br>-9.5 | %<br>%      |

| V <sub>PG1_HYST</sub>       | PGOOD 1st Trip Level Hysteresis (with Delay)         |                                                                                                                                                            |   |           | 15                   |            | mV          |

| V <sub>PG2</sub>            | PGOOD 2nd Trip Level                                 | V <sub>FB</sub> with Respect to Regulated Voltage V <sub>FB</sub> Ramping Up (Overvoltage 2nd Level) V <sub>FB</sub> Ramping Down (Undervoltage 2nd Level) |   |           | 15<br>-25            |            | %<br>%      |

| V <sub>PG2_HYST</sub>       | PGOOD 2nd Trip Level Hysteresis                      |                                                                                                                                                            |   |           | 15                   |            | mV          |

| V <sub>PGL</sub>            | PGOOD Voltage Low                                    | I <sub>PGOOD</sub> = 0.6mA                                                                                                                                 |   |           | 0.4                  | 0.5        | V           |

| I <sub>PGOOD</sub>          | PGOOD Leakage Current                                | V <sub>PG00D</sub> = 80V                                                                                                                                   |   |           |                      | 1          | μА          |

| Capacitor Balar             | ncing                                                |                                                                                                                                                            |   |           |                      |            |             |

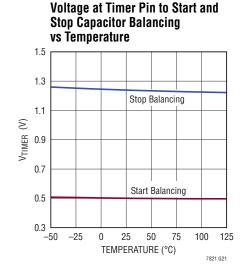

| V <sub>TIMER_LOW</sub>      | Voltage At TIMER Pin To Start Capacitor<br>Balancing |                                                                                                                                                            |   |           | 0.5                  |            | V           |

| V <sub>TIMER_HIGH</sub>     | Voltage At TIMER Pin To Stop Capacitor<br>Balancing  |                                                                                                                                                            |   |           | 1.25                 |            | V           |

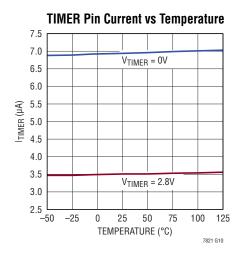

| I <sub>TIMER</sub>          | TIMER Pin Charge Current                             | I I I I I I I I I I I I I I I I I I I                                                                                                                      | • | -6<br>-3  | −7<br>−3.5           | -8<br>-4   | μA<br>μA    |

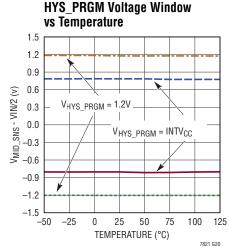

| V <sub>HYS_PRGM</sub>       | Capacitor Balancing Window Comparator<br>Threshold   | V <sub>HYS_PRGM</sub> = 0V<br>V <sub>HYS_PRGM</sub> = 1.2V<br>V <sub>HYS_PRGM</sub> = INTV <sub>CC</sub>                                                   |   |           | ±0.3<br>±1.2<br>±0.8 |            | V<br>V<br>V |

| I <sub>HYS_PRGM</sub>       | HYS_PRGM Pin Current                                 | V <sub>HYS_PRGM</sub> = 0V                                                                                                                                 | • | -9        | -10                  | -11        | μA          |

| V <sub>FAULT</sub>          | FAULT Pin Voltage Low                                | I <sub>FAULT</sub> = 0.6mA                                                                                                                                 |   |           | 0.2                  | 0.4        | V           |

| I <sub>FAULT</sub>          | FAULT Leakage Current                                | V <sub>FAULT</sub> = 80V                                                                                                                                   |   |           |                      | 1          | μА          |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = V_{IN\_SENSE} = 48V$ ,  $V_{RUN} = 5V$ , EXTV $_{CC} = 9V$ , EXT REF = 5.6V unless otherwise noted.

| SYMBOL                                       | PARAMETER                                           | CONDITIONS                                                                                                                  | MIN TYP | MAX | UNITS    |

|----------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|-----|----------|

| I <sub>FLYSRC1</sub>                         | Current Out of SW1 During Capacitor<br>Balancing    | $(V_{SW1} - V_{SW3}) < V_{IN}/2, V_{SW3} = 12V$                                                                             | 40      |     | mA       |

| I <sub>FLYSNK1</sub>                         | Current into SW1 During Capacitor Balancing         | $(V_{SW1} - V_{SW3}) > V_{IN}/2, V_{SW3} = 12V$                                                                             | 6       |     | mA       |

| I <sub>FLYSNK3</sub>                         | Current into SW3 During Capacitor Balancing         | $(V_{SW1} - V_{SW3}) < V_{IN}/2, V_{SW3} = 12V$                                                                             | 40      |     | mA       |

| I <sub>FLYSRC3</sub>                         | Current Out of SW3 During Capacitor<br>Balancing    | $(V_{SW1} - V_{SW3}) < V_{IN}/2, V_{SW3} = 12V$                                                                             | 6       |     | mA       |

| I <sub>MID_SRC</sub>                         | Current Out of MID During Capacitor<br>Balancing    | $V_{MID} < V_{IN}/2, V_{MID} = V_{MID\_SENSE} = 20V$<br>$V_{SW1} \ge 36V, V_{SW3} = 12V$                                    | 60      |     | mA       |

| I <sub>MID_SNK</sub>                         | Current into MID During Capacitor Balancing         | $ \begin{vmatrix} V_{MID} > V_{IN}/2, \ V_{MID} = V_{MID\_SENSE} = 28V \\ V_{SW1} \geq 36V, \ V_{SW3} = 12V \end{vmatrix} $ | 40      |     | mA       |

| <b>Gate Driver</b>                           |                                                     |                                                                                                                             |         |     |          |

| TG1,2                                        | Pull-Up ON Resistance<br>Pull-Down ON Resistance    |                                                                                                                             | 2 1     |     | Ω        |

| BG1, 2                                       | Pull-Up ON Resistance<br>Pull-Down ON Resistance    |                                                                                                                             | 2<br>1  |     | Ω<br>Ω   |

| TG1,2 t <sub>r</sub><br>TG1,2 t <sub>f</sub> | TG1, TG2 Transition Time:<br>Rise Time<br>Fall Time | (Note 7)                                                                                                                    | 4 4     |     | ns<br>ns |

| BG1,2 t <sub>r</sub><br>BG1,2 t <sub>f</sub> | BG1, BG2 Transition Time:<br>Rise Time<br>Fall Time | (Note 7)                                                                                                                    | 4 4     |     | ns<br>ns |

| T <sub>1D</sub>                              | TG1 Off to BG1 On                                   |                                                                                                                             | 45      |     | ns       |

| $T_{2D}$                                     | TG2 Off to BG2 On                                   |                                                                                                                             | 20      |     | ns       |

| T <sub>3D</sub>                              | TG1 Off to TG2 Off                                  |                                                                                                                             | 25      |     | ns       |

| T <sub>4D</sub>                              | BG1 Off to TG1 On                                   |                                                                                                                             | 40      |     | ns       |

| T <sub>5D</sub>                              | BG2 Off to TG2 On                                   |                                                                                                                             | 20      |     | ns       |

| T <sub>6D</sub>                              | BG1 Off to BG2 Off                                  |                                                                                                                             | 20      |     | ns       |

| t <sub>on(MIN)</sub>                         | Minimum On-Time                                     | (Note 8)                                                                                                                    | 210     |     | ns       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC7821E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC7821I is guaranteed to meet performance specifications over the full –40°C to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formulas:

**LTC7821UH:**  $T_{1} = T_{\Delta} + (P_{D} \cdot 44^{\circ}C/W)$

**Note 4:** Output voltage range is guaranteed by design. For output voltage setting, read "Output Voltage Setting" and "Minimum  $V_{OUT}$ " in the "Applications Information" section.

Note 5: The LTC7821 is tested in a feedback loop that servos  $V_{ITH}$  to a specified voltage and measures the resultant  $V_{FB}$ .

**Note 6:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See Applications Information.

**Note 7:** Rise and fall times are measured using 10% and 90% levels. Delay times are measured using 50% levels.

**Note 8:** The minimum on-time condition is specified for an inductor peak-to-peak ripple current  $\geq 40\%$  of  $I_{MAX}$  (see Minimum On-Time Considerations in the Applications Information section)

**Note 9:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum junction temperature may impair device reliability or permanently damage the device.

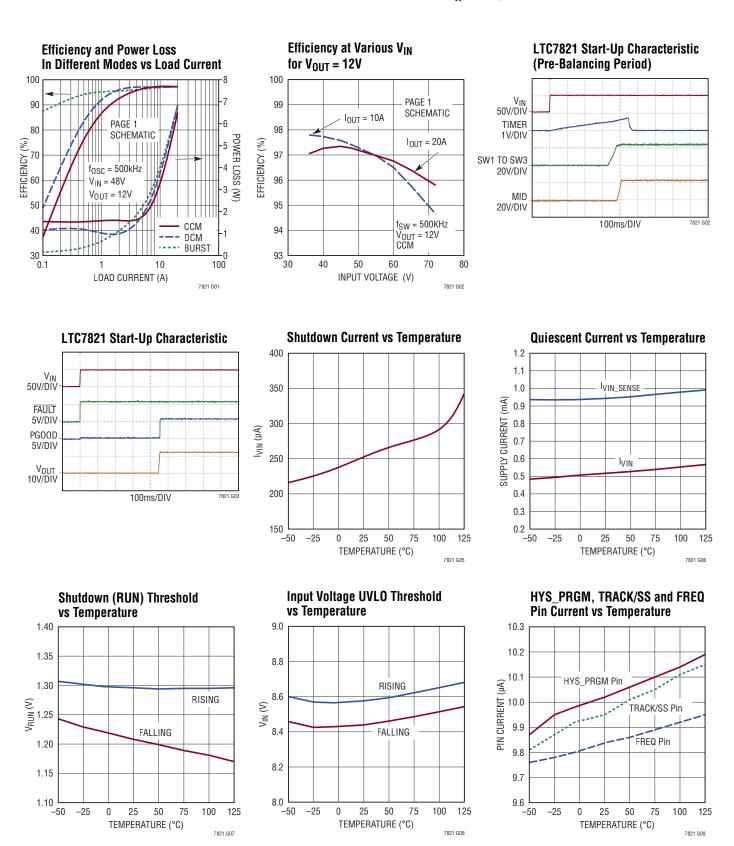

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

#### PIN FUNCTIONS

**MODE/PLLIN (Pin 1):** Mode Selection or External Synchronization Input to Phase Detector. When external synchronization is not used, this pin selects the operating modes and can be tied to SGND, to  $INTV_{CC}$  or left floating. If the pin is connected to SGND, it enables forced continuous mode while a connection to  $INTV_{CC}$  enables pulse-skipping mode. Floating the pin enables Burst Mode operation.

For external sync, apply a clock signal to this pin. The integrated PLL along with its internal compensation network will synchronize the internal oscillator to this clock. Forced continuous mode will be enabled.

**CLKOUT (Pin 2):** Clock Output Pin. This pin outputs a clock 180° out of phase with the main operating clock of the LTC7821.

**RUN (Pin 3):** Run Control Input. A voltage above 1.3V turns the controller ON. There is a  $1\mu$ A pull-up current on this pin when its voltage is below 1.3V.

**FAULT (Pin 4):** Open Drain Output pin. When the signal goes low, it indicates one of the following conditions:

- (a) In the capacitor balancing phase, capacitors  $C_{FLY}$  or  $C_{MID}$  (see Typical Application) are not charged to  $V_{IN}/2$ . A low FAULT indicates an abnormal condition that is preventing  $C_{FLY}$  or  $C_{MID}$  from being be charged up to  $V_{IN}/2$ .

- (b) During normal operation, the voltage deviates from  $V_{\text{IN}}/2$  by a window amount set by the voltage on the HYS\_PRGM pin.

- (c) The die temperature exceeds its internally set limit or the PTC resistor connected as the lower leg of a resistor divider trips the TEMP pin threshold.

During any of these condition, the TRACK/SS pin will also be pulled low.

**PGOOD** (**Pin 5**): Power Good Pin. This is an open drain output. PGOOD is pulled to ground when the voltage of the  $V_{FB}$  pin is not within  $\pm 7.5\%$  of its set point after an internal  $50\mu s$  mask timer expires. It will also be pulled low when FAULT is tripped.

**TIMER (Pin 6):** Charge Balancing Timer Input. A capacitor connected from this pin to ground sets the amount of time allocated to charge  $C_{FLY}$  and  $C_{MID}$  to  $V_{IN}/2$  during

the capacitor balancing phase. It also sets the auto-retry timeout, should the capacitors fail to reach this voltage within the set time. Capacitors  $C_{FLY}$  and  $C_{MID}$  begin and end charging when the TIMER voltage is between 0.5V and 1.2V, respectively. If the capacitor is balanced before the TIMER voltage reaches 1.2V, this voltage is reset to ground and normal operation begins. However, if the balance is not reached when the voltage reaches 1.2V, then the charging of the capacitors stops and the auto-retry timeout period begins. The TIMER capacitor will now slew at half the rate until it reaches 4V and then resets to zero and begins to slew at 1x rate. Once it reaches 0.5V, the  $C_{FLY}$  and  $C_{MID}$  begin to charge again and the process repeats.

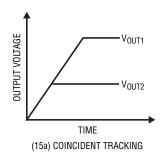

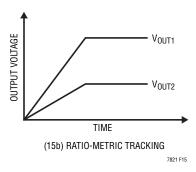

**TRACK/SS (Pin 7):** Output Voltage Tracking and Soft-Start Input. The LTC7821 regulates the  $V_{FB}$  voltage to the lowest of three voltages: 0.8V, the voltage on the EXT\_REF pin or the voltage on the TRACK/SS pin. An internal 10µA pull-up current source is connected to this pin. A capacitor to ground at this pin sets the ramp time to the final regulated output voltage. Alternatively, a resistor divider from another voltage supply connected to this pin allows the LTC7821 output voltage to track the other supply during start-up.

**EXT\_REF (Pin 8):** External Reference Input. A voltage applied to this pin forces the  $V_{FB}$  to regulate to this voltage. Internal clamps set at 0.4V and 0.93V limit the lower and upper bounds of  $V_{FB}$  regulation. Connecting this pin to INTV<sub>CC</sub> will cause the internal reference to be used for output voltage regulation.

HYS\_PRGM (Pin 9): There is a  $10\mu A$  current flowing out of this pin. A voltage created by connecting a resistor from this pin to ground sets an equal amount of window threshold around  $V_{IN}/2$  to a window comparator. When the voltage at MID<sub>SENSE</sub> is not within this window threshold, FAULT will be pulled low and switching will stop.  $C_{FLY}$  and  $C_{MID}$  will be rebalanced to half of  $V_{IN}$  before resuming normal operation.

$I_{TH}$  (**Pin 10**): Current Control Threshold and Error Amplifier Compensation Point. The current comparator threshold increases with its  $I_{TH}$  control voltage.

**FREQ (Pin 11):** Frequency Set Pin. There is a  $10\mu A$  current flowing out of this pin. A resistor to ground sets a voltage which in turn programs the frequency.

#### PIN FUNCTIONS

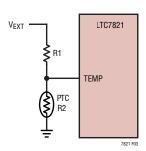

**TEMP (Pin 12):** Temperature Sensing Input. Using a PTC resistor as the lower leg of a resistor divider, connect the TEMP pin to the common point of the divider. The PTC resistor is used to monitor a hot spot on the PCB. Once it reaches the TEMP threshold of 1.22V, the LTC7821 stops switching for 100ms before retrying. Ground this pin if not used.

**V<sub>FB</sub> (Pin 13):** Error Amplifier Feedback Input. This pin receives the remotely sensed feedback voltage from an external resistive divider across the output.

**I<sub>SNS</sub>- (Pin 14):** Current Sense Comparator Input. The (–) input to the current comparator is Kelvin connected to the output voltage of the controller.

**I**<sub>SNS</sub>+ (**Pin 15**): Current Sense Comparator Input. The (+) input to the current comparator is normally Kelvin connected to the DCR sensing networks or current sensing resistor.

**EXTV**<sub>CC</sub> (**Pin 16**): External Power Input to an Internal LDO Connected to INTV<sub>CC</sub>. This LDO supplies INTV<sub>CC</sub> power, bypassing the internal LDO powered from  $V_{IN}$  whenever EXTV<sub>CC</sub> is higher than 6.4V. Do not float or exceed 40V on this pin.

**PGND (Pin 17):** Driver Power Ground. Connect this pin closely to the source of bottom (synchronous) N-channel MOSFET M4, the (-) terminal of  $C_{IN}$  and the (-) terminal of  $C_{VCC}$ .

**BG2** (**Pin 18**): Gate Drive for the Bottom (synchronous) N-Channel MOSFET. The voltage swings from slightly below ground to  $INTV_{CC}$ .

INTV<sub>CC</sub> (Pin 19): Internal Regulator Output. The bottom synchronous gate driver and control circuits are powered from this regulator. Bypass this pin to PGND with a minimum of  $4.7\mu F$  low ESR tantalum or ceramic capacitor. Do not use the INTV<sub>CC</sub> pin for any purpose other than described in this data sheet.

**SW3 (Pin 20):** Switch Node Connection to Inductor and One Terminal of Flying Capacitor. Voltage swing at this pin is from slightly below ground to  $V_{IN}/2$ .

**TG2 (Pin 21):** Floating Gate Drive for Second Lowermost N-Channel MOSFET. The voltage swings equal to INTV<sub>CC</sub> superimposed on the switch node voltage SW3.

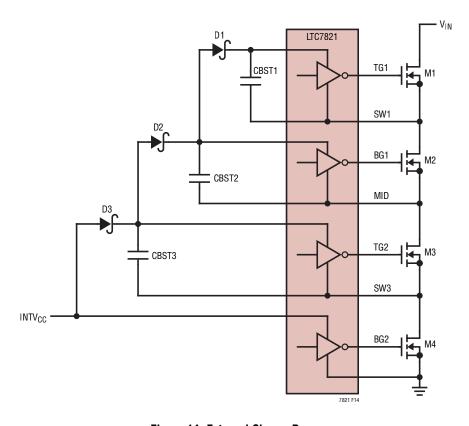

**BOOST1**, **BOOST2**, **BOOST3** (**Pin 31**, **23**, **22**): Bootstrapped Supplies to Floating Drivers. Capacitors are connected between the BOOSTx and SWx (MID) pin. Voltage swing at the BOOST1 pin is from ( $V_{IN}/2 + INTV_{CC}$ ) to ( $V_{IN} + INTV_{CC}$ ). Voltage at the BOOST2 pin is at ( $V_{IN}/2 + INTV_{CC}$ ). Voltage swing at the BOOST3 pin is from  $INTV_{CC}$  to ( $V_{IN}/2 + INTV_{CC}$ ).

**BG1 (Pin 24):** Floating Gate Drive for Second Uppermost N-Channel MOSFET. The voltage swings between  $(V_{IN}/2 + INTV_{CC})$  and  $V_{IN}/2$ .

**MID** (Pin 25): Half Supply from  $V_{IN}$ . Do not use this to source current. Connect a bypass capacitor from this node to PGND.

**MID**<sub>SENSE</sub> (**Pin 26**): Half Supply Monitor. Provides Kelvin sensing input for the comparator that monitors the voltage between MID<sub>SENSE</sub> and ground. An RC filter can be added from MID to this pin to filter out noise.

$V_{IN\_SENSE}$  (Pin 27):  $V_{IN}$  Kelvin Sensing Input. Allows an internal  $V_{IN}/2$  to be generated for LTC7821 control circuit usage. For a cleaner supply, an RC filter can be added from  $V_{IN}$  to this pin.

$V_{IN}$  (Pin 28): Main Input Supply. Bypass this pin to PGND with a capacitor.

**SW1 (Pin 29):** Switch Node Connection to One Terminal of Flying Capacitor. Voltage swing at this pin is from  $V_{IN}/2$  voltage to  $V_{IN}$ .

**TG1 (Pin 30):** Floating Gate Drive for Uppermost N-Channel MOSFET. The voltage swings equal to  $INTV_{CC}$  superimposed on the switch node voltage SW1.

**SGND** (Exposed Pad, Pin 33): Signal Ground. All Small-signal components and compensation components should connect to this ground, which in turn connects to PGND at one point. Exposed pad must be soldered to the PCB, providing a local ground for the control components of the IC, and be tied to the PGND pin under the IC.

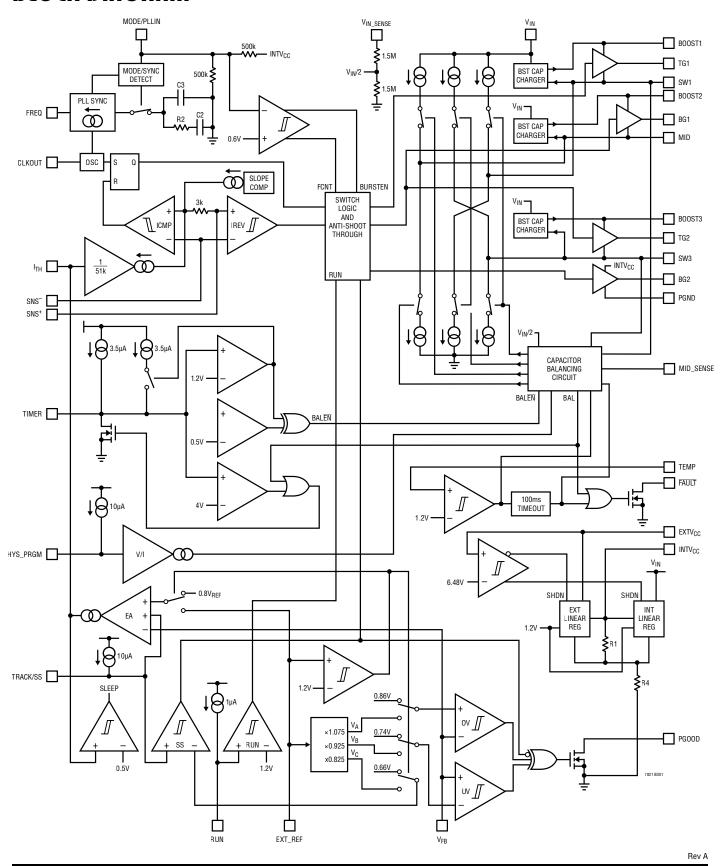

### **BLOCK DIAGRAM**

#### **Capacitor Balancing Phase**

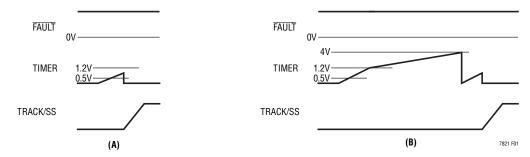

During initial power up, the voltage across the flying capacitor ( $C_{FLY}$ ) and  $C_{MID}$  are measured. If either of these voltages are not at  $V_{IN}/2$ , the TIMER's capacitor will be allowed to charge up. When the TIMER capacitor's voltage reaches 0.5V, internal current sources to bring  $C_{FLY}$  voltage to  $V_{IN}/2$  are turned ON. After the  $C_{FLY}$  voltage has reached  $V_{IN}/2$ ,  $C_{MID}$  will then be charged to  $V_{IN}/2$ . The TRACK/SS pin is pulled low during this duration and all external MOSFETs are shut off. The FAULT pin will not be pulled low during this initial power up. If the voltages across  $C_{FLY}$  and  $C_{MID}$  reach  $V_{IN}/2$  before the TIMER capacitor's voltage reaches 1.2V, the TRACK/SS will be released and allowed to charge up. The TIMER pin will reset to ground and remain there. Normal operation will begin (see Figure 1A).

If, however, the  $C_{FLY}$  or  $C_{MID}$  voltage is not at  $V_{IN}/2$  when  $V_{TIMER}$  reaches 1.2V, the internal current sources will be turned OFF and the TIMER capacitor will be charged at half the initial rate until it reaches 4V. Timer will then be reset to zero, and the LTC7821 will repeat the above process again until  $C_{FLY}$  and  $C_{MID}$  are at  $V_{IN}/2$  (See Figure 1B).

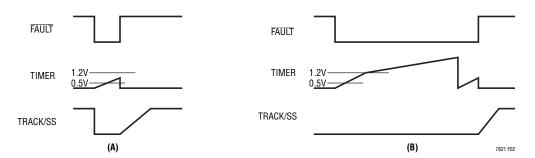

During normal operation, only  $C_{MID}$  is monitored for deviation away from  $V_{IN}/2$  by a window amount set by a resistor connected from HYS\_PRGM to ground. The voltage across this resistor sets the same amount of window threshold above and below  $V_{IN}/2$ . If  $V_{CMID}$  leaves this voltage window, all switching will stop and the TRACK/SS pin will be pulled low. Corresponding internal current sources will be turned on to bring  $C_{FLY}$  and  $C_{MID}$  voltages back to  $V_{IN}/2$ . FAULT will be pulled low and released once the balancing is complete. During this balancing period, PGOOD will also be pulled low. The TRACK/SS pin is also allowed to charge up upon the completion of balancing. Connecting HYS\_PRGM to INTV<sub>CC</sub> sets the window threshold to  $\pm 0.8$ V around  $V_{IN}/2$ . (see Figure 2)

#### **Main Control Loop**

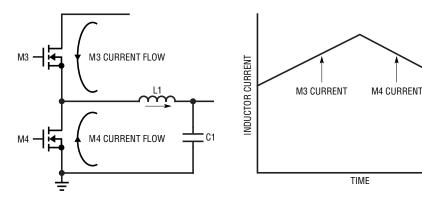

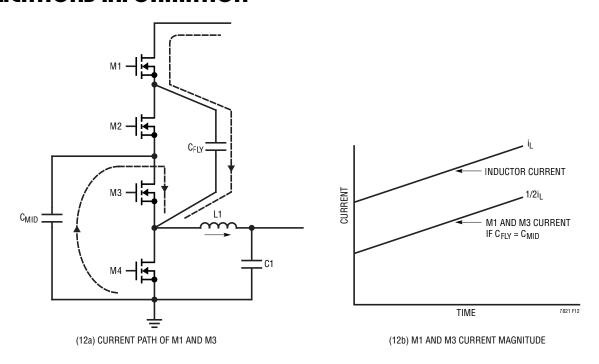

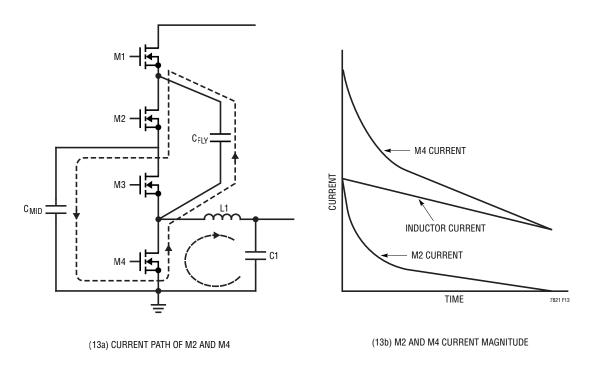

Once the capacitor balancing phase is completed, normal operation begins. MOSFETs M1 and M3 are turned ON when the clock sets the RS latch, and turned off when the main current comparator, I<sub>CMP</sub>, resets the RS latch. MOSFETs M2 and M4 are then turned on. The peak inductor

Figure 1. Charge Balancing During Power Up with (A) Balancing Completed within One Timer Period and (B) More Than One Timer Period

Figure 2. Charge Balancing During Normal Operation with (A) Balancing Completed within One Timer Period and (B) More Than One Timer Period

current at which  $I_{CMP}$  resets the RS latch is controlled by the voltage on the  $I_{TH}$  pin, which is the output of the error amplifier EA. The  $V_{FB}$  pin receives the voltage feedback signal, which is compared to the internal reference voltage by the EA. When the load current increases, it causes a slight decrease in  $V_{FB}$  relative to the 0.8V reference, which in turn causes the  $I_{TH}$  voltage to increase until the average inductor current matches the new load current. After MOSFETs M1 and M3 have turned OFF, MOSFETs M2 and M4 are turned ON until either the inductor current starts to reverse, as indicated by the reverse current comparator  $I_{REV}$ , or the beginning of the next cycle.

During the switching of M1/M3 and M2/M4, capacitor  $C_{FLY}$  is alternately connected in series with or parallel to  $C_{MID}$ . The voltage at MID will be approximately at  $V_{IN}/2$ .

#### INTV<sub>CC</sub>/EXTV<sub>CC</sub> Power

Power for the bootstrap drivers and bottom MOSFET and most internal circuitry is derived from the INTV $_{CC}$  pin. When the EXTV $_{CC}$  pin is grounded or tied to a voltage less than 7V, an internal 5.8V linear regulator supplies INTV $_{CC}$  power from V $_{IN}$ . If EXTV $_{CC}$  is taken above 7V, this linear regulator is turned OFF and another 5.8V linear regulator turns ON to provide the INTV $_{CC}$  power from EXTV $_{CC}$ . Using the EXTV $_{CC}$  pin allows the INTV $_{CC}$  power to be derived from a high efficiency external source, resulting in an overall increase in system efficiency.

#### **Bootstrap Capacitor Refresh**

Each of the three uppermost MOSFET drivers is biased from its respective floating bootstrap capacitor, CB1 to CB3, which are refreshed during switching through a charge pump configuration consisting of diodes D1 to D3 and the external MOSFETs.

During the charge balancing phase or light load condition when switching may stop for extended amount of time, the voltage across the bootstrap capacitor may decrease sufficiently that the gate drive voltage is not optimal. Undervoltage detectors monitor the voltage across each of the bootstrap capacitors. When any of them goes below 3V, an internal current source of 1mA will be turned ON to charge that bootstrap capacitor through the upper plate of the capacitor. A 1mA sinking source that is connected

to the bottom plate of the bootstrap capacitor will also be turned ON to sink away this current. This ensures a net zero residual current at the bottom plate capacitor node, hence avoiding any impact on the bias condition of that node. When CB1 and CB2/CB3 reach 4.3V and 4.47V respectively, the refreshing stops. When CB2 and CB3 need to be refreshed, all switching stops.

#### Shutdown and Start-Up (RUN and TRACK/SS Pins)

When the RUN pin is below 1.3V, the INTV<sub>CC</sub> linear regulator along with all the internal circuitry that is powered from this supply, is disabled. The main control loop will also be disabled. Releasing the RUN pin will allow the internal  $1\mu A$  current source to pull this pin up, thus enabling the part. The RUN pin can also be driven directly by logic but ensure that this voltage does not exceed the Absolute Maximum Rating of 6V.

The slew rate of the output voltage V<sub>OUT</sub> can be controlled by the voltage on the TRACK/SS pin. When the voltage on the TRACK/SS is less than the internal reference of 0.8V (or EXT\_REF if this feature is invoked), the LTC7821 regulates the V<sub>FR</sub> voltage to the TRACK/SS voltage instead of to the reference. This allows the TRACK/SS pin to be used to program the soft-start period by connecting an external capacitor from the TRACK/SS pin to SGND. An internal 10µA pull-up current charges this capacitor, creating a voltage ramp on the TRACK/SS pin. As the TRACK/ SS voltage rises linearly from 0V to the reference voltage (and beyond), the output voltage  $V_{OUT}$  rises smoothly from zero to the final value. Alternatively, the TRACK/SS pin can be used to cause the start-up of  $V_{OLIT}$  to track that of another supply. Typically this requires connecting to the TRACK/SS pin an external resistor divider from the other supply to ground (see Application Information section).

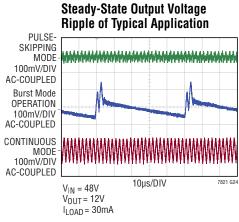

# Light Load Current Operation (Burst Mode Operation, Pulse-Skipping Mode, or Continuous Conduction)

The LTC7821 can be enabled to enter high efficiency Burst Mode operation, constant-frequency pulse-skipping mode, or forced continuous conduction mode. To select forced continuous operation, tie the MODE/PLLIN pin to a DC voltage below 0.6V (e.g., SGND). To select pulse-skipping mode of operation, tie the MODE/PLLIN pin to INTV $_{CC}$ . To select Burst Mode operation, float the MODE/PLLIN pin.

When the controller is enabled for Burst Mode operation, the peak current in the inductor is set to approximately one-third of the maximum sense voltage even though the voltage on the I<sub>TH</sub> pin indicates a lower value. If the average inductor current is higher than the load current, the error amplifier output, EA, will decrease the voltage on the I<sub>TH</sub> pin. When the I<sub>TH</sub> voltage drops below 0.5V, the internal sleep signal goes high (enabling sleep mode) and all external MOSFETs are turned off. In sleep mode, the load current is supplied by the output capacitor. As the output voltage decreases, the EA's output begins to rise. When the output voltage drops enough, the sleep signal goes low, and the controller resumes normal operation by turning on the external MOSFETs on the next cycle of the internal oscillator. When a controller is enabled for Burst Mode operation, the inductor current is not allowed to reverse. The reverse current comparator (IREV) turns off the bottom external MOSFET M4 and M2 just before the inductor current reaches zero, preventing it from reversing and going negative. Thus, the controller operates in discontinuous operation.

In forced continuous operation, the inductor current is allowed to reverse at light loads or under large transient conditions. The peak inductor current is determined by the voltage on the  $I_{TH}$  pin. In this mode, the efficiency at light loads is lower than in Burst Mode operation. However, continuous mode has the advantages of lower output ripple and less interference with audio circuitry.

When the MODE/PLLIN pin is connected to INTV<sub>CC</sub>, the LTC7821 operates in PWM pulse-skipping mode at light loads. At very light loads, the current comparator I<sub>CMP</sub> may remain tripped for several cycles and force the external MOSFETs M1 and M3 to stay off for the same number of cycles (i.e., skipping pulses). The inductor current is not allowed to reverse (discontinuous operation). This mode, like forced continuous operation, exhibits low output ripple as well as low audio noise and reduced RF interference as compared to Burst Mode operation. It provides higher low current efficiency than forced continuous mode, but not nearly as high as Burst Mode operation.

# Frequency Selection and Phase-Locked Loop (FREQ and MODE/PLLIN Pins)

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and/or output capacitance to maintain low output ripple voltage. In addition, it will also require larger BOOST capacitance and balancing capacitance ( $C_{FLY}$  and  $C_{MID}$ ) since the refresh rate is lower. The switching frequency of the LTC7821's controller can be selected using the FREQ pin. If the MODE/PLLIN pin is not being driven by an external clock source, the FREQ pin can be used to program the controller's operating frequency from 50kHz to 1.7MHz.

There is a  $10\mu A$  current flowing out of the FREQ pin, so the user can program the controller's switching frequency with a single resistor to SGND.

A phase-locked loop (PLL) is integrated on the LTC7821 to synchronize the internal oscillator to an external clock source that is connected to the MODE/PLLIN pin. The controller operates in forced continuous mode when it is synchronized. The PLL loop filter network is integrated inside the LTC7821. The phase-locked loop is capable of locking any frequency within the range of 200kHz to 1.5MHz. The frequency setting resistor should always be present to set the controller's initial switching frequency before locking to the external clock.

#### **Temperature Monitoring**

When the LTC7821 die temperature reaches 150°C, switching stops and TRACK/SS pin is pulled low. Charge balancing is also disabled.

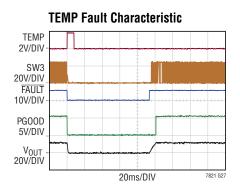

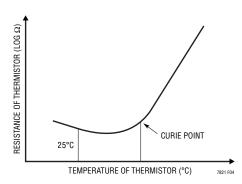

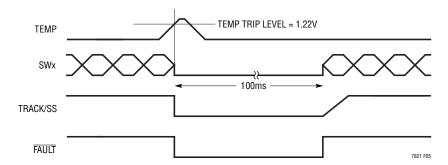

The LTC7821 can provide hotspot monitoring via the TEMP pin. By using a PTC thermistor as the lower leg of a resistor divider and connecting the common point of this divider to the TEMP pin, the voltage increases drastically when the temperature reaches beyond the Curie point of the PTC thermistor as shown in Figure 3. The characteristic of the PTC thermistor is shown in Figure 4. When the TEMP pin reaches 1.22V, all switching stops for 100ms.

The voltage on the TRACK/SS pin and FAULT is pulled low and is released after 100ms (Figure 5) if the voltage on the TEMP pin goes below 1.1V during this 100ms timeout. If the TEMP pin voltage remains above 1.1V, the timeout period will be extended until the voltage drops below 1.1V.

The temperature that is use to trigger the hotspot protection will determine the thermistor selection. This temperature will be the Curie point of the thermistor, which is often defined as having two times its resistance at 25°C. With the Curie point resistance of the thermistor known, R2<sub>CURIE</sub>, the upper resistance, R1, can be selected by the following equation:

$$R1 = \frac{R2_{CURIE} (V_{EXT} - 1.22)}{1.22}$$

#### Power Good (PGOOD Pin)

When  $V_{FB}$  pin voltage is not within  $\pm 10\%$  of the internal 0.8V reference or the reference set by EXT\_REF, the PGOOD pin is pulled low. The PGOOD pin is also pulled low when the RUN pin is below 1.3V or when the LTC7821 is in the

Figure 3. Temperature Monitoring Setup

soft-start or tracking phase. The PGOOD pin will flag power good immediately when the  $V_{FB}$  pin is within the  $\pm 10\%$  of the reference window. However, there is an internal 50µs power bad mask when  $V_{FB}$  goes out the  $\pm 10\%$  window. The PGOOD pin is allowed to be pulled up by an external resistor to sources of up to 80V.

#### FAULT (FAULT Pin)

During initial power up of the LTC7821 or when enabling the part via the RUN pin, the  $\overline{FAULT}$  pin will not be pulled low even when  $C_{FLY}$  and/or  $C_{MID}$  needed to be rebalanced to  $V_{IN}/2$ . But during normal operation, when rebalancing is needed, the  $\overline{FAULT}$  will be pulled low. Another condition that causes the  $\overline{FAULT}$  to go low is thermal shutdown, either caused by the internal die temperature reaching 150°C or the voltage at TEMP pin reaching 1.22V. The  $\overline{FAULT}$  pin is allowed to be pulled up by an external resistor to sources of up to 80V.

Figure 4. Characteristic of a Thermistor

Figure 5. Temperature Trip Characteristic

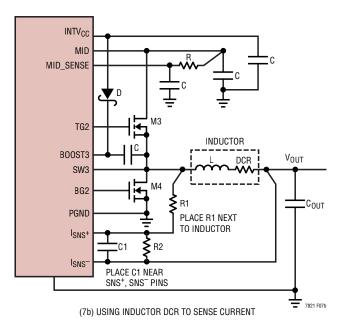

The "Typical Application" on the first page is a basic LTC7821 application circuit. The LTC7821 can be configured to use either DCR (inductor resistance) sensing or resistor sensing. The choice between the two current sensing schemes is largely a design trade-off between cost, power consumption, and accuracy. DCR sensing is popular because it saves an expensive current sensing resistor and is more power efficient, especially in high current applications. However, a current sensing resistor provides the most accurate current limit for the application. Other external component selection is driven by the load requirement, and begins with the selection of R<sub>SENSE</sub> (if R<sub>SENSE</sub> is used). Next C<sub>FLY</sub>, C<sub>MID</sub>, and the power MOSFETs are selected, followed by the input and output capacitors. In addition to the power level, switching frequency plays a role in selecting the balancing capacitance ( $C_{FIY}$  and  $C_{\text{MID}}$ ) and the inductance of the inductor.

#### ISNS+ and ISNS- Pins

The ISNS<sup>+</sup> and ISNS<sup>-</sup> pins are the inputs to the current comparators. The common mode input voltage range of the current comparators is 0V to 36V. Both ISNS pins are high impedance inputs with small leakage currents of less than 1.2µA. When the ISNS pins ramp up from 0V to 2.4V, small base currents flow out of the ISNS pins. When the ISNS pins ramp down from 36V to 2V, the small base currents flow into the ISNS pins. The high impedance inputs to the current comparators allow accurate DCR sensing. However, care must be taken not to float these pins during normal operation.

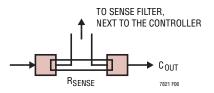

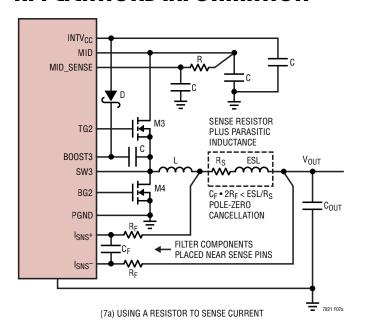

Filter components mutual to the sense lines should be placed close to the LTC7821, and the sense lines should run close together to a Kelvin connection underneath the current sense element (shown in Figure 6). Sensing current elsewhere can effectively add parasitic inductance and capacitance to the current sense element, degrading the information at the sense terminals and making the programmed current limit unpredictable. If DCR sensing is used (Figure 7b), sense resistor R1 should be placed close to the switching node, to prevent noise from coupling into sensitive small-signal nodes. The capacitor C1 should be placed close to the IC pins.

Figure 6. Sense Lines Placement with Sense Resistor

#### **Resistor Current Sensing**

The hybrid architecture of the LTC7821 generates a voltage rail of half the  $V_{IN}$  supply to the step-down control loop. Therefore the current ripple calculation and its operating duty cycle is referred to the voltage at the MID pin which is approximately at  $V_{IN/2}$ .

A typical sensing circuit using a discrete resistor is shown in Figure 7a.  $R_{SENSE}$  is chosen based on the required output current.

The current comparator has a maximum threshold of 50mV and its inputs have a common mode range of 0V to 36V. The current comparator threshold sets the peak of the inductor current, yielding a maximum average output current  $I_{MAX}$  equal to the peak value less half the peak-to-peak ripple current,  $\Delta I_L$ . To calculate the sense resistor value, use the equation:

$$R_{SENSE} = \frac{50mV}{I_{(MAX)} + \frac{\Delta I_L}{2}}$$

Because of possible PCB noise in the current sensing loop, the AC current sensing ripple of  $\Delta V_{SENSE} = \Delta I_L \bullet R_{SENSE}$  also needs to be verified in the design to get a good signal-to-noise ratio.

In general, for a reasonably good PCB layout, a 10mV  $\Delta V_{SENSE}$  voltage is recommended as a conservative number to start with, either for  $R_{SENSE}$  or DCR sensing applications, for duty cycles less than 40%. For applications where the inductor's ripple current could be greater than 50% and operating at 750kHz and above, the sense resistor's parasitic inductance has to be taken into consideration since its contribution is no longer negligible.

Figure 7. Two Different Methods of Sensing Current

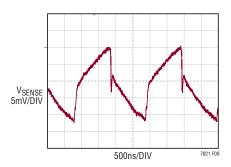

In an application where the sense resistor's parasitic inductance contribution is negligible, a small RC filter placed near the IC is enough to reduce the effects of capacitive and inductive noise coupled in the sense traces on the PCB. A typical filter consists of two series  $10\Omega$  resistors connected to a parallel 1000pF capacitor, resulting in a time constant of 20ns. However, the same RC filter with minor modifications can be used to extract the resistive component of the current sense signal in the presence of significant parasitic inductance in the sense resistor. For example, Figure 8 illustrates the voltage waveform across a  $1m\Omega$  sense resistor with a 2010 footprint for the 12V/20A converter operating at 100% load. The waveform is the superposition of a purely resistive component and a purely inductive component. It was measured using two scope probes and waveform math to obtain a differential measurement. Based on additional measurements of the inductor ripple current and the on-time and off-time of the top switch, the value of the parasitic inductance was determined to be 0.3nH using the equation:

$$ESL = \frac{V_{ESL(STEP)}}{\Delta I_{L}} \bullet \left(\frac{t_{ON} \bullet t_{OFF}}{t_{ON} + t_{OFF}}\right)$$

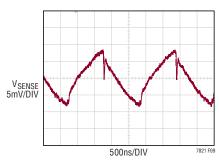

If the RC time constant is chosen to be close to the parasitic inductance divided by the sense resistor (L/R), the resulting waveform looks resistive again, as shown in Figure 9.

Check the sense resistor manufacturer's data sheet for information about parasitic inductance. In the absence of data, measure the voltage drop directly across the sense resistor to extract the magnitude of the ESL step and use

Figure 8. Voltage Waveform Measured Directly Across the Sense Resistor

Figure 9. Voltage Waveform Measured After the Sense Resistor Filter,  $C_F = 1nF$ ,  $R_F = 100\Omega$

the equation to determine the ESL. However, do not over filter. Keep the RC time constant less than or equal to the inductor time constant to maintain a high enough ripple voltage on  $V_{RSENSE.}$  The filter components need to be placed close to the IC. The positive and negative sense traces need to be routed as a differential pair and Kelvin connected to the sense resistor.

#### **Inductor DCR Sensing**

For applications requiring the highest possible efficiency at high load currents, the LTC7821 is capable of sensing the voltage drop across the inductor DCR, as shown in Figure 7b. The DCR of the inductor represents the small amount of DC winding resistance of the copper, which can be less than  $1 \text{m}\Omega$  for today's low value, high current inductors. In a high current application requiring such an inductor, conduction loss through a sense resistor would cost several points of efficiency compared to DCR sensing.

If the external R1|| R2 • C1 time constant is chosen to be exactly equal to the L/DCR time constant, the voltage drop across the external capacitor is equal to the drop across the inductor DCR multiplied by R2/(R1 + R2). R2 scales the voltage across the sense terminals for applications where the DCR is greater than the target sense resistor value. To properly dimension the external filter components, the DCR of the inductor must be known. It can be measured using a good RLC meter, but the DCR tolerance is not always the same and varies with temperature; consult the manufacturers' data sheets for detailed information.

Using the inductor ripple current value from the Inductor Value Calculation section, the target sense resistor value is:

$$R_{SENSE(EQUIV)} = \frac{50mV}{I_{(MAX)} + \frac{\Delta I_{L}}{2}}$$

To ensure that the application will deliver full load current over the full operating temperature range, choose the minimum value for the Maximum Current Sense Threshold  $(V_{SENSE(MAX)})$  in the Electrical Characteristics table.

Next, determine the DCR of the inductor. Where provided, use the manufacturer's maximum value, usually given at

20°C. Increase this value to account for the temperature coefficient of resistance, which is approximately 0.4%/°C. A conservative value for  $T_{L(MAX)}$  is 100°C. To scale the maximum inductor DCR to the desired sense resistor value, use the divider ratio:

$$R_D = \frac{R_{SENSE(EQUIV)}}{DCR(MAX) AT T_{L(MAX)}}$$

C1 is usually selected to be in the range of  $0.047\mu F$  to  $0.47\mu F$ . This forces R1|| R2 to around  $2k\Omega$ , reducing error that might have been caused by the SENSE pins'  $1.2\mu A$  current.  $T_{L(MAX)}$  is the maximum inductor temperature.

The equivalent resistance R1||R2 is scaled to the room temperature inductance and maximum DCR:

$$R1||R2 = \frac{L}{(DCR AT 20^{\circ}C) \cdot C1}$$

The sense resistor values are:

R1=

$$\frac{R1||R2}{R_D}$$

; R2= $\frac{R1 \cdot R_D}{1-R_D}$

The maximum power loss in R1 is related to duty cycle, and will occur in continuous mode at the maximum input voltage:

$$P_{LOSS\_R1} = \frac{(V_{MID} - V_{OUT}) \cdot V_{OUT}}{R1}$$

where  $V_{\text{MID}}$  is half the voltage of  $V_{\text{IN}}$ .

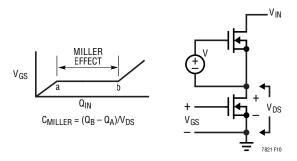

Ensure that R1 has a power rating higher than this value. If high efficiency is necessary at light loads, consider this power loss when deciding whether to use DCR sensing or sense resistors. Light load power loss can be modestly higher with a DCR network than with a sense resistor, due to the extra switching losses incurred through R1. However, DCR sensing eliminates a sense resistor, reduces conduction losses and provides higher efficiency at heavy loads. Peak efficiency is about the same with either method.