# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### LTM4676

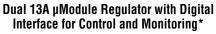

#### Dual 13A or Single 26A µModule Regulator with Digital Power System Management DESCRIPTION

The LTM<sup>®</sup>4676 is a dual 13A or single 26A step-down µModule<sup>®</sup> (micromodule) DC/DC regulator featuring remote configurability and telemetry-monitoring of power management parameters over PMBus— an open standard I<sup>2</sup>C-based digital interface protocol **②**. The LTM4676 is comprised of fast analog control loops, precision mixed-signal circuitry, EEPROM, power MOSFETs, inductors and supporting components.

The LTM4676's 2-wire serial interface allows outputs to be margined, tuned and ramped up and down at programmable slew rates with sequencing delay times. Input and output currents and voltages, output power, temperatures, uptime and peak values are readable. Custom configuration of the EEPROM contents is not required. At start-up, output voltages, switching frequency, and channel phase angle assignments can be set by pin-strapping resistors. The LTpowerPlay<sup>™</sup> GUI and DC1613 USB-to-PMBus converter and demo kits are available.

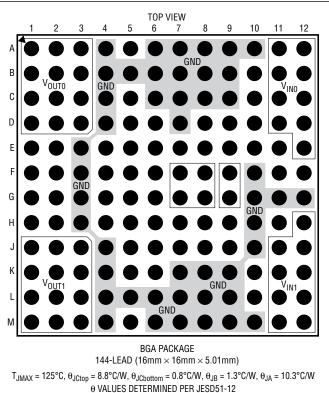

The LTM4676 is offered in a 16mm  $\times$  16mm  $\times$  5.01mm BGA package available with SnPb or RoHS compliant terminal finish.

$\overline{L\sigma}$ , LT, LTC, LTM, Linear Technology, the Linear logo, μModule, Burst Mode and PolyPhase are registered trademarks and LTpowerPlay is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5408150, 5481178, 5705919, 5929620, 6144194, 6177787, 6580258, 7420359, 8163643. Licensed under U.S. Patent 7000125 and other related patents worldwide.

Olick to view associated Video Design Idea.

#### FEATURES

- Dual, Fast, Analog Loops with Digital Interface for Control and Monitoring

- Wide Input Voltage Range: 4.5V to 26.5V

- Output Voltage Range: 0.5V to 5.4V (4V on V<sub>OUTO</sub>)

- ±1% Maximum DC Output Error Over Temperature

- ±2.5% Current Readback Accuracy at 10A Load

- 400kHz PMBus-Compliant I<sup>2</sup>C Serial Interface

- Integrated 16-Bit  $\Delta \Sigma$  ADC

- Constant Frequency Current Mode Control

- Parallel and Current Share Multiple Modules

- 16 Slave Addresses; Rail/Global Addressing

- 16mm × 16mm × 5.01mm BGA Package

#### Readable Data:

- Input and Output Voltages, Currents, and Temperatures

- Running Peak Values, Uptime, Faults and Warnings

- Onboard EEPROM Fault Log Record

#### Writable Data and Configurable Parameters:

- Output Voltage, Voltage Sequencing and Margining

- Digital Soft-Start/Stop Ramp

- OV/UV/OT, UVLO, Frequency and Phasing

### **APPLICATIONS**

- System Optimization, Characterization and Data Mining in Prototype, Production and Field Environments

- Telecom, Datacom, and Storage Systems

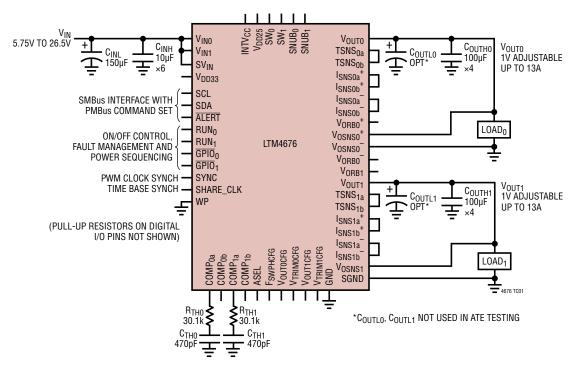

#### TYPICAL APPLICATION

€1.0

010 0.9

0.8

€ 10

0UT0

0

3

3

6

TIME (SEC)

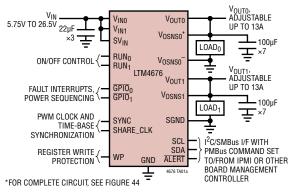

Output Current Readback, Varving Load Pattern

TIME (SEC)

9

Using PMBus and LTpowerPlay to Monitor Telemetry and Margin V<sub>OUT0</sub>/V<sub>OUT1</sub> During Load Pattern Tests. 10Hz Polling Rate. 12V<sub>IN</sub>

1.8 V<sub>0UT1</sub> 1.7 ⟨√

1.6

15

10 UT1 (А) 5

12

12

4677 TA01b

## TABLE OF CONTENTS

| Features                                             | 1    |

|------------------------------------------------------|------|

| Applications                                         | 1    |

| Typical Application                                  | 1    |

| Description                                          | 1    |

| Absolute Maximum Ratings                             | 3    |

| Order Information                                    |      |

| Pin Configuration                                    | 3    |

| Electrical Characteristics                           | 4    |

| Typical Performance Characteristics                  |      |

| Pin Functions                                        |      |

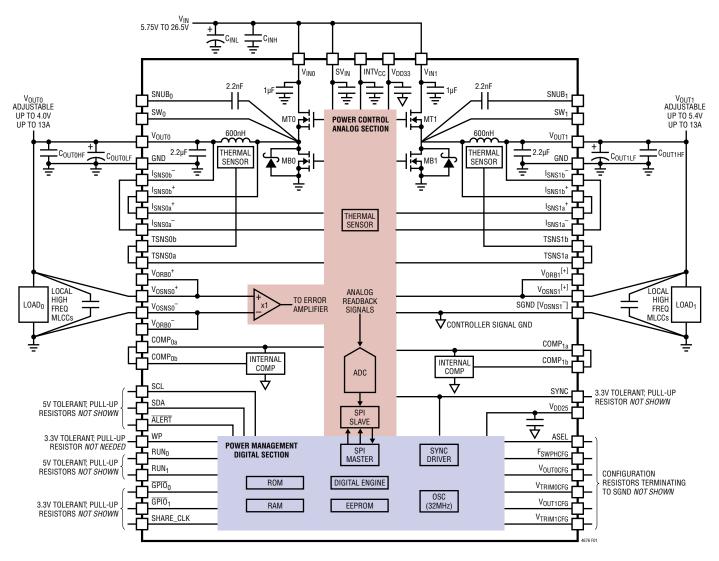

| Simplified Block Diagram                             |      |

| Decoupling Requirements                              |      |

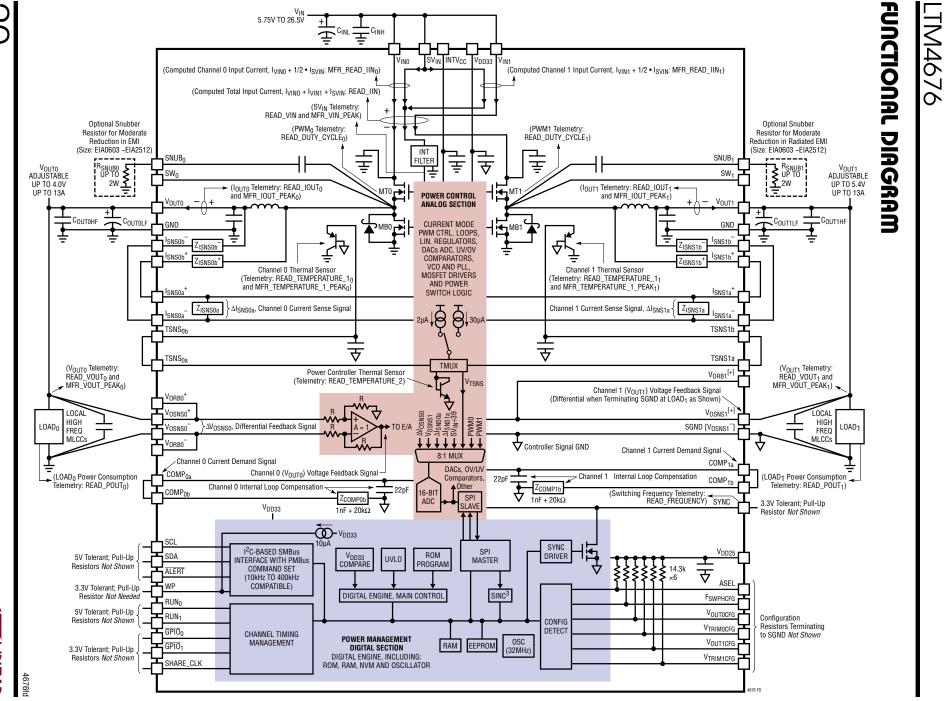

| Functional Diagram                                   |      |

| Test Circuits                                        |      |

| Operation                                            |      |

| Power Module Introduction                            | .22  |

| Power Module Configurability and                     |      |

| Readback Data                                        | . 24 |

| Time-Averaged and Peak Readback Data                 |      |

| Power Module Overview                                |      |

| EEPROM                                               |      |

| Additional Information                               |      |

| Applications Information                             |      |

| LTM4676 Control IC Differences from LTC3880          |      |

| V <sub>IN</sub> to V <sub>OUT</sub> Step-Down Ratios |      |

| Input Capacitors                                     |      |

| Output Capacitors                                    |      |

| Light Load Current Operation                         |      |

| Switching Frequency and Phase                        |      |

| Minimum On-Time Considerations                       |      |

| Variable Delay Time, Soft-Start and Output Voltag    |      |

| Ramping                                              |      |

| ······································               |      |

| Digital Servo Mode                                     | . 49 |

|--------------------------------------------------------|------|

| Soft Off (Sequenced Off)                               | .50  |

| Undervoltage Lockout                                   | . 50 |

| Fault Conditions                                       | . 51 |

| Open-Drain Pins                                        |      |

| Phase-Locked Loop and Frequency                        |      |

| Synchronization                                        | . 52 |

| RCONFIG Pin-Straps (External Resistor                  |      |

| Configuration Pins)                                    | . 52 |

| Voltage Selection                                      | . 52 |

| Connecting the USB to the I <sup>2</sup> C/SMBus/PMBus |      |

| Controller to the LTM4676 In System                    | .53  |

| LTpowerPlay: An Interactive GUI for Digital Power      |      |

| System Management                                      | .54  |

| PMBus Communication and Command                        |      |

| Processing                                             | .56  |

| Thermal Considerations and                             |      |

| Output Current Derating                                | .58  |

| EMI Performance                                        | .66  |

| Safety Considerations                                  | .67  |

| Layout Checklist/Example                               | .67  |

| Typical Applications                                   |      |

| Package Description                                    | . 74 |

| Package Photograph                                     |      |

| Package Description                                    | . 76 |

| Revision History                                       | . 77 |

| Typical Application                                    | . 78 |

| Design Resources                                       |      |

| Related Parts                                          | . 78 |

The LTC3880 data sheet is an essential reference document for this product. To obtain it go to:

www.linear.com/LTC3880

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

#### **Terminal Voltages:**

| V <sub>INn</sub> (Note 4), SV <sub>IN</sub> –0.3V to 28V                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OUT</sub> <i>n</i> –0.3V to 6V                                                                                             |

| V <sub>OSNS0</sub> <sup>+</sup> , V <sub>ORB0</sub> <sup>+</sup> –0.3V to 4.25V                                                   |

| V <sub>OSNS1</sub> , V <sub>ORB1</sub> , INTV <sub>CC</sub> , I <sub>SNSna</sub> <sup>+</sup> , I <sub>SNSnb</sub> <sup>+</sup> , |

| $I_{SNSna}$ , $I_{SNSnb}$                                                                                                         |

| RUN <sub>n</sub> , SDA, SCL, <u>ALERT</u> –0.3V to 5.5V                                                                           |

| F <sub>SWPHCFG</sub> , V <sub>OUTnCFG</sub> , V <sub>TRIMnCFG</sub> , ASEL –0.3V to 2.75V                                         |

| V <sub>DD33</sub> , <u>GPIO</u> <sub>n</sub> , SYNC, SHARE_CLK, WP, TSNS <sub>na</sub> ,                                          |

| $COMP_{na}$ , $COMP_{nb}$ , $V_{OSNS0}^{-}$ , $V_{ORB0}^{-}$ 0.3V to 3.6V                                                         |

| SGND0.3V to 0.3V                                                                                                                  |

| Terminal Currents                                                                                                                 |

| INTVoo Peak Output Current 100mA                                                                                                  |

| INTV <sub>CC</sub> Peak Output Current | 100mA           |

|----------------------------------------|-----------------|

| V <sub>DD25</sub>                      | –1.5mA to 1.5mA |

| TSNS <sub>nb</sub>                     | –1mA to 10mA    |

#### Temperatures

| Internal Operating Temperature Range              |

|---------------------------------------------------|

| (Notes 2, 3)–40°C to 125°C                        |

| Storage Temperature Range –55°C to 125°C          |

| Peak Package Body Temperature During Reflow 245°C |

#### PIN CONFIGURATION

WEIGHT = 3.3 GRAMS

#### ORDER INFORMATION

| PART NUMBER   | PAD OR BALL FINISH | PART MARKING* |             | PACKAGE | MSL    | TEMPERATURE RANGE |

|---------------|--------------------|---------------|-------------|---------|--------|-------------------|

|               |                    | DEVICE        | FINISH CODE | TYPE    | RATING | (See Note 2)      |

| LTM4676EY#PBF | SAC305 (RoHS)      | LTM4676Y      | e1          | BGA     | 4      | -40°C to 125°C    |

| LTM4676IY#PBF | SAC305 (RoHS)      | LTM4676Y      | e1          | BGA     | 4      | -40°C to 125°C    |

| LTM4676IY     | SnPb (63/37)       | LTM4676Y      | eO          | BGA     | 4      | -40°C to 125°C    |

Consult Marketing for parts specified with wider operating temperature ranges. \*Device temperature grade is indicated by a label on the shipping container. Pad or ball finish code is per IPC/JEDEC J-STD-609.

• Terminal Finish Part Marking: www.linear.com/leadfree

Recommended LGA and BGA PCB Assembly and Manufacturing Procedures: www.linear.com/umodule/pcbassembly

• LGA and BGA Package and Tray Drawings: www.linear.com/packaging

| SYMBOL                                     | PARAMETER                                                      | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | MIN            | TYP            | MAX            | UNITS             |

|--------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|-------------------|

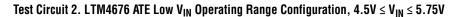

| V <sub>IN</sub>                            | Input DC Voltage                                               | Test Circuit 1<br>Test Circuit 2; VIN_OFF < VIN_ON = 4.25V                                                                                                                                                                                                                                                                                                                                                                                                      | • | 5.75<br>4.5    |                | 26.5<br>5.75   | V<br>V            |

| V <sub>OUTO</sub>                          | Range of Output Voltage<br>Regulation, Channel O               | $V_{OUT0}$ Differentially Sensed on $V_{OSNS0}^+/V_{OSNS0}^-$ Pin-Pair; Commanded by Serial Bus or with Resistors Present at Start-Up on $V_{OUT0CFG}$ and/or $V_{TRIM0CFG}$                                                                                                                                                                                                                                                                                    | • | 0.5            |                | 4.0            | V                 |

| V <sub>OUT1</sub>                          | Range of Output Voltage<br>Regulation, Channel 1               | $V_{OUT1}$ Differentially Sensed on $V_{OSNS1}/SGND$ Pin-Pair; Commanded by Serial Bus or with Resistors Present at Start-Up on $V_{OUT1CFG}$ and/ or $V_{TRIM1CFG}$                                                                                                                                                                                                                                                                                            | • | 0.5            |                | 5.4            | V                 |

| V <sub>OUT<i>n</i>(DC)</sub>               | Output Voltage, Total<br>Variation with Line and<br>Load       | Digital Servo Engaged (MFR_PWM_MODE <sub>n</sub> [6] = 1 <sub>b</sub> )<br>Digital Servo Disengaged (MFR_PWM_MODE <sub>n</sub> [6] = 0 <sub>b</sub> )<br>$V_{OUTn}$ Commanded to 1.000V, $V_{OUTn}$ Low Range<br>(MFR_PWM_CONFIG[6-n] = 1 <sub>b</sub> ), FREQUENCY_SWITCH = 250kHz<br>(Note 5)                                                                                                                                                                 | • | 0.990<br>0.985 | 1.000<br>1.000 | 1.010<br>1.015 | VV                |

| Input Specification                        | IS                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                |                |                |                   |

| IINRUSH(VIN)                               | Input Inrush Current at<br>Start-Up                            | Test Circuit 1, $V_{OUTn}$ =1V, $V_{IN}$ = 12V; No Load Besides Capacitors; TON_RISE <sub>n</sub> = 3ms                                                                                                                                                                                                                                                                                                                                                         |   |                | 400            |                | mA                |

| I <sub>Q(SVIN)</sub>                       | Input Supply Bias Current                                      | Forced Continuous Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $10_b$<br>RUN <sub>n</sub> = 5V, RUN <sub>1-n</sub> = 0V<br>Shutdown, RUN <sub>0</sub> = RUN <sub>1</sub> = 0V                                                                                                                                                                                                                                                                                        |   |                | 40<br>20       |                | mA<br>mA          |

| I <sub>S(VIN<i>n</i>,BURST)</sub>          | Input Supply Current in Burst Mode <sup>®</sup> Operation      | Burst Mode Operation, MFR_PWM_MODE <sub>n</sub> [1:0] = $01_b$ ,<br>$I_{OUTn} = 100mA$                                                                                                                                                                                                                                                                                                                                                                          |   |                | 15             |                | mA                |

| I <sub>S(VIN<i>n</i>,PSM)</sub>            | Input Supply Current in<br>Pulse-Skipping Mode<br>Operation    | Pulse-Skipping Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $00_b$ ,<br>$I_{OUTn} = 100mA$                                                                                                                                                                                                                                                                                                                                                                           |   |                | 20             |                | mA                |

| I <sub>S(VIN<i>n</i>,FCM)</sub>            | Input Supply Current in<br>Forced-Continuous Mode<br>Operation | Forced Continuous Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $10_b$<br>I <sub>OUTn</sub> = 100mA<br>I <sub>OUTn</sub> = 13A                                                                                                                                                                                                                                                                                                                                        |   |                | 40<br>1.37     |                | mA<br>A           |

| I <sub>S(VIN<i>n</i>,SHUTDOWN)</sub>       | Input Supply Current in Shutdown                               | Shutdown, $RUN_n = 0V$                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                | 50             |                | μA                |

| Output Specificatio                        | ons                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                |                |                |                   |

| I <sub>OUT</sub> n                         | Output Continuous<br>Current Range                             | (Note 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 0              |                | 13             | A                 |

| $\frac{\Delta V_{OUTn(LINE)}}{V_{OUTn}}$   | Line Regulation Accuracy                                       | Digital Servo Engaged (MFR_PWM_MODE_n[6] = 1 <sub>b</sub> )<br>Digital Servo Disengaged (MFR_PWM_MODE_n[6] = 0 <sub>b</sub> )<br>SV <sub>IN</sub> and V <sub>INn</sub> Electrically Shorted Together and INTV <sub>CC</sub> Open Circuit;<br>I <sub>OUT,n</sub> = 0A, 5.75V $\leq$ V <sub>IN</sub> $\leq$ 26.5V, V <sub>OUT</sub> Low Range<br>(MFR_PWM_CONFIG[6-n] = 1 <sub>b</sub> ) FREQUENCY_SWITCH = 250kHz<br>(Referenced to 12V <sub>IN</sub> ) (Note 5) | • |                | 0.03<br>0.03   | ±0.2           | %<br>%/V          |

| $\frac{\Delta V_{OUT n(LOAD)}}{V_{OUT n}}$ | Load Regulation<br>Accuracy                                    | Digital Servo Engaged (MFR_PWM_MODE <sub>n</sub> [6] = 1 <sub>b</sub> )<br>Digital Servo Disengaged (MFR_PWM_MODE <sub>n</sub> [6] = 0 <sub>b</sub> )<br>$OA \le I_{OUTn} \le 13A$ , $V_{OUT}$ Low Range, (MFR_PWM_CONFIG[6-n] = 1 <sub>b</sub> )<br>FREQUENCY_SWITCH = 250kHz (Note 5)                                                                                                                                                                         | • |                | 0.03<br>0.2    | 0.5            | %                 |

| V <sub>OUT<i>n</i>(AC)</sub>               | Output Voltage Ripple                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                | 10             |                | mV <sub>P-P</sub> |

| f <sub>S</sub> (Each Channel)              | V <sub>OUT</sub> n Ripple Frequency                            | FREQUENCY_SWITCH Set to 500kHz (0xFBE8)                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 462.5          | 500            | 537.5          | kHz               |

| $\Delta V_{OUT n(START)}$                  | Turn-On Overshoot                                              | $TON\_RISE_n = 3ms$ (Note 12)                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                | 8              |                | mV                |

| t <sub>START</sub>                         | Turn-On Start-Up Time                                          | Time from V <sub>IN</sub> Toggling from 0V to 12V to Rising Edge of $\overline{\text{GPIO}}_n$ .<br>TON_DELAY <sub>n</sub> = 0ms, TON_RISE <sub>n</sub> = 3ms,<br>MFR_GPI0_PROPAGATE <sub>n</sub> = 0x0100,<br>MFR_GPI0_RESPONSE <sub>n</sub> = 0x0000                                                                                                                                                                                                          |   |                | 153            | 170            | ms                |

LINTAR

ΙΤ

| SYMBOL                            | PARAMETER                                                               | CONDITIONS                                                                                                                                                                                                                                                                                                          |      | MIN      | TYP                               | MAX          | UNITS           |

|-----------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-----------------------------------|--------------|-----------------|

| tDELAY(0ms)                       | Turn-On Delay Time                                                      | Time from First Rising Edge of RUN <sub>n</sub> to Rising Edge of $\overline{\text{GPIO}}_n$ .<br>TON_DELAY <sub>n</sub> = 0ms, TON_RISE <sub>n</sub> = 3ms,<br>MFR_GPIO_PROPAGATE <sub>n</sub> = 0x0100,<br>MFR_GPIO_RESPONSE <sub>n</sub> = 0x0000.<br>V <sub>IN</sub> Having Been Established for at Least 170ms | •    | 2.75     | 3.1                               | 3.5          | ms              |

| $\Delta V_{OUTn(LS)}$             | Peak Output Voltage<br>Deviation for Dynamic<br>Load Step               | Load: OA to 6.5A and 6.5A to OA at 6.5A/ $\mu$ s, Figure 44 Circuit, V <sub>OUT<i>n</i></sub> = 1V, V <sub>IN</sub> = 12V (Note 12)                                                                                                                                                                                 |      |          | 50                                |              | mV              |

| t <sub>SETTLE</sub>               | Settling Time for<br>Dynamic Load Step                                  | Load: OA to 6.5A and 6.5A to 0A at 6.5A/ $\mu$ s, Figure 44 Circuit, V <sub>OUT</sub> = 1V, V <sub>IN</sub> = 12V (Note 12)                                                                                                                                                                                         |      |          | 35                                |              | μs              |

| I <sub>OUT<i>n</i>(OCL_PK)</sub>  | Output Current Limit,<br>Peak                                           | Cycle-by-Cycle Inductor Peak Current Limit Inception                                                                                                                                                                                                                                                                |      |          | 22.5                              |              | A               |

| I <sub>OUT<i>n</i>(OCL_AVG)</sub> | Output Current Limit,<br>Time Averaged                                  | Time-Averaged Output Inductor Current Limit Inception Threshold,<br>Commanded by IOUT_OC_FAULT_LIMIT <sub>n</sub> (Note 12)                                                                                                                                                                                         |      | Specif   | 5.6A; See<br>ication (<br>eadback | Output C     | urrent          |

| Control Section                   |                                                                         |                                                                                                                                                                                                                                                                                                                     |      |          |                                   |              |                 |

| VFBCM0                            | Channel 0 Feedback Input<br>Common Mode Range                           | V <sub>OSNS0</sub> <sup>-</sup> Valid Input Range (Referred to SGND)<br>V <sub>OSNS0</sub> <sup>+</sup> Valid Input Range (Referred to SGND)                                                                                                                                                                        | •    | -0.1     |                                   | 0.3<br>4.25  | V<br>V          |

| V <sub>FBCM1</sub>                | Channel 1 Feedback Input<br>Common Mode Range                           | SGND Valid Input Range (Referred to GND)<br>V <sub>OSNS1</sub> Valid Input Range (Referred to SGND)                                                                                                                                                                                                                 | •    | -0.3     |                                   | 0.3<br>5.5   | V<br>V          |

| V <sub>OUTO-RNGO</sub>            | Channel O Full-Scale<br>Command Voltage,<br>Range O                     | (Notes 7, 15)<br>V <sub>OUTO</sub> Commanded to 4.095V, MFR_PWM_CONFIG[6] = 0 <sub>b</sub><br>Resolution<br>LSB Step Size                                                                                                                                                                                           |      | 4.015    | 12<br>1.375                       | 4.176        | V<br>Bits<br>mV |

| Vouto-rng1                        | Channel 0 Full-Scale<br>Command Voltage,<br>Range 1                     | (Notes 7, 15)<br>V <sub>OUT0</sub> Commanded to 2.750V, MFR_PWM_CONFIG[6] = 1 <sub>b</sub><br>Resolution<br>LSB Step Size                                                                                                                                                                                           |      | 2.711    | 12<br>0.6875                      | 2.788        | V<br>Bits<br>mV |

| Vout1-rngo                        | Channel 1 Full-Scale<br>Command Voltage,<br>Range 0                     | (Notes 7, 15)<br>V <sub>OUT1</sub> Commanded to 5.500V, MFR_PWM_CONFIG[5] = 0 <sub>b</sub><br>Resolution<br>LSB Step Size                                                                                                                                                                                           |      | 5.422    | 12<br>1.375                       | 5.576        | V<br>Bits<br>mV |

| V <sub>OUT1-RNG1</sub>            | Channel 1 Full-Scale<br>Command Voltage,<br>Range 1                     | (Notes 7, 15)<br>V <sub>OUT1</sub> Commanded to 2.750V, MFR_PWM_CONFIG[5] = 1 <sub>b</sub><br>Resolution<br>LSB Step Size                                                                                                                                                                                           |      | 2.711    | 12<br>0.6875                      | 2.788        | V<br>Bits<br>mV |

| R <sub>VSENSE0</sub> <sup>+</sup> | V <sub>OSNS0</sub> <sup>+</sup> Impedance to<br>SGND                    | $0.05V \le V_{VOSNS0}^{+} - V_{SGND} \le 4.1V$                                                                                                                                                                                                                                                                      |      |          | 41                                |              | kΩ              |

| R <sub>VSENSE1</sub>              | V <sub>OSNS1</sub> Impedance to<br>SGND                                 | $0.05V \le V_{VOSNS1} - V_{SGND} \le 5.5V$                                                                                                                                                                                                                                                                          |      |          | 37                                |              | kΩ              |

| t <sub>ON(MIN)</sub>              | Minimum On-Time                                                         | (Note 8 )                                                                                                                                                                                                                                                                                                           |      |          | 90                                |              | ns              |

|                                   | vervoltage/Undervoltage) Outp                                           | but Voltage Supervisor Comparators (VOUT_OV/UV_FAULT_LIMIT and                                                                                                                                                                                                                                                      | VOUT | _OV/UV   | WARN                              | LIMIT Mo     | onitors)        |

| N <sub>OV/UV_COMP</sub>           | Resolution, Output<br>Voltage Supervisors,<br>Channels 0 and 1          | (Note 15)                                                                                                                                                                                                                                                                                                           |      |          | 8                                 |              | Bits            |

| V0 <sub>OU-RNG</sub>              | Output Voltage<br>Comparator Threshold<br>Detection Range,<br>Channel O | (Note 15)<br>High Range Scale, MFR_PWM_CONFIG[6] = 0 <sub>b</sub><br>Low Range Scale, MFR_PWM_CONFIG[6] = 1 <sub>b</sub>                                                                                                                                                                                            |      | 1<br>0.5 |                                   | 4.095<br>2.7 | V<br>V          |

| SYMBOL                          | PARAMETER                                                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                  |   | MIN      | ТҮР       | MAX             | UNITS        |

|---------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-----------|-----------------|--------------|

| V0 <sub>OU-STP</sub>            | Output Voltage<br>Comparator Threshold<br>Programming LSB Step<br>Size, Channel O                   | (Note 15)<br>High Range Scale, MFR_PWM_CONFIG[6] = 0 <sub>b</sub><br>Low Range Scale, MFR_PWM_CONFIG[6] = 1 <sub>b</sub>                                                                                                                                                                                                                    |   |          | 22<br>11  |                 | mV<br>mV     |

| V0 <sub>OU-ACC</sub>            | Output Voltage<br>Comparator Threshold<br>Accuracy, Channel O                                       | $ \begin{array}{l} (\text{See Note 14}) \\ 2V \leq V_{VOSNS0}^{+} - V_{VOSNS0}^{-} \leq 4.095V, \mbox{ MFR_PWM_CONFIG[6]} = 0_b \\ 1V \leq V_{VOSNS0}^{+} - V_{VOSNS0}^{-} \leq 2.7V, \mbox{ MFR_PWM_CONFIG[6]} = 1_b \\ 0.5V \leq V_{VOSNS0}^{+} - V_{VOSNS0}^{-} < 1V, \mbox{ MFR_PWM_CONFIG[6]} = 1_b \end{array} $                      | • |          |           | ±2<br>±2<br>±20 | %<br>%<br>mV |

| V1 <sub>OU-RNG</sub>            | Output Voltage<br>Comparator Threshold<br>Detection Range,<br>Channel 1                             | (Note 15)<br>High Range Scale, MFR_PWM_CONFIG[5] = 0 <sub>b</sub><br>Low Range Scale, MFR_PWM_CONFIG[5] = 1 <sub>b</sub>                                                                                                                                                                                                                    |   | 1<br>0.5 |           | 5.5<br>2.7      | V<br>V       |

| V1 <sub>OU-STP</sub>            | Output Voltage<br>Comparator Threshold<br>Programming LSB Step<br>Size, Channel 1                   | (Note 15)<br>High Range Scale, MFR_PWM_CONFIG[5] = 0 <sub>b</sub><br>Low Range Scale, MFR_PWM_CONFIG[5] = 1 <sub>b</sub>                                                                                                                                                                                                                    |   |          | 22<br>11  |                 | mV<br>mV     |

| V1 <sub>OU-ACC</sub>            | Output Voltage<br>Comparator Threshold<br>Accuracy, Channel 1                                       | $\begin{array}{l} (\text{See Note 14}) \\ 2V \leq V_{VOSNS1} - V_{SGND} \leq 5.5V, \ \text{MFR}\_\text{PWM}\_\text{CONFIG[5]} = 0_b \\ 1.5V \leq V_{VOSNS1} - V_{SGND} \leq 2.7V, \ \text{MFR}\_\text{PWM}\_\text{CONFIG[5]} = 1_b \\ 0.5V \leq V_{VOSNS1} - V_{SGND} < 1.5V, \ \text{MFR}\_\text{PWM}\_\text{CONFIG[5]} = 1_b \end{array}$ | • |          |           | ±2<br>±2<br>±30 | %<br>%<br>mV |

| t <sub>PROP-OV</sub>            | Output OV Comparator<br>Response Times,<br>Channels 0 and 1                                         | Overdrive to 10% Above Programmed Threshold                                                                                                                                                                                                                                                                                                 |   |          |           | 35              | μs           |

| t <sub>PROP-UV</sub>            | Output UV Comparator<br>Response Times,<br>Channels 0 and 1                                         | Underdrive to 10% Below Programmed Threshold                                                                                                                                                                                                                                                                                                |   |          |           | 50              | μs           |

| Analog OV/UV SV <sub>II</sub>   | Input Voltage Supervisor                                                                            | Comparators (Threshold Detectors for VIN_ON and VIN_OFF)                                                                                                                                                                                                                                                                                    |   |          |           |                 |              |

| N <sub>SVIN-OV/UV-COMP</sub>    | SV <sub>IN</sub> OV/UV Comparator<br>Threshold-Programming<br>Resolution                            | (Note 15)                                                                                                                                                                                                                                                                                                                                   |   |          | 8         |                 | Bits         |

| SV <sub>IN-OU-RANGE</sub>       | SV <sub>IN</sub> OV/UV Comparator<br>Threshold-Programming<br>Range                                 |                                                                                                                                                                                                                                                                                                                                             | • | 4.5      |           | 20              | V            |

| SV <sub>IN-OU-STP</sub>         | SV <sub>IN</sub> OV/UV Comparator<br>Threshold-Programming<br>LSB Step Size                         | (Note 15)                                                                                                                                                                                                                                                                                                                                   |   |          | 82        |                 | mV           |

| SV <sub>IN-OU-ACC</sub>         | SV <sub>IN</sub> OV/UV Comparator<br>Threshold Accuracy                                             | $9V < SV_{IN} \le 20V$<br>$4.5V \le SV_{IN} \le 9V$                                                                                                                                                                                                                                                                                         | • |          |           | ±2.5<br>±225    | %<br>mV      |

| t <sub>PROP-SVIN-HIGH-VIN</sub> | SV <sub>IN</sub> OV/UV Comparator<br>Response Time, High V <sub>IN</sub><br>Operating Configuration | Test Circuit 1, and:<br>VIN_ON = 9V; SV <sub>IN</sub> Driven from 8.775V to 9.225V<br>VIN_OFF = 9V; SV <sub>IN</sub> Driven from 9.225V to 8.775V                                                                                                                                                                                           | • |          |           | 35<br>35        | μs<br>µs     |

| t <sub>prop-svin-low-vin</sub>  | SV <sub>IN</sub> OV/UV Comparator<br>Response Time, Low V <sub>IN</sub><br>Operating Configuration  | Test Circuit 2, and:<br>VIN_ON = 4.5V; SV <sub>IN</sub> Driven from 4.225V to 4.725V<br>VIN_OFF = 4.5V; SV <sub>IN</sub> Driven from 4.725V to 4.225V                                                                                                                                                                                       | • |          |           | 35<br>35        | μs<br>µs     |

| Channels 0 and 1 (              | Output Voltage Readback (F                                                                          | READ_VOUT <sub>n</sub> )                                                                                                                                                                                                                                                                                                                    |   |          |           |                 |              |

| N <sub>VO-RB</sub>              | Output Voltage Readback<br>Resolution and LSB Step<br>Size                                          | (Note 15)                                                                                                                                                                                                                                                                                                                                   |   |          | 16<br>244 |                 | Bits<br>µV   |

| V <sub>0-F/S</sub>              | Output Voltage Full-Scale<br>Digitizable Range                                                      | V <sub>RUNn</sub> = 0V (Notes 7, 15)                                                                                                                                                                                                                                                                                                        |   |          | 8         |                 | V            |

6

| SYMBOL                                  | PARAMETER                                                                                   | CONDITIONS                                                                                                                                                                          |       | MIN                     | ТҮР               | MAX                  | UNITS      |

|-----------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|-------------------|----------------------|------------|

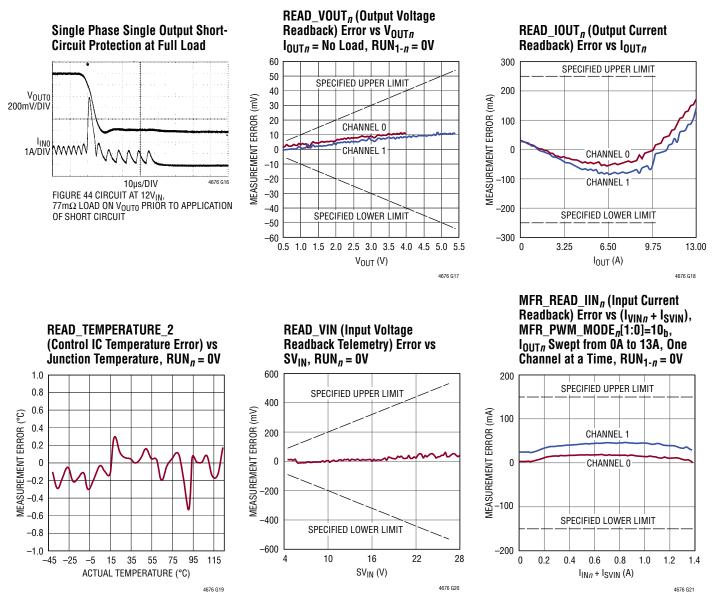

| V <sub>O-RB-ACC</sub>                   | Output Voltage Readback<br>Accuracy                                                         | Channel 0: 0.6V $\leq$ V <sub>VOSNS0</sub> <sup>+</sup> – V <sub>VOSNS0</sub> <sup>-</sup> $\leq$ 4V<br>Channel 1: 0.6V $\leq$ V <sub>VOSNS1</sub> – V <sub>SGND</sub> $\leq$ 5.4V  | •     |                         |                   | of Readi<br>of Readi |            |

| t <sub>CONVERT-VO-RB</sub>              | Output Voltage Readback<br>Update Rate                                                      | (Notes 9, 15)                                                                                                                                                                       |       |                         | 100               |                      | ms         |

| Input Voltage (SV                       | <sub>IN</sub> ) Readback (READ_VIN)                                                         |                                                                                                                                                                                     |       |                         |                   |                      |            |

| N <sub>SVIN-RB</sub>                    | Input Voltage Readback<br>Resolution and LSB Step<br>Size                                   | (Notes 10, 15)                                                                                                                                                                      |       |                         | 10<br>5.625       |                      | Bits<br>mV |

| SV <sub>IN-F/S</sub>                    | Input Voltage Full-Scale<br>Digitizable Range                                               | (Notes 11, 15)                                                                                                                                                                      |       | 3                       | 8.91              |                      | V          |

| SV <sub>IN-RB-ACC</sub>                 | Input Voltage Readback<br>Accuracy                                                          | $READ\_VIN, 4.5V \le SV_{IN} \le 26.5V$                                                                                                                                             | •     | Withir                  | 1 ±2%             | of Read              | ing        |

| t <sub>convert-svin-rb</sub>            | Input Voltage Readback<br>Update Rate                                                       | (Notes 9, 15)                                                                                                                                                                       |       |                         | 100               |                      | ms         |

| Channels 0 and 1 0                      | utput Current (READ_IOUT_)                                                                  | , Duty Cycle (READ_DUTY_CYCLE <sub>n</sub> ), and Computed Input Current (M                                                                                                         | FR_RE | AD_IIN <sub>n</sub> ) R | eadba             | k                    |            |

| N <sub>IO-RB</sub>                      | Output Current Readback<br>Resolution and LSB Step<br>Size                                  | (Notes 10, 12)                                                                                                                                                                      |       |                         | 10<br> 5.6        |                      | Bits<br>mA |

| I <sub>0-F/S</sub> , I <sub>I-F/S</sub> | Output Current Full-Scale<br>Digitizable Range and<br>Input Current Range of<br>Calculation | (Note 12)                                                                                                                                                                           |       |                         | ±40               |                      | A          |

| I <sub>O-RB-ACC</sub>                   | Output Current, Readback<br>Accuracy                                                        | READ_IOUT <sub>n</sub> , Channels 0 and 1, $0 \le I_{OUTn} \le 10A$ ,<br>Forced-Continuous Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $10_b$                                           | •     | Within 250mA of Readin  |                   |                      | ding       |

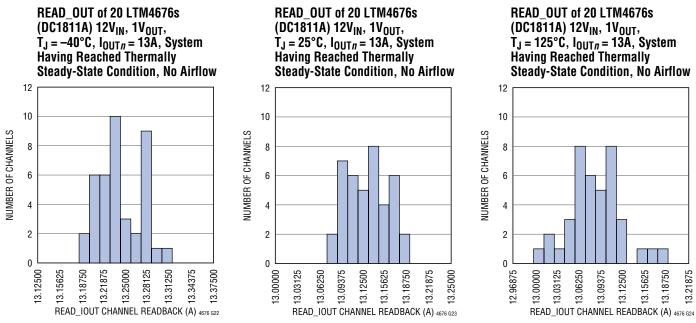

| I <sub>O-RB(13A)</sub>                  | Full Load Output Current<br>Readback                                                        | I <sub>OUT<i>n</i></sub> = 13A (Note 12). See Histograms in Typical Performance<br>Characteristics                                                                                  |       | -                       | 13.1              |                      | A          |

| N <sub>II-RB</sub>                      | Computed Input Current,<br>Readback Resolution and<br>LSB Step Size                         | (Notes 10, 12)                                                                                                                                                                      |       |                         | 10<br>I.95        |                      | Bits<br>mA |

| I <sub>I-RB-ACC</sub>                   | Computed Input Current,<br>Readback Accuracy,<br>Neglecting I <sub>SVIN</sub>               | MFR_READ_IIN <sub>n</sub> , Channels 0 and 1, $0 \le I_{OUTn} \le 10A$ ,<br>Forced-Continuous Mode, MFR_PWM_MODE <sub>n</sub> [1:0] = $10_b$ ,<br>MFR_IIN_OFFSET <sub>n</sub> = 0mA | •     | Within                  | 150m/             | A of Read            | ling       |

| t <sub>CONVERT-IO-RB</sub>              | Output Current Readback<br>Update Rate                                                      | (Notes 9, 15)                                                                                                                                                                       |       |                         | 100               |                      | ms         |

| t <sub>CONVERT-II-RB</sub>              | Computed Input Current,<br>Readback Update Rate                                             | (Notes 9, 15)                                                                                                                                                                       |       |                         | 100               |                      | ms         |

| N <sub>DUTY-RB</sub>                    | Resolution, Duty Cycle<br>Readback                                                          | (Notes 10, 15)                                                                                                                                                                      |       |                         | 10                |                      | Bits       |

| D <sub>RB-ACC</sub>                     | Duty Cycle TUE                                                                              | READ_DUTY_CYCLE <sub>n</sub> , 16.3% Duty Cycle (Note 15)                                                                                                                           |       |                         |                   | ±3                   | %          |

| t <sub>CONVERT</sub> -DUTY-RB           | Duty Cycle Readback<br>Update Rate                                                          | (Notes 9, 15)                                                                                                                                                                       |       |                         | 100               |                      | ms         |

| Temperature Read<br>and READ_TEMPE      |                                                                                             | el 1, and Controller (Respectively: READ_TEMPERATURE_1 <sub>0</sub> , REA                                                                                                           | D_TEM | PERATUR                 | _1 <sub>1</sub> , |                      |            |

| T <sub>RES-RB</sub>                     | Temperature Readback<br>Resolution                                                          | Channel 0, Channel 1, and Controller (Note 15)                                                                                                                                      |       | 0.                      | 0625              |                      | °C         |

| T <sub>RB-CH-ACC(72mV)</sub>            | Channel Temperature                                                                         | Channels 0 and 1, PWM Inactive, $RUN_n = 0V$ ,                                                                                                                                      |       | Withir                  | ±3°C              | of Read              | ing        |

| SYMBOL                                       | PARAMETER                                                                                                               | CONDITIONS                                                                                                                                                                               |          | MIN      | ТҮР                             | MAX          | UNITS                           |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|---------------------------------|--------------|---------------------------------|

| T <sub>RB-CTRL-ACC(ON)</sub>                 | Control IC Die<br>Temperature TUE,<br>Switching Action On                                                               | READ_TEMPERATURE_2, PWM Active, RUN <sub>0</sub> = RUN <sub>1</sub> = 5V<br>(Note 12)                                                                                                    |          | Wit      | hin ±1°(                        | c of Read    | ling                            |

| t <sub>CONVERT</sub> -TEMP-RB                | Temperature Readback<br>Update Rate                                                                                     | (Notes 9, 15)                                                                                                                                                                            |          |          | 100                             |              | ms                              |

| INTV <sub>CC</sub> Regulator                 | ·                                                                                                                       |                                                                                                                                                                                          |          |          |                                 |              |                                 |

| VINTVCC                                      | Internal V <sub>CC</sub> Voltage No<br>Load                                                                             | $6V \le V_{IN} \le 26.5V$                                                                                                                                                                | •        | 4.8      | 5                               | 5.2          | V                               |

| $\frac{\Delta V_{INTVCC(LOAD)}}{V_{INTVCC}}$ | INTV <sub>CC</sub> Load Regulation                                                                                      | $0mA \le I_{INTVCC} \le 50mA$                                                                                                                                                            |          |          | 0.5                             | ±2           | %                               |

| V <sub>DD33</sub> Regulator                  |                                                                                                                         | I                                                                                                                                                                                        |          |          |                                 |              |                                 |

| V <sub>VDD33</sub>                           | Internal V <sub>DD33</sub> Voltage                                                                                      |                                                                                                                                                                                          |          | 3.2      | 3.3                             | 3.4          | V                               |

| ILIM(VDD33)                                  | V <sub>DD33</sub> Current Limit                                                                                         | V <sub>DD33</sub> Electrically Short-Circuited to GND                                                                                                                                    | <b>–</b> | 0.2      | 70                              | 0.1          | mA                              |

| V <sub>VDD33_0V</sub>                        | V <sub>DD33</sub> Overvoltage<br>Threshold                                                                              | (Note 15)                                                                                                                                                                                |          |          | 3.5                             |              | V                               |

| V <sub>VDD33_UV</sub>                        | V <sub>DD33</sub> Undervoltage<br>Threshold                                                                             | (Note 15)                                                                                                                                                                                |          |          | 3.1                             |              | V                               |

| V <sub>DD25</sub> Regulator                  | 1                                                                                                                       | I                                                                                                                                                                                        |          | <u> </u> |                                 |              | I                               |

| V <sub>VDD25</sub>                           | Internal V <sub>DD25</sub> Voltage                                                                                      |                                                                                                                                                                                          |          | 2.25     | 2.5                             | 2.75         | V                               |

| ILIM(VDD25)                                  | V <sub>DD25</sub> Current Limit                                                                                         | V <sub>DD25</sub> Electrically Short-Circuited to GND                                                                                                                                    |          |          | 50                              | -            | mA                              |

|                                              | ase-Locked Loop (PLL)                                                                                                   |                                                                                                                                                                                          |          | L        |                                 |              | L                               |

| f <sub>OSC</sub>                             | Oscillator Frequency<br>Accuracy                                                                                        | FREQUENCY_SWITCH = 500kHz (0xFBE8)<br>250kHz ≤ FREQUENCY_SWITCH ≤ 1MHz (Note 15)                                                                                                         | •        |          |                                 | ±7.5<br>±7.5 | %                               |

| f <sub>SYNC</sub>                            | PLL SYNC Capture Range                                                                                                  | FREQUENCY_SWITCH Set to Frequency Slave Mode (0x0000);<br>SYNC Driven by External Clock; 3.3V <sub>OUT</sub>                                                                             | •        | 225      |                                 | 1100         | kHz                             |

| V <sub>TH,SYNC</sub>                         | SYNC Input Threshold                                                                                                    | V <sub>SYNC</sub> Rising (Note 15)<br>V <sub>SYNC</sub> Falling (Note 15)                                                                                                                |          |          | 1.5<br>1                        |              | V<br>V                          |

| VOL,SYNC                                     | SYNC Low Output<br>Voltage                                                                                              | I <sub>SYNC</sub> = 3mA                                                                                                                                                                  | •        |          | 0.3                             | 0.4          | V                               |

| ISYNC                                        | SYNC Leakage Current in<br>Frequency Slave Mode                                                                         | $0V \le V_{SYNC} \le 3.6V$<br>FREQUENCY_SWITCH Set to Slave Mode (0x0000)                                                                                                                | •        |          |                                 | ±5           | μA                              |

| θ <sub>SYNC</sub> -θΟ                        | SYNC-to-Channel 0<br>Phase Relationship, Lag<br>from Falling Edge of Sync<br>to Rising Edge of Top<br>MOSFET (MT0) Gate | (Note 15)<br>MFR_PWM_CONFIG[2:0] = $000_b$ , $01X_b$<br>MFR_PWM_CONFIG[2:0] = $101_b$<br>MFR_PWM_CONFIG[2:0] = $001_b$<br>MFR_PWM_CONFIG[2:0] = $1X0_b$                                  |          |          | 0<br>60<br>90<br>120            |              | Deg<br>Deg<br>Deg<br>Deg        |

| θ <sub>SYNC</sub> -θ1                        | SYNC-to-Channel 1<br>Phase Relationship, Lag<br>from Falling Edge of Sync<br>to Rising Edge of Top<br>MOSFET (MT1) Gate | (Note 15)<br>MFR_PWM_CONFIG[2:0] = $011_b$<br>MFR_PWM_CONFIG[2:0] = $000_b$<br>MFR_PWM_CONFIG[2:0] = $010_b$ , $10X_b$<br>MFR_PWM_CONFIG[2:0] = $001_b$<br>MFR_PWM_CONFIG[2:0] = $110_b$ |          |          | 120<br>180<br>240<br>270<br>300 |              | Deg<br>Deg<br>Deg<br>Deg<br>Deg |

| EEPROM Characte                              | eristics                                                                                                                |                                                                                                                                                                                          |          |          |                                 |              |                                 |

| Endurance                                    | (Note 13)                                                                                                               | $0^{\circ}C \leq T_J \leq 85^{\circ}C$ During EEPROM Write Operations (Note 3)                                                                                                           | •        | 10,000   |                                 |              | Cycles                          |

| Retention                                    | (Note 13)                                                                                                               | $T_J < T_{J(MAX)},$ with Most Recent EEPROM Write Operation Having Occurred at 0°C $\leq T_J \leq 85$ °C (Note 3)                                                                        | •        | 10       |                                 |              | Years                           |

| Mass_Write                                   | Mass Write Operation<br>Time                                                                                            | Execution of STORE_USER_ALL Command, $0^{\circ}C \le T_{J} \le 85^{\circ}C$<br>(ATE-Tested at $T_{J} = 25^{\circ}C$ ) (Notes 3, 13)                                                      |          |          | 440                             | 4100         | ms                              |

Digital I/Os

| SYMBOL                   | PARAMETER                                   | CONDITIONS                                                                                                                                                                                             |   | MIN        | ТҮР       | MAX        | UNITS    |

|--------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-----------|------------|----------|

| V <sub>IH</sub>          | Input High Threshold<br>Voltage             | SCL, SDA, RUN <sub>n</sub> , <u>GPIO</u> n (Note 15)<br>SHARE_CLK, WP (Note 15)                                                                                                                        |   | 2.0<br>1.8 |           |            | V<br>V   |

| V <sub>IL</sub>          | Input Low Threshold<br>Voltage              | SCL, SDA, RUN <sub>n</sub> , <u>GPIO</u> n (Note 15)<br>SHARE_CLK, WP (Note 15)                                                                                                                        |   |            |           | 1.4<br>0.6 | V<br>V   |

| V <sub>HYST</sub>        | Input Hysteresis                            | SCL, SDA (Note 15)                                                                                                                                                                                     |   |            | 80        |            | mV       |

| V <sub>OL</sub>          | Output Low Voltage                          | SCL, SDA, $\overline{\text{ALERT}}$ , $\text{RUN}_{\eta}$ , $\overline{\text{GPIO}}_{\eta}$ , $\text{SHARE\_CLK}$ :<br>I <sub>SINK</sub> = 3mA                                                         | • |            | 0.3       | 0.4        | v        |

| I <sub>OL</sub>          | Input Leakage Current                       | SDA, SCL, $\overline{\text{ALERT}}$ , $\text{RUN}_n$ : $\text{OV} \le \text{V}_{\text{PIN}} \le 5.5\text{V}$<br>GPIO <sub>n</sub> and SHARE_CLK: $\text{OV} \le \text{V}_{\text{PIN}} \le 3.6\text{V}$ | • |            |           | ±5<br>±2   | μA<br>μA |

| t <sub>FILTER</sub>      | Input Digital Filtering                     | $\frac{\text{RUN}_n}{\text{GPIO}_n}$ (Note 15)                                                                                                                                                         |   |            | 10<br>3   |            | μs<br>μs |

| C <sub>PIN</sub>         | Input Capacitance                           | SCL, SDA, RUN <sub>n</sub> , GPIO <sub>n</sub> , SHARE_CLK, WP (Note 15)                                                                                                                               |   |            |           | 10         | pF       |

|                          | e Timing Characteristics                    |                                                                                                                                                                                                        |   |            |           |            |          |

| f <sub>SMB</sub>         | Serial Bus Operating<br>Frequency           | (Note 15)                                                                                                                                                                                              |   | 10         |           | 400        | kHz      |

| t <sub>BUF</sub>         | Bus Free Time Between<br>Stop and Start     | (Note 15)                                                                                                                                                                                              |   | 1.3        |           |            | μs       |

| t <sub>HD,STA</sub>      | Hold Time After Repeated<br>Start Condition | Time Period After Which First Clock Is Generated (Note 15)                                                                                                                                             |   | 0.6        |           |            | μs       |

| t <sub>SU,STA</sub>      | Repeated Start Condition<br>Setup Time      | (Note 15)                                                                                                                                                                                              |   | 0.6        |           |            | μs       |

| t <sub>SU,STO</sub>      | Stop Condition Setup<br>Time                | (Note 15)                                                                                                                                                                                              |   | 0.6        |           |            | μs       |

| t <sub>HD,DAT</sub>      | Data Hold Time                              | Receiving Data (Note 15)<br>Transmitting Data (Note 15)                                                                                                                                                |   | 0<br>0.3   |           | 0.9        | μs<br>μs |

| t <sub>su,dat</sub>      | Data Setup Time                             | Receiving Data (Note 15)                                                                                                                                                                               |   | 0.1        |           |            | μs       |

| t <sub>TIMEOUT_SMB</sub> | Stuck PMBus Timer<br>Timeout                | Measured from the Last PMBus Start Event:<br>Block Reads (Note 15)<br>Non-Block Reads (Note 15)                                                                                                        |   |            | 150<br>32 |            | ms<br>ms |

| t <sub>LOW</sub>         | Serial Clock Low Period                     | (Note 15)                                                                                                                                                                                              |   | 1.3        |           | 10000      | μs       |

| t <sub>HIGH</sub>        | Serial Clock High Period                    | (Note 15)                                                                                                                                                                                              |   | 0.6        |           |            | μs       |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listing under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating conditions for extended periods may affect device reliability and lifetime.

**Note 2:** The LTM4676 is tested under pulsed-load conditions such that  $T_J \approx T_A$ . The LTM4676E is guaranteed to meet performance specifications over the 0°C to 125°C internal operating temperature range. Specifications over the -40°C to 125°C internal operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTM4676I is guaranteed to meet specifications over the full -40°C to 125°C internal operating temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

**Note 3:** The LTM4676's EEPROM temperature range for valid write commands is 0°C to 85°C. To achieve guaranteed EEPROM data retention, execution of the "STORE\_USER\_ALL" command—i.e., uploading RAM contents to NVM—outside this temperature range is not recommended. However, as long as the LTM4676's EEPROM temperature is less than 130°C, the LTM4676 *will* obey the STORE\_USER\_ALL command. Only when EEPROM temperature exceeds 130°C, the LTM4676 will not act on any STORE\_USER\_ALL transactions: instead, the LTM4676 NACKs the serial command and asserts its relevant CML (communications, memory, logic) fault bits. EEPROM temperature can be queried prior to commanding STORE\_USER\_ALL; see the Applications Information section.

**Note 4:** The two power inputs— $V_{IN0}$  and  $V_{IN1}$ —and their respective power outputs— $V_{OUT0}$  and  $V_{OUT1}$ —are tested independently in production. A shorthand notation is used in this document that allows these parameters to be referred to by " $V_{INn}$ " and " $V_{OUTn}$ ", where *n* is permitted to take on a value of 0 or 1. This italicized, subscripted "*n*" notation and convention is extended to encompass all such pin names, as well as register names with channel-specific, i.e., paged data. For example, VOUT\_COMMAND<sub>n</sub> refers to the VOUT\_COMMAND command code data located in Pages 0 and 1, which in turn relate to Channels 0 ( $V_{OUT0}$ ) and Channel 1 ( $V_{OUT1}$ ). Registers containing non-page-specific data, i.e., whose data is "global" to the module or applies to both of the module's Channels lack the italicized, subscripted "*n*", e.g., FREQUENCY\_SWITCH.

**Note 5:**  $V_{OUTn(DC)}$  and line and load regulation tests are performed in production with digital servo disengaged (MFR\_PWM\_MODE<sub>n</sub>[6] = 0<sub>b</sub>) and low  $V_{OUTn}$  range selected (MFR\_PWM\_CONFIG[6-n] = 1<sub>b</sub>. The digital servo control loop is exercised in production (setting MFR\_PWM\_MODE<sub>n</sub>[6] = 1<sub>b</sub>), but convergence of the output voltage to its final settling value is not necessarily observed in final test—due to potentially long time constants involved—and is instead guaranteed by the output voltage readback accuracy specification. Evaluation in application demonstrates capability; see the Typical Performance Characteristics section.

**Note 6:** See output current derating curves for different  $V_{IN}$ ,  $V_{OUT}$ , and  $T_{A}$ , located in the Applications Information section.