Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

ON Semiconductor®

www.onsemi.com

## **Bi-CMOS IC**

# 1-channel Step-down Switching Regulator

#### Overview

The LV5768V-A is a 1-channel step-down switching regulator.

#### **Feature**

- 1 channel step-down switching regulator controller.

- Frequency decrease function at pendent.

- Load-independent soft start circuit.

- ON/OFF function.

- Built-in pulse-by-pulse OCP circuit. It is detected by using ON resistance of an external MOS.

- Synchronous rectification

- Current mode control

SSOP16(225mil)

### **Specifications**

**Absolute Maximum Ratings** at Ta = 25°C

|           | Parameter                                    | Symbol              | Conditions                       | Ratings              | Unit |

|-----------|----------------------------------------------|---------------------|----------------------------------|----------------------|------|

| Su        | pply voltage                                 | V <sub>IN</sub> max |                                  | 45                   | V    |

|           | V <sub>IN</sub> , SW                         |                     |                                  | 45                   | V    |

|           | HDRV, CBOOT                                  |                     |                                  | 52                   | V    |

| voltage   | LDRV                                         |                     |                                  | 6.0                  | V    |

| pin       | Between CBOOT to SW<br>Between CBOOT to HDRV |                     |                                  | 6.0                  | V    |

| Allowable | EN, ILIM                                     |                     |                                  | V <sub>IN</sub> +0.3 | V    |

| Allov     | Between V <sub>IN</sub> to ILIM              |                     |                                  | 1.0                  | V    |

|           | $V_{DD}$                                     |                     |                                  | 6.0                  | V    |

|           | SS, FB, COMP,RT                              |                     |                                  | V <sub>DD</sub> +0.3 | V    |

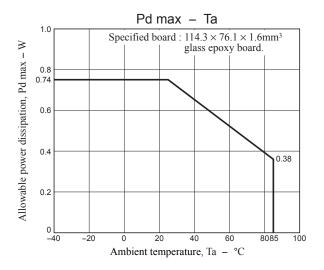

| All       | owable Power dissipation                     | Pd max              | Mounted on a specified board. *1 | 0.74                 | W    |

| Op        | erating temperature                          | Topr                |                                  | -40 to +85           | °C   |

| Sto       | orage temperature                            | Tstg                |                                  | -55 to +150          | °C   |

<sup>\*1</sup> Specified board: 114.3mm × 76.1mm × 1.6mm, glass epoxy board.

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 17 of this data sheet.

## **Recommended Operating Range** at Ta = 25°C

| Parameter                     | Symbol          | Conditions | Ratings   | Unit |

|-------------------------------|-----------------|------------|-----------|------|

| Supply voltage range          | V <sub>IN</sub> |            | 8.5 to 42 | V    |

| Error amplifier input voltage | V <sub>FB</sub> |            | 0 to 1.6  | ٧    |

| Oscillatory frequency         | Fosc            |            | 80 to 500 | kHz  |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## **Electrical Characteristics** at Ta = 25°C, $V_{IN} = 12V$

| Parameter                                         | Parameter Symbol Conditions |                                    | Ratings               |         | Unit     |               |

|---------------------------------------------------|-----------------------------|------------------------------------|-----------------------|---------|----------|---------------|

| r drameter                                        |                             | Conditions                         | min                   | typ     | max      | Unit          |

| Reference voltage block                           | _                           |                                    |                       |         |          |               |

| Internal reference voltage                        | Vref                        | Including offset of E/A            | 0.654                 | 0.67    | 0.686    | V             |

| 5V power supply                                   | $V_{DD}$                    | I <sub>OUT</sub> = 0 to 5mA        | 4.7                   | 5.2     | 5.7      | V             |

| Triangular waveform oscillator bloo               | k                           |                                    |                       |         |          |               |

| Oscillation frequency                             | Fosc                        | RT=220kΩ                           | 110                   | 125     | 140      | kHz           |

| Frequency variation                               | Fosc dv                     | V <sub>IN</sub> = 8.5 to 42V       |                       | 1       |          | %             |

| Oscillation frequency fold back detection voltage | V <sub>OSC</sub> FB         | FB voltage detection after SS ends |                       | 0.1     |          | V             |

| Oscillation frequency after fold back             | F <sub>OSC</sub> FB         |                                    |                       | 1/3Fosc |          | kHz           |

| ON/OFF circuit block                              |                             |                                    |                       |         |          |               |

| IC start-up voltage                               | V <sub>EN</sub> on          |                                    | 2.5                   | 3.0     | 3.5      | >             |

| IC off voltage                                    | V <sub>EN</sub> off         |                                    | 1.0                   | 1.2     | 1.4      | V             |

| Soft start circuit block                          |                             |                                    |                       |         |          |               |

| Soft start source current                         | I <sub>SS</sub> SC          | EN > 3.5V                          | 4                     | 5       | 6        | μΑ            |

| Soft start sink current                           | I <sub>SS</sub> SK          | EN < 1V, V <sub>DD</sub> = 5V      |                       | 2       |          | mA            |

| UVLO circuit block                                |                             |                                    |                       |         |          |               |

| UVLO lock release voltage                         | V <sub>UVLO</sub>           |                                    |                       | 8       |          | V             |

| UVLO hysteresis                                   | V <sub>UVLO</sub> H         |                                    |                       | 0.7     |          | V             |

| Error amplifier                                   | •                           | •                                  |                       | •       |          |               |

| Input bias current                                | IEA IN                      |                                    |                       |         | 100      | nA            |

| Error amplifier gain                              | G <sub>EA</sub>             |                                    | 1000                  | 1400    | 1800     | μ <b>A</b> /V |

| Sink output current                               | IEA OSK                     | FB = 1.0V                          |                       | -100    |          | μА            |

| Source output current                             | IEA OSC                     | FB = 0V                            |                       | 100     |          | μА            |

| Current detection amplifier gain                  | GISNS                       |                                    |                       | 1.5     |          |               |

| over current limiter circuit block                | •                           | •                                  |                       | •       |          |               |

| Reference current                                 | I <sub>LIM</sub> 1          |                                    | -10%                  | 18.5    | +10%     | μА            |

| Over current detection comparator                 | V <sub>LIM</sub> OFS        |                                    | -5                    |         | +5       | mV            |

| offset voltage                                    |                             |                                    |                       |         |          |               |

| Over current detection comparator                 |                             |                                    | V <sub>IN</sub> -0.45 |         | $v_{IN}$ | V             |

| common mode input range  PWM comparator           |                             |                                    |                       |         |          |               |

| Input threshold voltage                           | Vt max                      | Duty cycle = DMAX                  | 0.9                   | 1.0     | 1.1      | V             |

| (F <sub>OSC</sub> =125kHz)                        | Vt111ax<br>Vt0              | Duty cycle = 0%                    | 0.9                   | 0.5     | 0.6      | V             |

| Maximum ON duty                                   | DMAX                        | Duty Cycle = 0%                    | 86                    | 90      | 95       | %             |

| Output block                                      | DIVIAX                      |                                    | 00                    | 90      | 93       | /0            |

| Output block  Output stage ON resistance          | Povili                      |                                    |                       | 5       |          | Ω             |

| (the upper side)                                  | RONH                        |                                    |                       | 5       |          | 5.2           |

| Output stage ON resistance                        | R <sub>ONL</sub>            |                                    |                       | 5       |          | Ω             |

| (the lower side)                                  | OTAL                        |                                    |                       |         |          |               |

| Output stage ON current                           | IONH                        |                                    | 240                   |         |          | mA            |

| (the upper side)                                  |                             |                                    |                       |         |          | _             |

| Output stage ON current                           | IONL                        |                                    | 240                   |         |          | mA            |

| (the lower side)                                  |                             | <u> </u>                           |                       |         |          |               |

Continued on next page

Continued from preceding page.

| Parameter                              | Symbol  | Conditions             | Ratings |     |     | 1.1-4 |

|----------------------------------------|---------|------------------------|---------|-----|-----|-------|

| Parameter                              |         |                        | min     | typ | max | Unit  |

| The whole device                       |         |                        |         |     |     |       |

| Standby current                        | Iccs    | EN < 1V                |         |     | 10  | μА    |

| Mean consumption current               | ICCA    | EN > 3.5V              |         | 3   |     | mA    |

| Security function                      |         |                        |         |     |     |       |

| Protection function operating          | TSD on  | * Design certification |         | 170 |     | °C    |

| temperature at high temperature        |         |                        |         |     |     |       |

| Protection function hysteresis at high | TSD hys | * Design certification |         | 30  |     | °C    |

| temperature                            |         |                        |         |     |     |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

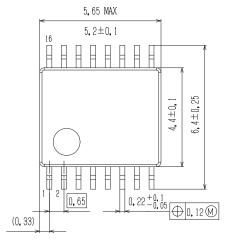

## **Package Dimensions**

unit: mm

## SSOP16 (225mil)

CASE 565AM ISSUE A

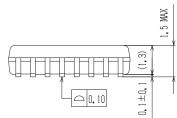

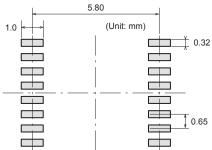

#### **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code

Y = Year M = Month

DDD = Additional Traceability Data

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " •", may or may not be present.

## **Pin Assignment**

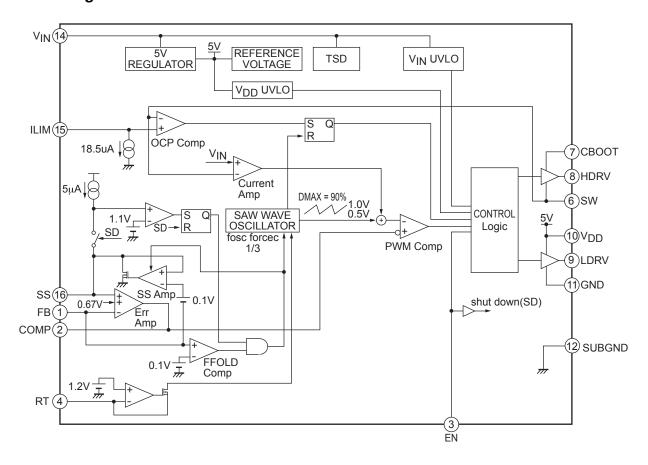

## **Block Diagram**

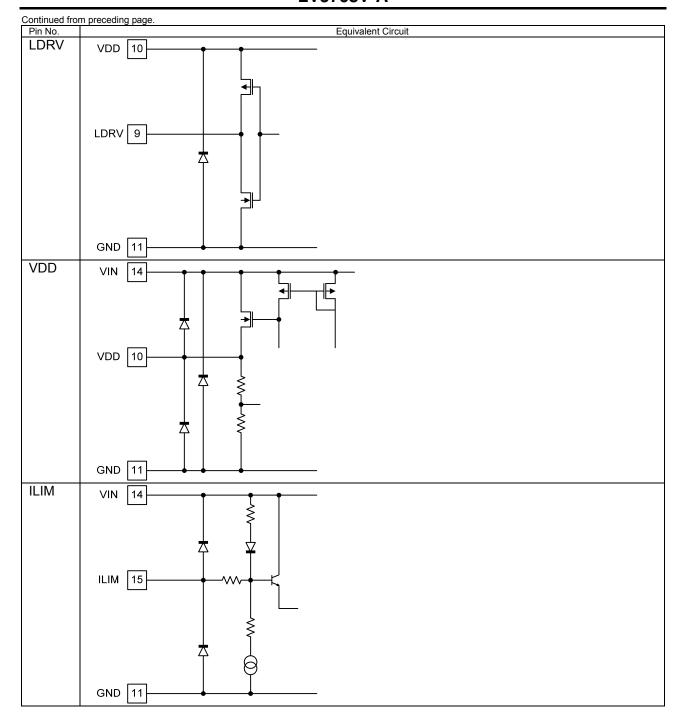

#### **Pin Function**

| Pin No. | Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

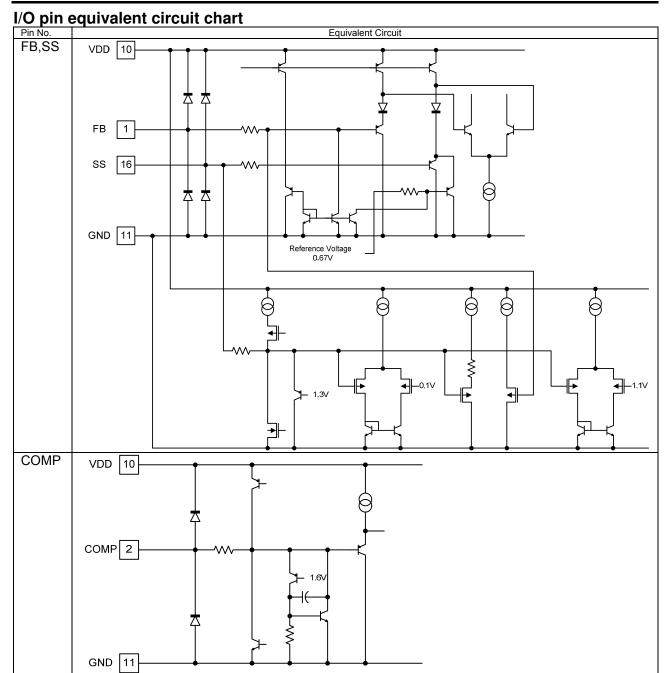

| 1       | FB       | Error amplifier reverse input pin. By operating the converter, the voltage of this pin becomes 0.67V.                                                                                                                                                                                                                                                                                                                  |

|         |          | The voltage in which the output voltage is divided by an external resistance is applied to this pin. Moreover, when this pin                                                                                                                                                                                                                                                                                           |

|         |          | voltage becomes 0.1V or less after a soft start ends, the oscillatory frequency becomes 1/3.                                                                                                                                                                                                                                                                                                                           |

| 2       | COMP     | Error amplifier output pin. Connect a phase compensation circuit between this pin and GND.                                                                                                                                                                                                                                                                                                                             |

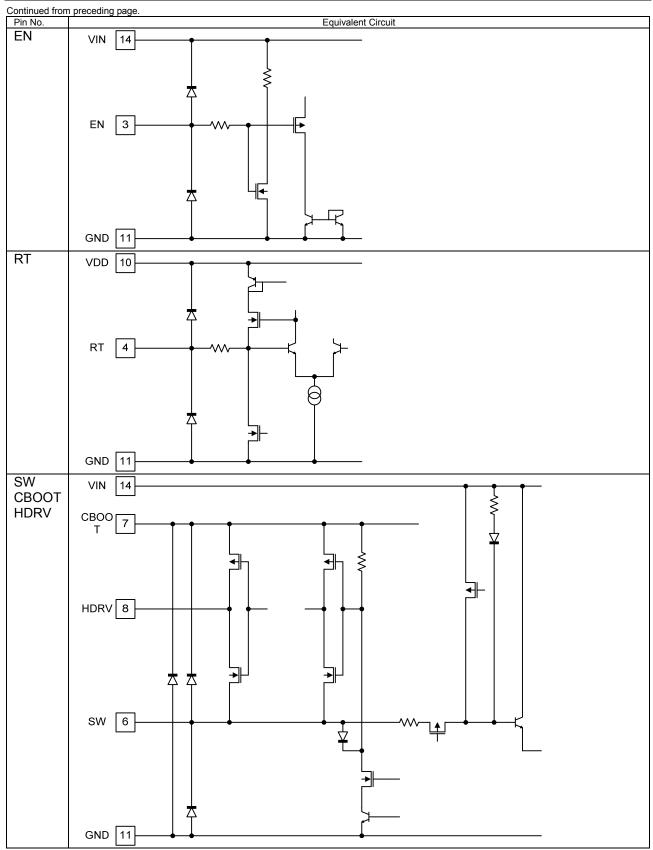

| 3       | EN       | ON/OFF pin.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4       | RT       | Oscillation frequency setting pin. Resistance is connected with this pin between GND.                                                                                                                                                                                                                                                                                                                                  |

| 5       | N.C.     | No connection *2                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6       | SW       | Pin to connect with switching node. A source of external Upper NchMOSFET is connected with a drain of external lower NchMOSFET.                                                                                                                                                                                                                                                                                        |

| 7       | CBOOT    | Bootstrap capacitor connection pin. This pin becomes a GATE drive power supply of an external NchMOSFET.                                                                                                                                                                                                                                                                                                               |

|         |          | Connect a bypath capacitor between CBOOT and SW.                                                                                                                                                                                                                                                                                                                                                                       |

| 8       | HDRV     | An external upper MOSFET gate drive pin.                                                                                                                                                                                                                                                                                                                                                                               |

| 9       | LDRV     | An external lower MOSFET gate drive pin.                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | $V_{DD}$ | Power supply pin for an external the lower MOS-FET gate drive.                                                                                                                                                                                                                                                                                                                                                         |

| 11      | GND      | Ground pin. Each reference voltage is based on the voltage of the ground pin.                                                                                                                                                                                                                                                                                                                                          |

| 12      | SUBGND   | It is connected with the GND pin of 11pin inside. *3                                                                                                                                                                                                                                                                                                                                                                   |

| 13      | N.C.     | No connection *2                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14      | VIN      | Power supply pin. This pin is monitored by UVLO function. When the voltage of this pin becomes 8V or more, the IC starts by UVLO function and the soft start function operates.                                                                                                                                                                                                                                        |

| 15      | ILIM     | Reference current pin for current detection. The sink current of about 18.5µA flows to this pin.  When a resistance is connected between this pin and V <sub>IN</sub> outside and the voltage applied to the SW pin is lower than the voltage of the terminal side of the resistance, the upper NchMOSFET is off by operating the current limiter comparator.  This operation is reset with respect to each PWM pulse. |

| 16      | SS       | Pin to connect a capacitor for soft start. A capacitor for soft start is charged by using the current of about 5μA.  When this pin voltage becomes about 1.1V, the soft start period is expired. And the frequency fold back function becomes active.                                                                                                                                                                  |

$<sup>^{\</sup>star}2$  The problem does not occur even if connected to the GND.

<sup>\*3</sup> Short-circuit 11pin and 12pin.

Continued on next page

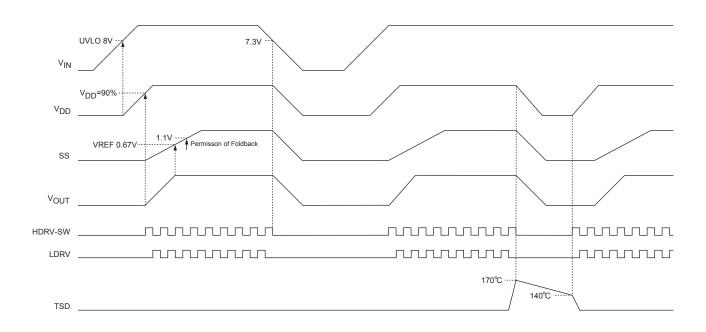

## Boot sequence, UVLO, and TSD operation

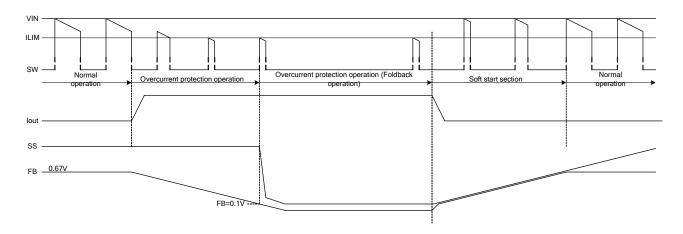

## Sequence of overcurrent protection

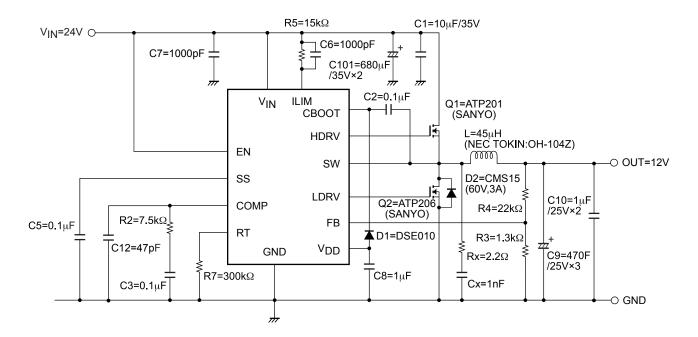

## **Sample Application Circuit**

$V_{IN}$ =24V,  $V_{OUT}$ =12V,  $I_{OUT}$ =7A, Fosc=100kHz

#### · Part selection and set

#### 1) Output voltage set

Output voltage (VOUT) is shown the equation (1).

$$V_{OUT} = (1 + \frac{R4}{R3}) \times VREF = (1 + \frac{22k\Omega}{1.3k\Omega}) \times 0.67 \text{ (typ)}$$

[V] (1)

Ex) To set output voltage of 12V, set resistors as follows: R3=1.3k $\Omega$  and R4=22k $\Omega$ .

#### 2) Soft start set

Soft start capacitor (C5) is obtained by the equation (2).

$$C5 = \frac{I_{SS} \times T_{SS}}{V_{RFF}} = \frac{5\mu \times T_{SS}}{0.67V} \quad [\mu F]$$

(2)

ISS: Charge current value, TSS: soft start time

Ex) To set soft start time of 15ms (approx.), set C5=0.1μF.

#### 3) Overcurrent protector set

Overcurrent limit setting resistor (R5) is obtained by the equation (3).

$$R5 = \frac{Rdson \times I_L max}{I_I lim} = \frac{Rdson \times I_L max}{18.5\mu} \quad [\Omega]$$

(3)

IJlim: ILIM current value,

ILmax: the maximum value of coil current,

Rdson: Ron between drain and source of Q1 (upper Nch MOS FET).

Ron of ATP201  $\approx 23 \text{m}\Omega$  (when VGS=4.5V at 25°C)

Ex) To set current limit operation point to 11.3A (load current) where coil peak current value is 12A (approx.), set  $R5 = 15k\Omega$ . Set an optimum resistor taking variation of ON resistance into consideration due to temperature change and make sure to confirm it with the user's specific board. For C6, connect a capacitor of 1000pF to filter unwanted noise for the proper operation of current limiting.

#### ON resistance of FET

- \* Rdson of FET has its own temperature coefficient and the resistor becomes higher in proportion to the temperature.

- \* To set Rdson value within the range of operating temperature, it is advisable that the user confirm the data sheet by the FET supplier.

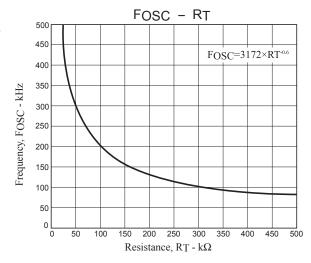

#### 4) How to set oscillation frequency

Oscillation frequency Fosc is adjustable by RT resistor as shown in the correlation chart as follows:

SW frequency setting range: 80kHz to 500kHz

#### 5) Boot strap capacitor set

For boot strap capacitor C2, use capacitor 100 times larger than Ciss of power MOSFET.

#### 6) Phase compensation set

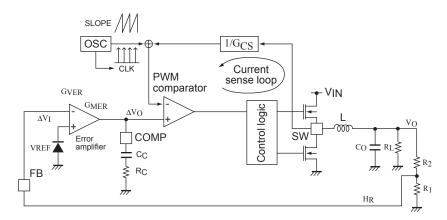

Since LV5768V adopts current mode control, low ESR capacitor and solid polymer capacitor such as OS capacitor can be used as output capacitor with simple phase compensation.

#### \*Frequency characteristics

Frequency characteristics of LV5768V consist of the following transfer functions.

(1) Output resistor divider ; HR

(2) Voltage gain of error amplifier ; GVEA

Current gain (Transconductance) ; GMEA

(3) Impedance of external phase compensation part ; ZC

(4) Current sense loop gain ; GCS

(5) Output smoothing impedance ; ZO

Fig. Current control loop of LV5768V

Closed loop gain is obtained by the equation (4)

$$G = H_R \times G_{MEA} \times Z_C \times G_{CS} \times Z_O$$

$$R5 = \frac{VREF}{VO} \times GMEA \times (RC + \frac{1}{SCC}) \times GCS \times \frac{RL}{1 + SCORL}$$

(4)

From the equation (4), the frequency characteristics of closed loop gain is given by pole fp1 which consists of output capacitor Co and output load resistor RL, zero point fz which is given by external resistor Rc and capacitor Cc of phase compensation pin COMP and pole fp2 which is given by output impedance of error amplifier  $Z_{EA}$  and external phase compensation capacitor Cc. fp1, fz, fp2 are given by the equation (5), (6) and (7).

fp1 =

$$\frac{1}{2\pi C_0 R_L}$$

(5), fz =  $\frac{1}{2\pi C_0 R_C}$  (6), fp2 =  $\frac{1}{2\pi \times Z_{EA} \times C_C}$  (7)

\*Calculation of the phase compensation by external part R<sub>C</sub> and C<sub>C</sub>

In general, the frequency where closed loop gain becomes 1 (zero cross frequency fzc) should be 1/10 of the switching frequency (or 1/5 at the highest) to stabilize the operation of switching regulator.

Ex) When switching frequency of LV5768V is 100kHz:

$$fzc = \frac{100kHz}{10} \approx 10kHz \tag{8}$$

Since the closed loop gain becomes 1 with this frequency, the equation (7) = 1

$$\frac{V_{REF}}{V_{O}} \times G_{MEA} \times (R_{C} + \frac{1}{SC_{C}}) \times G_{CS} \times \frac{R_{L}}{1 + SC_{O}R_{L}} = 1$$

(9)

In reality for zero cross frequency, since capacity element  $\frac{1}{SCC}$  of phase compensation becomes lower enough than

the resistance element R<sub>C</sub>:

$$R_C \gg \frac{1}{SCC}$$

(10)

$$\frac{V_{REF}}{V_{O}} \times G_{MEA} \times R_{C} \times G_{CS} \times \frac{R_{L}}{1 + 2\pi \times f_{7C} \times C_{O} \times R_{L}} = 1$$

(11)

From the equation, phase compensation external resistor R<sub>C</sub> is obtained by the following formula. However,  $G_{CS}=0.67/Rdson=29A/V$ ,  $G_{MEA}=1400\mu A/V$ .

Given that output is 12V and load resistor is  $1.7\Omega$  (7A load):

$$\therefore R_{C} = \frac{V_{O}}{V_{REF}} \times \frac{1}{G_{MEA}} \times \frac{1}{G_{CS}} \times \frac{1+2\pi \times f_{ZC} \times C_{O} \times R_{L}}{R_{L}}$$

$$= \frac{12}{0.67} \times \frac{1}{1400\mu A/V} \times \frac{1}{29A/V} \times \frac{1+2\pi \times 10k \times 1410\mu \times 1.7}{1.7}$$

$$\approx 39k\Omega$$

(12)

This is the external resistor value R<sub>C</sub> obtained from this calculation (the calculation reveals that the last block where load resistor R<sub>L</sub> is inserted is  $1 \ll 2\pi \times f_{ZC} \times C_O \times R_L$ . Therefore, there is no dependence on R<sub>L</sub>.).

When point zero  $f_Z(6)$  and pole fp1(5) are the same values, they cancel out each other. Hence, there is only one pole frequency for the phase characteristics of closed loop gain. In other words, you can obtain characteristics in which waveform is stable because the gain frequency lowers at -20dB/DEC and phase only rotates by -90 degree.

Since (6) = (5)

$$f_Z = fp1$$

(14)

$$\frac{1}{2\pi C_C R_C} = \frac{1}{2\pi C_O R_L}$$

$$\therefore C_C = \frac{R_L \times C_O}{R_C} = \frac{1.7 \times 1410 \mu}{39 k} = 0.062 \mu F$$

The external resistor value  $R_C$  and capacitor value  $C_C$  between phase compensator pin COMP and GND is obtained as such using ideal equations. In reality, stable phase margin should be defined based on testing under the entire temperature, load and input voltage range. On the other hand, such ideal value is used as starting point for the assessment. In the deliverable evaluation board, the above values are used as defaults.  $C_C$  and  $R_C$  are defined according to conditions of transient response too. If the influence of noise is significant, it is advisable to increase the capacitance of  $C_C$ .

#### 7) Input capacitor selection

When switching of the IC occurs, ripple current flows into the input capacitor of DC-DC converter. Like input current, the more the output current flows, the more the ripple current into input capacitor flows. Also, the lower the input voltage is, the more the duty expands. As a result, the ripple current flows more. Allow higher ripple current than the result of the equation. The input capacitor should be connected adjacent to the power IC and minimize the inductance from the pattern layout. Root mean squared value is obtained by the equation (15).

$$Irip\_in = \sqrt{D(1-D)} \times IOUT \quad [Arms]$$

(15)

D represents duty cycle defined by VOUT/VIN.

#### 8) Output capacitor selection

If ceramic capacitor is used to output, output ripple voltage is obtained as follows since ESR of capacitance is small.

$$Vrip = \frac{VOUT}{8 \times L \times C_O \times f_{OSC}^2} \times (1 - \frac{VOUT}{V_{IN}}) \quad [V]$$

(16)

Also if electrolytic capacitor is used to output, output ripple voltage is affected by ESR since ESR of capacitance is large. In this case, output ripple voltage is obtained by the following equation.

$$Vrip = \frac{VIN - VOUT}{fOSC \times VIN} \times \frac{VOUT \times RESR}{L} \quad [V]$$

(17)

Since the allowable ripple current of electrolytic capacitor is lower compared to that of ceramic capacitor, the allowable ripple current value must not be exceeded. Root mean squared value is obtained by the following equation.

Irip\_out =

$$\frac{1}{2\sqrt{3}} \times \frac{\text{VOUT (VIN - VOUT)}}{\text{L} \times \text{fOSC} \times \text{VIN}}$$

[Arms] (18)

It is advisable to use ceramic capacitor in combination with electrolytic capacitor to reject high frequency noise. The electrolytic capacitor can be low ESR aluminum electrolytic capacitor or polymer aluminum electrolytic capacitor.

#### 9) Inductor selection

L1: Caution is required due to the heat generation of choke coil caused by overload and load short. The inductance value is determined by output ripple voltage (Vrip) and the impedance of output capacitor for switching frequency. The minimum inductance is obtained by the equation (19).

$$L \min = \frac{V_{IN} - V_{OUT}}{f_{OSC} \times V_{IN}} \times \frac{V_{OUT} \times RESR}{V_{rip}} \quad [\mu H]$$

(19)

In the above equation, ESR is used in place of the impedance of output capacitor. The reason is, the impedance of output capacitor for switching frequency is close to R<sub>ESR</sub> in many cases. However with ceramic capacitor, real impedance is used instead of R<sub>ESR</sub>.

Ex) $V_{IN}$ (max)=24V,  $V_{OUT}$ =12V,  $V_{rip}$ =20mV,  $R_{ESR}$ =9 $m\Omega$ ,  $f_{OSC}$ =100kHz

L min =

$$\frac{24V - 12V}{100k \times 24V} \times \frac{12V \times 9m}{20mV}$$

(20)

In the actual part selection, ripple voltage is defined first, then capacitor and inductor are selected. Take the maximum value and minimum value of input voltage, output voltage and load variation into consideration. Also, the ripple current of inductor is used as basis for output inductor selection in many cases. Ripple current is obtained by the equation (21).

$$Irip = \frac{V_{IN} - V_{OUT}}{f_{OSC} \times L} \times D \quad [A]$$

(21)

D represents duty cycle defined by VOUT/VIN.

The important term is the ripple current represented as Irip/I<sub>OUT</sub>. As long as the ripple element is less than 50%, it should not be a problem. If the ripple element is higher, inductor loss becomes significant.

Irip =

$$\frac{24V - 12V}{100k \times 45\mu} \times 0.5$$

(22)

= 1.3 [A]

#### 10) Power consumption of high side MOSFET

The power consumption in the external high side MOSFET is represented by conduction loss and switching loss. The conduction loss of MOSFET is obtained by the following equation (23).

$$Psat = I_O^2 \times R_{DS(ON)} \times D \quad [W]$$

(23)

Since R<sub>DS(ON)</sub> is affected by temperature, it is advisable to confirm the actual FET temperature and data sheet.

The switching loss of high side MOSFET is obtained by the following equation (24).

$$Psw = V_{IN} \times I_O \times t_{SW} \times f_{SW} \quad [W]$$

(24)

In: DC output current

tsw: Rise time of switching waveform

fSW: Switching frequency

The junction temperature of high side MOSFET is obtained by the following equation (25).

$$Tj = Ta + (Psat + Psw) \times \theta ja \quad [W]$$

(25)

$\theta$ ja: heat resistor between junction and ambient.

Tj should not exceed the Tjmax as stated in the data sheet.

#### 11) Power consumption of low side MOSFET

The power consumption in low side MOSFET consists of conduction loss from  $R_{DS}$  (ON) as well as from body diode and reverse recovery loss. The conduction loss due to  $R_{DS}$  (ON) is obtainable by the equation (23) which is represented in the equation (26).

$$Psat = IO^{2} \times RDS(ON) \times (1-D) [W]$$

(26)

The conduction loss from body diode occurs when the body diode is conducted forwardly between high side off and low side off zone, which is represented in the equation (27).

$$Pdf = 2 \times I_O \times Vf \times tdelay \times f_{SW} [W]$$

(27)

Vf: Forward voltage of body diode

tdelay: Delay time immediately before surge of SW node

The total power consumption of low side MOSFET is obtained by the equation (28).

$$Pls = Psat + Pdf [W]$$

(28)

#### 12) Power consumption of LV5768V

The total power consumption of LV5768V is represented in the equation (29) given that the same MOSFET is selected for high side and low side.

$$Pd_ic = (2 \times Qg \times f_{SW} + I_{CCA}) \times V_{IN} \quad [W]$$

(29)

ICCA: IC consumption current when switching is stopped.

#### Caution for pattern layout

#### C1: input capacitor

When the IC performs switching, a ripple current flows into the input capacitor of DC-DC converter. The capacitor of input should be connected adjacent to the power IC and minimize the inductance from pattern layout. C1 should be connected adjacently to V<sub>IN</sub> pin of the IC and Q1 (high side FET- drain). If implementation to IC side is not feasible, insert adjacently to Q1.

C7 (bypass capacitor connected to V<sub>IN</sub> pin of the IC) should be connected adjacently to V<sub>IN</sub> pin and GND pin. In rare cases, intensive ringing may occur in the V<sub>IN</sub> pin by connecting bypass capacitor. The recommendation value is 1000pF.

#### Q1, Q2 (D1): external FET

Both high and low sides are driven by Nch-MOSFET. In Q1, a transition of SW node takes place between  $V_{IN}$  and GND by turn on and off, where high frequency noise occurs. The noise affects the surrounding pattern layouts and parts. The high/ low side gate and SW node should be laid out as fat and short as possible and connect to HDRV, LDRV and SW pins of the IC. HDRV, LDRV and SW pins should be shielded with GND to prevent influence from noise

When high side FET is turned on, ripple current path is as follows:  $V_{IN} + (C1) --> Q1--> inductor (L) --> C9--> GND$ . When low side FET is turned on, current path is as follows: Q2(D1) --> inductor (L) --> C9--> GND. By minimizing the area of current path and keeping the pattern layout fat and short, noise is eliminated and error operation is prevented. Hence, Q1, Q2, D1, C1 and C9 should be implemented nearby.

#### R5,C6: ILIM (overcurrent limiter set pin)

ILIM pin detects overcurrent which is used as set point where current limit comparator in the IC starts operation. The overcurrent limiter is adjustable by the resistor between ILIM pin and VIN pin. When the voltage of SW pin becomes lower than that of ILIM pin, current limit comparator functions and turns off the high side MOSFET. This operation is reset at every PWM pulse.

To filter unwanted noise, C6 should be connected in parallel to the set resistor (the recommendation is 1000pF). R5 and C6 should be implemented adjacently to the  $V_{IN}$  side of the IC. If they are apart from the  $V_{IN}$  side, detection precision for overcurrent point may be deteriorated.

#### Small signal blocks: part for FB, COMP, EN, CBOOT, VDD and SS pins.

The parts should be implemented adjacently to the IC and be connected as short as possible. Also the GND of the parts should have common GND pattern as the IC. FB pattern layout should not be under nor nearby the inductor or SW node. This must be complied to avoid error operation.

#### ORDERING INFORMATION

| Device          | Package                      | Shipping (Qty / Packing) |

|-----------------|------------------------------|--------------------------|

| LV5768V-A-TLM-E | SSOP16 (225mil)<br>(Pb-Free) | 2000 / Tape & Reel       |

| LV5768V-A-MPB-E | SSOP16 (225mil)<br>(Pb-Free) | 90 / Fan-Fold            |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re