Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Sine wave PWM Drive, Pre drive IC, for Brushless Motor Drive

# Overview

The LV8139JA is a PWM system pre driver IC designed for three-phase brushless motors.

This IC reduces motor driving noise by using a high-efficiency, sine wave PWM drive type.

It incorporates a full complement of protection circuits and, by combining it with a hybrid IC in the STK611 or STK5C4 series, the number of components used can be reduced and a high level of reliability can be achieved. Furthermore, its power-saving mode enables the power consumption in the standby mode to be reduced to zero. This IC is optimally suited for driving various large-size motors such as those used in air conditioners and hot-water heaters.

#### **Features**

- Three-phase bipolar drive

- Sine wave PWM drive

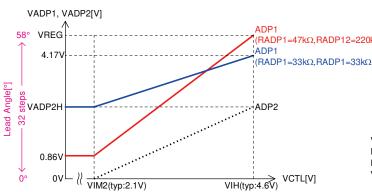

- Drive phase setting function (Set 0-58 degrees 32 steps: There is an adjustment function corresponding to the CTL pin input)

- Supports power saving mode(power saving mode at CTL pin voltage of 0.95V (typ) or less; ICC = 0mA, HB pin turned off)

- Supports bootstrap

- Automatic recovery type constraint protection circuit

- Forward/reverse switching circuit, Hall bias pin

- Current limiter circuit, low-voltage protection circuit, and thermal shutdown protection circuit

- FG1 and FG3 output (360-degree electrical angle/1 pulse and 3 pulses)

# **Typical Applications**

- Air Purifier

- Clothes Dryer

- Air conditioners

- Consumer

ON Semiconductor® www.onsemi.com

SSOP30 (275mil)

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code Y = Year M = Month DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

## ORDERING INFORMATION

Ordering Code: LV8139JA-AH

Package SSOP30 (275mil) (Pb-Free / Halogen Free)

Shipping (Qty / packing) 1000 / Tape & Reel

† For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. http://www.onsemi.com/pub link/Collateral/BRD8011-D.PDF

# **Specifications**

# Absolute Maximum Ratings at Ta = 25°C (Note 1)

| Parameter                   | Symbol                                         | Conditions                                     | Ratings     | Unit |

|-----------------------------|------------------------------------------------|------------------------------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max                            | V <sub>CC</sub> pin                            | 18          | ٧    |

| Output current              | I <sub>O</sub> max                             |                                                | 15          | mA   |

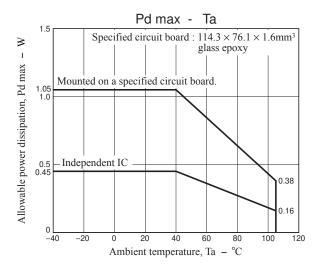

| Allowable power dissipation | Pd max1                                        | Independent IC                                 | 0.45        | W    |

|                             | Pd max2                                        | Mounted on a specified circuit board. (Note 2) | 1.05        | W    |

| CTL pin applied voltage     | V <sub>CTL</sub> max                           |                                                | 18          | ٧    |

| FG1,FG3 pin applied voltage | V <sub>FG</sub> 1 max<br>V <sub>FG</sub> 3 max |                                                | 18          | V    |

| Junction temperature        | Tj max                                         |                                                | 150         | °C   |

| Operating temperature       | Topr                                           |                                                | -40 to +105 | °C   |

| Storage temperature         | Tstg                                           |                                                | -55 to +150 | °C   |

Stresses exceeding those listed in the Absolute Maximum Rating table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Specified circuit board: 114.3mm × 76.1mm × 1.6mm, glass epoxy

# **Recommendation Operating Range** at $Ta = 25^{\circ}C$ (Note 3)

| Parameter                  | Symbol                               | Conditions | Ratings     | Unit |

|----------------------------|--------------------------------------|------------|-------------|------|

| Supply voltage range       | V <sub>CC</sub>                      |            | 9.5 to 16.5 | V    |

| VREG5 pin output current   | IREG                                 |            | -10         | mA   |

| HB pin output current      | I <sub>HB</sub>                      |            | -30         | mA   |

| FG1,FG3 pin output current | I <sub>FG</sub> 1, I <sub>FG</sub> 3 |            | 10          | mA   |

<sup>3.</sup> Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# Electrical Characteristics at $Ta = 25^{\circ}C$ , $V_{CC} = 15V$ (Note 4)

| Parameter                                | O. make al            | Conditions                                            |           | Ratings   |          |       |  |

|------------------------------------------|-----------------------|-------------------------------------------------------|-----------|-----------|----------|-------|--|

| Parameter                                | Symbol                | Conditions                                            | min       | typ       | max      | Unit  |  |

| Supply current 1                         | I <sub>CC</sub> 1     |                                                       |           | 4         | 6        | mA    |  |

| Supply current 2                         | I <sub>CC</sub> 2     | At stop (CTL < VIL1)                                  |           | 0         | 10       | μА    |  |

| Output Block (Pin HIN1, HIN2, HIN3,      | IN1, LIN2 and LI      | N3)                                                   |           |           |          |       |  |

| High level output voltage                | V <sub>HO</sub>       | I <sub>O</sub> = -10mA                                | VREG-0.40 | VREG-0.25 |          | ٧     |  |

| Upper output ON resistance               | R <sub>ON</sub> H     | I <sub>O</sub> = -10mA                                |           | 25        | 40       | Ω     |  |

| Low level output voltage                 | V <sub>LO</sub>       | I <sub>O</sub> = 10mA                                 |           | 0.15      | 0.25     | ٧     |  |

| Lower output ON resistance               | R <sub>ON</sub> L     | I <sub>O</sub> = 10mA                                 |           | 15        | 25       | Ω     |  |

| Output leakage current                   | l <sub>O</sub> leak   |                                                       |           |           | 10       | μΑ    |  |

| Bootstrap charge pulse width             | Tboot                 |                                                       | 1.6       | 2.5       | 3.4      | μS    |  |

| Output minimum dead time                 | Tdt                   |                                                       | 1.6       | 2.5       | 3.4      | μS    |  |

| 5V Constant Voltage Output (VREG5        | pin)                  | •                                                     |           |           |          |       |  |

| Output voltage                           | VREG                  | I <sub>O</sub> = -5mA                                 | 4.7       | 4.9       | 5.1      | V     |  |

| Voltage fluctuation                      | ΔV (REG1)             | V <sub>CC</sub> = 9.5 to 16.5V, I <sub>O</sub> = -5mA |           |           | 100      | mV    |  |

| Load fluctuation                         | ΔV (REG2)             | I <sub>O</sub> = -5 to -10mA                          |           |           | 100      | mV    |  |

| Hall Amplifier (Pin IN1+, IN1-, IN2+, IN | N2-, IN3+ and IN3     | -)                                                    |           |           |          |       |  |

| Input bias current                       | IB (HA)               |                                                       | -1        |           | 0        | μА    |  |

| Common-mode input voltage range 1        | VICM1                 | When a Hall element is used                           | 0.3       |           | VREG-1.8 | ٧     |  |

| Common-mode input voltage range 2        | VICM2                 | Single-sided input bias mode (when a Hall IC is used) | 0         |           | VREG     | V     |  |

| Hall input sensitivity                   | VHIN                  | Sine wave,<br>Hall element offset = 0V                | 80        |           |          | mVp-p |  |

| Hysteresis width                         | ΔV <sub>IN</sub> (HA) |                                                       | 15        | 30        | 45       | mV    |  |

| Input voltage Low → High                 | VSLH                  |                                                       | 5         | 15        | 25       | mV    |  |

| Input voltage High → Low                 | VSHL                  |                                                       | -25       | -15       | -5       | mV    |  |

Continued from preceding page.

| Parameter                                                        | Symbol                   | Conditions                                             | Ratings |      |                 | Uni   |

|------------------------------------------------------------------|--------------------------|--------------------------------------------------------|---------|------|-----------------|-------|

| T didiffictor                                                    | Cymbol                   | Conditions                                             | min     | typ  | max             | Orine |

| CSD Oscillator Circuit (CSD pin)                                 | 1                        | 1                                                      |         |      |                 |       |

| High level output voltage                                        | V <sub>OH</sub> (CSD)    |                                                        | 2.75    | 2.95 | 3.15            | V     |

| Low level output voltage                                         | V <sub>OL</sub> (CSD)    |                                                        | 0.85    | 1.05 | 1.25            | V     |

| Amplitude                                                        | V (CSD)                  |                                                        | 1.7     | 1.9  | 2.1             | Vp-p  |

| External capacitor charging current                              | ICHG1 (CSD)              | VCHG1 = 2.0V                                           | -14     | -10  | -6              | μΑ    |

| External capacitor discharging current                           | ICHG2 (CSD)              | VCHG2 = 2.0V                                           | 6       | 10   | 14              | μА    |

| Lock detection ON/OFF time ratio                                 | LRTO                     | Drive OFF/drive ON                                     |         | 11   |                 |       |

| PWM Oscillator (PWM pin)                                         | 1                        | 1                                                      | 1       |      |                 |       |

| High level output voltage                                        | V <sub>OH</sub> (PWM)    |                                                        | 3.3     | 3.5  | 3.7             | V     |

| Low level output voltage                                         | V <sub>OL</sub> (PWM)    |                                                        | 1.3     | 1.5  | 1.7             | V     |

| Amplitude                                                        | V (PWM)                  |                                                        | 1.8     | 2.0  | 2.2             | Vp-p  |

| Oscillation frequency                                            | f (PWM)                  | $C = 2200 pF, R = 15 k\Omega$<br>(design target value) |         | 17.3 |                 | kHz   |

| Current Limiter Operation (RF pin)                               | II.                      | (                                                      |         | l l  |                 |       |

| Limiter voltage                                                  | VRF                      |                                                        | 0.225   | 0.25 | 0.275           | V     |

| Thermal Shutdown Protection Oper                                 |                          | 1                                                      | 1       | -    | -               |       |

| Thermal shutdown protection                                      | TSD                      | Design target value (Note 5)                           | 150     | 175  |                 | °C    |

| operating temperature                                            | 1.02                     | (junction temperature)                                 |         |      |                 | Ū     |

| Hysteresis width                                                 | ΔTSD                     | Design target value (Note 5) (junction temperature)    |         | 35   |                 | °C    |

| TH pin                                                           | -1                       | , ,                                                    | 1       |      |                 |       |

| Protection start voltage                                         | VTH                      |                                                        | 0.50    | 0.65 | 0.80            | V     |

| Hysteresis width                                                 | ΔVTH                     |                                                        | 0.32    | 0.42 | 0.52            | V     |

| HB pin                                                           |                          |                                                        |         | i_   |                 |       |

| Output ON resistance                                             | R <sub>ON</sub> (HB)     | IHB = -10mA                                            |         | 10   | 20              | Ω     |

| Output leakage current                                           | I <sub>I</sub> (HB)      | Power saving mode V <sub>CC</sub> = 15V                |         |      | 10              | μА    |

| Low Voltage Protection Circuit (det                              |                          | I.                                                     |         |      | 10              | part  |

| Operation voltage                                                | VSD                      |                                                        | 7.4     | 7.9  | 8.4             | V     |

| <u> </u>                                                         |                          |                                                        | +       |      |                 | V     |

| Hysteresis width                                                 | ΔVSD                     |                                                        | 0.35    | 0.5  | 0.65            | V     |

| FG1 FG3 Pin                                                      | T p (50)                 | T                                                      | 1       | 40   | 22              | -     |

| Output ON resistance                                             | R <sub>ON</sub> (FG)     | IFG = 5mA                                              |         | 40   | 60              | Ω     |

| Output leakage current                                           | I <sub>L</sub> (FG)      | VFG = 18V                                              |         |      | 10              | μA    |

| CTL Amplifier (drive mode)                                       | T                        | 1                                                      | 1       |      |                 |       |

| Input voltage range                                              | V <sub>IN</sub> (CTL)    |                                                        | 0       |      | V <sub>CC</sub> | V     |

| High level input voltage                                         | V <sub>IH</sub> (CTL)    | HIN pin PWM ON duty 100%                               | 4.4     | 4.6  | 4.8             | V     |

| Middle level input voltage 1 (At drive start)                    | V <sub>IM</sub> 1 (CTLI) | HIN pin PWM ON duty 0%                                 | 2.15    | 2.35 | 2.55            | V     |

| Middle level input voltage 2 (During drive)                      | V <sub>IM</sub> 2 (CTLI) | HIN pin PWM ON duty 0%                                 | 1.9     | 2.1  | 2.3             | ٧     |

| Input current (During drive in 120-degree current-carrying mode) | I <sub>IH</sub> 1 (CTLI) | VCTL = 3.5V                                            | 13      | 25   | 37              | μА    |

| Input current (During drive in sine wave                         | I <sub>IH</sub> 2 (CTLI) | VCTL = 3.5V                                            | 10      | 20   | 30              | μА    |

| current-carrying mode)  CTL Amplifier (power saving mode)        |                          | 1                                                      |         |      |                 |       |

|                                                                  | V 1 (OT!)                | Power equips made                                      | 0.75    | 0.05 | 4 4 5           | 17    |

| Low level input voltage                                          | V <sub>IL</sub> 1 (CTL)  | Power saving mode                                      | 0.75    | 0.95 | 1.15            | V     |

| Hysteresis width                                                 | ΔCTL                     |                                                        | 0.15    | 0.35 | 0.55            | V     |

Continued from preceding page.

| Parameter                               | Symbol                | Conditions               | Ratings |      |      | Unit |

|-----------------------------------------|-----------------------|--------------------------|---------|------|------|------|

| Parameter                               | Symbol                | Conditions               | min     | typ  | max  | Unit |

| F/R Pin                                 |                       |                          |         |      |      |      |

| High level input voltage range          | V <sub>IH</sub> (FR)  |                          | 3.0     |      | VREG | V    |

| Low level input voltage range           | V <sub>IL</sub> (FR)  |                          | 0       |      | 0.7  | V    |

| Input open voltage                      | V <sub>IO</sub> (FR)  |                          |         | 0    | 0.3  | V    |

| Hysteresis width                        | V <sub>IS</sub> (FR)  |                          | 0.15    | 0.3  | 0.45 | V    |

| High level input current                | I <sub>IH</sub> (FR)  | VF/R = VREG              | 25      | 45   | 65   | μΑ   |

| Low level input current                 | I <sub>IL</sub> (FR)  | VF/R = 0V                | -2      | 0    | +2   | μΑ   |

| FAULT Pin                               |                       |                          |         |      |      | •    |

| Drive stop voltage                      | VFOF                  |                          | 0       |      | 0.5  | V    |

| Drive start voltage                     | VFON                  |                          | 3.0     |      | VREG | V    |

| Input open voltage                      | V <sub>IO</sub> (FLT) |                          | 4.6     | VREG |      | V    |

| High level input current                | I <sub>IH</sub> (FLT) | VFAULT=VREG              |         | 0    | 10   | μΑ   |

| Low level input current                 | I <sub>IL</sub> (FLT) | VFAULT=0V                | -200    | -160 | -120 | μΑ   |

| ADP1 Pin (drive phase adjustment)       |                       |                          |         |      |      | •    |

| Minimum lead angle                      | Vadp01                | VADP1 = 0V               |         | 0    | 2    | Deg  |

| Maximum lead angle                      | Vadp16                | VADP1 = VREG             | 56      | 58   |      | Deg  |

| Current ratio with the ADP2 pin current | ADP                   | VCTL = 5.5V, IADP1/IADP2 | 1.8     | 2    | 2.2  | A/A  |

| ADP2 Pin (drive phase adjustment)       | •                     |                          |         |      |      |      |

| High level output voltage               | VADP2H                | VCTL = 5.5V              | 2.25    | 2.45 | 2.65 | V    |

| Low level output voltage                | VADP2L                | VCTL = 1.5V              | 0       |      | 0.3  | V    |

| DPL Pin (drive-phase-adjustment lim     | nit setting pin)      | •                        |         |      |      |      |

| Lead angle limit high level voltage     | VDPLH                 |                          | 3.3     | 3.5  | 3.7  | V    |

| Lead angle limit low level voltage      | VDPLL                 |                          | 1.3     | 1.5  | 1.7  | V    |

|                                         |                       |                          |         |      |      |      |

<sup>4.</sup> Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. These are design target values and no measurements are made.

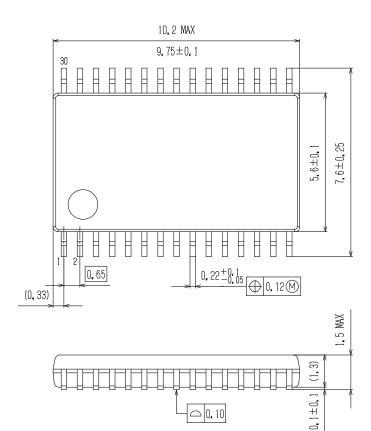

# **Package Dimensions**

unit: mm (typ)

# SSOP30 (275mil)

CASE 565AT

**ISSUE A**

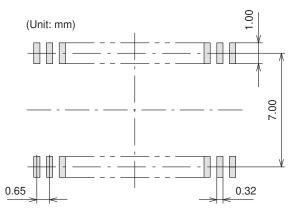

# **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# Pdmax-Ta diagram

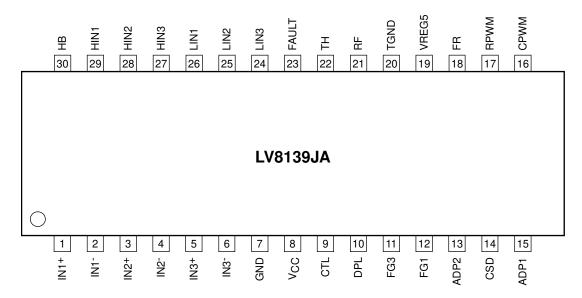

# **Pin Assignment**

Top view

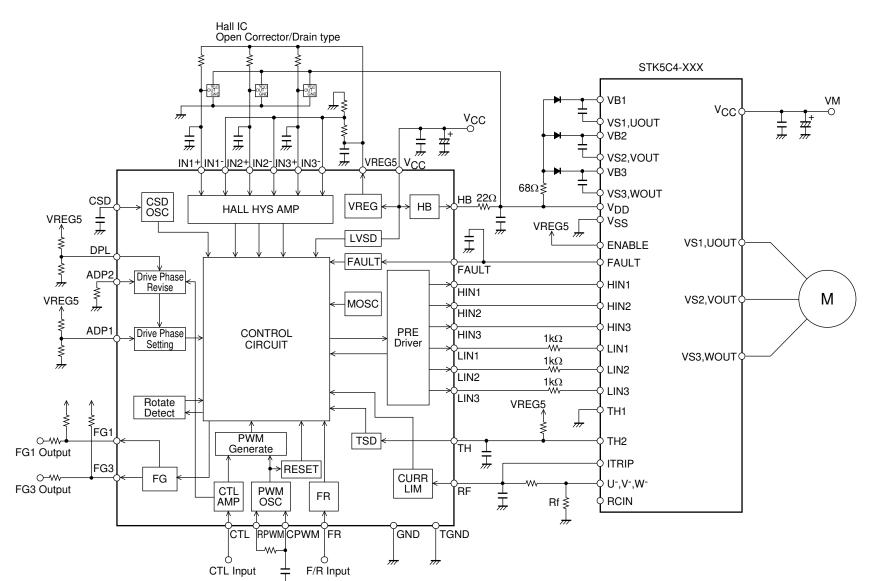

# Sample Application Circuit 1 (Hall IC, HIC)

The Hall IC to be used must be of open-collector or open-drain output type, and it must be pulled up by VREG5.

The type of Hall IC incorporating a pull-up resistor cannot be used.

Furthermore, when using an element that cannot turn off the control power while VM is being applied, the control power must be supplied from the VCC pin rather than from the HB pin.

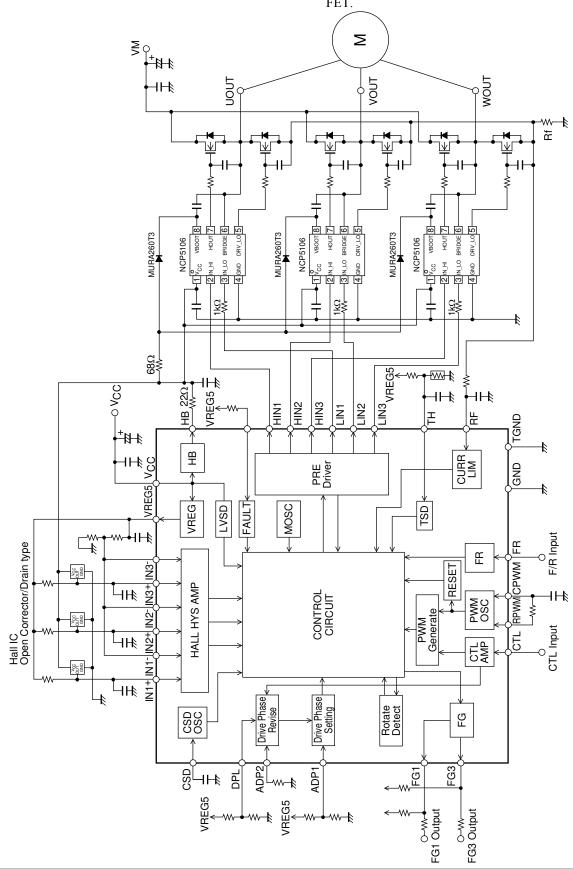

# Sample Application Circuit 2 (Hall IC, FET)

The Hall IC to be used must be of open-collector or open-drain output type, and it must be pulled up by VREG5.

The type of Hall IC incorporating a pull-up resistor cannot be used.

Furthermore, when using a gate driver that cannot turn off the control power while VM is being applied, the control power must be supplied from the V<sub>CC</sub> pin rather than from the HB pin. An element with a short reverse recovery time must be selected as the output FET.

# **Pin Functions**

| Pin Func<br>Pin No. | Pin Name         | Pin function                                                   | Equivalent Circuit                                |

|---------------------|------------------|----------------------------------------------------------------|---------------------------------------------------|

| 1                   | IN1+             | Hall signal input pins.                                        |                                                   |

| 2                   | IN1-             | The high state is when IN+ is greater                          | VDEC                                              |

| 3                   | IN2+             | than IN <sup>-</sup> , and the low state is the                | VREG                                              |

| 4                   | IN2-             | reverse.                                                       |                                                   |

| 5                   | IN3+             | An amplitude of at least 100mVp-p                              |                                                   |

| 6                   | IN3 <sup>-</sup> | (differential) is desirable for the Hall                       |                                                   |

| -                   |                  | signal inputs. If noise on the Hall signals                    | *     *                                           |

|                     |                  | is a problem, insert capacitors between                        |                                                   |

|                     |                  | IN <sup>+</sup> and IN <sup>-</sup> pins.                      | $\begin{pmatrix} 1 \\ 500\Omega \\ \end{pmatrix}$ |

|                     |                  | If input is provided from a Hall IC, fix one                   | $500\Omega$                                       |

|                     |                  | side of the inputs (either the "+" or "-"                      | $(5)$ $\downarrow$ $(6)$                          |

|                     |                  | side) at a voltage within the                                  |                                                   |

|                     |                  | common-mode input range (0.3V to                               | ↑   <sub>↑</sub> }→ ↑   ↑                         |

|                     |                  | VREG-1.8V), and use the other input                            |                                                   |

|                     |                  | side as an input over the 0V to VREG                           |                                                   |

|                     |                  | range.                                                         |                                                   |

| 7                   | GND              | Ground pin of the control circuit block.                       |                                                   |

| 8                   | V <sub>CC</sub>  | Power supply pin for control.                                  |                                                   |

|                     |                  | Insert a capacitor between this pin and                        |                                                   |

|                     |                  | ground to prevent the influence of noise,                      |                                                   |

|                     |                  | etc.                                                           |                                                   |

| 9                   | CTL              | Control input pin. When CTL pin voltage                        | VREG V <sub>CC</sub>                              |

|                     |                  | rises, the IC changes the output signal                        |                                                   |

|                     |                  | PWM duty to increase the torque output.                        | <b>↓</b>                                          |

|                     |                  | In sine wave mode, Nch FET (in equivalent circuit diagram) OFF | <b>_</b>                                          |

|                     |                  | In 120-degree current-carrying mode,                           | 45kΩ (9)                                          |

|                     |                  | Nch FET ON                                                     |                                                   |

|                     |                  |                                                                |                                                   |

|                     |                  |                                                                | \$ \$ \sqrt{200 4100 \$\frac{1}{2}}               |

|                     |                  |                                                                | ] ⊣Ε                                              |

|                     |                  |                                                                | m mm m                                            |

| 10                  | DPL              | Setting pin for drive phase adjustment                         | VREG                                              |

|                     |                  | limit.                                                         |                                                   |

|                     |                  | This pin is used to limit the lead angle of                    | $(\downarrow)$                                    |

|                     |                  | the drive phase. The lead angle is                             | <b>†</b>                                          |

|                     |                  | limited to zero degrees when the voltage                       | $\downarrow$ 500 $\Omega$ $\downarrow$ 40         |

|                     |                  | is 1.5V or lower and the limit is released                     | 10                                                |

|                     |                  | when the voltage is 3.5V or higher.                            |                                                   |

|                     |                  |                                                                | \$ \$                                             |

|                     |                  |                                                                |                                                   |

|                     |                  |                                                                | <i>m m</i>                                        |

| 11                  | FG3              | FG3 : 3-Hall FG signal output pin.                             | VREG                                              |

|                     |                  | 8-pole motor outputs 12 FG pulses per                          | <u>VREG</u> (11) 12)                              |

|                     |                  | one rotation. In power saving mode,                            |                                                   |

|                     |                  | high-level is output.                                          | 25Ω ≩                                             |

|                     |                  |                                                                |                                                   |

| 12                  | FG1              | FG1 :1-Hall FG signal output pin.                              | <b>→ → →</b>                                      |

|                     |                  | 8-pole motor outputs 4 pulses per one                          |                                                   |

|                     |                  | rotation. In power saving mode,                                |                                                   |

|                     |                  | high-level is output.                                          | T                                                 |

|                     |                  |                                                                |                                                   |

|                     |                  |                                                                | m m                                               |

Continued from preceding page.

|         | m preceding page. | D                                                                                                                                                                                                                      | 5                         |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Pin No. | Pin Name<br>ADP2  | Pin function Setting pin for phase drive correction.                                                                                                                                                                   | Equivalent Circuit        |

| 13      | AUFZ              | This pin sets the amount of correction made to the lead angle according to the CTL input. Insert a resistor between this pin and ground to adjust the amount of correction.                                            | VREG VREG  VREG  VREG  13 |

| 14      | CSD               | Pin to set the operating time of the motor constraint protection circuit.  Insert a capacitor between this pin and ground.  Connect this pin to ground when the constraint protection circuit is not going to be used. | VREG  500Ω  14            |

| 15      | ADP1              | Drive phase adjustment pin. The drive phase can be advanced from 0 to 58 degrees during 180-degree current carrying drive. The lead angle becomes 0 degrees when 0V is input and 58 degrees when VREG is input.        | VCC VREG  AD 500Ω  AD 15  |

| 16      | СРWМ              | Triangle wave oscillation pin for PWM generation. Insert a capacitor between this pin and ground and a resistor between this pin and RPWM for triangle wave oscillation.                                               | VREG 200Ω 16              |

| 17      | RPWM              | Oscillation pin for PWM generation. Insert a resistor between this pin and CPWM.                                                                                                                                       | VREG (17)                 |

| Continued from | m preceding page. | _                                                                                                                                                                                                                                                                                    |                                       |

|----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Pin No.        | Pin Name          | Pin function                                                                                                                                                                                                                                                                         | Equivalent Circuit                    |

| 20             | FR<br>TGND        | FR Forward/reverse rotation setting pin. A low-level specifies forward rotation and a high-level specifies reverse rotation. This pin is held low when open.  TGND Test pin. Connect this pin to ground.                                                                             | VREG $2k\Omega$ $18(20)$ $100k\Omega$ |

| 19             | VREG5             | 5V regulator output pin (control circuit power supply). Insert a capacitor between this pin and ground for power stabilization. 0.1μF or so is desirable.                                                                                                                            | Vcc 50Ω 19                            |

| 21             | RF                | Output current detection pin. This pin is used to detect the voltage across the current detection resistor (Rf). The maximum output current is determined by the equation I <sub>OUT</sub> = 0.25V/Rf.                                                                               | VREG 5kΩ 21                           |

| 22             | TH                | Thermistor connection pin. The thermistor detects heat generated from HIC and turns off the drive output when an overheat condition occurs. All the HIN/LIN output pins are set to low at a pin voltage of 0.6V or less.  * For further details, refer to "Description of LV8139JA." | VREG 500Ω 22                          |

| Pin No.                          | Pin Name                                     | Pin function                                                                                                                                                                                                                                                                                       | Equivalent Circuit    |

|----------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 23                               | FAULT                                        | HIC protection signal input pin. This pin accepts an error mode detection signal generated by the HIC side. With a low-level input, the error mode detection condition is established, and all the HIN/LIN output pins are set to low.  * For further details, refer to "Description of LV8139JA." | VREG \$30kΩ \$500Ω 23 |

| 24<br>25<br>26<br>27<br>28<br>29 | LIN3<br>LIN2<br>LIN1<br>HIN3<br>HIN2<br>HIN1 | LIN1, LIN2, and LIN3: L side drive signal output pin. Generate 0 to VREG push-pull outputs.  HIN1, HIN2, and HIN3: H side drive signal output pin. Generate 0 to VREG push-pull outputs.                                                                                                           | VREG                  |

| 30                               | НВ                                           | Hall bias HIC power supply pin. Insert a capacitor between this pin and ground. This pin is set to high-impedance state in power saving mode. By supplying Hall bias and HIC power using this pin, the power consumption by Hall bias and HIC in power saving mode can be reduced to zero.         | VCC 30                |

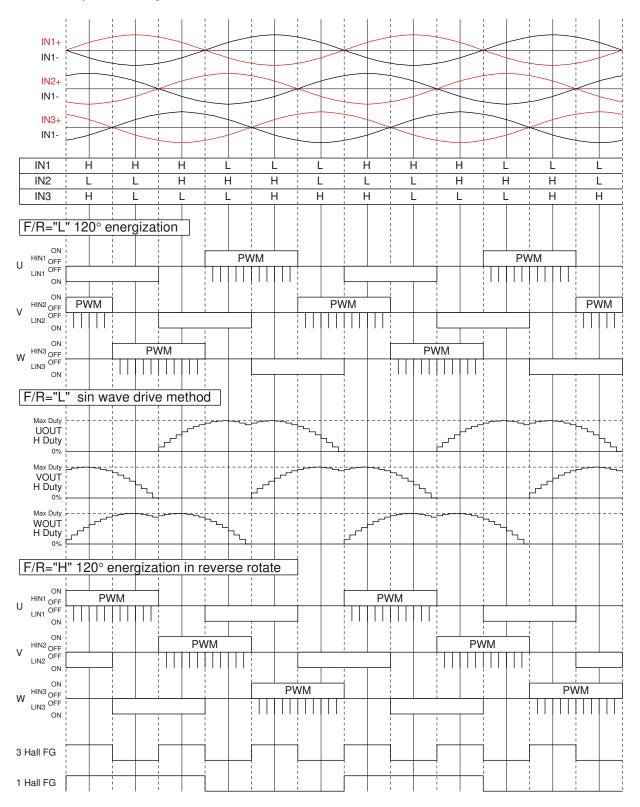

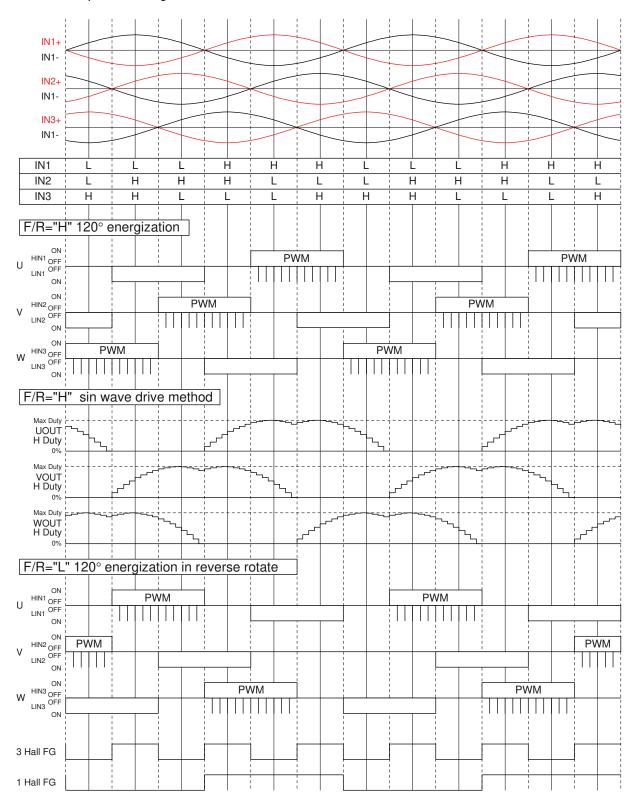

**Timing Chart** (IN = "H"indicates the state in which IN+ is greater than IN-.) (1) F/R pin = L

Normal Hall input Lead Angle=0°

The energization is switched to 120° wher 3 Hall FG frequency is 5.15Hz (typ) or lower A direction of rotation is detected from Hall signal according to F/R pin input

If the motor rotates in reverse against F/R pin input  $120^{\circ}$  energization is maintained forcibly

# (2) F/R pin = H

# Reverse Hall input Lead Angle=0°

The energization is switched to 120° wher 3 Hall FG frequency is 5.15Hz (typ) or lower A direction of rotation is detected from Hall signal according to F/R pin input

If the motor rotates in reverse against F/R pin input  $120^\circ$  energization is maintained forcibly

# **Functional Description**

• Basic operation of 120-degree ⇔ Sine wave current-carrying switching

At startup, this IC starts at 120-degree current-carrying. The current-carrying is switched to sine wave when the 3-Hall FG frequency is 5.15Hz (typ) or above and the rising edge of the IN2 signal has been detected twice in succession.

O Concerning the Hall signal input sequence

This IC controls the motor rotation direction

commands and Hall signal input sequence in order to

set the lead angle. If the motor rotation direction

commands and Hall signal input sequence do not

conform to what is shown on the timing chart, the

motor is driven by 120-degree current-carrying.

Shown below are two Hall signal input sequences.

Sequence 1: When the Hall signal has been input with the following logic

| IN1 | Η |               | Η |               | Н |               | L |               | L |               | L |

|-----|---|---------------|---|---------------|---|---------------|---|---------------|---|---------------|---|

| IN2 | L | $\rightarrow$ | L | $\rightarrow$ | Н | $\rightarrow$ | Η | $\rightarrow$ | Н | $\rightarrow$ | L |

| IN3 | Н |               | L |               | L |               | L |               | Н |               | Н |

|     |   |               |   |               |   |               |   |               |   |               |   |

When F/R pin input is high  $\rightarrow$  120-degree current-carrying When F/R pin input is low  $\rightarrow$  180-degree current-carrying

Sequence 2: When the Hall signal has been input with the following logic

| IN1 | Н               | L               | L               | L               | Н               | Н |

|-----|-----------------|-----------------|-----------------|-----------------|-----------------|---|

| IN2 | $L \rightarrow$ | $L \rightarrow$ | $H \rightarrow$ | $H \rightarrow$ | $H \rightarrow$ | L |

| IN3 | Н               | H               | H               | L               | L               | L |

|     | <b>†</b>        |                 |                 |                 |                 |   |

When F/R pin input is high  $\rightarrow$  180-degree current-carrying When F/R pin input is low  $\rightarrow$  120-degree current-carrying

- CTL pin input

- a) Power-saving mode V<sub>CTL</sub> < V<sub>IL</sub> (0.95V : typ)

- $\bullet$   $L_{IN}1$  to  $L_{IN}3$  and  $H_{IN}1$  to  $H_{IN}3$  outputs all set to low

- $I_{CC} = 0$ , HB pin = OFF

The power consumption of the IC can now be set to 0, and the power consumption of the Hall element connected to the HB pin and the output block can also be set to 0.

b) Standby mode While stopped: V<sub>IL</sub> < V<sub>CTL</sub> < V<sub>IM</sub>1 (2.33V: typ); while running: V<sub>IL</sub> < V<sub>CTL</sub> < V<sub>IM</sub>2 (2.1V: typ)

The  $U_{IN}1$  to 3 outputs are set to low, and the bootstrap charge pulse (pulse width: 2.5 $\mu$ s: design target) is output to the  $L_{IN}1$  to 3 outputs in preparation for drive start.

- c) Drive mode At drive start: V<sub>IM</sub>1 < V<sub>CTL</sub> < 7V; during drive: V<sub>IM</sub>2 < V<sub>CTL</sub> < 7V (V<sub>IH</sub> 4.7V: typ) The motor is driven at the PWM duty ratio that corresponds to V<sub>CTL</sub>. When V<sub>CTL</sub> is increased, the PWM duty ratio increases, and the maximum duty ratio is established at "V<sub>IH</sub>."

- d) Test mode 8.5V < V<sub>CTL</sub> < V<sub>CC</sub>

When the CTL pin voltage is 8V or higher, the IC enters the test mode, and the motor is driven at the 120-degree current-carrying and maximum duty\* ratio.

- \* When the PWM oscillation frequency setting is 17kHz, the maximum duty ratio in the 120-degree current carrying mode is 88% (typ).

- The CTL pin is pulled down by  $170k\Omega$  (120-degree mode): Typ,  $131.6k\Omega$  (sine wave mode): typ inside the IC. Caution is required when the control input voltage input is subjected to resistance division, for example.

- Bootstrap capacitor initial charging mode

When the mode is switched from the power-saving

mode to the standby mode and then to the drive mode,

the IC enters the bootstrap capacitor charging mode

(HIN1, HIN2, HIN3 pins = L LIN1, LIN2, LIN3 pins

= H 4.55ms typ) in order to charge the bootstrap

capacitor.

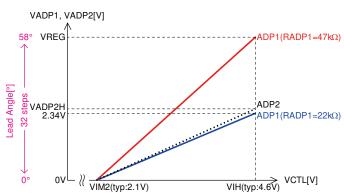

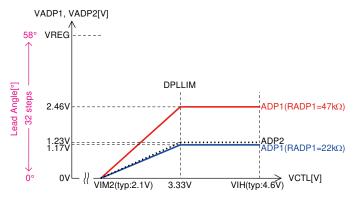

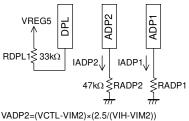

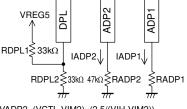

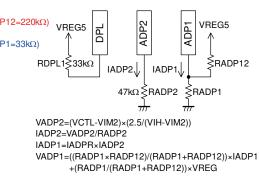

• Drive phase adjustment

During 180-degree current-carrying drive, any lead angle from 0 to 58 degrees can be set using the ADP1 pin voltage (lead angle control). This setting can be adjusted in 32 steps (in 1.875-degree increments) from 0 to 58 degrees using the ADP1 pin voltage, and it is updated every Hall signal cycle (it is sampled at the rising edge of the IN3 input and updated at its falling edge).

A number of lead angle adjustments proportionate to the CTL pin voltage can be undertaken by adjusting

2. The ADP2 pin rise can be halted (a limit on the lead angle adjustment can be set by means of the CTL voltage) by setting DPL (pin 10).

3. The offset and slope can be adjusted as desired by setting RADP1 and RADP12 of ADP1 (pin 15). (It is also possible to set a limit on the lead angle

the resistance levels of resistors connected to the ADP1 pin, ADP2 pin and DPL pin. When these pins are not going to be used, reference must be made to section 4.5, and the pins must not be used in the open status. Furthermore, a resistance of  $47k\Omega$  or more must be used for the resistor (RADP2) that is connected to the ADP2 pin.

1. The slopes of V<sub>CTL</sub> and VADP1 can be adjusted by setting the resistance level of the resistor (RADP1) connected to ADP1 (pin 15).

VADP2=(VCTL-VIM2)×(2.5/(VIH-VIM2)) =(VCTL-2.1V)×(2.5/(4.6V-2.1V)) IADP2=VADP2/RADP2 IADP1=IADPR×IADP2 VADP1=IADP1×RADP1

VADP2=(VCTL-VIM2)×(2.5/(VIH-VIM2)) IADP2=VADP2/RADP2 IADP1=IADPR×IADP2 VADP1=IADP1×RADP1 DPLLIM=VDPL×1.36

adjustment by means of the CTL voltage by setting DPL.)

4. When the lead angle is not adjusted ADP1 pin: shorted to ground; ADP2 pin and DPL pin: pulled down to ground using the resistors

5. When the lead angle is not adjusted by means of the CTL pin voltage (for use with a fixed lead angle) ADP1 pin: lead angle setting by resistance division from VREG5; ADP2 pin and DPL pin: pulled down to ground by the resistors

# **Description of LV8139**

## 1. Current Limiter Circuit

The current limiter circuit limits the output current peak value to a level determined by the equation  $I = V_{RF}/Rf$  (where  $V_{RF} = 0.25V$  typ, Rf is the value of the current detection resistor). The current limiter operates by reducing the  $H_{IN}$  output on duty to suppress the current.

The current limiter circuit detects the reverse recovery current of the diode due to PWM operation. To assure that the current limiting function does not malfunction, its operation has a delay of approx. 1µs. If the motor coils resistance or a low inductance, current fluctuation at startup (when there is no back electromotive force in the motor) will be rapid. The delay in this circuit means that at such times the current limiter circuit may operate at a point well above the set current. Application must take this increase in the current due to the delay into account when the current limiter value is set.

# 2. Power Saving Circuit (CTL pin)

This IC goes into the power saving mode that stops operation of all the circuits to reduce the power consumption. If the HB pin is used for the Hall element bias and the output block, the current consumption in the power-saving mode is zero.

# 3. Hall Input Signal

Signals with an amplitude in excess of the hysteresis is required for the Hall inputs. However, considering the influence of noise and phase displacement, an amplitude of over 100mV is desirable.

If noise disrupts the output waveform, this must be prevented by inserting capacitors or other devices across the Hall inputs. The Hall inputs are used by the circuit inside the IC as decision signals so if noise enters, a malfunction occurs in the operation.

Although the circuit is designed to tolerate a certain

Although the circuit is designed to tolerate a certain amount of noise, care is required.

Furthermore, when the Hall signal amplitude has changed as a result of a change in temperature, the drive phase may possibly shift due to the Hall amplifier hysteresis. It is the user who is responsible for giving due consideration to this aspect. Use of a Hall IC is recommended unless there is a reason not to use one.

If all three phases of the Hall input signal go to the same input state (HHH or LLL), all the HIN/LIN outputs are set to low.

If the outputs from a Hall IC are used, fix one side of the inputs (either the "+" or "-" side) at a voltage within the common-mode input voltage range (0.3V to VREG-1.8V), and use the other input side as an input over the 0V to VREG range.

# 4. Constraint Protection Circuit

A constraint protection circuit is incorporated in order to protect the output elements and motor when the motor is constrained. The circuit is activated when the Hall signal is not switched for a specific period of time when the motor is in operation. The counter is reset each time the motor rotates 360 degrees in terms of the electrical angle. All the H<sub>IN</sub> and L<sub>IN</sub> outputs are set to the low level when the constraint protection circuit is in operation. This time is determined by the capacitance of the capacitor connected to the CSD pin.

Oscillation time of CSD pin (1 pulse) T = |  $(V_{OH}-V_{OL})/ICHG1 \mid \times C (\mu F) + \mid (V_{OH}-V_{OL})/ICHG2 \mid \times C (\mu F)$ Constraint protection detection time T1 (s) = T × 256 (count) Constraint protection time T2 (s) = T × 2816 (count)

When a  $0.022\mu F$  capacitor is attached, T = 8.36ms, T1 = 2.14s and T2 = 23.54s are established as the typical ratings. After the motor has been constrained, the constraint protection state is established at 2.14 (s), and then after 23.54 (s) has elapsed, the constraint protection circuit is reset automatically. A time that provides some leeway in the motor start time that factors in any fluctuations must be selected as the setting.

Conditions for releasing the constraint protection state other than by automatic resetting:

When CTL pin voltage <  $V_{IM}2$  input  $\rightarrow$  protection release and CSD count reset When the low level is detected on the TH pin  $\rightarrow$  protection release and CSD count reset When FR has been switched  $\rightarrow$  protection release and CSD count reset When TSD protection is detected  $\rightarrow$  CSD count

when ISD protection is detected  $\rightarrow$  CSD count stop

# 5. Power Supply Stabilization

Since this IC adopts a switching drive technique, the power-supply line level can be disrupted easily. Thus capacitors large enough to stabilize the power supply voltage must be inserted between the  $V_{CC}$  pins and ground. If the electrolytic capacitors cannot be connected close to their corresponding pins, ceramic capacitors of about  $0.1\mu F$  must be connected near these pins.

If diodes are inserted in the power-supply line to prevent destruction of the device when the power supply is connected with reverse polarity, the power supply line levels will be even more easily disrupted, and even larger capacitors must be used.

## 6. VREG Stabilization

Connect a capacitor with a capacitance of  $0.1\mu F$  or more between VREG5 and ground in order to stabilize the VREG voltage that is the power supply of the control circuit.

The ground lead of that capacitor must be located as close as possible to the control system ground (SGND) of the IC.

Forward/Reverse Switching (F/R pin)

Switching between forward rotation and reverse rotation must not be undertaken while the motor is running.

# 8. TH Pin

The TH pin must normally be pulled up to VREG5 for use. When this pin has been set to low, all the H<sub>IN</sub>/L<sub>IN</sub> outputs are set to low. When reset is initiated, the bootstrap initial charging mode is established.

## 9. FAULT Pin

The FAULT pin must normally be pulled up to VREG5 for use. When this pin has been set to low, all the  $H_{\mbox{IN}}/L_{\mbox{IN}}$  outputs are set to low. When reset is initiated, the bootstrap initial charging mode is established.

All the outputs are set to low. In addition, the FG1/FG3 output goes off, too. When reset is initiated, the bootstrap initial charging mode is established.

# 10. PWM Frequency Setting fCPWM ≈ 1/(1.7CR)

Components with good temperature characteristics must be used.

An oscillation frequency of about 17kHz is obtained when a 2200pF capacitor and  $15k\Omega$  resistor are used. If the PWM frequency is too low, switching noise will be heard from the motor; conversely, if it is too high, the output power loss will increase. For this reason, a frequency between 15kHz and 30kHz or so is desirable. The capacitor ground must be connected as close as possible to the control system ground (SGND pin) of the IC to minimize the effects of the outputs.

If there are no fluctuations in the capacitance or resistance of the external capacitors or resistors and only the IC fluctuations are to be considered, an actual capability of  $\pm 3\%$  can be expected.

11. Concerning the power-raising operation

This IC provides sine wave PWM drive so it

performs operations similar to synchronous

rectification. These operations are such that current is

sometimes returned to the motor power supply side

depending on the conditions of use. For instance, this

may happen when:

- The drive phase is shifted.

- The motor has been suddenly accelerated.

- The output duty ratio has been decreased sharply while the motor is running.

If the output duty ratio has been decreased sharply, it is highly likely that current will return to the motor power supply.

The extent to which the motor supply voltage increases differs depending on the size of the capacitors used in the product that incorporates the motor, the size of the capacitor inserted between the motor power supply and ground on the motor circuit board and the motor used; as such, it is the user who is responsible for giving due consideration to this aspect.

It is necessary to take remedial action such as increasing the capacitance of the capacitors or reducing the speed at which the duty ratio will be reduced when the motor supply voltage rises to ensure that the maximum withstand voltage of the element used for output is not exceeded.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re