# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Stepper Motor Driver, PWM, Constant-Current Control, 1/128 step

#### **Overview**

The LV8728MR is a PWM current-controlled micro step stepper motor driver. This driver can perform eight types of excitation mode from Full step to 1/128 step and can drive simply by the CLK input.

#### Function

- Single-channel PWM current control stepper motor driver

- BiCDMOS process IC

- Output on-resistance (upper side:  $0.3\Omega$ ; lower side:  $0.25\Omega$ ; total of upper and lower:  $0.55\Omega$ ; Ta = 25°C, I $_{O}$  = 2.0A)

- Full, Half, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128 step excitation mode are selectable

- Advance the excitation step with the only step signal input

- Available forward reverse control

- $I_0 max = 2.0A$

- Over-current protection circuit

- Thermal shutdown circuit

- Input pull down resistance

- With reset pin and enable pin.

#### **Typical Applications**

- Printer (Multi-function printer, 3D printer, etc.)

- Security camera

- Scanner

- Stage light

#### **ON Semiconductor®**

#### www.onsemi.com

MFP30KR (375mil)

#### **ORDERING INFORMATION**

Ordering Code: LV8728MR-AH

Package MFP30KR (Pb-Free / Halogen Free)

Shipping (quantity/packing) 1000 / Tape & Reel

For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. http://www.onsemi.com/pub\_link/Collateral/BRD8011-D.PDF

#### Maximum Ratings (Note 1)

| Parameter                            | Symbol                | Conditions                                     | Ratings     | Unit |

|--------------------------------------|-----------------------|------------------------------------------------|-------------|------|

| Maximum supply voltage               | VM max                | VM , VM1 , VM2                                 | 36          | V    |

| Maximum output current               | I <sub>O</sub> max    | Per 1ch                                        | 2.0         | А    |

| Maximum logic input voltage          | V <sub>IN</sub> max   | ST , MD1 , MD2 , MD3 , OE , RST , FR ,<br>STEP | 6           | V    |

| Maximum FDT input voltage            | VFDT max              |                                                | 6           | V    |

| Maximum VREF input voltage           | VREF max              |                                                | 6           | V    |

| Maximum MO input voltage             | V <sub>MO</sub> max   |                                                | 6           | V    |

| Maximum DOWN input voltage           | V <sub>DOWN</sub> max |                                                | 6           | V    |

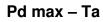

| Allowable power dissipation (Note 2) | Pd max                |                                                | 1.55        | W    |

| Operating temperature                | Topr                  |                                                | -30 to +85  | °C   |

| Storage temperature                  | Tstg                  |                                                | -55 to +150 | °C   |

1. Stresses exceeding those listed in the Absolute Maximum Rating table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. Specified circuit board: 76.1mm×114.3mm×1.6mm, glass epoxy board.

#### Recommended Operating Ranges (Note 3)

| Parameter                | Symbol | Conditions                           | Ratings | Unit |

|--------------------------|--------|--------------------------------------|---------|------|

| Supply voltage range     | VM     | VM , VM1 , VM2                       | 9 to 32 | V    |

| Logic input voltage      | VIN    | ST, MD1, MD2, MD3, OE, RST, FR, STEP | 0 to 5  | V    |

| FDT input voltage range  | VFDT   |                                      | 0 to 5  | V    |

| VREF input voltage range | VREF   |                                      | 0 to 3  | V    |

3. Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Electrical Characteristics at Ta=25°C, VM=24V, VREF=1.5V unless otherwise noted. (Note 4)

| Parameter                             |            | Ciurah al          | Conditions                                                              | Ratings |      |       | 1.1  |

|---------------------------------------|------------|--------------------|-------------------------------------------------------------------------|---------|------|-------|------|

|                                       |            | Symbol Conditions  |                                                                         | min     | typ  | max   | Unit |

| Standby mode curren                   | t drain    | I <sub>M</sub> st  | ST = "L" , VM+VM1+VM2                                                   |         | 70   | 100   | μA   |

| Current drain                         |            | IM                 | ST = "H", OE = "H", no load<br>VM+VM1+VM2                               |         | 3.3  | 4.6   | mA   |

| Thermal shutdown temperature          |            | TSD                | Guaranteed by design                                                    | 150     | 180  | 200   | °C   |

| Thermal hysteresis wi                 | idth       | ΔTSD               | Guaranteed by design                                                    |         | 40   |       | °C   |

| Logic pin input curren                | t          | IINL               | ST , MD1 , MD2 , MD3 , OE , RST ,<br>FR , STEP , V <sub>IN</sub> = 0.8V | 3       | 8    | 15    | μA   |

|                                       |            | IINH               | ST,MD1,MD2,MD3,OE,RST,<br>FR,STEP,V <sub>IN</sub> = 5V                  | 30      | 50   | 70    | μA   |

| Logic input H                         | ligh       | V <sub>IN</sub> H  | ST, MD1, MD2, MD3, OE, RST,                                             | 2.0     |      | 5.0   | V    |

| voltage Lo                            | ow         | VINL               | FR, STEP                                                                | 0       |      | 0.8   | V    |

| FDT pin high level vol                | ltage      | Vfdth              |                                                                         | 3.5     |      |       | V    |

| FDT pin middle level                  | voltage    | Vfdtm              |                                                                         | 1.1     |      | 3.1   | V    |

| FDT pin low level volt                | age        | Vfdtl              |                                                                         |         |      | 0.8   | V    |

| Chopping frequency                    |            | Fch                | Cosc1 = 100pF                                                           | 70      | 100  | 130   | kHz  |

| OSC1 pin charge/disc<br>current       | charge     | losc1              |                                                                         | 7       | 10   | 13    | μA   |

| Chopping oscillation of               | circuit    | Vtup1              |                                                                         | 0.8     | 1    | 1.2   | V    |

| threshold voltage                     |            | Vtdown1            |                                                                         | 0.3     | 0.5  | 0.7   | V    |

| VREF pin input voltag                 | je         | Iref               | VREF = 1.5V                                                             | -0.5    |      |       | μA   |

| DOWN output residua                   | al voltage | VOIDOWN            | ldown = 1mA                                                             |         | 40   | 100   | mV   |

| MO pin residual voltag                | ge         | V <sub>O</sub> IMO | Imo = 1mA                                                               |         | 40   | 100   | mV   |

| Hold current switching frequency      | 9          | Fdown              | Cosc2 = 1500pF                                                          | 1.12    | 1.6  | 2.08  | Hz   |

| OSC2 pin charge/disc<br>current       | charge     | losc2              |                                                                         | 7       | 10   | 13    | μA   |

| Hold current switching                | 9          | Vtup2              |                                                                         | 0.8     | 1    | 1.2   | V    |

| frequency threshold v                 | oltage     | Vtdown2            |                                                                         | 0.3     | 0.5  | 0.7   | V    |

| VREG1 output voltage                  | е          | Vreg1              |                                                                         | 4.7     | 5    | 5.3   | V    |

| VREG2 output voltage                  | е          | Vreg2              |                                                                         | 18      | 19   | 20    | V    |

| Output on-resistance                  |            | Ronu               | I <sub>O</sub> = 2.0A, upper side ON resistance                         |         | 0.3  | 0.42  | Ω    |

|                                       |            | Rond               | I <sub>O</sub> = 2.0A, lower side ON resistance                         |         | 0.25 | 0.35  | Ω    |

| Output leakage currer                 | nt         | lOleak             | V <sub>M</sub> = 36V                                                    |         |      | 50    | μA   |

| Diode forward voltage                 | ;          | VD                 | I <sub>D</sub> = -2.0A                                                  |         | 1.1  | 1.4   | V    |

| Current setting reference VRF voltage |            | VRF                | VREF = 1.5V, Current ratio 100%                                         | 0.285   | 0.3  | 0.315 | V    |

4. Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

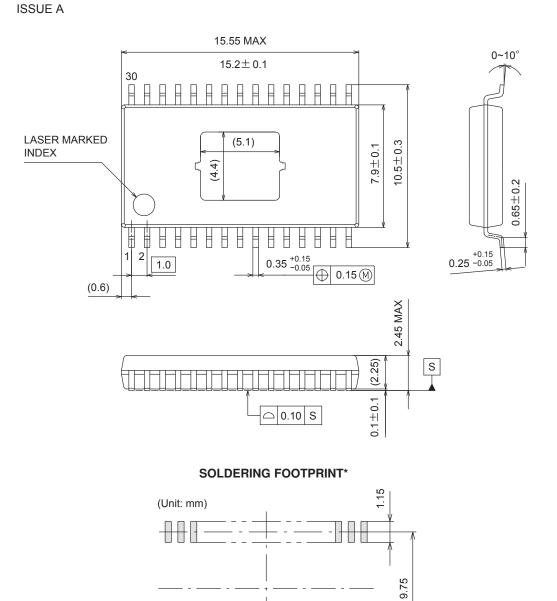

#### **Package Dimensions**

unit : mm

SOIC30 W / MFP30KR (375 mil) CASE 751CH

NOTE: The measurements are not to guarantee but for reference only.

1.00

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

0.50

#### **Pin Assignment**

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | VREG2<br>VM<br>OUT1A<br>PGND1<br>VM1<br>RF1<br>OUT1B | LV87    | VREG1<br>ST<br>MD1<br>MD2<br>MD3<br>OE<br>RST | 30<br>29<br>28<br>27<br>26<br>25<br>24 |

|---------------------------------|------------------------------------------------------|---------|-----------------------------------------------|----------------------------------------|

|                                 |                                                      |         |                                               |                                        |

| 5                               | VM1                                                  | _       | MD3                                           | 26                                     |

| 6                               | RF1                                                  | <       | OE                                            | 25                                     |

| 7                               | OUT1B                                                | 8       | RST                                           | 24                                     |

| 8                               | NC                                                   | 728MF   | GND                                           | 23                                     |

| 9                               | OUT2A                                                | 28<br>7 | FR                                            | 22                                     |

| 10                              | RF2                                                  | R       | STEP                                          | 21                                     |

| 11                              | VM2                                                  |         | OSC1                                          | 20                                     |

| 12                              | PGND2                                                |         | OSC2                                          | 19                                     |

| 13                              | OUT2B                                                |         | FDT                                           | 18                                     |

| 14                              | GND                                                  |         | DOWN                                          | 17                                     |

| 15                              | VREF                                                 |         | МО                                            | 16                                     |

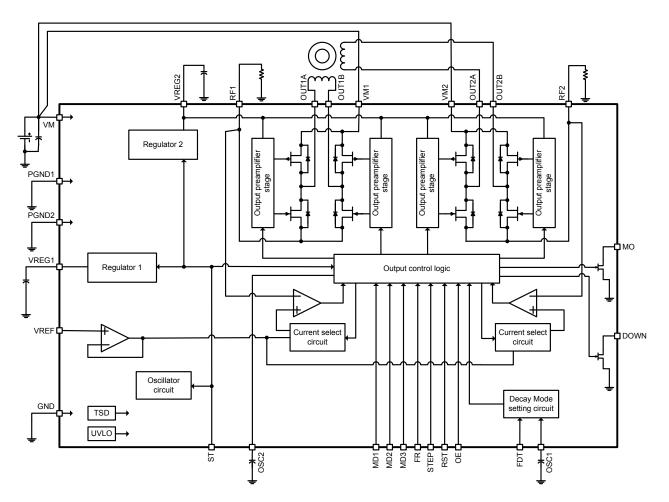

#### **Block Diagram**

#### **Pin Functions**

| Pin F   | unctions |                                         |                                       |

|---------|----------|-----------------------------------------|---------------------------------------|

| Pin No. | Pin Name | Pin Function                            | Equivalent Circuit                    |

| 21      | STEP     | Step clock pulse signal input pin       |                                       |

| 22      | FR       | Forward / Reverse signal input pin      | VREG1O                                |

| 24      | RST      | Reset signal input pin                  |                                       |

| 24      | OE       | Output enable signal input pin          |                                       |

|         |          |                                         |                                       |

| 26      | MD3      | Excitation mode switching pin           |                                       |

| 27      | MD2      | Excitation mode switching pin           | Ť                                     |

| 28      | MD1      | Excitation mode switching pin           |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         | ι τοκΩ μ→Η                            |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

| 29      | ST       | Chip enable pin                         | V77010                                |

|         |          |                                         | VREG1O                                |

|         |          |                                         | *                                     |

|         |          |                                         | L L L L L L L L L L L L L L L L L L L |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         | ξ20ΚΩ                                 |

|         |          |                                         |                                       |

|         |          |                                         | 10K0                                  |

|         |          |                                         | 10KΩ<br>•                             |

|         |          |                                         | │                                     |

|         |          |                                         |                                       |

|         |          |                                         | <u></u>                               |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

| 3       | OUT1A    | Channel 1 output A pin                  |                                       |

| 4       | PGND1    | Channel 1 Power ground pin              | 511                                   |

| 5       | VM1      | Channel 1 motor power supply pin        |                                       |

| 6       | RF1      | Channel 1 current sense resistor        |                                       |

| 0       |          | pin                                     |                                       |

| 7       | OUT1B    | Channel 1 output B pin                  |                                       |

| 9       | OUT2A    | Channel 2 output A pin                  |                                       |

| 10      | RF2      | Channel 2 current sense resistor        |                                       |

| 10      | NI Z     |                                         |                                       |

| 11      | VM2      | pin<br>Channel 2 motor power supply pin | │                                     |

| 12      | PGND2    | Channel 2 Power ground pin              |                                       |

|         |          | Channel 2 output B pin                  |                                       |

| 13      | OUT2B    | Channel 2 output B pin                  |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         | GNDO • •                              |

|         |          |                                         |                                       |

| 15      | VREF     | Constant-current control reference      |                                       |

| 15      | VINEI    | voltage input pin.                      | VREG1 O                               |

|         |          | voltage input pin.                      |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

| 1       |          | 1                                       |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

|         |          |                                         |                                       |

Continued on next page

#### Continued from preceding page

|              | ed from prece     |                                                                                                                                                                                                   |                    |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Pin No.<br>1 | Pin Name<br>VREG2 | Pin Function<br>Internal regulator capacitor                                                                                                                                                      | Equivalent Circuit |

|              | VREGZ             | connection pin.                                                                                                                                                                                   |                    |

| 30           | VREG1             | Internal regulator capacitor<br>connection pin.                                                                                                                                                   |                    |

| 16<br>17     | MO<br>DOWN        | Output pin for position detecting<br>Output pin for holding current<br>reduction                                                                                                                  | VREG1 O            |

| 19           | OSC2              | Capacitor connection pin for STEP<br>signal off detection time setting<br>When not using the current<br>reduction by DOWN pin, need to<br>connect OSC2 pin to GND at 10kΩ<br>(recommended value). | VREG1 O            |

| 20           | OSC1              | Capacitor connection pin for<br>chopping frequency setting.                                                                                                                                       |                    |

| 14<br>23     | GND<br>GND        | Ground pin                                                                                                                                                                                        |                    |

#### **Functional Description**

1. Input Pin Function

Each input terminal has the function to prevent the flow of the current from an input to a power supply. Therefore, Even if a power supply (VM) is turned off in the state that applied voltage to an input terminal, the electric current does not flow into the power supply.

2. Stand-by function

When ST pin is at low levels, the IC enters stand-by mode, all logic is reset and output is turned OFF. When ST pin is at high levels, the stand-by mode is released.

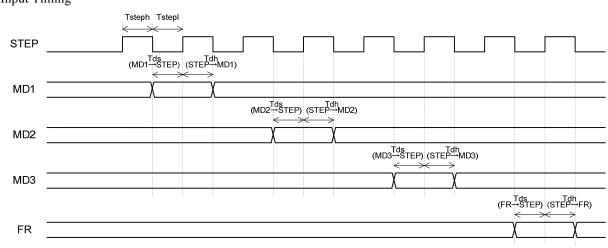

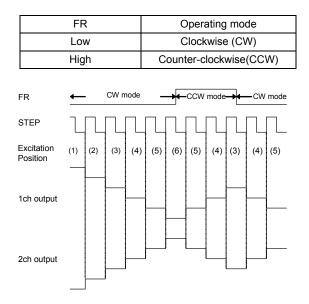

#### 4. Input Timing

3. STEP pin function

| Input |            | Operating mode               |

|-------|------------|------------------------------|

| ST    | STEP       |                              |

| Low   | Don't care | Standby mode                 |

| High  |            | Excitation step is proceeded |

| High  |            | Excitation step is kept      |

Tsteph/Tstepl: Clock H/L pulse width (min 500ns) Tds: Data set-up time (min 500ns) Tdh: Data hold time (min 500ns)

#### 5. Position detection monitor function

The MO position detection monitoring pin is an open drain type.

When the excitation position is in the initial position, the MO output is placed in the ON state.

(Refer to "Examples of current waveforms in each of the excitation modes.")

| MO  | Status                  |

|-----|-------------------------|

| ON  | Initial position        |

| OFF | Except initial position |

#### 6. Excitation mode setting function

Set the excitation setting as shown in the following

table by setting MD1 pin, MD2 pin and MD3 pin.

|      | Input |      | Excitation | Initial p   | osition     |

|------|-------|------|------------|-------------|-------------|

| MD3  | MD2   | MD1  | mode       | 1ch current | 2ch current |

| Low  | Low   | Low  | Full step  | 100%        | -100%       |

| Low  | Low   | High | Half step  | 100%        | 0%          |

| Low  | High  | Low  | 1/4 step   | 100%        | 0%          |

| Low  | High  | High | 1/8 step   | 100%        | 0%          |

| High | Low   | Low  | 1/16 step  | 100%        | 0%          |

| High | Low   | High | 1/32 step  | 100%        | 0%          |

| High | High  | Low  | 1/64 step  | 100%        | 0%          |

| High | High  | High | 1/128 step | 100%        | 0%          |

The initial position is also the default state at start-up and excitation position at counter-reset in each excitation mode.

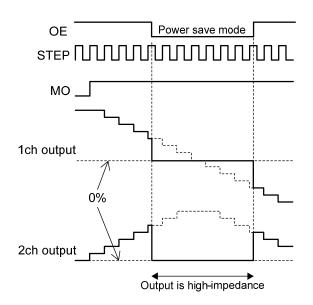

7. Output enable function

When the OE pin is set Low, the output is forced OFF and goes to high impedance. However, the internal logic circuits are operating, so the excitation position proceeds when the STEP is input. Therefore, when OE pin is returned to High, the output level conforms to the excitation position that is advanced by the STEP input.

| OE   | Operating mode |

|------|----------------|

| Low  | Output OFF     |

| High | Output ON      |

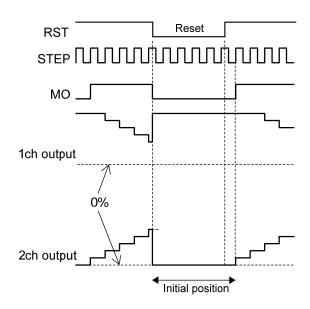

8. Reset function

When the RST pin is set Low, the excitation position of the output is set to the initial position forcibly and MO pin output is turn ON state. And then by setting RST pin is High, the excitation position moves forward with the next step signal.

| RST  | Operating mode   |

|------|------------------|

| Low  | Reset status     |

| High | Normal operation |

9. Forward / Reverse switching

The internal D/A converter proceeds by a bit on the rising edge of the step signal input to the STP pin. In addition, CW and CCW mode are switched by FR pin setting.

In CW mode, the channel 2 current phase is delayed by 90° relative to the channel 1 current.

In CCW mode, the channel 2 current phase is advanced by 90° relative to the channel 1 current.

#### 10. Decay mode setting

Current Decay method is selectable as shown below by applied voltage to the FDT pin.

| FDT voltage          | Decay mode  |

|----------------------|-------------|

| 3.5V to 5.0V         | SLOW Decay  |

| 1.1V to 3.1V or Open | MIXED Decay |

| 0V to 0.8V           | FAST Decay  |

#### 11. Output current setting

Output current is set as shown below by the VREF pin (applied voltage) and a resistance value between RF1 (2) pin and GND.

$$I_{OUT} = \frac{V_{REF}}{5 \cdot R_{RFx}}$$

The setting current value above is a 100% output current in each excitation mode.

Where,

| I <sub>OUT</sub> | : Coil current [A]               |

|------------------|----------------------------------|

| Rnn              | · Resistor between RF1 (2) and ( |

$\begin{array}{l} R_{RFx} & : \mbox{Resistor between RF1 (2) and GND [} \Omega \mbox{]} \\ V_{REF} & : \mbox{Input voltage at the VREF pin [V]} \end{array}$

For example, when VREF = 1.1V and RF1 (2) resistance is  $0.22\Omega$ , the setting current is shown below:

$$I_{OUT} = \frac{1.1}{5 \times 0.22} = 1.0 \ [A]$$

12. Chopping frequency setting

For constant-current control, LV8728 performs PWM operation at the chopping frequency determined by the capacitor (COSC1) connected between the OSC1 pin and GND.

The calculation for the value of chopping frequency is:

$$Fch = \frac{IOSC1}{COSC1}$$

Where,

Fch : Chopping frequency [Hz]

I<sub>OSC1</sub> : Charge/ Discharge current of OSC1pin [A].

IOSC1 is 10uA (typ) by electrical Characteristics.

C<sub>OSC1</sub> : Capacitor for chopping frequency setting [F]

For example, when COSC1=100pF and IOSC1=10uA (typ), the chopping frequency is shown below:

$$Fch = \frac{10 \times 10^{-6}}{100 \times 10^{-12}} = 100 \ [kHz]$$

The higher the chopping frequency is, the greater the output switching loss becomes. As a result, heat generation issue arises. The lower the chopping frequency is, the lesser the heat generation becomes. However, current ripple occurs. Since noise increases when switching of chopping takes place, you need to adjust frequency with the influence to the other devices into consideration.

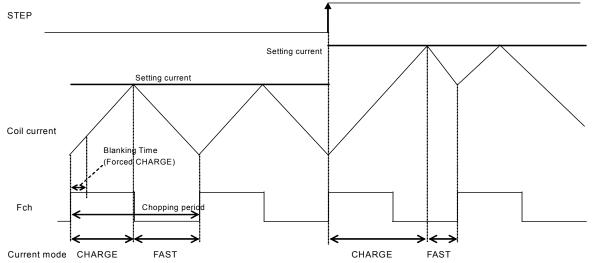

#### 13. Blanking time

If, when exercising PWM constant-current chopping control over the motor current, the mode is switched from decay to charge, the recovery current of the parasitic diode may flow to the current sensing resistance, causing noise to be carried on the current sensing resistance pin, and this may result in erroneous detection. To prevent this erroneous detection, a blanking period is provided to prevent the noise occurring during mode switching from being received. During the blanking time, even if noise is generated in sense resistor, a mode does not switch from CHARGE to DECAY. In this IC, the blanking time is fixed to approximately  $1\mu$ s.

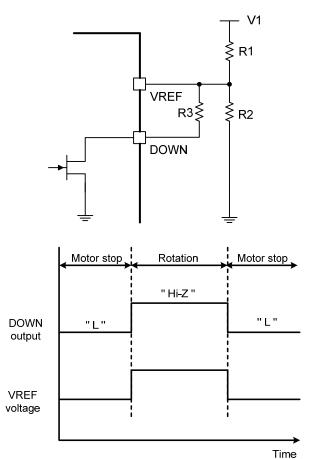

14. DOWN output pin for holding current reduction The DOWN output pin is an open drain type. When DOWN pin is turned ON, the motor is holding current.

| DOWN | Status           |

|------|------------------|

| ON   | Holding current  |

| OFF  | Normal operation |

To avoid to applying high current to a motor coil for long term at one position, the DOWN output may be used to reduce the reference current. The DOWN is asserted when the step clock interval is longer than TDOWN (STEP signal off detection time). With the circuit is shown in below. VREF voltage can be reduced when the DOWN is turned ON. The open-drain output in once turned ON, is turned OFF at the next rising edge of STP.

For example, when V1=5V, R1=68k $\Omega$ , R2=30k $\Omega$ , R3=5k $\Omega$ , RRF1 (2) =0.22 $\Omega$ , the VREF voltage is shown below:

$R_{RF1 (2)}$  is Resistor between RF1 (2) and GND [ $\Omega$ ] VREF is input voltage at the VREF pin [V]

When the DOWN is turned OFF

$$V_{REF} = \frac{5 \times 30}{68 + 30} \approx 1.53 \ [V]$$

$$I_{OUT} = \frac{1.53}{5 \times 0.22} \approx 1.39 \ [A]$$

When the DOWN is turned ON, combined resistor of R2 and R3 is about  $4.3k\Omega$ .

$$V_{REF} = \frac{5 \times 4.3}{68 + 4.3} \approx 0.3 \ [V]$$

$$I_{OUT} = \frac{0.3}{5 \times 0.22} \approx 0.27 \ [A]$$

15. SETP signal off detection time setting STEP signal off time is determined by the capacitor (COSC2) connected between the OSC2 pin and GND. When this function is unused, connect OSC2 pin to GND at 10kohm (recommendation). The calculation for the value of STEP signal off detection time is:

$$T_{DOWN} = C_{OSC2} \times 0.4 \times 10^9$$

Where,

$T_{DOWN}$  : STEP signal off detection time [Sec]  $C_{OSC2}$  : Capacitor for STEP signal off time [F]

For example, when COSC2=1500pF, the STEP signal off detection time is shown below:

$$T_{DOWN} = 1500 \times 10^{-12} \times 0.4 \times 10^{9} \\ = 0.6 [Sec]$$

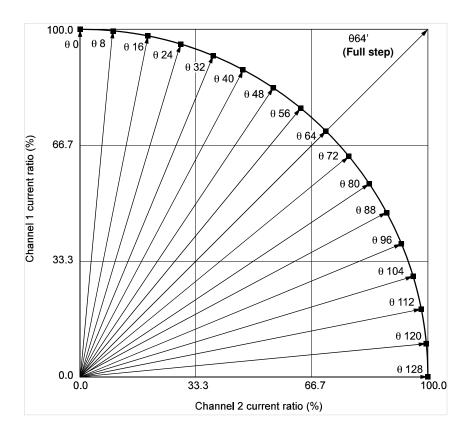

#### 16. Output current vector locus (one step is normalized to 90 degrees)

| Current setting ratio in each excitation mode |

|-----------------------------------------------|

|-----------------------------------------------|

|      |     | tep (%) | 1/64 st | en (%) |     | ep (%) | 1/16 st | ep (%) | 1/8 st | ep (%) | 1/4 ste | ep (%) | Half step (%) |     | Full step (%) |     |

|------|-----|---------|---------|--------|-----|--------|---------|--------|--------|--------|---------|--------|---------------|-----|---------------|-----|

| STEP | 1ch | 2ch     | 1ch     | 2ch    | 1ch | 2ch    | 1ch     | 2ch    | 1ch    | 2ch    | 1ch     | 2ch    | 1ch           | 2ch | 1ch           | 2ch |

| θ0   | 100 | 0       | 100     | 0      | 100 | 0      | 100     | 0      | 100    | 0      | 100     | 0      | 100           | 0   |               |     |

| θ1   | 100 | 1       |         |        |     | -      |         | -      |        | -      |         | -      |               | -   |               |     |

| θ2   | 100 | 2       | 100     | 2      |     |        |         |        |        |        |         |        |               |     |               |     |

| θ3   | 100 | 4       |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ4   | 100 | 5       | 100     | 5      | 100 | 5      |         |        |        |        |         |        |               |     |               |     |

| θ5   | 100 | 6       |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ6   | 100 | 7       | 100     | 7      |     |        |         |        |        |        |         |        |               |     |               |     |

| θ7   | 100 | 9       |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ8   | 100 | 10      | 100     | 10     | 100 | 10     | 100     | 10     |        |        |         |        |               |     |               |     |

| 69   | 99  | 11      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ10  | 99  | 12      | 99      | 12     |     |        |         |        |        |        |         |        |               |     |               |     |

| θ11  | 99  | 13      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ12  | 99  | 15      | 99      | 15     | 99  | 15     |         |        |        |        |         |        |               |     |               |     |

| θ13  | 99  | 16      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ14  | 99  | 17      | 99      | 17     |     |        |         |        |        |        |         |        |               |     |               |     |

| θ15  | 98  | 18      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ16  | 98  | 20      | 98      | 20     | 98  | 20     | 98      | 20     | 98     | 20     |         |        |               |     |               |     |

| θ17  | 98  | 21      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ18  | 98  | 22      | 98      | 22     |     |        |         |        |        |        |         |        |               |     |               |     |

| θ19  | 97  | 23      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ20  | 97  | 24      | 97      | 24     | 97  | 24     |         |        |        |        |         |        |               |     |               |     |

| θ21  | 97  | 25      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ22  | 96  | 27      | 96      | 27     |     |        |         |        |        |        |         |        |               |     |               |     |

| θ23  | 96  | 28      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

| θ24  | 96  | 29      | 96      | 29     | 96  | 29     | 96      | 29     |        |        |         |        |               |     |               |     |

| θ25  | 95  | 30      |         |        |     |        |         |        |        |        |         |        |               |     |               |     |

Continued on next page

| Continued | from | preceding | page |  |

|-----------|------|-----------|------|--|

|-----------|------|-----------|------|--|

|                   | 1/128          |                |         | tep (%) | 1/32 d  | tep (%) | 1/16 c | tep (%)  | 1/8 ct/ | ep (%) | 1/4 ct | ep (%) | Halfet | ep (%) | Full et | ер (%) |

|-------------------|----------------|----------------|---------|---------|---------|---------|--------|----------|---------|--------|--------|--------|--------|--------|---------|--------|

| STEP              | 1/120          | 2ch            | 1/04 St | 2ch     | 1/32 Si | 2ch     | 1/10 S | 2ch      | 1/8 St  | 2ch    | 1/4 St | 2ch    | 1ch    | 2ch    | 1ch     | 2ch    |

| θ26               | 95             | 31             | 95      | 31      | TCH     | 2011    | TCH    | 2011     | TCH     | 2011   | TCH    | 2011   | TCH    | 2011   | TCH     | 2011   |

| θ27               | 95             | 33             | 00      | 01      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ28               | 94             | 34             | 94      | 34      | 94      | 34      |        |          |         |        |        |        |        |        |         |        |

| θ29               | 94             | 35             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| 030               | 93             | 36             | 93      | 36      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ31               | 93             | 37             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ32               | 92             | 38             | 92      | 38      | 92      | 38      | 92     | 38       | 92      | 38     | 92     | 38     |        |        |         |        |

| θ33               | 92             | 39             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ34               | 91             | 41             | 91      | 41      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ35               | 91             | 42             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ36               | 90             | 43             | 90      | 43      | 90      | 43      |        |          |         |        |        |        |        |        |         |        |

| θ37               | 90             | 44             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ38               | 89             | 45             | 89      | 45      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ39               | 89             | 46             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ40               | 88             | 47             | 88      | 47      | 88      | 47      | 88     | 47       |         |        |        |        |        |        |         |        |

| θ41               | 88             | 48             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ42               | 87             | 49             | 87      | 49      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ43               | 86             | 50             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ44               | 86             | 51             | 86      | 51      | 86      | 51      |        |          |         |        |        |        |        |        |         |        |

| θ45               | 85             | 52             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ46               | 84             | 53             | 84      | 53      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ47               | 84             | 55             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ48               | 83             | 56             | 83      | 56      | 83      | 56      | 83     | 56       | 83      | 56     |        |        |        |        |         |        |

| θ49               | 82             | 57             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ50               | 82             | 58             | 82      | 58      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ51               | 81             | 59             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ52               | 80             | 60             | 80      | 60      | 80      | 60      |        |          |         |        |        |        |        |        |         |        |

| θ53               | 80             | 61             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ54               | 79             | 62             | 79      | 62      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ55               | 78             | 62             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ56               | 77             | 63             | 77      | 63      | 77      | 63      | 77     | 63       |         |        |        |        |        |        |         |        |

| θ57               | 77             | 64             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ58               | 76             | 65             | 76      | 65      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ59               | 75             | 66             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ60               | 74             | 67             | 74      | 67      | 74      | 67      |        |          |         |        |        |        |        |        |         |        |

| <del>0</del> 61   | 73             | 68             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| <del>0</del> 62   | 72             | 69             | 72      | 69      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ63               | 72             | 70             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ64               | 71             | 71             | 71      | 71      | 71      | 71      | 71     | 71       | 71      | 71     | 71     | 71     | 71     | 71     | 100     | 100    |

| θ65               | 70             | 72             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ66               | 69             | 72             | 69      | 72      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ67               | 68             | 73             |         |         |         |         |        | ļ        |         |        |        |        |        |        |         |        |

| <del>0</del> 68   | 67             | 74             | 67      | 74      | 67      | 74      |        | ļ        |         |        |        |        |        |        |         |        |

| 069               | 66             | 75             |         |         |         |         |        | ļ        |         |        |        |        |        |        |         |        |

| θ70               | 65             | 76             | 65      | 76      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ71               | 64             | 77             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| θ72               | 63             | 77             | 63      | 77      | 63      | 77      | 63     | 77       |         |        |        |        |        |        |         |        |

| 073               | 62             | 78             |         |         |         |         |        | ļ        |         |        |        |        |        |        |         |        |

| θ74               | 62             | 79             | 62      | 79      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ75               | 61             | 80             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| 076               | 60             | 80             | 60      | 80      | 60      | 80      |        |          |         |        |        |        |        |        |         |        |

| θ77               | 59             | 81             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| 078               | 58             | 82             | 58      | 82      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ79               | 57             | 82             |         |         |         |         |        |          |         |        |        |        |        |        |         |        |

| 080               | 56             | 83             | 56      | 83      | 56      | 83      | 56     | 83       | 56      | 83     |        |        |        |        |         | ļ      |

| 081               | 55             | 84             |         |         |         |         |        | <u> </u> |         |        |        |        |        |        |         |        |

| 082               | 53             | 84             | 53      | 84      |         |         |        |          |         |        |        |        |        |        |         |        |

| 083               | 52             | 85             |         |         |         |         |        |          |         |        |        |        |        |        |         | ļ      |

| 084               | 51             | 86             | 51      | 86      | 51      | 86      |        |          |         |        |        |        |        |        |         | ļ      |

| 085               | 50             | 86             |         |         |         |         |        |          |         |        |        |        |        |        |         | ļ      |

| 086               | 49             | 87             | 49      | 87      |         |         |        |          |         |        |        |        |        |        |         |        |

| θ87               | 48             | 88             | 47      | 00      | 47      |         | 4-     | 00       |         |        |        |        |        |        |         |        |

| 000               | 4              |                |         | 88      | 47      | 88      | 47     | 88       |         | 1      |        | 1      | 1      | 1      |         |        |

| 088               | 47             | 88             | 47      | 00      | 7/      | 00      |        | 00       |         |        |        |        |        |        |         |        |

| 088<br>089<br>090 | 47<br>46<br>45 | 88<br>89<br>89 | 47      | 89      | 47      |         |        |          |         |        |        |        |        |        |         |        |

Continued on next page

| Continu         | ued from   | precedi | ng page       |     |               |     |               |     |              |     |              |     |               |     |               |     |

|-----------------|------------|---------|---------------|-----|---------------|-----|---------------|-----|--------------|-----|--------------|-----|---------------|-----|---------------|-----|

| STEP            | 1/128 step |         | 1/64 step (%) |     | 1/32 step (%) |     | 1/16 step (%) |     | 1/8 step (%) |     | 1/4 step (%) |     | Half step (%) |     | Full step (%) |     |

| SIEP            | 1ch        | 2ch     | 1ch           | 2ch | 1ch           | 2ch | 1ch           | 2ch | 1ch          | 2ch | 1ch          | 2ch | 1ch           | 2ch | 1ch           | 2ch |

| θ91             | 44         | 90      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| <del>0</del> 92 | 43         | 90      | 43            | 90  | 43            | 90  |               |     |              |     |              |     |               |     |               |     |

| θ93             | 42         | 91      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| <del>0</del> 94 | 41         | 91      | 41            | 91  |               |     |               |     |              |     |              |     |               |     |               |     |

| θ95             | 39         | 92      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ96             | 38         | 92      | 38            | 92  | 38            | 92  | 38            | 92  | 38           | 92  | 38           | 92  |               |     |               |     |

| <del>0</del> 97 | 37         | 93      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| <del>0</del> 98 | 36         | 93      | 36            | 93  |               |     |               |     |              |     |              |     |               |     |               |     |

| 699             | 35         | 94      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ100            | 34         | 94      | 34            | 94  | 34            | 94  |               |     |              |     |              |     |               |     |               |     |

| θ101            | 33         | 95      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ102            | 31         | 95      | 31            | 95  |               |     |               |     |              |     |              |     |               |     |               |     |

| θ103            | 30         | 95      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ104            | 29         | 96      | 29            | 96  | 29            | 96  | 29            | 96  |              |     |              |     |               |     |               |     |

| θ105            | 28         | 96      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ106            | 27         | 96      | 27            | 96  |               |     |               |     |              |     |              |     |               |     |               |     |

| θ107            | 25         | 97      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ108            | 24         | 97      | 24            | 97  | 24            | 97  |               |     |              |     |              |     |               |     |               |     |

| θ109            | 23         | 97      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ110            | 22         | 98      | 22            | 98  |               |     |               |     |              |     |              |     |               |     |               |     |

| θ111            | 21         | 98      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ112            | 20         | 98      | 20            | 98  | 20            | 98  | 20            | 98  | 20           | 98  |              |     |               |     |               |     |

| θ113            | 18         | 98      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ114            | 17         | 99      | 17            | 99  |               |     |               |     |              |     |              |     |               |     |               |     |

| θ115            | 16         | 99      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ116            | 15         | 99      | 15            | 99  | 15            | 99  |               |     |              |     |              |     |               |     |               |     |

| θ117            | 13         | 99      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ118            | 12         | 99      | 12            | 99  |               |     |               |     |              |     |              |     |               |     |               |     |

| θ119            | 11         | 99      |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ120            | 10         | 100     | 10            | 100 | 10            | 100 | 10            | 100 |              |     |              |     |               |     |               |     |

| θ121            | 9          | 100     |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ122            | 7          | 100     | 7             | 100 |               |     |               |     |              |     |              |     |               |     |               |     |

| θ123            | 6          | 100     |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ124            | 5          | 100     | 5             | 100 | 5             | 100 |               |     |              |     |              |     |               |     |               |     |

| θ125            | 4          | 100     |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ126            | 2          | 100     | 2             | 100 |               |     |               |     |              |     |              |     |               |     |               |     |

| θ127            | 1          | 100     |               |     |               |     |               |     |              |     |              |     |               |     |               |     |

| θ128            | 0          | 100     | 0             | 100 | 0             | 100 | 0             | 100 | 0            | 100 | 0            | 100 | 0             | 100 |               |     |

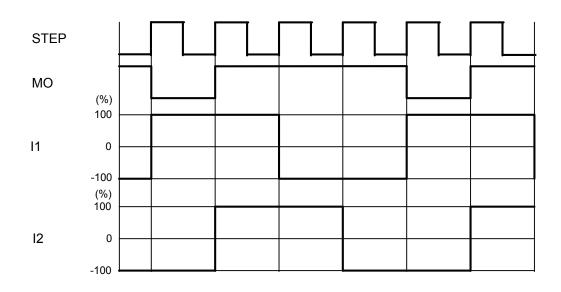

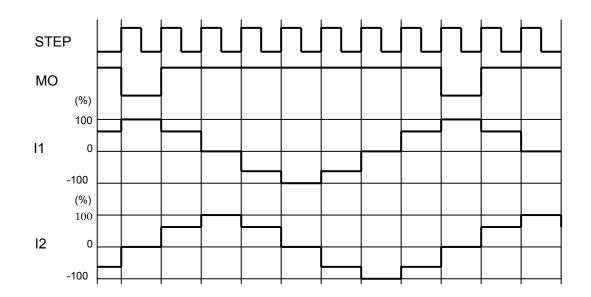

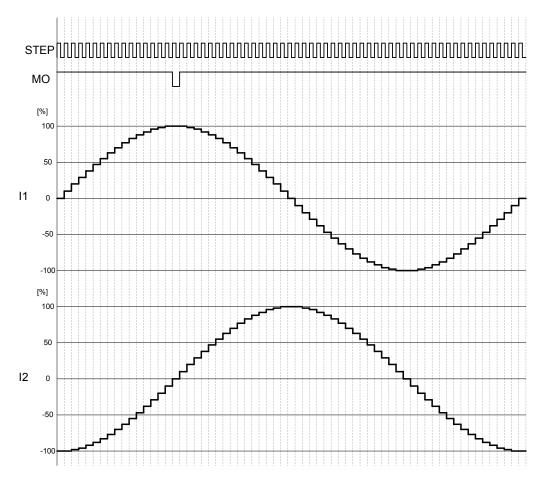

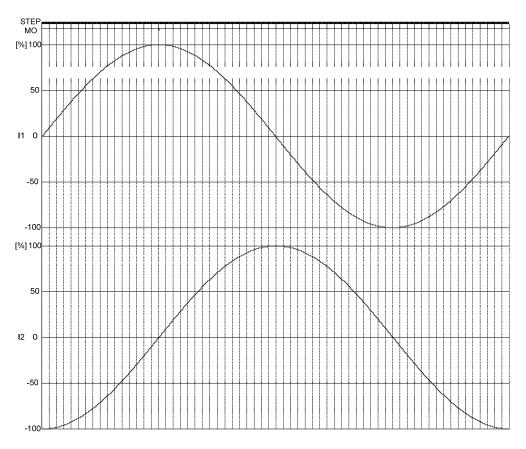

#### 17. Current wave example in each excitation mode (Full, Half, 1/16, 1/128 step)

Full step (CW mode)

Half step (CW mode)

<sup>1/128</sup> step (CW mode)

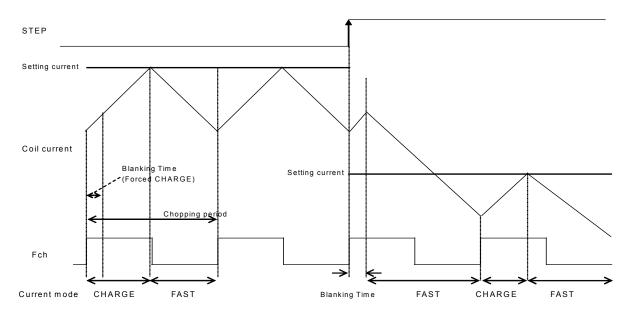

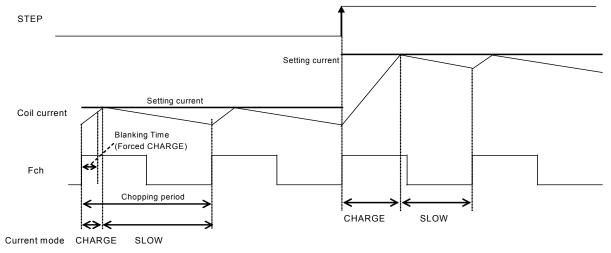

#### 18. Current control operation

FAST Decay current control: When FDT pin voltage is 0.8V or less, the constant- current control is

operated in FAST Decay mode.

#### (Sine-wave decreasing direction)

The current control of FAST Decay operates with the follow sequence.

- The IC enters CHARGE mode at a rising edge of the chopping oscillation. The CHARGE of the blanking time is forced regardless of the magnitude of the coil current (ICOIL) and set current (IREF). The blanking time is approximately 1µs.

- After the period of the blanking time, The IC operates in CHARGE mode until ICOIL ≥ IREF.

After that, the mode switches to the FAST Decay

mode and the coil current is attenuated until the end of a chopping period.

• If ICOIL > IREF state exists when the end of blanking time, the coil current is attenuated by the FAST Decay mode until the end of a chopping period.

Since the attenuation of the current is fast, it is early that the coil current follows the set current. However, the current ripple value may be higher.

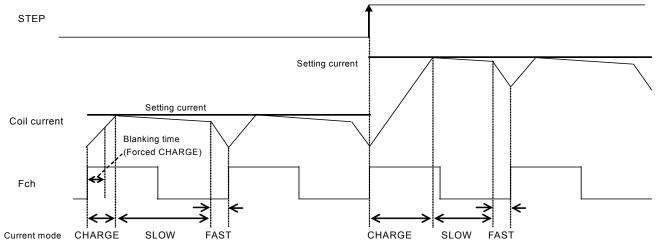

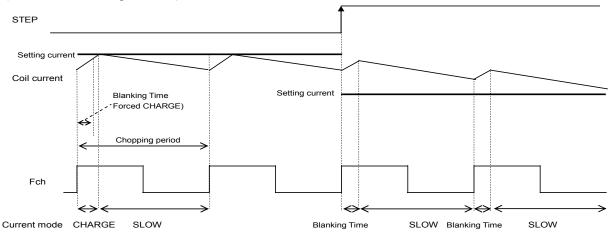

MIXED Decay current control: When FDT pin voltage is between 1.1V and 3.1V or Open, the

constant- current control is operated in MIXED Decay mode.

(Sine-wave increasing direction)

The current control of MIXED Decay operates with the follow sequence.

- The IC enters CHARGE mode at a rising edge of the chopping oscillation. The CHARGE of the blanking time is forced regardless of the magnitude of the coil current (ICOIL) and set current (IREF). The blanking time is approximately 1µs.

- In a period of Blanking Time, the coil current (ICOIL) and the setting current (IREF) are compared.

If an ICOIL < IREF state exists during the charge period:

The IC operates in CHARGE mode until ICOIL  $\geq$  IREF. After that, it switches to SLOW DECAY mode and then switches to FAST DECAY mode in the last approximately 1µs of the period.

If no ICOIL < IREF state exists during the charge period:

The IC switches to FAST DECAY mode and the coil current is attenuated with the FAST DECAY operation until the end of a chopping period.

The above operation is repeated. Normally, the IC operates in SLOW (+ FAST) Decay mode at the sine wave increasing direction, and the IC operates in FAST Decay mode at the sine wave decreasing direction until the current is attenuated. And then the IC operates in SLOW Decay mode when the current reaches the set value.

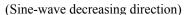

SLOW Decay current control: When FDT pin voltage is 3.5V or more, the constant- current control is

operated in SLOW Decay mode.

(Sine-wave increasing direction)

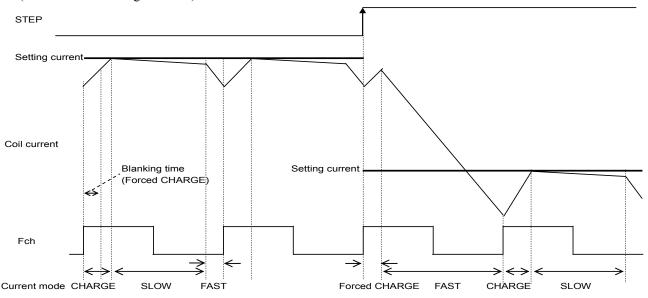

#### (Sine-wave decreasing direction)

The current control of SLOW Decay operates with the follow sequence.

- The IC enters CHARGE mode at a rising edge of the chopping oscillation. The CHARGE of the blanking time is forced regardless of the magnitude of the coil current (ICOIL) and set current (IREF). The blanking time is approximately 1µs.

- After the period of the blanking time, The IC operates in CHARGE mode until ICOIL ≥ IREF. After that, the mode switches to the SLOW Decay mode and the coil current is attenuated until the end of a chopping period.

- If ICOIL > IREF state exists when the end of blanking time, the coil current is attenuated by the SLOW Decay mode until the end of a chopping period.

Since the attenuation of the current is slow, it may be slow that the coil current follows the set current. Or the coil current may not follow a set current.

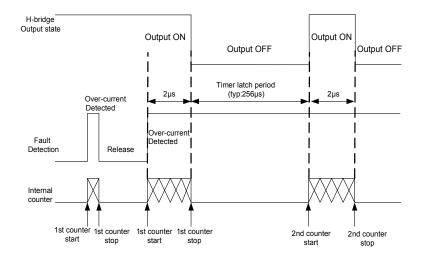

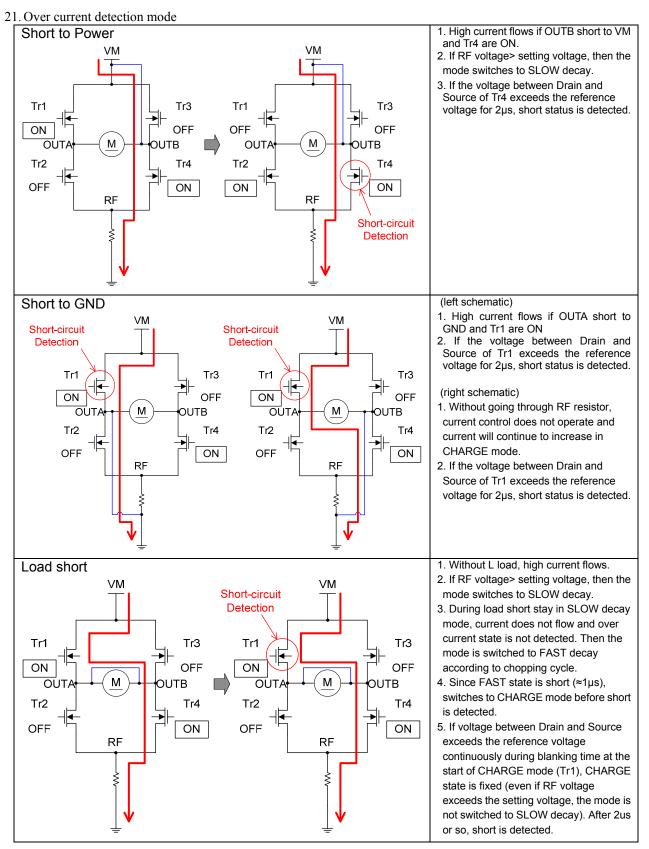

#### 19. Over-current protection function

This IC incorporates an over current protection circuit that, when the output has been shorted by an event such as shorting to power, shorting to ground and shorting to other output. And it switches the output to the standby mode in order to prevent the IC from being damaged. Three over-current detection modes are shown in the next page. When the over current is detected, the over current protection circuit operates. If the short status continues for the period of internal timer ( $\approx 2\mu s$ ), the output of 1 ch/ 2ch is turned off. If the short status exceeds the timer latch time ( $\approx 256us$ ) set in the internal timer, the output is turned on again and detects short status again. If short is detected again, all the outputs of 1 ch/ 2ch are switched to standby mode and the status is kept. To cancel the standby status, set ST="L".

20. Thermal shutdown function

The thermal shutdown circuit is incorporated and the output is turned Off when junction temperature Tj exceeds 180°C. As the temperature falls by hysteresis, the output turned on again (automatic restoration). The thermal shutdown circuit does not guarantee the protection of the final product because it operates when the temperature exceed the junction temperature of  $Tjmax=150^{\circ}C$ .

$TSD = 180^{\circ}C (typ)$  $\Delta TSD = 40^{\circ}C (typ)$

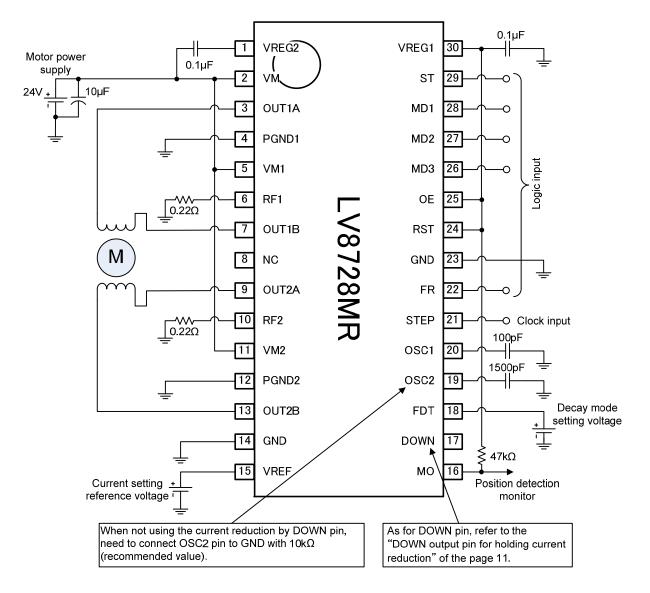

#### **Application Circuit Example**

Calculation for each constant setting according to the above circuit diagram is as follows. For example, when VREF=1.1V, IOSC1=10uA (typ) and COSC1=100pF

• Coil current

$$I_{OUT} = \frac{1.1}{5 \times 0.22} \approx 1.0 \ [A]$$

• Chopping frequency

$$Fch = \frac{10 \times 10^{-6}}{100 \times 10^{-12}} = 100 \ [kHz]$$

- STEP signal off detection time

- $T_{DOWN} = 1500 \times 10^{-12} \times 0.4 \times 10^{9}$ = 0.6 [Sec]

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf//Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or dath associa