# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# SANYO Semiconductors DATA SHEET

An ON Semiconductor Company

**Bi-CMOS IC** LV8827LF — For Brushless Motor Drive **PWM Driver IC**

# **Overview**

The LV8827LF is a PWM-type driver IC designed for 3-phase brushless motors. The rotational speed can be controlled by inputting the PWM pulse from the outside, and changing Duty. The IC incorporates a latch-type constraint protection circuit.

# Features

- $I_{O}$  max = 1.5A (built-in output Tr)

- Speed control and synchronous rectification using direct PWM input (supports 3.3V inputs)

- 1-Hall FG output

- Latch type constraint protection circuit (the latch is released by S/S and F/R.)

- Forward/reverse switching circuit, Hall bias pin

- Power save circuit (Power save in stop mode)

- Current limiter circuit, Low-voltage protection circuit, Overheat protection circuit

- Charge pump circuit, 5V regulator output.

- Start/stop circuit (short brake when motor is to be stopped)

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co., Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

SANYO Semiconductor Co., Ltd. http://semicon.sanyo.com/en/network

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions                    | Ratings     | Unit |

|-----------------------------|---------------------|-------------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max | V <sub>CC</sub> pin           | 36          | V    |

|                             | V <sub>G</sub> max  | V <sub>G</sub> pin            | 42          | V    |

| Output current              | I <sub>O</sub> max  | t ≤ 500ms *1                  | 1.5         | А    |

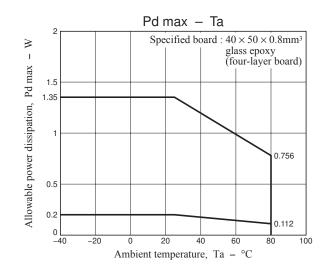

| Allowable power dissipation | Pd max1             | Independent IC                | 0.2         | W    |

|                             | Pd max2             | Mounted on a circuit board.*2 | 1.35        | W    |

| Junction temperature        | Tj max              |                               | 150         | °C   |

| Operating temperature       | Topr                |                               | -40 to +80  | °C   |

| Storage temperature         | Tstg                |                               | -55 to +150 | °C   |

\*1 : Tj cannot exceed Tj max = 150°C \*2 : Specified circuit board : 40mm × 50mm × 0.8mm, glass epoxy (four-layer board)

## Allowable Operating range at $Ta = 25^{\circ}C$

| Parameter                          | Symbol          | Conditions | Ratings   | Unit |

|------------------------------------|-----------------|------------|-----------|------|

| Supply voltage range               | V <sub>CC</sub> |            | 8.0 to 35 | V    |

| 5V constant voltage output current | IREG            |            | 0 to -10  | mA   |

| HB pin output current              | I <sub>HB</sub> |            | 0 to -200 | μA   |

| FG pin applied voltage             | V <sub>FG</sub> |            | 0 to 6    | V    |

| FG pin output current              | I <sub>FG</sub> |            | 0 to 10   | mA   |

# Electrical Characteristics at Ta = $25^{\circ}$ C, V<sub>CC</sub> = 24V

| Parameter Symbol                     |                       | Conditions                                   | Ratings |                      |          | Unit  |

|--------------------------------------|-----------------------|----------------------------------------------|---------|----------------------|----------|-------|

| Parameter                            | Symbol                | Conditions                                   | min     | typ                  | max      | Unit  |

| Supply current 1                     | ICC1                  |                                              |         | 3.3                  | 4.0      | mA    |

| Supply current 2                     | I <sub>CC</sub> 2     | At stop                                      |         | 0.7                  | 0.8      | mA    |

| Output block                         |                       |                                              |         |                      |          |       |

| Low-side output ON resistance        | R <sub>ON</sub> (L1)  | I <sub>O</sub> = 1.0A                        |         | 0.47                 | 0.65     | Ω     |

| High-side output ON resistance       | R <sub>ON</sub> (H1)  | I <sub>O</sub> = -1.0A                       |         | 0.67                 | 0.9      | Ω     |

| Low-side output leak current         | I_ (L)                |                                              |         |                      | 50       | μA    |

| High-side output leak current        | I <sub>L</sub> (Н)    |                                              | -50     |                      |          | μA    |

| Low-side diode forward voltage       | V <sub>D</sub> (L1)   | I <sub>D</sub> = -1.0A                       |         | 1.0                  | 1.2      | V     |

| High-side diode forward voltage      | V <sub>D</sub> (H1)   | I <sub>D</sub> = 1.0A                        |         | 1.1                  | 1.3      | V     |

| 5V Constant-voltage Output           |                       |                                              |         |                      |          |       |

| Output voltage                       | VREG                  | I <sub>O</sub> = -5mA                        | 4.8     | 5.1                  | 5.4      | V     |

| Line regulation                      | ∆V (REG1)             | $V_{CC} = 8.0$ to 35V, $I_{O} = -5mA$        |         |                      | 50       | mV    |

| Load regulation                      | ΔV (REG2)             | I <sub>O</sub> = -5m to -10mA                |         |                      | 100      | mV    |

| Hall Amplifier                       |                       |                                              |         |                      |          |       |

| Input bias current                   | IB (HA)               |                                              | -2      |                      |          | μA    |

| Common-mode input voltage range 1    | VICM1                 | When using Hall elements                     | 0.3     |                      | VREG-1.7 | V     |

| Common-mode input voltage range 2    | VICM2                 | At one-side input bias (Hall IC application) | 0       |                      | VREG     | V     |

| Hall input sensitivity               | VHIN                  | SIN wave                                     | 80      |                      |          | mVp-p |

| Hysteresis width                     | $\Delta V_{IN}$ (HA)  |                                              | 9       | 20                   | 35       | mV    |

| Input voltage Low $\rightarrow$ High | VSLH                  |                                              | 3       | 9                    | 16       | mV    |

| Input voltage High $\rightarrow$ Low | VSHL                  |                                              | -19     | -11                  | -5       | mV    |

| CSD oscillator circuit               |                       |                                              |         |                      |          |       |

| High level output voltage            | V <sub>OH</sub> (CSD) |                                              | 2.7     | 3.0                  | 3.3      | V     |

| Low level output voltage             | V <sub>OL</sub> (CSD) |                                              | 0.9     | 1.1                  | 1.3      | V     |

| Amplitude                            | V (CSD)               |                                              | 1.6     | 1.9                  | 2.2      | Vp-р  |

| External capacitor charge current    | ICHG1 (CSD)           | VCHG1 = 2.0V                                 | -14     | -11.5                | -9       | μA    |

| External capacitor discharge current | ICHG2 (CSD)           | VCHG2 = 2.0V                                 | 9.5     | 12                   | 14.5     | μA    |

| Oscillation frequency                | f (CSD)               | C = 0.022µF (Design target value)            |         | 130                  |          | Hz    |

| Charge pump output (VG pin)          |                       | I                                            |         |                      |          | -     |

| Output voltage                       | VGOUT                 |                                              |         | V <sub>CC</sub> +4.5 |          | V     |

No.A1865-2/13

| Parameter                              | Symbol                 | Conditions                                  |          | Ratings  |          | Unit |

|----------------------------------------|------------------------|---------------------------------------------|----------|----------|----------|------|

|                                        | Cymbol                 | Conditions                                  | min      | typ      | max      | 0111 |

| CP1 pin                                |                        |                                             |          |          |          |      |

| Output ON resistance (High level)      | V <sub>OH</sub> (CP1)  | ICP1 = -2mA                                 |          | 500      | 700      | Ω    |

| Output ON resistance (Low level)       | V <sub>OL</sub> (CP1)  | ICP1 = 2mA                                  |          | 350      | 500      | Ω    |

| Charge pump frequency                  | f (CP)                 |                                             | 82       | 103      | 124      | kHz  |

| Internal PWM frequency                 | I                      | 11                                          |          |          |          |      |

| Oscillation frequency                  | f (PWM)                |                                             | 41       | 51.5     | 62       | kHz  |

| Current limiter operation              | -                      | · · · · · · · · · · · · · · · · · · ·       |          | r        |          |      |

| Limiter voltage                        | VRF                    |                                             | 0.19     | 0.21     | 0.23     | V    |

| Thermal shutdown operation             |                        |                                             |          |          |          |      |

| Thermal shutdown operation temperature | TSD                    | *Design target value (junction temperature) | 150      | 165      | 180      | °C   |

| Hysteresis width                       | ΔTSD                   | *Design target value (junction temperature) |          | 30       |          | °C   |

| HB pin                                 | ·                      | ·                                           |          |          | -        |      |

| Output voltage                         | VHB                    | IHB = -100μA                                | 3.4      | 3.6      | 3.8      | V    |

| Low-voltage protection (5V constan     | t-voltage output d     | etection)                                   |          |          |          |      |

| Operation voltage                      | VSD                    |                                             | 3.95     | 4.15     | 4.35     | V    |

| Hysteresis width                       | ΔVSD                   |                                             | 0.2      | 0.3      | 0.4      | V    |

| FG pin (3FG pin)                       |                        |                                             |          |          |          |      |

| Output ON resistance                   | VOL (FG)               | IFG = 5mA                                   |          | 40       | 60       | Ω    |

| Output leak current                    | IL (FG)                | V <sub>O</sub> = 5V                         |          |          | 10       | μA   |

| S/S pin                                |                        |                                             |          |          |          |      |

| High level input voltage               | V <sub>IH</sub> (SS)   |                                             | 2.0      |          | VREG     | V    |

| Low level input voltage                | V <sub>IL</sub> (SS)   |                                             | 0        |          | 1.0      | V    |

| Input open voltage                     | V <sub>IO</sub> (SS)   |                                             | VREG-2.2 | VREG-2.0 | VREG-1.8 | V    |

| Hysteresis width                       | V <sub>IS</sub> (SS)   |                                             | 0.25     | 0.33     | 0.4      | V    |

| High level input current               | I <sub>IH</sub> (SS)   | V <sub>SS</sub> = VREG                      | 45       | 60       | 75       | μA   |

| Low level input current                | I <sub>IL</sub> (SS)   | $V_{SS} = 0V$                               | -115     | -90      | -65      | μA   |

| PWMIN pin                              |                        |                                             |          |          |          |      |

| Recommended input frequency            | F (PWIN)               |                                             | 0.5      |          | 60       | kHz  |

| High level input voltage               | V <sub>IH</sub> (PWIN) |                                             | 2.0      |          | VREG     | V    |

| Low level input voltage                | V <sub>IL</sub> (PWIN) |                                             | 0        |          | 1.0      | V    |

| Input open voltage                     | V <sub>IO</sub> (PWIN) |                                             | VREG-2.2 | VREG-2.0 | VREG-1.8 | V    |

| Hysteresis width                       | V <sub>IS</sub> (PWIN) |                                             | 0.25     | 0.33     | 0.4      | V    |

| High level input current               | I <sub>IH</sub> (PWIN) | VPWIN = VREG                                | 45       | 60       | 75       | μA   |

| Low level input current                | IIL (PWIN)             | VPWIN = 0V                                  | -115     | -90      | -65      | μA   |

| F/R pin                                |                        |                                             |          |          |          |      |

| High level input voltage               | V <sub>IH</sub> (FR)   | *Design target value                        | 2.0      |          | VREG     | V    |

| Low level input voltage                | V <sub>IL</sub> (FR)   | *Design target value                        | 0        |          | 1.0      | V    |

| Input open voltage                     | V <sub>IO</sub> (FR)   |                                             | VREG-2.2 | VREG-2.0 | VREG-1.8 | V    |

| Hysteresis width                       | V <sub>IS</sub> (FR)   | *Design target value                        | 0.25     | 0.33     | 0.4      | V    |

| High level input current               | I <sub>IH</sub> (FR)   | VF/R = VREG                                 | 45       | 60       | 75       | μA   |

| Low level input current                | I <sub>IL</sub> (FR)   | VF/R = 0V                                   | -115     | -90      | -65      | μΑ   |

$^{\star}$  : Design target value and no measurement is made.

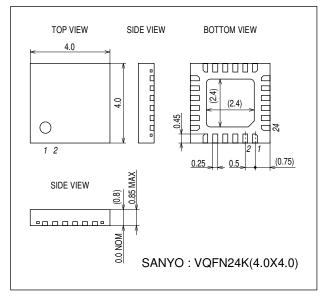

# Package Dimensions

unit : mm (typ) 3400

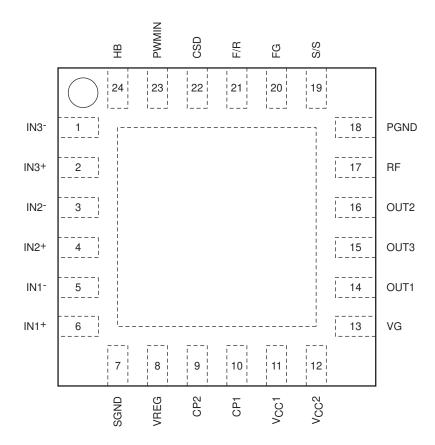

# **Pin Assignment**

# LV8827LF

|     |           | -g.e |     | (11, 115   | ii iiiaicatet | , the state w |             |             |                      |

|-----|-----------|------|-----|------------|---------------|---------------|-------------|-------------|----------------------|

|     |           |      |     | ("H" = SOU | URCE, "L"     | = SINK, an    | d "M" = out | put OFF are | e shown with OUT1 to |

|     | F/R = [H] |      |     | F/R = [L]  |               |               | Output      |             |                      |

| IN1 | IN2       | IN3  | IN1 | IN2        | IN3           | OUT1          | OUT2        | OUT3        |                      |

| Н   | L         | Н    | L   | Н          | L             | L             | Н           | М           |                      |

| Н   | L         | L    | L   | н          | Н             | L             | М           | Н           |                      |

| Н   | Н         | L    | L   | L          | Н             | М             | L           | Н           | 1                    |

| L   | Н         | L    | Н   | L          | Н             | Н             | L           | М           | 1                    |

| L   | Н         | н    | Н   | L          | L             | Н             | М           | L           |                      |

| L   | L         | Н    | Н   | н          | L             | М             | н           | L           |                      |

# Three-phase logic truth table (IN = "High" indicates the state where IN+ > IN-.)

| L   | П   | П   | п      | L |

|-----|-----|-----|--------|---|

| L   | L   | Н   | Н      | Н |

|     |     |     |        |   |

|     | F/R |     | Output |   |

| IN1 | IN2 | IN3 | FG     |   |

| Н   | L   | Н   | L      |   |

| Н   | L   | L   | L      |   |

| Н   | Н   | L   | L      |   |

| L   | Н   | L   | Н      |   |

| L   | Н   | Н   | Н      |   |

| L   | L   | Н   | Н      |   |

# S/S pin, PWMIN pin

| Input state  | S/S pin            | PWMIN pin  |

|--------------|--------------------|------------|

| High or Open | Stop (short brake) | Output OFF |

| Low          | Start              | Output ON  |

CSD function

When the S/S pin is in a STOP state When the F/R pin is switched

When 0% duty is detected at the PWMIN pin input  $\rightarrow$

When low-voltage condition is detected

When TSD condition is detected

$\rightarrow$  Protection released and count reset (Initial reset)

$\rightarrow$  Protection released and count reset

Protection released and count reset

$\rightarrow$ Protection released and count reset (Initial reset)

Stop counting  $\rightarrow$

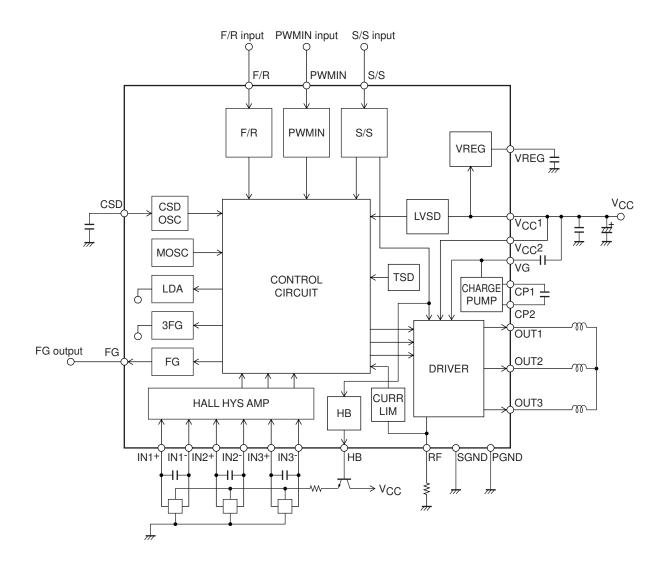

# Internal Equivalent Circuit and Sample External Component Circuit

# Pin Functions

| Pin No.                    | Pin Name                                                                                                             | Pin function                                                                                                                                                                                                                                                                                                                | Equivalent Circuit                                         |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6 | IN3 <sup>-</sup><br>IN3 <sup>+</sup><br>IN2 <sup>-</sup><br>IN2 <sup>+</sup><br>IN1 <sup>-</sup><br>IN1 <sup>+</sup> | Hall input pin.<br>•High when IN <sup>+</sup> > IN <sup>-</sup> .<br>Low in reverse relationship.<br>The input amplitude of over 100mVp-p<br>(differential) is desirable in the Hall<br>inputs. Insert a capacitor between the<br>IN <sup>+</sup> and IN <sup>-</sup> pins if the noise on the Hall<br>signal is a problem. | VREG<br>135<br>5000<br>5000<br>5000<br>5000<br>5000<br>246 |

| 7                          | SGND                                                                                                                 | Control circuit block ground pin.                                                                                                                                                                                                                                                                                           |                                                            |

| 8                          | VREG                                                                                                                 | 5V regulator output pin (control circuit<br>power supply).<br>Insert a capacitor between this pin and<br>ground for stabilization.<br>About 0.1μF is necessary.                                                                                                                                                             | V <sub>CC</sub>                                            |

| 9                          | CP2                                                                                                                  | Charge pump capacitor connection pin.                                                                                                                                                                                                                                                                                       |                                                            |

| 10<br>11                   | CP1<br>V <sub>CC</sub> 1                                                                                             | Insert capacitor between CP1 and CP2.<br>Control power pin.<br>Insert a capacitor between this pin and<br>ground to prevent the influence of noise,<br>etc.                                                                                                                                                                 |                                                            |

| 12                         | V <sub>CC</sub> 2                                                                                                    | Output power pin.<br>Insert a capacitor between this pin and<br>ground to prevent the influence of noise,<br>etc.                                                                                                                                                                                                           |                                                            |

| 13                         | VG                                                                                                                   | Charge pump output pin.<br>(Upper-side FET gate power supply)<br>Insert a capacitor between this pin and<br>V <sub>CC</sub> .                                                                                                                                                                                               | $V_{CC}$                                                   |

Continued on next page.

| Continued from | m preceding page.    | I                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.        | Pin Name             | Pin function                                                                                           | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14<br>15<br>16 | OUT1<br>OUT3<br>OUT2 | Output pin.<br>PWM is controlled by the upper-side<br>FET.                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17             | RF                   | Output current detection pin.<br>Insert a low resistance resistor (Rf)<br>between this pin and ground. | VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18             | PGND                 | Out circuit block ground pin.                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19             | S/S                  | Pin to select the start/stop type.<br>Stop = High or open<br>Start = Low                               | VREG<br>$50k\Omega \leq 5k\Omega$<br>$75k\Omega \leq 75k\Omega \leq 775k\Omega < 775k\Omega \leq 775k\Omega \leq 775k\Omega < 775k\Omega \leq 775k\Omega \leq 775k\Omega \leq 775k\Omega \leq 775k\Omega < 775k\Omega \leq 775k\Omega < 77$ |

| 20             | FG                   | FG signal output pin.<br>1-Hall FG (IN1).<br>Open drain output.                                        | VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Continued on next page.

| Continued from | n preceding page. |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.        | Pin Name          | Pin function                                                                                                                                                                                                                                         | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21             | F/R               | Pin to select the forward/reverse type.<br>This pin goes to the high level when<br>open.                                                                                                                                                             | VREG<br>50kΩ \$<br>50kΩ \$<br>5kΩ (21)<br>75kΩ \$<br>75kΩ |

| 22             | CSD               | Pin to set the constraint protection circuit<br>operating time and initial reset pulse.<br>Insert a capacitor between this pin and<br>ground.<br>Insert a resistor in parallel with the<br>capacitor if the protection circuit is not to<br>be used. | VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23             | PWMIN             | External PWM input pin.<br>Apply an external PWM input signal to<br>this pin.<br>(Input frequency range is from 0.5 to<br>60kHz.)<br>PWM ON = Low<br>PWM OFF = High or open                                                                          | VREG<br>50kΩ \$<br>50kΩ \$<br>50kΩ \$<br>75kΩ 23<br>75kΩ 7<br>75kΩ 7                                                                                                                                                                                                                                                          |

| 24             | НВ                | HALL bias pin (3.6V output).<br>Connect an NPN transistor.<br>(See "5 Hall Input Signal.")                                                                                                                                                           | VREG<br>2500<br>(24)<br>(24)<br>(24)<br>(24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Description of LV8827LF

#### 1. Output Drive Circuit

This IC adopts a direct PWM drive method to reduce power loss in the output. It regulates the drive force of the motor by changing the output on duty. The output PWM switching is performed by the upper-side output transistor. The current regeneration route during the normal PWMOFF passes through the parasitic diode of the output DMOS. This IC performs synchronous rectification, and is intended to reduce heat generation compared to diode regeneration.

#### 2. Current Limiter Circuit

The current limiter circuit limits the output current peak value to a level determined by the equation  $I = V_{RF}/Rf(V_{RF} = 0.21V$  (typical), Rf: current detection resistor). This circuit suppresses the output current by reducing the output on duty.

The current limiter circuit has an operation delay (approx. 700ns) to detect reverse recovery current flowing in the diode due to the PWM operation, and prevent a malfunction of the current limiting operation. If the coil resistance of the motor is small, or the inductance is low, the current at startup (the state in which there is no back electromotive force generated in the motor) will change rapidly. As a result, the operation delay may sometimes cause the current limiting operation to take place at a value above the set current. In such a case, it is necessary to set the current limit value while taking into consideration the increase in current due to the delay.

\* Regarding the PWM frequency in the current limiter circuit

The PWM frequency in the current limiter circuit is determined by the internal reference oscillator, and is approximately 50kHz.

#### 3. Speed control method

Pulses are input to the PWMIN pin, and the output can be controlled by varying the duty cycle of these pulses. When a low-level input voltage is applied to the PWMIN pin, the output at the PWM side (upper side) is set to ON. When a high-level input voltage is applied to the PWMIN pin, the output at the PWM side (upper side) is set to OFF. If it is necessary to input pulses using inverted logic, this can be done by adding an external transistor (NPN). It is judged Duty=0%, count reset and the HB pin output of the CSD circuit become "L" when the input of the PWMIN pin becomes "H" level during the fixed time, and it enters the state of a short brake.

#### 4. Constraint Protection Circuit

The LV8827LF includes a constraint protection circuit for protecting the IC and the motor in a motor constraint mode. This circuit operates when the motor is in an operation condition and the Hall signal does not switch over for a certain period. Note that while this constraint protection is operating, the upper-side output transistor will be OFF. Time setting is performed according to the capacitance of the capacitor connected to the CSD pin.

### Set time (s) $\approx$ 90 × C (µF)

When a  $0.022\mu$ F capacitor is connected, the protection time becomes approximately 2.0 seconds. The set time must be selected to a value that provides adequate margin with respect to the motor startup time. Conditions for releasing the constraint protection state:

- When the S/S pin is in a STOP state

- When the F/R pin is switched

- When 0% duty is detected at the PWMIN pin input  $\rightarrow$

- When low-voltage condition is detected

- (• When TSD condition is detected

- → Protection released and count reset(Initial reset)

- $\rightarrow$  Protection released and count reset

- → Protection released and count reset

- $\rightarrow$  Protection released and count reset (Initial reset)

- $\rightarrow$  Stop counting)

The CSD pin also functions as the initial reset pulse generation pin. If it is connected to ground, the logic circuit will go into a reset state, preventing speed control from taking place. Consequently, when not using constraint protection, connect a resistor of approximately  $220k\Omega$  and a capacitor of about 4700pF in parallel to ground.

5. Hall Input Signal

A pulse input with the amplitude in excess of the hysteresis (35mV maximum) is required for the Hall inputs.

It is desirable that the amplitude of the Hall input signal be 100mVp-p or more in consideration of the effect of noise and phase displacement.

If disturbances to the output waveform (during phase switching) occur due to noise, connect a capacitor between the Hall input pins to prevent such disturbances. In the constraint protection circuit, the Hall input is utilized as a judgment signal. Although the circuit ignores a certain amount of noise, caution is necessary.

If all three phases of the Hall input signal go to the same input state (HHH or LLL), the outputs are all set to the OFF state.

If the Hall IC is used, fixing one side of the inputs (either the + or - side) at a voltage within the common-mode input voltage range (between 0.3V and VREG-1.7V) allows the other input side to be used as an input over the 0V to VREG range.

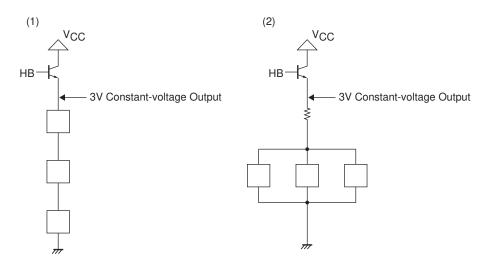

• Method of connecting Hall elements

Type (1) connection (three Hall elements connected in series)

Advantages

- Because the current flowing in Hall elements can be shared by connecting the Hall elements in series, the current consumption is less than that of a parallel-connected arrangement.

- The use of a current limiting resistor can be eliminated.

- Fluctuations of amplitude with temperature are reduced.

Disadvantages

- Because only 1V can be applied to one Hall device, there is a possibility that adequate amplitude cannot be obtained.

- The current flowing in the Hall elements varies with temperature.

Type (2) connection (three Hall elements connected in parallel)

Advantages

• The current flowing in the Hall elements can be determined by the current limiting resistor.

• The voltage applied to the Hall elements can be varied, enabling adequate amplitude to be obtained.

Disadvantages

- Because it is necessary to supply current separately to each Hall element, the current consumption becomes large.

- A current limiting resistor is necessary.

- The amplitude varies with temperature.

• HB pin

The HB pin is used for cutting off the current flowing in the Hall elements during standby (for saving electricity). The output from the HB pin is set to OFF in the following cases.

- When the S/S pin is in a STOP state

- When 0% duty is detected at the PWMIN pin input

## 6. Power Saving Circuit (Start/Stop circuit)

To save power when the LV8827LF is in the stop state, most of the circuit is stopped, aiming at reducing current consumption. If the Hall bias pin is used, the current consumption in the power-saving mode will be approximately  $700\mu$ A. Even in the power-saving mode, a 5V regulator voltage is output. Also, in the power-saving mode, the IC is in a short break state. (lower-side shorted)

#### 7. Power Supply Stabilization

This IC generates a large output current, and employs a switching drive method, so the power supply line level can be disturbed easily. For this reason, it is necessary to connect a capacitor (electrolytic) of sufficient capacitance between the V<sub>CC</sub> pin and ground to ensure a stable voltage. Connect the ground side of the capacitor to the PGND pin, which is the power ground, as close as possible to the pin. If it is not possible to connect a capacitor of sufficiently large capacitance close to the pin, connect a ceramic capacitor of approximately  $0.1 \mu$ F to the vicinity of the pin. If diodes are inserted in the power supply line to prevent IC destruction resulting from reverse-connecting the power supply, the power supply lines are even more easily disrupted. And even larger capacitor is required.

#### 8. VREG Stabilization

To stabilize the VREG voltage, which is the power supply for the control circuit, connect a capacitor of  $0.1\mu$ F or larger. Connect the ground of this capacitor as close as possible to the control block ground (SGND pin) of the IC.

## 9. Charge pump Circuit

The voltage is stepped-up by the charge pump circuit, causing the gate voltage of the upper-side output FET to be generated. The voltage is stepped-up by capacitor CP connected between pins CP1 and CP2, causing charge to accumulate in capacitor CG connected between pins VG and V<sub>CC</sub>. The capacitance of CP and CG must always satisfy the following relationship.

$CG \ge 4 \times CP$

Charging and discharging of capacitor CP take place based on a frequency of 100kHz. When the capacitance of capacitor CP is large, the current supply capability of power supply VG will increase. However, if the capacitance is too large, the charging and discharging operations will be insufficient. The larger the capacitance of capacitor CG, the more stable voltage VG will become. However, if the capacitance is made too large, the period during which voltage VG is generated when the power is switched ON will become long, so caution is necessary.

The capacitance settings of CP and CG should be the following.

$CP = 0.01 \mu F$  $CG = 0.1 \mu F$

#### 10. Difference point of LV8827LF and LV8829LF

This difference that IC is the more following compared with LV8829LF exists.