Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **PRODUCTION DATA SHEET**

### DESCRIPTION

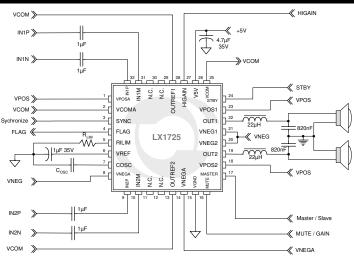

The Microsemi LX1725 is part of a with both split and single power built-in protection typical output power up to 15W+15W channel applications.. in stereo, and 30W BTL into a  $\,4\Omega$ amplifier operates over a wide supply outline surface mount. voltage range of ±6V to ±15V split supply or 12V to 30V single supply, and consumes a very little quiescent

The LX1725 features Mute and new generation of fully integrated Standby modes, over-current protection, amplifiers from POP-free turn-on and turn-off, under-Microsemi. The fully integrated half- voltage lockout, over-voltage protection bridge output for each channel works and over-temperature protection. All supply operation. The outputs can be automatic recovery when the fault bridged to run in BTL (Bridge Tied condition has been cleared. The gain is Load) mode. In BTL mode, 3-level pin selectable between 14 / 20 / 26dB to modulation is used which allow accommodate different signal source operation without an L-C filter to amplitudes. Several LX1725s can be reduce system cost and area. The easily synchronized together to prevent LX1725 has >90% efficiency, with beat frequency interference in multi-

The LX1725 comes in a MLPQ 32 load with less than 1% THD+N. The pin package with a 7mmx7mm small

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com

### **KEY FEATURES**

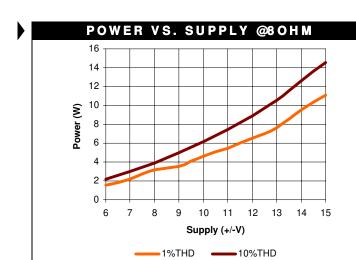

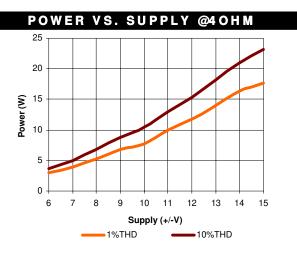

- 12Wx2 @ 4Ω THD+N<1%</li> 16Wx2 @ 4Ω THD+N<10%

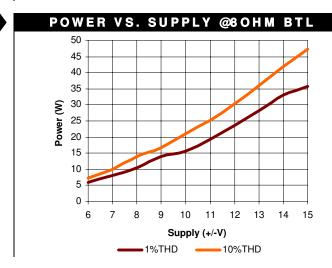

- 25W BTL @ 8Ω THD+N<1% 32W BTL @ 8Ω THD+N<10%

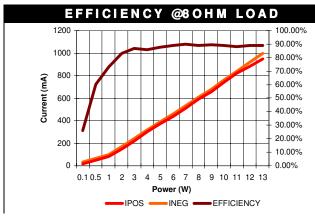

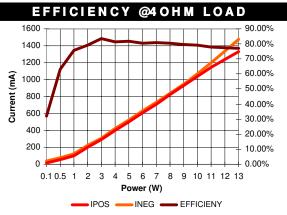

- High Efficiency: >90% @8 $\Omega$

- Full Audio Band: 20Hz~20KHz

- Low Distortion: <0.1% @1KHz, 8Ω <0.4% @20~20KHz. 8Ω

- High Signal-to-Noise Ratio: >85dB non A-Weighted

- Split/Single Power Supply

- Wide Supply Voltage Range: ±6V ~ ±15V or 12V ~ 30V

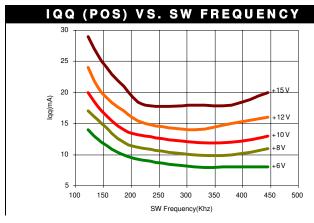

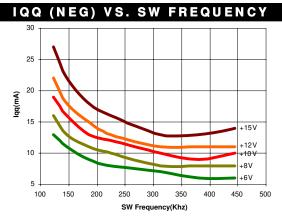

- Low Quiescent Current <20mA

- Turn ON/OFF POP Free

- STANDBY/MUTE Feature

- Programmable Gain 14/20/26dB

- **Built-in Over Current Protection**

- Built-in Under Voltage Lockout

- Thermal Shut Down

- Power Limiting Based on Die Temperature (gain fold back)

- Synchronization

### PRODUCT HIGHLIGHT

#### **APPLICATIONS**

- LCD TV, PDP Sets

- CD/DVD Combo Player

- Combo DVD 5.1 Amplifier

- Home Theater System

- Computer Speaker System

- Game Machine

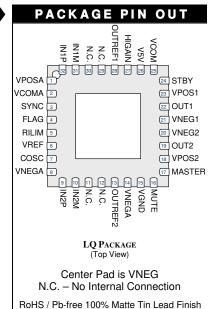

### PACKAGE ORDER INFO **Plastic MLPQ** $T_{J}(^{\circ}C)$ **32-PIN** RoHS Compliant / Pb-free -40 to +85 LX1725ILQ

Note: Available in Tape & Reel. Append the letters "TR" to the part number. (i.e. LX1725ILQ-TR)

#### **PRODUCTION DATA SHEET**

### ABSOLUTE MAXIMUM RATINGS

| C 1 M I (MDOCAMEC MDOCAMMECA) 0.2                            | V. 115V 20V            |

|--------------------------------------------------------------|------------------------|

| Supply Voltage (VPOS/VNEG, VPOSA/VNEGA)                      |                        |

| Common Supply Voltage (VCOM, VCOMA)                          | V to $\pm 15$ V or 30V |

| Analog Supply Voltage (V5V)                                  | 0.3 to 7.0V            |

| Input Voltage (IN1P, IN1M, IN2P, IN2M)                       | 0.3 to 7.0V            |

| Standby and Mute Voltage (STBY, MUTE)                        | 0.3 to 7.0V            |

| Synchronization Input Voltage (MASTER, SYNC)                 | 0.3 to 7.0V            |

| Operating Temperature                                        | 40°C to +85°C          |

| Maximum Operating Junction Temperature                       | 150°C                  |

| Storage Temperature                                          | 65°C to 150°C          |

| Peak Package Solder Reflow Temp.(40 second maximum exposure) |                        |

Note: Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of specified terminal.

### THERMAL DATA

LQ Plastic MLPQ 32-Pin

THERMAL RESISTANCE-JUNCTION TO CASE,  $\theta_{JC}$  1.12°C/W THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{JA}$  15.5°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

| Name  | Description                                                                                                                                                                                                                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPOSA | Analog voltage sense for VPOS voltage. Needs to be protected from noise at VPOS1 and VPOS2. Connect to VPOS bus with appropriate filtering. For VPOSA – VNEGA less than 10V, the under voltage lockout circuit will keep the part in sleep mode. Typically 250µA is drawn at this pin.                                                                                     |

| VCOMA | Analog voltage sense for VCOM voltage. Typically 150μA is drawn at this pin.                                                                                                                                                                                                                                                                                               |

| SYNC  | Bi-directional clock signal pin. In Master mode, this pin outputs the clock to other slave units. In Slave mode, this pin is a clock input. CMOS logic levels.                                                                                                                                                                                                             |

| FLAG  | Monitor point that indicates a fault has been detected. This pin goes high during the power on reset period, when current limiting is in effect, when the voltage at VPOS – VNEG is less than 10V or greater than 33V, when the V5V voltage is less than 4V, and when an over-temperature condition is detected. CMOS logic levels.                                        |

| RILIM | A current limit-programming resistor should be connected between this pin and ground. A $50K\Omega$ resistor will give a 3.75A current limit threshold. This pin may be connected to V5V in which case both current limiting protection and over-voltage protection will be disabled.                                                                                      |

| VREF  | 2.25V reference voltage, used as a local "gnd" reference. Place a decoupling capacitor greater than 1µF between this pin and VGND. This pin will be prone to instability for capacitor values less than this. In applications where more several LX1725s are synchronized together, the VREF pins should all be tied together so that all units use a common VREF voltage. |

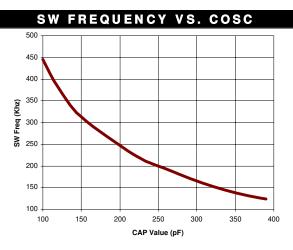

| COSC  | Place a capacitor between this pin and VGND to generate the PWM triangle wave. A 125pF capacitor will give an oscillation frequency of about 373KHz. In Master mode, this pin serves as the output for the triangle wave. In Slave mode, this pin is an input. The total capacitance on this pin will determine the frequency of oscillation.                              |

|         | FUNCTIONAL PIN DESCRIPTION (CONTINUED)                                                                                                                                                                                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Description                                                                                                                                                                                                                                                                                                                                          |

| VNEGA   | Analog voltage sense for VNEG voltage. Needs to be protected from noise at VNEG1 and VNEG2. Typically, about 180μA is sourced out of this pin.                                                                                                                                                                                                       |

| IN2P    | Positive audio input for channel 2. The input signal should be AC-coupled into this pin. The DC bias voltage will be equal to VREF. The input impedance to VREF will be about 17Kohm.                                                                                                                                                                |

| IN2M    | Negative audio input for channel 2. The input signal should be AC-coupled into this pin. The DC bias voltage will be equal to VREF. The input impedance to VREF will be about 17Kohm.                                                                                                                                                                |

| OUTREF2 | Negative feedback input pin for channel 2. Normally connected to VCOM.                                                                                                                                                                                                                                                                               |

| VGND    | Ground reference return for the analog +5V power supply. This supply is allowed to "float" between VNEG and VCOM. Typical current out of this pin is about 600μA.                                                                                                                                                                                    |

| MUTE    | Tri-level control pin. When this pin is set to greater than V5V/2, the audio signal path is muted. For voltages between V5V/4 and V5V/2, the audio gain will be set to approximately 5V/V. This allows the "Low Gain" mode to be tested. For voltages less than V5V/4, the normal 10V/V gain is in place.                                            |

| MASTER  | Quad-level control pin. This pin has three thresholds to enable Master/Slave and the "Quick" test mode. Quick mode forces the internal 65224 clock counter to be bypassed in order to speed-up production testing. Here is how the various modes are mapped:    V @ Master   Mode                                                                    |

| VPOS2   | Normally, this pin should be shorted to either V5V or GND.  Positive voltage supply to channel 2's output buffer. In a split supply system, this voltage will range between +5V up to +15V. In a single supply system, this voltage is allowed to be +10V up to +30V. Power supply de-coupling capacitance should be placed between VPOS2 and VNEG2. |

| OUT2    | PWM output for channel 2. This pin drives the L-C low pass filter prior to driving the speaker.                                                                                                                                                                                                                                                      |

| VNEG2   | Negative voltage supply to channel 2's output buffer. In a split supply system, this voltage will range between – 5V down to –15V. In a single supply system, this represents the 0V point.                                                                                                                                                          |

| VNEG1   | Negative voltage supply to channel 1's output buffer. In a split supply system, this voltage will range between – 5V down to –15V. In a single supply system, this represents the 0V point.                                                                                                                                                          |

| OUT1    | PWM output for channel 1. This pin drives the L-C low pass filter prior to driving the speaker.                                                                                                                                                                                                                                                      |

| VPOS1   | Positive voltage supply to channel 1's output buffer. In a split supply system, this voltage will range between +5V up to +15V. In a single supply system, this voltage is allowed to be +10V up to +30V. Power supply de-coupling capacitance should be placed between VPOS1 and VNEG1.                                                             |

| STBY    | A logic high as this pin forces a zero current standby mode. CMOS logic levels.                                                                                                                                                                                                                                                                      |

| VCOM    | Mid-voltage supply for both channel 1 and channel 2. This voltage should be half way between VPOS and VNEG. De-coupling capacitance should be placed between this pin and both VPOS and VNEG.                                                                                                                                                        |

| V5V     | Analog +5V supply for the signal processing section. This pin is referenced to VGND. For voltages less than 4V, the under voltage lockout circuit will keep the part in sleep mode. De-coupling capacitance should be placed between this pin and VGND.                                                                                              |

|         | FUNCTIONAL PIN DESCRIPTION (CONTINUED)                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Description                                                                                                                                                                           |

| HIGAIN  | High Gain mode control pin. If connected to V5V gives +6dB more gain.                                                                                                                 |

| OUTREF1 | Negative feedback input pin for channel 1, normally connected to VCOM.                                                                                                                |

| IN1M    | Negative audio input for channel 1. The input signal should be AC-coupled into this pin. The DC bias voltage will be equal to VREF. The input impedance to VREF will be about 17Kohm. |

| IN1P    | Positive audio input for channel 1. The input signal should be AC-coupled into this pin. The DC bias voltage will be equal to VREF. The input impedance to VREF will be about 17Kohm. |

### **PRODUCTION DATA SHEET**

### **ELECTRICAL CHARACTERISTICS**

Notes: Unless otherwise specified, the following specifications apply over the operating ambient temperature  $T_A$  = -40 ~ +85°C°C except where otherwise noted (typical @  $T_A$  = 25°C) and the following test conditions: VPOS = +12V, VNEG = -12V, VGND = 0V, V5V = 5V, VCOM = 0V  $R_{ILIM}$  = 50Kohm,  $C_{OSC}$  = 220pF, RL = 8 $\Omega$ .

| Parameter                                   | Symbol             | Symbol Test Conditions                                                                  |      | LX1725 |       |      |  |

|---------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|------|--------|-------|------|--|

|                                             | Cymbol             | Test conditions                                                                         | Min  | Тур    | Max   | Unit |  |

| OSCILLATOR                                  |                    |                                                                                         |      |        |       |      |  |

| Oscillator Frequency                        | FOSC               | Varies with C <sub>OSC</sub> capacitor value, value shown is for default conditions.    |      | 220    | 280   | KHz  |  |

| Voltage Stability                           |                    | VPOS-VNEG = 12V to 30V                                                                  |      |        | 10    | %    |  |

| Temperature Stability                       |                    | $T_A = 0$ °C to $70$ °C                                                                 |      |        | 5     | %    |  |

| Temperature Stability                       |                    | $T_A = -40$ °C to 85°C                                                                  |      |        | 8     | %    |  |

| POWER SUPPLY                                |                    |                                                                                         |      |        |       |      |  |

|                                             | $V_{POS}/V_{NEG}$  | VCOM to GND                                                                             | ±6   | ±12    | ±15   |      |  |

| Supply Voltage                              | V POS/ V NEG       | VNEG to GND                                                                             |      | 24     | 30    | V    |  |

|                                             | V5V                | @ Single Power Supply                                                                   | 4.5  | 5.0    | 5.5   |      |  |

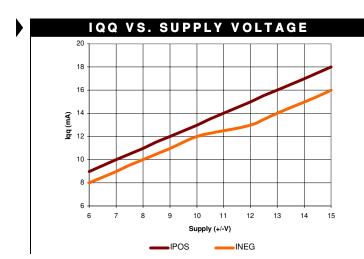

| Stand-By Current                            |                    | STBY Enable, T <sub>A</sub> = 25°C @ V5V                                                |      |        | 250   | μΑ   |  |

| Operating Current                           |                    | STBY Disabled, MUTE Enabled @ V5V                                                       |      | 15     | 20    | mA   |  |

| GAIN                                        | •                  |                                                                                         |      |        |       |      |  |

| High Gain Mode                              | GHIGH              | $oxed{ \begin{tabular}{lllllllllllllllllllllllllllllllllll$                             | 18   | 22     | 26    | V/V  |  |

| Normal Gain                                 | G <sub>NOM</sub>   | Pout=1W, F=1KHz, V <sub>MUTE</sub> = V <sub>GND</sub> , HIGAIN = V <sub>GND</sub>       | 9    | 11     | 13    | V/\  |  |

| Low Gain                                    | G <sub>LOW</sub>   | Pout=0.25W, F=1KHz, V5V / 4 < V <sub>MUTE</sub> < V5V / 2,<br>HIGAIN = V <sub>GND</sub> |      | 5.5    | 6.5   | V/\  |  |

| Mute Gain                                   | G <sub>MUTE</sub>  | Input 2Vpp, F=1KHz, V <sub>MUTE</sub> = V5V                                             |      | 0.01   | 0.045 | V/V  |  |

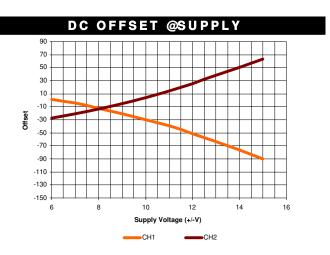

| OFFSET                                      |                    |                                                                                         |      |        |       |      |  |

| Output DC Offset                            | Voff               | Measured WRT VCOM                                                                       |      | 100    | 170   | m۷   |  |

| INPUT STAGE                                 |                    |                                                                                         |      | •      |       |      |  |

| Input Resistance                            | R <sub>IN</sub>    | Single-ended                                                                            | 17   |        | 27    | KΩ   |  |

| Common Mode Voltage                         | $V_{CM}$           |                                                                                         |      | 2.29   |       | V    |  |

| Common Mode Rejection Ratio                 | CMRR               |                                                                                         |      | 60     |       | dB   |  |

| OUTPUT STAGE                                | _                  |                                                                                         |      |        |       |      |  |

| PFET On resistance                          | $R_{DSONp}$        | VPOS = 12V, VNEG = -12V, Ids = 0.2A                                                     |      | 550    | 900   | mΩ   |  |

| NFET On resistance                          | R <sub>DSONn</sub> | VPOS = 12V, VNEG = -12V, lds = 0.2A                                                     |      | 550    | 900   | mΩ   |  |

| CURRENT LIMIT                               |                    |                                                                                         |      |        |       |      |  |

| Current Limit Threshold                     | lth                | GBNT **                                                                                 |      | 3.75   |       | Α    |  |

| Pulse Qualification Count                   | Icount             | Any 4 out of 5 clock periods                                                            |      | 4      |       |      |  |

| <b>VOLTAGE THRESHOLDS AT VPO</b>            | S – VNEG           |                                                                                         |      | _      |       |      |  |

| Under Voltage Threshold                     |                    | VPOS – VNEG                                                                             | 10   | 12     | 13.2  | V    |  |

| Start Threshold Hysteresis                  |                    |                                                                                         | 0.38 | 1      | 1.78  | V    |  |

| UNDER VOLTAGE LOCK-OUT @                    | V5V                |                                                                                         |      |        |       |      |  |

| Start Threshold Voltage                     |                    |                                                                                         | 3.8  | 4      |       | V    |  |

| THERMAL                                     |                    |                                                                                         |      |        | ,     |      |  |

| Thermal Gain Fold Back Junction Temperature |                    |                                                                                         |      | 125    |       | °C   |  |

| Thermal shut off Junction Temperature       |                    |                                                                                         |      | 150    |       | °C   |  |

Microsemi

### **PRODUCTION DATA SHEET**

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

Notes: Unless otherwise specified, the following specifications apply over the operating ambient temperature  $T_A = -40 \sim 85^{\circ}C$  except where otherwise noted (typical @  $T_A = 25^{\circ}C$ ) and the following test conditions: VPOS=+12V, VNEG=-12V, VGND = 0V, V5V = 5V, VCOM = 0V  $R_{ILIM} = 50$ Kohm,  $C_{OSC} = 220$ pF,  $R_{L} = 8\Omega$ .

| Parameter                    | Symbol | Symbol Test Conditions                     | LX1725 |       |      | Units    |  |

|------------------------------|--------|--------------------------------------------|--------|-------|------|----------|--|

| Faranielei                   |        | rest Conditions                            |        | Тур   | Max  | _ Silits |  |

| MUTE / STBY / MASTER SECTION |        |                                            |        |       |      |          |  |

|                              |        | Mute Mode @ V5V = 5.0V                     | 2.5    |       |      |          |  |

| MUTE Threshold               |        | Low Gain Mode @ V5V = 5.0V                 | 1.25   |       | 2.5  | V        |  |

|                              |        | Normal Gain Mode @ V5V = 5.0V              |        |       | 1.25 |          |  |

| STBY Threshold               |        | @ V5V = 5.0V                               | 2.60   |       | 2.85 | V        |  |

| STBY To Output Enable        |        | After Power on Reset Pulse, Not Quick Mode |        | 65536 |      | Clocks   |  |

|                              |        | Master, Not Quick Mode @ V5V = 5.0V        | 3.75   |       |      |          |  |

| Master Threshold             |        | Master, Quick Mode @ V5V = 5.0V            | 2.50   |       | 3.75 | W        |  |

| Master Threshold             |        | Slave, Quick Mode @ V5V = 5.0V             | 1.25   |       | 2.50 | V        |  |

|                              |        | Slave, Not Quick Mode @ V5V = 5.0V         |        |       | 1.25 |          |  |

<sup>\*</sup> RDSONP and RDSONN include all bond wires and pad resistance.

<sup>\*\*</sup> GBNT - Guarantee by design and system, no test.

### **PRODUCTION DATA SHEET**

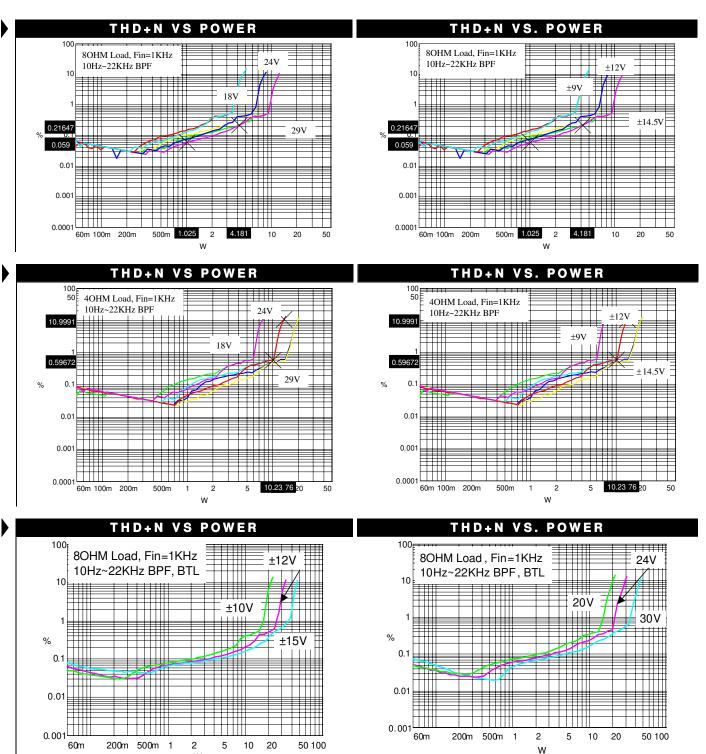

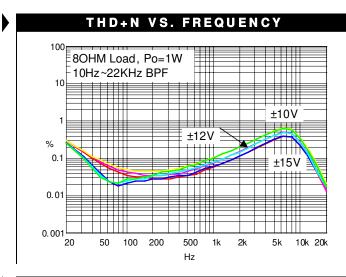

### SYSTEM MODULE CHARACTERISTICS

Notes: Unless otherwise specified, the following specifications apply over the operating ambient temperature  $T_A = 25^{\circ}\text{C}$  except where otherwise noted and the following test conditions: VPOS=+12V, VNEG=-12V, VGND = 0V, V5V = 5V, VCOM = 0V  $R_{ILIM} = 50 \text{Kohm}$ ,  $C_{OSC} = 220 \text{pF}$ , Output LC filter 47uH/0.68uF,  $R_L = 8\Omega$ , Test equipment built-in BPF 10Hz~22KHz.

| Parameter                               |                           | Symbol                 | Symbol Test Conditions                                             |                    | LX1725 |      | Units         |  |

|-----------------------------------------|---------------------------|------------------------|--------------------------------------------------------------------|--------------------|--------|------|---------------|--|

|                                         |                           | Symbol Test conditions |                                                                    | Min                | Тур    | Max  | 0             |  |

| AUDIO CHARACTERIS                       | STICS                     | •                      |                                                                    |                    |        |      |               |  |

|                                         | $R_L=8\Omega$             | Po                     | $V_{POS}/V_{NEG}=\pm 12V$ ; THD+N < 1%                             |                    | 7      |      |               |  |

| Output Power Stereo                     | 11[-022                   | ' 0                    | $V_{POS}/V_{NEG}=\pm 12V$ ; THD+N < 10%                            |                    | 9      |      |               |  |

| Output I ower otereo                    | $R_L=4\Omega$             | Po                     | $V_{POS}/V_{NEG}=\pm 12V$ ; THD+N < 1%                             |                    | 12     |      | w             |  |

|                                         | 11[-722                   | ' 0                    | $V_{POS}/V_{NEG}=\pm 12V$ ; THD+N < 10%                            |                    | 16     |      |               |  |

| Output Power BTL                        | R <sub>1</sub> =8Ω        | Po                     | $V_{POS}$ - $V_{NEG}$ =±12V; THD+N < 1%                            |                    | 25     | 25   |               |  |

| Output 1 Ower B12                       | 11[-022                   | ' 0                    | $V_{POS}$ - $V_{NEG}$ = $\pm 12V$ ; THD+N < 10%                    |                    | 32     |      |               |  |

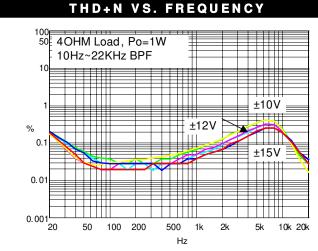

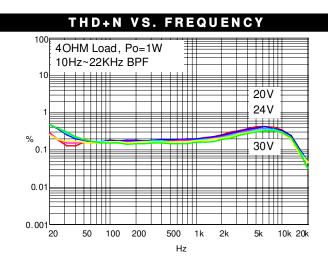

|                                         | R <sub>1</sub> =8Ω        | THD+N                  | V <sub>POS</sub> /V <sub>NEG</sub> =±12V ;Pout=1W, FIN=1KHz        |                    | 0.05   | 0.08 |               |  |

| Total Harmonic                          | 11[-022                   | 1110111                | V <sub>POS</sub> /V <sub>NEG</sub> =±12V ;Pout=1W, FIN=20~20KHz    |                    |        | 0.5  |               |  |

| Distortion Stereo                       | $R_L=4\Omega$             | THD+N                  | V <sub>POS</sub> /V <sub>NEG</sub> =±12V ;Pout=1W, FIN=1KHz        |                    | 0.08   | 0.1  | %             |  |

|                                         | 11[-722                   | 1110111                | V <sub>POS</sub> /V <sub>NEG</sub> =±12V ;Pout=1W, FIN=20~20KHz    |                    |        | 0.3  | 70            |  |

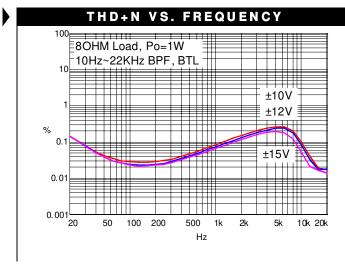

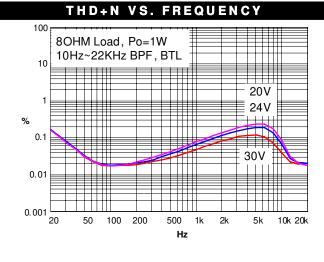

| Total Harmonic                          | $R_L=8\Omega$             | THD+N                  | $V_{POS}$ - $V_{NEG}$ = $\pm 12V$ ; $Pout$ = $1W$ , $FIN$ = $1KHz$ |                    | 0.05   | 0.08 |               |  |

| Distortion BTL                          | 11[-052                   |                        | V <sub>POS</sub> /V <sub>NEG</sub> =±12V ;Pout=1W, FIN=20~20KHz    |                    |        | 0.3  |               |  |

| Power Efficiency $R_L=8\Omega$ Stereo   |                           |                        | V <sub>POS</sub> /V <sub>NEG</sub> =±12V, Pout=Max, THD+N<1%       | 89                 | 91     | 91 % |               |  |

| Power Efficiency $R_L=4\Omega$ Stereo   |                           | η                      | V <sub>POS</sub> /V <sub>NEG</sub> =±12V, Pout=Max, THD+N<1%       | 80                 | 85     |      |               |  |

| Channel Crosstalk                       |                           | $V_{XTALK}$            | Pout=1W, F=1KHz                                                    |                    | -60    |      | dB            |  |

| Audio Bandwidth                         |                           | BW                     | Pout=1W, F=20-20KHz RL=8Ω                                          |                    | 2      | 3    | dB            |  |

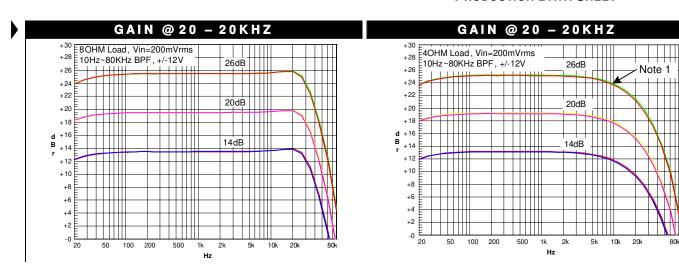

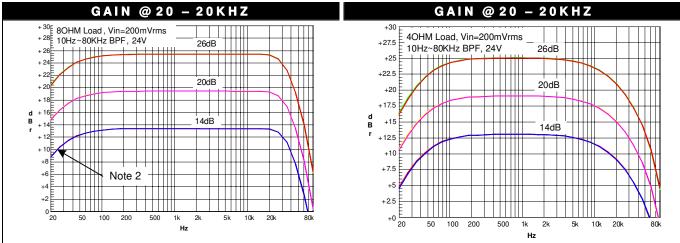

|                                         | HIGH                      |                        | $V_{IN}$ =200mVrms, F=20Hz~20KHz                                   | Vrms, F=20Hz~20KHz |        |      |               |  |

| Stage Gain                              | MID                       | $G_{SYS}$              | $V_{IN}$ =200mVrms, F=20Hz~20KHz                                   |                    | 20     | dl   |               |  |

|                                         | LOW                       |                        | V <sub>IN</sub> =200mVrms, F=20Hz~20KHz                            |                    | 14     | İ    |               |  |

| Mute Output                             |                           | $V_{MUTE}$             | Input short, system muted, stereo                                  |                    | -60    | 60   |               |  |

| Mute Output                             |                           | ▼ MUTE                 | Input short, system muted, BTL                                     |                    | -60    | ,    |               |  |

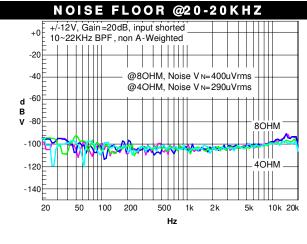

| Signal to Noise Ratio                   | Stereo S                  | SNR                    | 20-20KHz, non A-Weighted, $8\Omega$                                |                    | 85     |      | dB            |  |

| Signal to Noise Hallo                   |                           | SINIT                  | 20-20KHz, non A-Weighted, $4\Omega$                                | ited, 4Ω 89        |        |      | UD.           |  |

| Output Noise Floor                      | Stereo                    | $V_N$                  | Input short, non A-Weighted @ 20-20KHz, $8\Omega$                  |                    | 400    |      | ш\/           |  |

| Output Noise Floor Stereo               |                           | V N                    | Input short, non A-weighted @ 20-20KHz, 4Ω                         |                    | 300    |      | $\mu V_{RMS}$ |  |

| CURRENT LIMIT                           |                           |                        |                                                                    |                    |        |      |               |  |

| Current Limit Threshold I <sub>TH</sub> |                           | I <sub>TH</sub>        |                                                                    |                    | 3.75   | 4.0  | Α             |  |

| Pulse Qualification Count               |                           |                        | Any 4 out of 5 clock periods                                       |                    | 4      |      | cycle         |  |

| SUPPLY VOLTAGE LI                       | MIT                       |                        |                                                                    |                    |        |      |               |  |

| Lladau Valtana Ladi                     | Split V <sub>UVLO</sub>   |                        | VPOS                                                               | +5                 |        |      |               |  |

| Under Voltage Lock-<br>Out              | voltage Lock- Spire VOVLO | V UVLO                 | VNEG                                                               | -5                 |        |      |               |  |

|                                         | Single                    | $V_{UVLO}$             | VPOS, VNEG tied to GND                                             | 10                 |        |      |               |  |

Note: Characteristics done by system module evaluation.

Microsemi

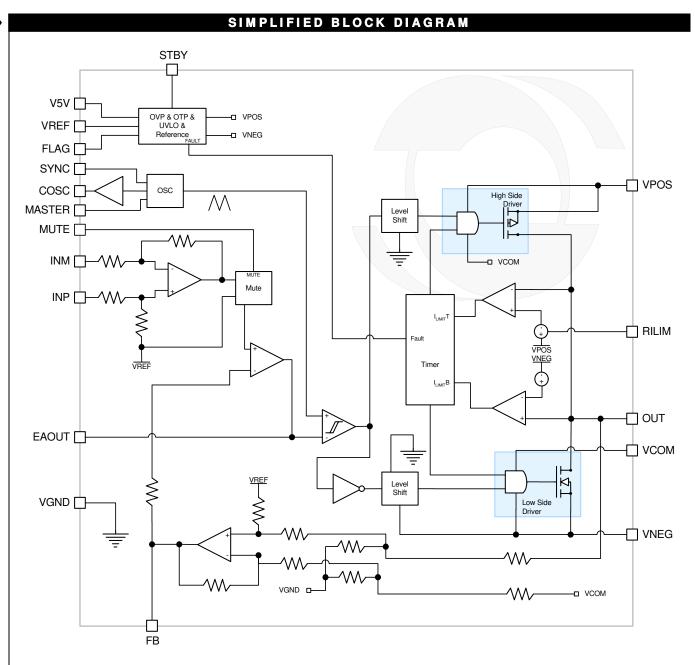

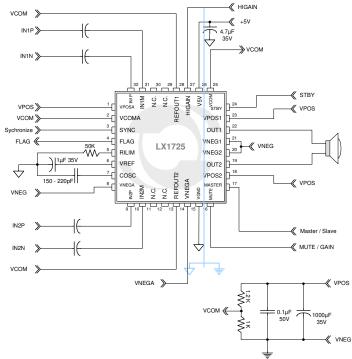

Figure 1 - Simplified Block Diagram (half of the circuit)

#### **PRODUCTION DATA SHEET**

#### **FUNCTION DESCRIPTION**

#### **OSCILLATOR**

LX1725 has a fixed PWM modulation frequency, but it is programmable by using an external capacitor connected to  $C_{\rm OSC}$  pin to GND. The switching frequency is approximately 235KHz with capacitor's value 220pF. With the capacitor value given, the switching frequency can be calculated as follows:

$F_{OSC} = 52000 / C_{OSC}$  $F_{OSC}$  in KHz, and  $C_{OSC}$  in pF.

The suggested switching frequency is 250KHz

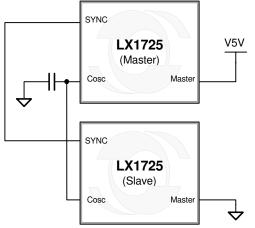

#### SYNCHRONIZATION

Two or more LX1725 oscillators can be configured for synchronous operation. One unit, the master, is programmed for the desired frequency with  $C_{\rm OSC}$  as usual, also with the MASTER pin tied to V5V. The SYNC pin and the  $C_{\rm OSC}$  pin of the slave units should be tied to the SYNC pin and the  $C_{\rm OSC}$  pin of the master unit respectively. The MASTER pin of slave components is tied to GND. In this configuration, the SYNC pins of the slave units begin receiving instead of transmitting clock pulses. Also, the  $C_{\rm OSC}$  pins quit driving the PWM capacitor in the slave units. Note that for optimum performance, all slave units should be located as close to the master unit as possible (Figure 2).

Figure 2 - Two Devices Synchronized Block Diagram

#### POWER ON RESET (POR)

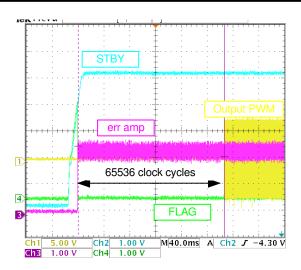

At start up or upon recovery from a fault condition, an internal "hiccup" counter counts 65536 clock cycles before allowing the outputs to begin switching. See the POR timing sequence in Figure 3.

Figure 3 – Power-On-Reset Timing Sequence

The MASTER pin, as mentioned in **SYNCHRONIZATION**, is for multi devices operation. It is also a Quad-level control pin with three thresholds to enable Master/Slave and the "Quick" test mode. Quick mode forces the internal 65536 clock counter to be bypassed in order to speed-up production testing; this is usually for factory production test purposes.

| V @ Master        | <u>Mode</u>         |

|-------------------|---------------------|

| < V5V/4           | Slave, Normal Mode  |

| < V5V/2, >V5V/4   | Slave, Quick mode   |

| < 3*V5V/4, >V5V/2 | Master, Quick mode  |

| > 3*V5V/4         | Master, Normal mode |

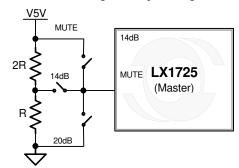

#### GAIN SELECTION/MUTE

The channel gain can be programmed between 26dB and 20dB by setting the HIGAIN pin to V5V or to GND. The MUTE pin is a Tri-level control pin for test purposes. When this pin is set to greater than V5V/2, the audio signal path is muted. For voltages between V5V/4 and V5V/2, the audio gain will be reduced by 6dB. This allows the "Low Gain" mode to be tested. For voltages less than V5V/4, the normal gain is in place (Figure 4).

Figure 4 - Gain Selection Block Diagram

#### **PRODUCTION DATA SHEET**

### FUNCTION DESCRIPTION(CONTINUED)

#### STAND BY

Forcing the STBY pin high puts the LX1725 into a zero current sleep mode. The outputs enter a high impedance mode and all internal bias circuits are disabled.

#### **OVER CURRENT LIMIT**

The LX1725 has built-in over circuit protection. The circuit works by monitoring the voltage drop across whichever power FET is active. When this voltage is greater than a certain threshold, an over-current condition is assumed. If this condition occurs during AUDIO INPUT five consecutive clock cycles, then the output transistors are immediately disabled. The hiccup counter then counts 65536 clock cycles before allowing the outputs to begin switching again. During this period the FLAG pin goes to HIGH to indicate a system fault. A "hiccup" condition will be clearly audible if a speaker is connected to the outputs. The threshold for the overcurrent condition is set to 3.75A.

The over current circuit hiccup protection can be disabled by pulling the RILIM pin to V5V.

#### UNDER VOLTAGE LOCK-OUT (UVLO)

If the voltage drops below ±5V under dual supply operation or 10V under single supply operation, the under voltage lock out circuit is activated and the LX1725 will enter the standby mode. This switch-off will be silent and without pop noise. It will be recovered when the supply voltage rises above the threshold level.

The FLAG pin will go logic HIGH to indicate the system fault. A similar circuit monitors V5V with a threshold of 4V.

#### THERMAL PROTECTION

When the junction temperature exceeds 125°C, the gain is reduced by 6dB (gain fold back) to reduce the output power and on-chip power dissipation., when the temperature drops below 110°C the gain will returns to normal. When the temperature exceeds 155°C the outputs are shut off to force the output current to zero. Again, when the temperature drops below 130°C the outputs are allowed to switch and normal operation resumes.

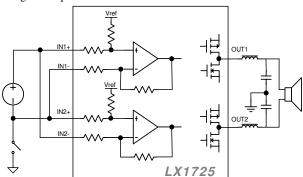

For a high common mode rejection ratio and a maximum flexibility in the application, the audio inputs are fully differential. By connecting the inputs anti-parallel the phase of one of the channels can be inverted, so that a load can be connected between the two output filters. In this case the system operates as a mono BTL amplifier and with the same loudspeaker impedance an approximately four times higher output power can be obtained. The input configuration for a mono BTL application is illustrated in Figure 6. In the stereo single-ended configuration it is also recommended to connect the two differential inputs in anti-phase. This has advantages for the current handling of the power supply at low signal frequencies.

Figure 6 - Audio Input Block Diagram

### **PRODUCTION DATA SHEET**

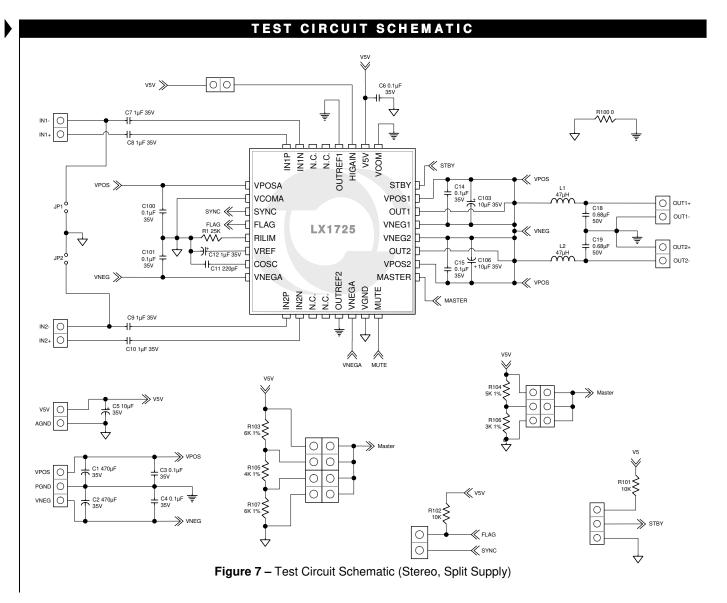

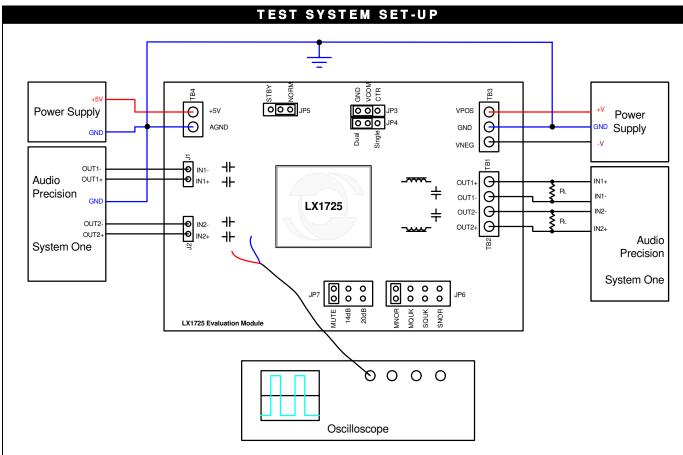

Figure 8 - System Test Set-up

### SYSTEM CONFIGURATION TEST Filterless Driver Driver & & NEG2 Filterless Logic Logic LX1725 LX1725 POS2 VPOS Figure 9 - System Test Configuration

#### **PRODUCTION DATA SHEET**

Microsemi

### **PRODUCTION DATA SHEET**

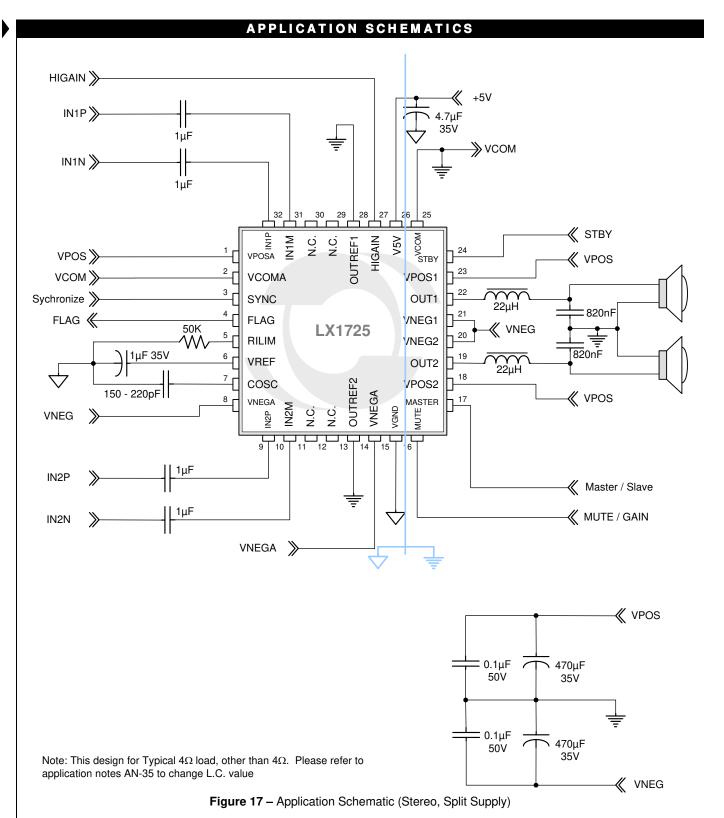

Note 1 – The output LC filter are based on 8OHM design, L=47uH, C=0.68uF, the 4OHM load LC filter design please refer to the application notes. Note 2 – At single supply mode, the output AC coupling capacitor value based on 470uF, for lower cut-off frequency, please refer to the application notes.

Microsemi

### **PRODUCTION DATA SHEET**

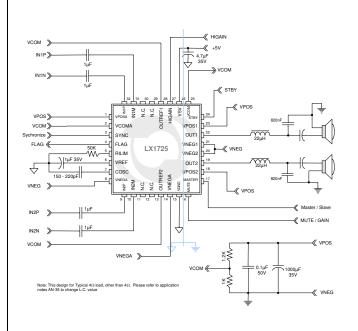

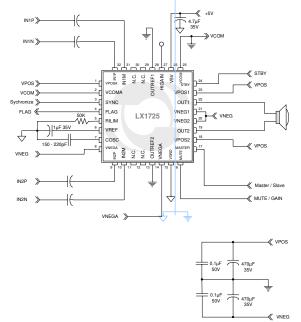

### APPLICATION SCHEMATICS (CONTINUED)

Figure 18 – Application Schematic (Stereo, Single Supply)

Figure 19 - Application Schematic (BTL, Split Supply)

Figure 20 – Application Schematic (BTL, Single Supply)

#### **PRODUCTION DATA SHEET**

### PCB DESIGN GUIDELINES

#### **PCB DESIGN GUIDELINES**

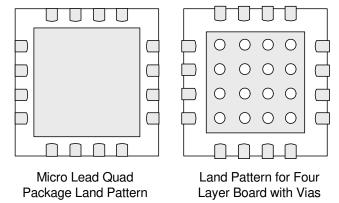

One of the key efforts in implementing the MLP package on a pc board is the design of the land pattern. The MLP has rectangular metallized terminals exposed on the bottom surface of the package body. Electrical and mechanical connection between the component and the pc board is made by screen printing solder paste on the pc board and then reflowing the paste after placement. To guarantee reliable solder joints it is essential to design the land pattern to the MLP terminal pattern, exposed PAD, and Thermal PAD via. There are two basic designs for PCB land pads for the MLP: Copper Defined style (also known as Non Solder Mask Defined (NSMD)) and the Solder Mask Defined style (SMD). The industry has had some debate on the merits of both styles and although Microsemi recommends the Copper Defined style land pad (NSMD), both styles are acceptable for use with the MLP package.

NSMD pads are recommended over SMD pads due to the tighter tolerance on copper etching than solder masking. NSDM by definition also provides a larger copper pad area and allows the solder to anchor to the edges of the copper pads thus providing improved solder joint reliability.

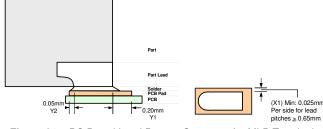

### DESIGN OF PCB LAND PATTERN FOR PACKAGE TERMINALS

As a general rule, the PCB lead finger pad (Y) should be designed 0.2-0.5mm longer than the package terminal length for good filleting. The pad length should extend 0.05mm towards the centerline of the package. The pad width (X) should be a minimum 0.05mm wider than the package terminal width (0.025mm per side), refer to figure 21. However, the pad width is reduced to the width of the component terminal for lead pitches below 0.65mm. This is done to minimize the risk of solder bridging.

Figure 21 – PC Board Land Pattern Geometry for MLP Terminals

#### EXPOSED PAD PCB DESIGN

The construction of the Exposed Pad MLP enables enhanced thermal and electrical characteristics. In order to take full advantage of this feature the exposed pad must be physically connected to the PCB substrate with solder. The exposed pad is internally connected to the die substrate potential which is VNEG so it is very important that the PCB substrate potential be connected to VNEG as well.

The thermal pad (D2th) should be greater than D2 of the MLP whenever possible; however adequate clearance (Cpl > 0.15mm) must be met to prevent solder bridging. If this clearance cannot be met, then D2th should be reduced in area. The formula would be: D2TH >D2 only if D2TH <Gmin - (2 x Cpl).

#### THERMAL PAD VIA DESIGN

There are two types of on-board thermal PAD designs: one is using thermal vias to sink the heat to the other layer with metal traces. Based on the Jedec Specification (JESD 51-5) the thermal vias should be designed like Figure 22. Another one is the no via thermal PAD which is using the same side copper PAD as heat sink, this type of thermal PAD is good for a two layer board, since the bottom side is filled with all other kinds of trace also, it's hard to use the whole plane for the heat sink. But you still can use vias to sink the heat to the bottom layer by the metal traces, then layout a NMSD on which a metal heat sink is put to sink the heat to the air.

Figure 22 - Comparison of land pattern theory

#### **PRODUCTION DATA SHEET**

### PCB DESIGN GUIDELINES (CONTINUED)

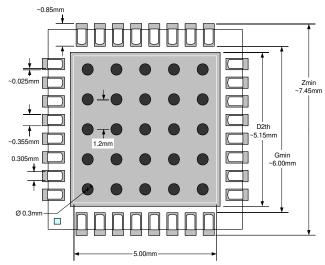

The LX1725 is supplied in an MLPQ-7mmx7mm, 32 pin package.  $\theta_{JA}$  =29.3°C/W for the package by itself in still air. When running at a continuous 20W output power, the on-chip power dissipation will be 3.5W assuming 85% efficiency. With no reduction in the thermal resistance, the die temperature will rise 103 above ambient.  $\theta_{JC}$  is about 4°C/W. If the exposed pad is properly connected to a heat sink, then the temperature rise will be reduced to around 16°C under these condition. So the non-via type thermal PAD is suggested.

Figure 23 - Recommended Land Pad with Vias for LQ32 (7mm²)

Zmin= D + aaa + 2(0.2) (where pkg body tolerance aaa=0.15) (where 0.2 is outer pad extension) Gmin= D-2(Lmax)-2(0.05) (where 0.05 is inner pad extension) (Lmax=0.50 for this example) D2th max = Gmin-2(CpL) (where CpL=0.2)

### **PRODUCTION DATA SHEET**

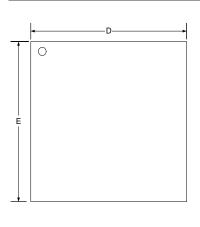

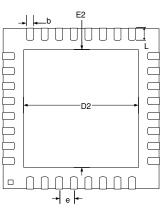

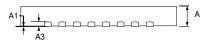

### PACKAGE DIMENSIONS

### LQ 32-Pin Package Description (Micro Lead Quad Package)

|     | MILL | METERS   | INCHES    |           |  |  |

|-----|------|----------|-----------|-----------|--|--|

| Dim | MIN  | MAX      | MIN       | MAX       |  |  |

| Α   | 0.80 | 1.00     | 0.031     | 0.039     |  |  |

| A1  | 0    | 0.05     | 0         | 0.002     |  |  |

| A3  | 0.2  | 5 REF    | 0.010     |           |  |  |

| b   | 0.23 | 0.38     | 0.009     | 0.015     |  |  |

| D   | 7.0  | 7.00 BSC |           | 0.276 BSC |  |  |

| D2  | 5.00 | 5.25     | 0.197     | 0.207     |  |  |

| E   | 7.0  | 0 BSC    | 0.276 BSC |           |  |  |

| E2  | 5.00 | 5.25     | 0.197     | 0.207     |  |  |

| е   | 0.6  | 0.65 BSC |           | 26        |  |  |

| L   | 0.45 | 0.65     | 0.018     | 0.026     |  |  |

**Note:** Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm(.006") on any side. Lead dimension shall not include solder coverage.

LX1725

# 15W+15W Stereo Class-D Amplifier Filterless 30W Mono in BTL

**PRODUCTION DATA SHEET**

NOTES

PRODUCTION DATA – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.