Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

PRODUCTION DATASHEET

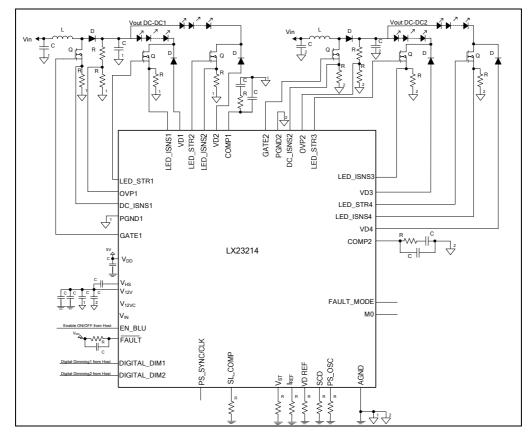

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

## Introduction

efficiency.

# The LX23214 is a four-channel LED driver for backlight applications in LCD TVs and monitors. It integrates two individual DC/DC blocks with peak current mode control. Each DC/DC section has two PWM controllers to drive two LED strings. The DC/DC control loop adjusts the supply voltage for each pair of LED strings for maximum power

**DESCRIPTION**

The DC/DC PWM controllers are phase shifted by 180° to reduce peak ripple currents and radiated EMI. Systems with two LX23214 units can be synchronized to prevent beat frequency interference.

LED string short circuit or open circuit conditions are detected, flagged, and protected against.

Internal linear regulators provide 12V and 5V power rails to drive internal circuitry from the  $V_{\rm IN}$  voltage. Alternatively a 12V supply can be fed directly to the device.

The LX23214 supports Analog Dimming or two Direct Digital Dimming inputs. Each Direct Digital Dimming input controls two LED strings.

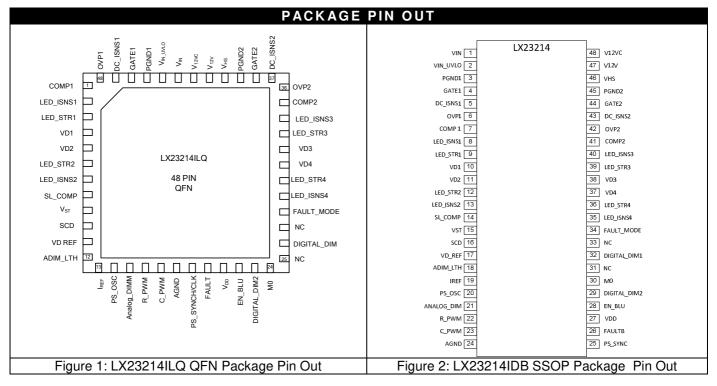

The LX23214 is available in both 48 pin QFN and 48 pin SSOP packages.

**IMPORTANT:** For the most current data, consult *MICROSEMI*'s website: <a href="http://www.microsemi.com">http://www.microsemi.com</a>

## **KEY FEATURES**

- EDGE-Lit LED Backlight Driver for LCD TVs and Monitor Displays

- Supports Analog Input dimming or Direct Digital LED dimming operations.

- Supports LED PWM dimming frequency of up to 2kHz

- Direct Digital PWM mode supports two independent digital input signals

- 2% precision current control of four LED strings (string to string).

- ±3% precision current control (chip to chip)

- Supports four LED strings with control and protection

- LED string currents are completely user programmable

- Two integrated, independent DC/DC power supplies controllers which support boost operation mode.

- 100kHz to 300kHz constant switching frequency power conversion

- Supports DC/DC synchronization across multiple ICs

- LED open and short circuit fault protection and indication

- Over temperature and over voltage fault protection and indication

- RoHS compliant

|                                  | PACKAGE ORDER INFO                                 | THERMAL DATA                                                      |

|----------------------------------|----------------------------------------------------|-------------------------------------------------------------------|

| T <sub>A</sub> (℃)<br>-40 to +85 | LX23214IDB (Bulk)<br>LX23214IDB-TR (Tape and Reel) | $\theta_{JA} = 70$ °C/W SSOP leaded package according to JESD51-7 |

| -40 10 +05                       | LX23214ILQ (Bulk)<br>LX23214ILQ-TR (Tape and Reel) | θ <sub>JA</sub> = 29°C/W QFN package according to JESD51-7        |

RoHS Compliant / Pb-free

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .  $\theta_{JA}$  levels are guidelines for the thermal performance of the device/pc-board system. All of the above assumes no ambient airflow.

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                |                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| V <sub>IN</sub> Supply Input Voltage                                                                                                                    | 0.3V to 45V                      |

| V <sub>12V</sub> Supply Input Voltage                                                                                                                   | 0.3V to 15V                      |

| V <sub>12V</sub> Supply Input Voltage                                                                                                                   | $V_{12V}$ -0.3V to $V_{12V}$ +2V |

| V <sub>IO</sub> Input Voltage                                                                                                                           | 0.3V to V <sub>DD</sub> +0.3V    |

| Gate1, Gate2, LED_STR1-LED_STR 4, VD1-VD4FAULT,LED ISNS 1-LED ISNS4                                                                                     | 0.3V to +6V                      |

| Between any two grounds.                                                                                                                                | 0.3V to+ 0.3V                    |

| Operating Ambient Temperature Range                                                                                                                     |                                  |

| Maximum Operating Junction Temperature                                                                                                                  | +/- 2.5 kV                       |

| CDM ESD Protection at all I/O pins                                                                                                                      | +/- 1.5kV                        |

| MM ESD Protection at all I/O pins                                                                                                                       | +/- 250V                         |

| Storage Temperature Range                                                                                                                               |                                  |

| Lead Temperature (Soldering 10 seconds)                                                                                                                 |                                  |

| Package Peak Temperature for Solder Reflow (40 seconds maximum exposure)                                                                                | 260°C (+0,-5°C)                  |

| <b>Notes</b> : Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. C negative out of specified terminal. | urrents are positive into,       |

| RECOMMENDED OPERATING CONDITIONS                                          |           |  |  |  |  |

|---------------------------------------------------------------------------|-----------|--|--|--|--|

| V <sub>IN</sub> Supply Input Voltage                                      | 15 to 30V |  |  |  |  |

| V <sub>12V</sub> Supply Input Voltage when driven from an external supply | 10 to 15V |  |  |  |  |

| Operating Ambient Temperature Range                                       | 40 to 85℃ |  |  |  |  |

| Minimum PWM pulse width                                                   | 20µs      |  |  |  |  |

| ADIM_LTH voltage                                                          | 0 to 0.5V |  |  |  |  |

| R <sub>IREF</sub>                                                         |           |  |  |  |  |

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

# **Electrical Specifications**

**PRODUCTION DATASHEET**

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, the following specifications apply for operating ambient temperature -10 $^{\circ}$   $\leq$  Tamb  $\leq$  +85 $^{\circ}$ .

## **IC Supply Specifications**

| PARAMETER                                                                                  | SYMBOL             | TEST CONDITIONS /                                                                                              |          | X2321 | 4                | UNIT       |  |

|--------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|----------|-------|------------------|------------|--|

| FARAMETER                                                                                  | 31 MBGE            | COMMENT                                                                                                        | MIN      | TYP   | MAX              | ONI        |  |

| IC Supply Specification                                                                    | ns                 |                                                                                                                |          |       |                  |            |  |

| Supply Voltage                                                                             | V <sub>IN</sub>    | Input condition when V <sub>IN</sub> drives the 12V internal linear regulator                                  | 15       | 24    | 40               | V          |  |

| Input Supply Current                                                                       | I <sub>IN</sub>    | V <sub>IN</sub> = 24V, LED PWM 50% duty at 2kHz, DC/DC switching at 300kHz, gate drivers loaded by 1000pF      |          | 23    | 30               | mA         |  |

|                                                                                            |                    | LED dimming at 0%                                                                                              |          | 6     | 8                |            |  |

| Sleep Current                                                                              | I <sub>SLEEP</sub> | EN_BLU = Logic low, V <sub>DD</sub> and V <sub>12V</sub> are active and available to drive external circuitry. |          |       | 5                | mA         |  |

| (I <sub>REF</sub> , V <sub>12VC</sub> , V <sub>12V</sub> , V <sub>DD</sub> , V             | нѕ)                |                                                                                                                |          |       |                  |            |  |

| I <sub>REF</sub> Output voltage                                                            | V <sub>IREF</sub>  | Loaded with a 30.1kΩ resistor                                                                                  | 1.181    | 1.201 | 1.222            | V          |  |

| 12 V <sub>DC</sub> Input Voltage                                                           | V <sub>12V</sub>   | Input condition when using an external 12V supply to drive V <sub>12V</sub>                                    | 10       | 12    | 15               | V          |  |

| 12V Regulated V <sub>12V</sub> Voltage Output  5V Regulated V <sub>DD</sub> Voltage Output |                    | $15V \le V_{IN} \le 30V, 0 \le I \le 50 mA$<br>Pins $V_{12V}$ and $V_{12VC}$ are connected together            | 10.8     | 12    | 13.2             | V          |  |

|                                                                                            |                    | $10V \le V_{12V} \le 15V$ , $0 \le I \le 10 \text{ mA}$                                                        | 4.75     | 5     | 5.25             | V          |  |

| V <sub>12VC</sub> Output Current                                                           | I <sub>12VC</sub>  | V <sub>12VC</sub> pin is shorted to V <sub>12V</sub> pin.<br>Available for external use                        | 2        |       |                  | m <i>A</i> |  |

| V <sub>DD</sub> Output Current                                                             | I <sub>VDD</sub>   | Available for external use                                                                                     | 1        |       |                  | m <i>A</i> |  |

| LED Current Accuracy                                                                       | (20 mA < ILED      | < 350 mA @ 100% duty cycle, VSENSE = 35                                                                        | 0 mV)    |       |                  |            |  |

| LED Current<br>Accuracy Chip to                                                            |                    | -10°C ≤T <sub>amb</sub> ≤ +85°C                                                                                |          |       | ±3               | %          |  |

| Chip                                                                                       |                    | +50°C ≤T <sub>amb</sub> ≤+70°C                                                                                 |          |       | ±2               | %          |  |

| LED Current Matching                                                                       | (20 mA < ILED      | ) < 350 mA @ 100% duty cycle, VSENSE = 3                                                                       | 50 mV)   |       |                  |            |  |

| LED Current<br>Matching String to                                                          |                    | -10℃ ≤T <sub>amb</sub> ≤ +85℃                                                                                  |          |       | ±2               | %          |  |

| String                                                                                     |                    | +50°C ≤T <sub>amb</sub> ≤+70°C                                                                                 |          |       | ±1               | %          |  |

| LED NFET Driver (LED_                                                                      | ISNS1-4,LED_       | STR1-4)                                                                                                        | <u>ı</u> |       | 1                |            |  |

| LED Current Sense<br>Accuracy                                                              | $V_{SENSE}$        | LED_ISNS voltage absolute accuracy                                                                             | 340      | 348   | 355              | m۷         |  |

| Gate Drive Range                                                                           | $V_{GD\_LED}$      |                                                                                                                | 0        |       | V <sub>12V</sub> | V          |  |

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

|                                                   |                                       | TEST CONDITIONS /                                                                                                             |                    |                           |       |        |  |

|---------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|-------|--------|--|

| PARAMETER                                         | SYMBOL                                | COMMENT                                                                                                                       | LX23214 MIN TYP MA |                           | MAX   | W UNIT |  |

| PS reference voltage                              | $V_{PS}$                              | Loaded with a $30.1k\Omega$ resistor.                                                                                         | 1.127              | 1.154                     | 1.173 | V      |  |

| Upper oscillator frequency                        | f <sub>OSC_UPPER</sub>                | $R_{PS\_OSC} = 30.1k\Omega$ DC/DC switching frequency is 1/2 of the oscillator frequency                                      | 0.54               | 0.6                       | 0.66  | MHz    |  |

| Lower oscillator frequency                        | fosc_lower                            | R <sub>PS_OSC</sub> = 90.9kΩ  DC/DC switching frequency is 1/2 of the oscillator frequency                                    | 0.18               | 0.20                      | 0.22  | MHz    |  |

| DC/DC NFET Driver (GA                             | ATE1,GATE2)                           |                                                                                                                               |                    |                           |       |        |  |

| DC/DC Maximum Duty Cycle Pull up Resistance       | DC <sub>MAX</sub>                     |                                                                                                                               |                    | 90                        | 18    | %      |  |

| Pull down                                         |                                       |                                                                                                                               |                    | 6                         | 12    | Ω      |  |

| Resistance                                        |                                       |                                                                                                                               |                    |                           |       |        |  |

| DC/DC Current Sense s                             | · –                                   | NS1, DC_ISNS2)                                                                                                                |                    |                           |       |        |  |

| Maximum Sense<br>Input Voltage                    | V <sub>SENSE</sub>                    |                                                                                                                               | 180                | 200                       | 220   | mV     |  |

| Leading Edge<br>Blanking                          | t <sub>BLANK</sub>                    |                                                                                                                               | 75                 | 100                       | 125   | ns     |  |

| Drain Voltage Sensing                             | section (VD1,                         | VD2, VD3, VD4)                                                                                                                |                    |                           |       |        |  |

| VDMIN Accuracy                                    |                                       | WRT VD_REF                                                                                                                    | -0.1               | 0                         | 0.1   | V      |  |

| VD bias Current                                   |                                       | Bias for external blocking diode                                                                                              |                    | 90                        |       | μΑ     |  |

| LED short circuit detect                          | tion level (SCI                       | ), VD1, VD2, VD3, VD4)                                                                                                        |                    |                           |       |        |  |

| Differential SCD threshold                        | V <sub>SCD</sub>                      | Difference between VDmax and $V_{ADIM}$ , $R_{SCD} = 100k\Omega$ ,                                                            | 7.6                | 8                         | 8.4   | V      |  |

| Absolute SCD<br>threshold                         |                                       | Measured WRT V12V                                                                                                             |                    | 92                        |       | %      |  |

| SCD bias current                                  |                                       |                                                                                                                               |                    | 0.6/R <sub>IRE</sub>      |       | Α      |  |

| V <sub>DMIN</sub> Reference (V <sub>DREF</sub> )  |                                       |                                                                                                                               |                    | <u> </u>                  |       |        |  |

| V <sub>DREF</sub> Bias Current                    |                                       |                                                                                                                               |                    | 0.6/R <sub>IRE</sub>      |       | Α      |  |

| Fast Start Threshold (V                           | ST)                                   |                                                                                                                               |                    | F                         |       |        |  |

| •                                                 |                                       |                                                                                                                               |                    |                           |       |        |  |

| VST Bias Current                                  |                                       |                                                                                                                               |                    | 0.6/R <sub>IRE</sub>      |       | Α      |  |

| VST Bias Current  Analog PWM Oscillator           | (R <sub>PWM</sub> ,C <sub>PWM</sub> ) |                                                                                                                               |                    | 0.6/R <sub>IRE</sub><br>F |       | A      |  |

|                                                   | (R <sub>PWM</sub> ,C <sub>PWM</sub> ) | Loaded with a 30.1KΩ resistor.                                                                                                | 1.178              |                           | 1.222 | A V    |  |

| Analog PWM Oscillator  R <sub>PWM</sub> Reference | (R <sub>PWM</sub> ,C <sub>PWM</sub> ) | Loaded with a 30.1KΩ resistor.  C <sub>PWM</sub> should be in a range between 3.6nF and 22nF and +/-1% accuracy               | 1.178              | F                         | 1.222 |        |  |

| Analog PWM Oscillator                             | (R <sub>PWM</sub> ,C <sub>PWM</sub> ) | C <sub>PWM</sub> should be in a range between 3.6nF and 22nF and +/-1% accuracy R <sub>PWM</sub> should be in a range between | 1.178              | F                         | 1.222 |        |  |

| Analog PWM Oscillator  R <sub>PWM</sub> Reference | (R <sub>PWM</sub> ,C <sub>PWM</sub> ) | C <sub>PWM</sub> should be in a range between 3.6nF and 22nF and +/-1% accuracy                                               | 1.178              | F                         | 1.222 |        |  |

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

|                                         |                        | TEST CONDITIONS /                                                         |                       | X2321                   |                                  |      |

|-----------------------------------------|------------------------|---------------------------------------------------------------------------|-----------------------|-------------------------|----------------------------------|------|

| PARAMETER                               | SYMBOL                 | COMMENT                                                                   | MIN                   | TYP                     | MAX                              | UNIT |

| Analog Inputs (ANALO                    | G_DIM, ADIM_           | ı                                                                         |                       |                         |                                  |      |

| ANALOG_DIM<br>Voltage Range             |                        | ADIM_LTH connected to AGND                                                | -0.125                |                         | 2.5                              | V    |

| LED PWM Duty Cycle Range                |                        | ADIM_LTH connected to AGND                                                | 0                     |                         | 100                              | %    |

| Input Current                           |                        | $V_{ANALOG\_DIM} = 2.5V$                                                  |                       |                         | 1                                | μΑ   |

| TTL Inputs (EN_BLU,D                    | └<br>IGITAL_DIM1,D     | IGITAL_DIM2)                                                              |                       |                         |                                  |      |

| Input Logic High                        | V <sub>IH</sub>        | Input Condition                                                           | 2.0                   |                         |                                  | V    |

| Input Logic Low                         | V <sub>IL</sub>        | Input Condition                                                           |                       |                         | 0.8                              | V    |

| Input High Current                      | I <sub>IH</sub>        | $V_{INH} = 5V$                                                            |                       |                         | 10<br>(140<br>for<br>EN_BL<br>U) | μА   |

| Input Low Current                       | I <sub>IL</sub>        | $V_{INL} \le 0.8V$                                                        |                       |                         | 5<br>(25 for<br>EN_BL<br>U)      | μА   |

| Input Hysteresis Voltage                | V <sub>IHH</sub>       |                                                                           |                       | 0.6                     | 0)                               | V    |

| CMOS I/O (PS_SYNC/C                     | LK)                    |                                                                           |                       | L                       |                                  |      |

| Input Logic<br>Threshold                | V <sub>TH</sub>        |                                                                           |                       | V <sub>DD</sub><br>*0.5 |                                  | V    |

| Output High Voltage                     | V <sub>OH</sub>        | I = 5mA                                                                   | V <sub>DD</sub> - 0.5 |                         |                                  | V    |

| Output Low Voltage                      | V <sub>OL</sub>        | I = 5mA                                                                   |                       |                         | 0.5                              | V    |

| Input Logic High<br>Threshold           | V <sub>IH</sub>        |                                                                           | V <sub>DD</sub> - 1.7 |                         |                                  | V    |

| Input Logic Low<br>Threshold            | V <sub>IL</sub>        |                                                                           |                       |                         | 1                                | V    |

| Tri-state Threshold Input Float Voltage | V <sub>TRI_STATE</sub> | Input is floating                                                         |                       | V <sub>DD</sub> /2      |                                  | V    |

| Input High Current                      | I <sub>IH</sub>        | $V_{\rm IN} = V_{\rm DD}$                                                 |                       |                         | 20                               | μΑ   |

| Input Low Current                       | I <sub>IL</sub>        | $V_{IN} = 0V$                                                             | -20                   |                         |                                  | μΑ   |

| Over voltage protection                 | n (OVP1,OVP2)          |                                                                           |                       |                         |                                  |      |

| OVP threshold                           | $V_{IN\_OVPT}$         |                                                                           | 3.8                   | 4                       | 4.2                              | V    |

| OVP Hysteresis                          | V <sub>IN_OVPH</sub>   |                                                                           |                       | 0.6                     |                                  | V    |

| UVLO Threshold<br>Level                 | V <sub>IN_UVLOT</sub>  | Disable IC by holding POR low while under this level                      | 3.85                  | 4.0                     | 4.2                              | V    |

| UVLO Hysteresis                         | V <sub>IN_UVLOH</sub>  | Hysteresis for programmable input (V <sub>IN</sub> ) UVLO threshold level |                       | 0.5                     |                                  | V    |

| Open drain (FAULT)                      |                        |                                                                           | •                     |                         |                                  |      |

| Output Low Voltage                      | V <sub>OL_FAULT</sub>  | $I_{OL} = 2mA$                                                            |                       |                         | 0.2                              | V    |

| Leakage Current                         | I <sub>L_FAULT</sub>   | $V_{OUT} = 5V$                                                            |                       |                         | 1                                | μΑ   |

|                                         |                        |                                                                           |                       |                         |                                  |      |

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

| PARAMETER                        | CVMDOL                | TEST CONDITIONS /                       |     |         |     |      |

|----------------------------------|-----------------------|-----------------------------------------|-----|---------|-----|------|

| PARAMETER                        | SIMBUL                | COMMENT                                 | MIN | TYP     | MAX | UNIT |

| Threshold Voltage                |                       | 2.                                      |     | 2.4 2.5 |     | V    |

| Thermal Protection               | n                     |                                         |     |         |     |      |

| Over Temperature<br>Shutdown     | T <sub>SHUT_OFF</sub> | Maximum temperature shutdown protection | 160 | 175     | 195 | ōC   |

| Over Temp<br>Shutdown Hysteresis | T <sub>OTSH</sub>     |                                         |     | 40      |     | ºC   |

Note: Thermal protection shuts down all DC/DC ports in auto restart mode; this mode is independent of the fault mode selection.

www. Microsemi.com

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

# **Pin Description**

| QFN   | SSOP  | Pin Name        | Pin Type         |                                                                                                                                                                                                                                     |

|-------|-------|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Pin # |                 | Jpo              | Description                                                                                                                                                                                                                         |

| 1     | 7     | COMP1           | Input            | DC/DC1 loop compensation, R/C network to PGND1                                                                                                                                                                                      |

| 2     | 8     | LED_ISNS1       | Input            | LED String1 current sense, resistor to PGND1. $R_{SENSE} = 0.35V/I_{LED}$                                                                                                                                                           |

| 3     | 9     | LED_STR1        | Output           | LED String1 NFET gate drive.                                                                                                                                                                                                        |

| 4     | 10    | VD1             | Input            | Connect to an isolating NFET or diode to sense String 1 NFET drain voltage.                                                                                                                                                         |

| 5     | 11    | VD2             | Input            | Connect to an isolating NFET or diode to sense String 2 NFET drain voltage.                                                                                                                                                         |

| 6     | 12    | LED_STR2        | Output           | LED String2 NFET gate drive.                                                                                                                                                                                                        |

| 7     | 13    | LED_ISNS2       | Input            | LED String2 current sense, resistor to PGND1.  R <sub>SENSE</sub> = 0.35V/I <sub>LED</sub>                                                                                                                                          |

| 8     | 14    | SL_COMP         | Input            | DC/DC boost converter slope compensation, resistor to AGND. $R_{SL\ COMP} = 1.2V/(10*m_a*30pF)$                                                                                                                                     |

| 9     | 15    | V <sub>ST</sub> | Input            | DC/DC fast start threshold, resistor to AGND. Fast start stops when the OVP pin reaches VST. $R_{VST} = V_{ST} *R_{IREF}/0.6V$                                                                                                      |

| 10    | 16    | SCD             | Input            | LED short circuit threshold, resistor to AGND. $R_{SCD} = V_{SCD} * R_{IREF} / 2.4 V$                                                                                                                                               |

| 11    | 17    | VD_REF          | Input            | $V_{DMIN}$ set point, resistor to AGND.<br>$R_{VD REF} = V_{DMIN} * R_{IREF} / 0.6 V$                                                                                                                                               |

| 12    | 18    | ADIM_LTH        | Input            | Analog PWM dimming valley setting, resistor to AGND, leave open for digital dimming.  R <sub>ADIM_LTH</sub> = (Valley+0.125)*R <sub>IREF</sub> /0.6V  Short to AGND for Valley = -0.125V.                                           |

| 13    | 19    | IREF            | Input            | Bias current setting, connect $30.1 \text{K}\Omega$ to AGND.                                                                                                                                                                        |

| 14    | 20    | PS_OSC          | Input            | DC/DC frequency setting, resistor to AGND. $R_{PS\_OSC} = 9.6*(1000/F_{DC/DC} - 0.129)$ $R_{PS\_OSC} \text{ in } k\Omega \text{ and } F_{DC/DC} \text{ in } kHz.$ Leave PS_OSC pin open to use an external clock.                   |

| 15    | 21    | ANALOG_DIM      | Input            | Analog PWM Dimming Control voltage input, leave open for digital dimming.                                                                                                                                                           |

| 16    | 22    | R_PWM           | Input            | Analog PWM dimming frequency setting, resistor to AGND, leave open for digital dimming. $R_{PWM} = 4/(13.18^*F_{PWM}^*C_{PWM}^*(2.625\text{-ADIM\_LTH}))$ $R_{PWM} \text{ should be set between } 15k\Omega \text{ and } 60k\Omega$ |

| 17    | 23    | C_PWM           | Input            | Analog PWM dimming frequency setting, capacitor to AGND, leave open for digital dimming.  C <sub>PWM</sub> should be set between 3.6nF to 22nF.                                                                                     |

| 18    | 24    | AGND            | Ground           | Analog ground supply.                                                                                                                                                                                                               |

| 19    | 25    | PS_SYNC/CLK     | Input/<br>Output | DC/DC clock output as a master of clock input as a slave.                                                                                                                                                                           |

| 20    | 26    | FAULT           | Output           | Fault flag and hiccup timer, open drain, connect to an external R-C pull up network. Goes low to indicate a fault.                                                                                                                  |

| 21    | 27    | $V_{DD}$        | Power            | 5V volt supply for internal circuitry, 2.2μF capacitor to AGND to guarantee stability.                                                                                                                                              |

| 22    | 28    | EN_BLU          | Input            | Back light enable. Turns on the DC/DC converters and LED string controllers.                                                                                                                                                        |

| 23    | 29    | DIGITAL_DIM2    | Input            | Digital Dimming input; drives strings 3 and 4. Connect to AGND in analog dimming mode.                                                                                                                                              |

Copyright © 2012 Rev. 1.2 / 20 April 2012

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

## **PRODUCTION** DATASHEET

| 24 | 30 | MO                   | 3 state input | PWM Dimming mode control selection.                                                                                                                                |

|----|----|----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25 | 31 | NC                   | Input         | Reserved , Not connect                                                                                                                                             |

| 26 | 32 | DIGITAL_DIM1         | Input         | Digital Dimming input; drives strings 1 and 2. Connect to AGND in analog dimming mode.                                                                             |

| 27 | 33 | NA                   | Input         | Test pin only. Connect to AGND.                                                                                                                                    |

| 28 | 34 | FAULT_MODE           | 3 state input | Fault Mode control                                                                                                                                                 |

| 29 | 35 | LED_ISNS4            | Input         | LED String4 current sense, resistor to PGND2. $R_S = 0.35V/I_{LED}$                                                                                                |

| 30 | 36 | LED_STR4             | Output        | LED String 4 NFET gate drive                                                                                                                                       |

| 31 | 37 | VD4                  | Input         | Connect to an isolating NFET or diode to sense String 4 NFET drain voltage.                                                                                        |

| 32 | 38 | VD3                  | Input         | Connect to an isolating NFET or diode to sense String 3 NFET drain voltage.                                                                                        |

| 33 | 39 | LED_STR3             | Output        | LED String 3 NFET gate drive                                                                                                                                       |

| 34 | 40 | LED_ISNS3            | Input         | LED String3 current sense, resistor to PGND2.  R <sub>SENSE</sub> = 0.35V/I <sub>LED</sub>                                                                         |

| 35 | 41 | COMP2                | Input         | DC/DC 2 loop compensation, R/C network to PGND2                                                                                                                    |

| 36 | 42 | OVP2                 | Input         | DC/DC2 over voltage protection threshold, connect to resistor divider between V <sub>boost2</sub> and PGND2.                                                       |

| 37 | 43 | DC_ISNS2             | Input         | DC/DC2 NFET current sense, resistor to PGND2.                                                                                                                      |

| 38 | 44 | GATE2                | Output        | DC/DC2 NFET gate control.                                                                                                                                          |

| 39 | 45 | PGND2                | Ground        | Power ground supply for DC/DC2 and strings 3 and 4.                                                                                                                |

| 40 | 46 | V <sub>HS</sub>      | Output        | Bias for internal PFET gate drivers, bypass with 1μF capacitor connected between this pin and V12V                                                                 |

| 41 | 47 | V <sub>12V</sub>     | Power         | 12V supply voltage, bypass with 4x2.2µF capacitors connected between this pin and GND plane                                                                        |

| 42 | 48 | V <sub>12VC</sub>    | Output        | Control output to drive an external transistor to generate V12V. Bypass with $1\mu F$ capacitor to AGND. If internal regulation is used, connect to $V_{12V}$ pin. |

| 43 | 1  | V <sub>IN</sub>      | Power         | High voltage supply for the 12V regulator and housekeeping bias circuitry.                                                                                         |

| 44 | 2  | V <sub>IN_UVLO</sub> | Input         | Monitors $V_{\text{IN}}$ through an external resistive voltage divider. If this function is not used connect to $V_{\text{DD}}$                                    |

| 45 | 3  | PGND1                | Ground        | Power ground supply for DC/DC1 and strings 1 and 2.                                                                                                                |

| 46 | 4  | GATE1                | Output        | DC/DC1 NFET gate control                                                                                                                                           |

| 47 | 5  | DC_ISNS1             | Input         | DC/DC1 NFET current sense                                                                                                                                          |

| 48 | 6  | OVP1                 | Input         | DC/DC1 over voltage protection threshold, connect to resistor divider between $V_{\text{boost1}}$ and PGND1.                                                       |

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

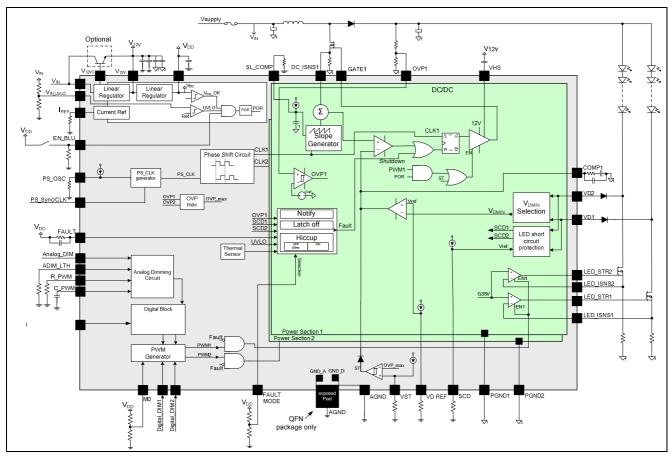

## **Functional Description**

Figure 3: Functional Block Diagram

## **Theory of Operation**

The LX23214 controls four LED strings for a D0 edge LED BLU LCD TV application. Each pair of LED strings share a dedicated DC/DC switch mode current programmed controller. The switching converter can be configured to operate in a boost topology with fixed switching frequency in a range of 100 kHz to 300 kHz.

#### Start Up

When  $V_{IN}$  is applied, the internal 12V and 5V linear regulators and the bias voltage and current generators turn on. When all the regulators and bias voltages have stabilized above their respective UVLO thresholds, the LX23214 is ready to drive the LED strings. When the  $V_{IN\_UVLO}$  and EN\_BLU rising thresholds are met, the LX23214 starts switching at the DC/DC converters.

When the OVP voltage is below the  $V_{ST}$  voltage, the DC/DC converter will be continuously enabled. This allows the boost or flyback voltage to charge up quickly with no dependency on the PWM duty cycle. Above the  $V_{ST}$  voltage, the DC/DC converter switches only when the PWM signal is asserted. The  $V_{ST}$  voltage should be selected so that it is as high as possible but always lower than the normal boost or flyback voltage range. This will give the quickest start up performance.

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

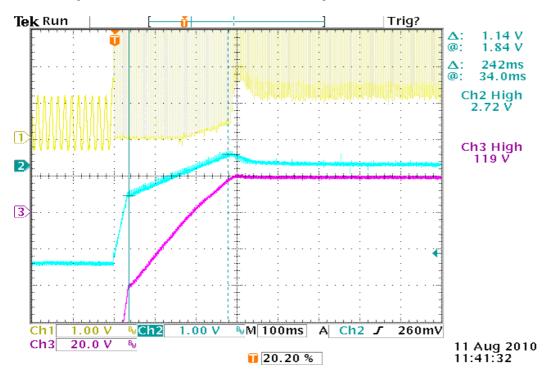

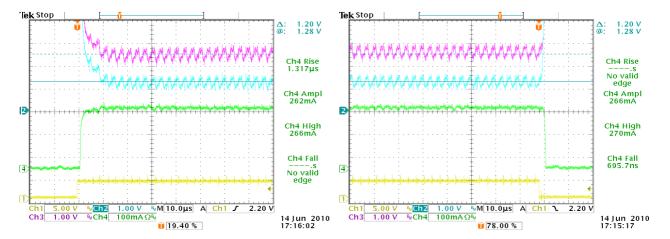

Here is a picture of the start-up sequence at 10% PWM duty cycle. Channel 1 is the NFET drain voltage, channel 2 is the COMP1 voltage, and channel 3 shows the boost1 voltage.

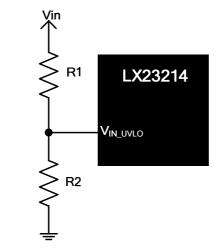

## Input under Voltage Lock out Circuit (VIN UVLO)

Input UVLO prevents the LX23214 from starting up in case the V<sub>IN</sub> input voltage is lower than a user defined threshold. Connect a voltage divider on the DC/DC input voltage and set it according to the minimal requested system operating input voltage.

Figure 4: VIN UVLO Connection Example

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

## **LED Mosfet Drain Voltage Measurements**

For each pair of LED strings, the LX23214 regulates the DC/DC output voltage so that the lowest MOSFET drain voltage matches the target value as set by VD REF pin. This target voltage should be selected so that the LED MOSFETs remain in their saturated region. Keeping this voltage as low as possible maximizes the system's power efficiency.

The LED MOSFET drain voltages are monitored through blocking diodes or blocking NFETs to protect the LX23214 from excessive voltages. ~90μA is sourced from each of the VD1-4 pins to bias external blocking diodes. If a blocking diode is used, then the voltage at the VD1-4 pins will be one diode drop above the actual LED MOSFET drain voltage. This voltage drop can be compensated for by raising VD REF pin by a matching diode voltage drop.

A comparator determines which of the two drain voltage is lowest (V<sub>DMIN</sub>). That voltage is then routed to the DC/DC error amplifier. The DC/DC control loop works to keep V<sub>DMIN</sub> equal to VD REF.

## **Power/Thermal Conditions**

The maximum LED current depends on heat sink capabilities of the external LED's MOSFETs and the allowable temperature rise.

## PWM Dimming Control

LED PWM dimming can be controlled by digital PWM signals at DIGITAL DIM1 and 2 or by an analog control voltage at ANALOG DIM. The dimming mode is determined by the M0 pin as shown in the following table:

| Pin M0 | Mode           | Remarks                                                                              |

|--------|----------------|--------------------------------------------------------------------------------------|

| 0      | Analog In +    | 0V => 4%<br>2.5V=> 100%<br>DC = V <sub>ADIM</sub> <*38.1 +4.05<br>With ADIM_LTH = 0V |

| NC     | Digital Direct | LED current is directly enabled by the DIGITAL_DIM inputs.                           |

Analog PWM dimming compares the ANALOG\_DIM voltage with a triangle wave which runs at four times the desired PWM frequency. The triangle wave has a peak of 2.5V and a valley of -0.125V when ADIM\_LTH is at 0V. The ADIM\_LTH pin allows easy control of the minimum duty cycle by adjusting the valley voltage of the triangle wave. The valley voltage will be ADIM\_LTH - 0.125V. Changing the valley voltage also changes the triangle wave frequency since the frequency is inversely proportional to the amplitude.

In digital direct mode, the LED PWM signal exactly matches the digital input at DIGITAL DIM1/2. controls strings 1 and 2. DIGITAL DIM2 controls strings 3 and 4. No filtering or synchronization occurs in this mode. The ANALOG DIM, R PWM, C PWM, and ADIM LTH pins should be left open in digital direct mode.

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

## LED string current control

The LED string NFET is controlled by the LED STR pin so that the voltage at the LED ISNS pin is 350mV when a given string is enabled. At the rising edge of the PWM signal, the LED\_STR pin is quickly charged up to turn on the LED NFET. When the PWM signal is deasserted, the LED STR pin is quickly discharged to 0V.

When the LED string is turned on, the NFET drain voltage quickly drops from the boost voltage to around 1V. It can take up to 20µS for the drain voltage to stabilize. It also takes around 3 to 4 PS clock periods for the boost inductor to charge to its steady state value. For this reason, a 10µS blanking period is used at the leading edge of the PWM signal to keep the drain voltage control loop from being disturbed. For the same reason, it is recommended that the minimum PWM pulse be greater than 20µS.

Here are pictures showing the beginning and end of a digital PWM pulse. Channel 1 = DIGPWM, Channel 2 = Vdrain1, Channel 3 = Vdrain2, Channel 4 = LED String 2 current. These pictures show how the minimum drain voltage is regulated to about 1V. The ripple on the drain voltage is due to the ESR ripple from the boost power supply. The high impedance nature of the LED current source works to reject this voltage ripple from affecting the LED string current.

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

## DC/DC boost controller

The LX23214 DC/DC boost converters operate at a constant frequency with peak current control. The minimum output pulse width is 100nS. Once started, the output pulse will terminate immediately when any of the following events occur:

- The DC\_ISNS voltage crosses 200mV.

- The DC\_ISNS voltage plus the artificial slope compensation crosses the DC/DC comparator control voltage (Vc). Vc is derived from the COMP pin via a level shift and a 5:1 attenuator.

- Maximum duty cycle has been reached. In boost mode, the maximum duty cycle is set to 90%.

## PS Switching Frequency Set (PS\_OSC)

DC/DC switching frequency and operation mode are set by a resistor at PS\_OSC pin. Frequency can be programmed from 100 kHz to 300 kHz.

| Rosc                                                  | DC/DC FREQUENCY                    | IC MODE                     |

|-------------------------------------------------------|------------------------------------|-----------------------------|

| 95.3K $\Omega$ ≥ R <sub>PS-OSC</sub> ≥ 30.1K $\Omega$ | 100kHz ≤ f <sub>OSC</sub> ≤ 300kHz | Asynchronous or Master mode |

| open                                                  | Not applicable                     | Slave mode                  |

**Note:** To disable DC/DC oscillator for synchronizing it with another LX23214 functioning as a "Master", R<sub>PS-OSC</sub> should be left open (see PS\_SYNC/CLK pin description).

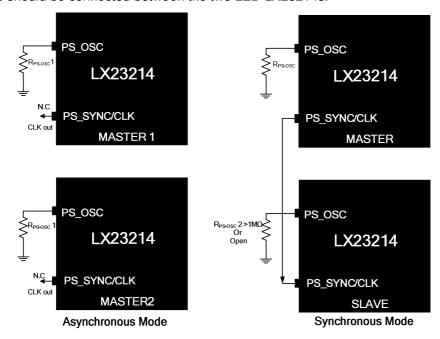

## PS Clock Synchronization (PS\_SYNC/CLK)

The PS\_SYNCH/CLK input/output is used to synchronize DC/DC converters between two LX23214 drivers within a single system.

When using two LX23214s, the DC/DC power supplies can operate in asynchronous and synchronous modes.

- Asynchronous mode The PS\_OSC frequency is not synchronized between ICs.

- Synchronous mode One LX23214 (master) generates the PS clock for the other LX23214 (slave).

Master setup: PS\_OSC resistor set for the required frequency.

Slave setup: PS OSC resistor not connected.

- PS SYNC line should be connected between the two LED LX23214s.

Figure 5: PS Asynchronous/synchronous Mode

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

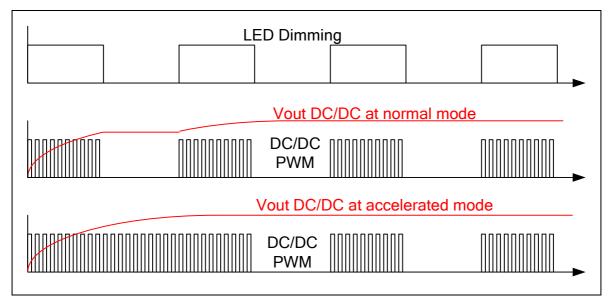

## DC/DC Start Up

There are two start up modes: Normal (slow) and Accelerated.

In Normal (slow) mode, start up time is a function of LED BL Dimming frequency and duty cycle, since LED PWM modulates DC/DC ON time.

In Accelerated mode, DC/DC starts up in open loop and operates in this mode until DC/DC voltage reaches about 80% of LED voltage (user selected). This value is programmed by a resistor connected to  $V_{ST}$ . After reaching this threshold, start up continues in normal mode, whereas DC/DC ON is modulated with PWM.

If V<sub>ST</sub> pin is connected to ground, DC/DC starts up in a normal mode.

Accelerated mode significantly reduces the startup time difference, especially when LED's dimming is working in low duty cycle.

Figure 6: Normal/Accelerated Mode

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

#### **Fault Detection and Protection**

LX23214 detects and protects against the following fault conditions:

- Over Voltage Protection of DC/DC #1 (sampled on OVP1)

- Over Voltage Protection of DC/DC #2 (sampled on OVP2)

- LED Short Circuit of Channel #1 (sampled on VD1)

- LED Short Circuit of Channel #2 (sampled on VD2)

- LED Short Circuit of Channel #3 (sampled on VD3)

- LED Short Circuit of Channel #4 (sampled on VD4)

- Open LED of Channel #1 (sampled on VD1)

- Open LED of Channel #2 (sampled on VD2)

- Open LED of Channel #3 (sampled on VD3)

- Open LED of Channel #4 (sampled on VD4)

- V<sub>in</sub> under voltage (sampled on V<sub>IN UVLO</sub>)

- IC Thermal Protection

LED short circuit conditions are detected by monitoring the LED MOSFET drain voltages when the string current is enabled. When the difference between the drain voltages for a LED string pair (VD1-VD2 or VD3-VD4) exceeds the level of four times the voltage at SCD pin, a short circuit event is declared. This differential voltage approach makes the short circuit detection immune to the DC/DC boost voltage.

LED open circuit conditions are detected by a combination of OVP pin and VD pins. When a LED string is open, the corresponding VD voltage changes to 0V. This causes the DC/DC loop to pump up the boost voltage. The high boost voltage will most likely cause the drain voltage of the non-open string to rise above short circuit detection level. This will cause a short circuit event to be declared. If both LED strings are open, the boost voltage will rise until it hits OVP protection threshold and an OVP event is declared.

There are three different fault modes, as described in Table 1.

**Table 1: Fault Modes**

| PIN FAULT_MODE       | MODE                    | ACTION                                                                                                                                  | REMARKS                                                             |

|----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| NC (Floating)        | Hiccup Fault Mode       | Turns off DC/DC that supplies faulty string. Wait for external hiccup capacitor charge to rise to predetermined level and turn on DC/DC | Both channels of the specific DC/DC turn off                        |

| 0 (AGND)             | Latch off Fault<br>Mode | Turns off DC/DC that supplies the faulty string                                                                                         | DC/DC resumes normal operation after toggling EN_BLU or power reset |

| 1 (V <sub>DD</sub> ) | Notify Fault Mode       | Activates fault signal,<br>DC/DCs are not affected                                                                                      |                                                                     |

Thermal and V<sub>IN UVLO</sub> shutdown faults turn off the LED strings until the fault condition is cleared. The FAULT pin is asserted for the duration of the fault condition.

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

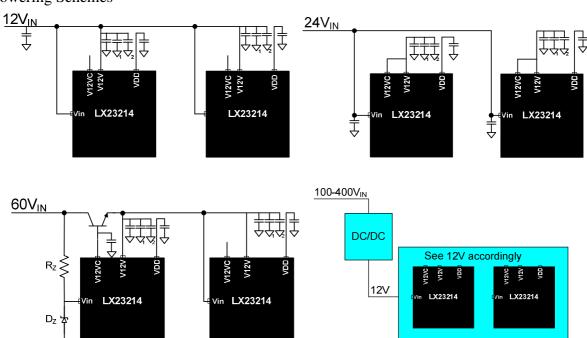

## **Typical Powering Schemes**

Figure 7: Powering Diagram

**Figure 8: Typical Application Diagram**

www.*Microsemi .*com

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

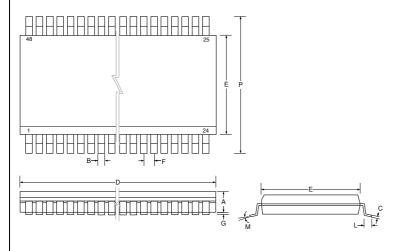

## PACKAGE DIAGRAM

## DB

## 48-Pin Small Shrink Outline Package (SSOP)

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| Dim | MIN         | MAX   | MIN       | MAX   |

| Α   | 2.18        | 2.39  | 0.086     | 0.094 |

| В   | 0.20        | 0.35  | 0.008     | 0.014 |

| С   | 0.13        | 0.25  | 0.005     | 0.010 |

| D   | 15.75       | 16.00 | 0.620     | 0.630 |

| Е   | 7.39        | 7.60  | 0.291     | 0.299 |

| F   | 0.635 BSC   |       | 0.025 BSC |       |

| G   | 0.23        | 0.38  | 0.009     | 0.015 |

| L   | 0.51        | 1.02  | 0.02      | 0.040 |

| М   | 0°          | 8°    | 0°        | 8°    |

| Р   | 10.16       | 10.41 | 0.400     | 0.410 |

| *LC | _           | 0.10  | _         | 0.004 |

<sup>\*</sup>Lead Coplanarity

#### Note:

Dimensi ns do not include mold flash or protrusions; these shall not exceed 0.155mm(.006") on any side. Lead dimension shall not include solder coverage.

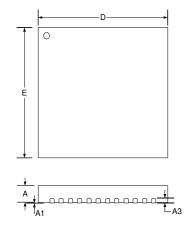

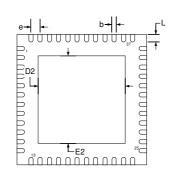

# LQ

## 48-Pin 7x7 mm QFN

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| Dim | MIN         | MAX  | MIN       | MAX   |

| Α   | 0.80        | 1.00 | 0.031     | 0.039 |

| A1  | 0           | 0.05 | 0         | 0.002 |

| A3  | 0.20 REF    |      | 0.008 REF |       |

| b   | 0.18        | 0.30 | 0.007     | 0.012 |

| D   | 7.00 BSC    |      | 0.276 BSC |       |

| D2  | 5.00        | 5.25 | 0.197     | 0.207 |

| Е   | 7.00 BSC    |      | 0.276 BSC |       |

| E2  | 5.00        | 5.25 | 0.197     | 0.207 |

| е   | 0.50 BSC    |      | 0.020 BSC |       |

| L   | 0.30        | 0.50 | 0.012     | 0.020 |

#### Note:

Dimensions do not include protrusions; these shall not exceed 0.155mm(.006") on any side. Lead dimension shall not include solder coverage.

4 Channel EDGE Lit LED Display Driver with 2 Independent DC/DC PSU Controllers

#### **PRODUCTION DATASHEET**

The information contained in the document is PROPRIETARY AND CONFIDENTIAL information of Microsemi and cannot be copied, published, uploaded, posted, transmitted, distributed or disclosed or used without the express duly signed written consent of Microsemi If the recipient of this document has entered into a disclosure agreement with Microsemi, then the terms of such Agreement will also apply . This document and the information contained herein may not be modified, by any person other than authorized personnel of Microsemi. No license under any patent, copyright, trade secret or other intellectual property right is granted to or conferred upon you by disclosure or delivery of the information, either expressly, by implication, inducement, estoppels or otherwise. Any license under such intellectual property rights must be approved by Microsemi in writing signed by an officer of Microsemi.

Microsemi reserves the right to change the configuration, functionality and performance of its products at anytime without any notice. This product has been subject to limited testing and should not be used in conjunction with life-support or other mission-critical equipment or applications. Microsemi assumes no liability whatsoever, and Microsemi disclaims any express or implied warranty, relating to sale and/or use of Microsemi products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. The product is other terms and conditions subject which can be located http://www.microsemi.com/legal/tnc.asp

#### Revision History

| Revision Level / Date | Para. Affected | Description                                 |

|-----------------------|----------------|---------------------------------------------|

| 0.1 / Dec 2010        |                | Preliminary Release                         |

| 1.0 / July 2011       |                | Release to Production                       |

| 1.1 / July 2011       |                | Adjust specs                                |

| 1.2 / April 2012      |                | Adjust specs after changes in digital block |

© 2012 Microsemi Corp. All rights reserved.

For support contact: sales AMSG@microsemi.com

Visit our web site at: www.microsemi.com Catalogue Number: DS LX23214