Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### FREQUENCY TRANSLATION PLL

#### **GENERAL DESCRIPTION**

The M2004 variants -01 and -11 are VCSO (Voltage

Controlled SAW Oscillator) based clock generator PLLs designed for clock frequency translation and jitter attenuation in a high-speed data communications system. The clock multiplication ratio and output divider ratio are pin selectable and

also configurable through serial programming. External loop components allow the tailoring of PLL loop response. The M2004-11 adds Hitless Switching with Phase Build-out (HS/PBO) to ensure that reference clock reselection does not disrupt the output clock.

Also read about device variants -21, -31, -41, and -51 in the M2004-x1 Preliminary Information sheet.

#### **FEATURES**

- ♦ Ideal for OC-48/192 data clock

- ◆ Integrated SAW (surface acoustic wave) delay line

- ♦ VCSO frequency from 300 to 700MHz (Specify VCSO center frequency at time of order)

- ◆ Low phase jitter of < 0.5ps rms, typical (12kHz to 20MHz or 50kHz to 80MHz)

- ◆ Pin-selectable or serially programmed configuration

- ◆ The M2004-11 adds Hitless Switching with Phase Build-out (HS/PBO) to ensure SONET/SDH MTIE and TDEV compliance during reference clock reselection

- ◆ Reference clock inputs support single-ended LVCMOS, LVTTL

- ♦ Industrial temperature available

- ◆ Single 3.3V power supply

- ◆ Small 9 x 9 mm SMT (surface mount) package

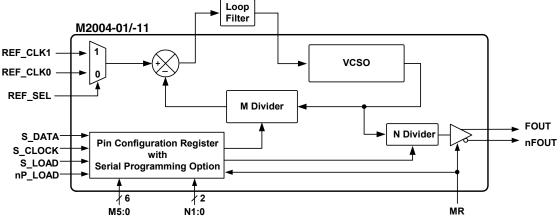

#### SIMPLIFIED BLOCK DIAGRAM

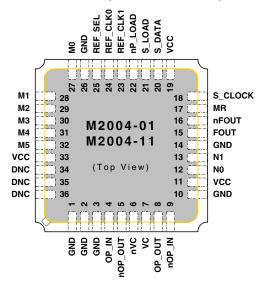

### PIN ASSIGNMENT (9 x 9 mm SMT)

Figure 1: Pin Assignment

#### **Example Input / Output Frequency Combinations**

| Input Clock<br>(MHz) | VCSO <sup>1</sup><br>Freq (MHz) | Output<br>Freq (MHz) | Application      |  |

|----------------------|---------------------------------|----------------------|------------------|--|

| 19.44                |                                 | 77.76                |                  |  |

| 38.80                | 622.08                          | 155.52               | OC-12 / 48 /192  |  |

| 77.76                | 022.00                          | 311.04               | 00 127 107102    |  |

| 155.52               |                                 | 622.08               |                  |  |

| 25.00                | 625.00                          | 156.25               | Gigabit Ethernet |  |

Table 1: Example Input / Output Frequency Combinations

Note 1: Specify VCSO center frequency at time of order

Figure 2: Simplified Block Diagram

#### **PIN DESCRIPTIONS**

| Number              | Name                        | I/O    | Configuration                             | Description                                                                                                                                                                                                                                                                          |

|---------------------|-----------------------------|--------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 10, 14, 26 | GND                         | Ground |                                           | Power supply ground connections.                                                                                                                                                                                                                                                     |

| 4<br>9              | OP_IN<br>nOP_IN             | Input  |                                           |                                                                                                                                                                                                                                                                                      |

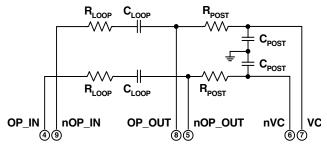

| 5<br>8              | nOP_OUT<br>OP_OUT           | Output |                                           | External loop filter connections. See Figure 5, External Loop Filter, on pg. 6.                                                                                                                                                                                                      |

| 6<br>7              | nVC<br>VC                   | Input  |                                           |                                                                                                                                                                                                                                                                                      |

| 11, 19, 33          | VCC                         | Power  |                                           | Power supply connection, connect to +3.3V.                                                                                                                                                                                                                                           |

| 12<br>13            | N0<br>N1                    | Input  | Internal pull-down resistor <sup>1</sup>  | N divider (output divider) inputs N1:0.<br>LVCMOS/LVTTL. See Table 5, Pin Selection of N<br>Divider Using N1:0 Pins, on pg. 3.                                                                                                                                                       |

| 15<br>16            | FOUT<br>nFOUT               | Output | No internal terminator                    | Clock output pair. Differential LVPECL.                                                                                                                                                                                                                                              |

| 17                  | MR                          | Input  | Internal pull-down resistor <sup>1</sup>  | Reset: Logic 1 resets M and N dividers and forces FOUT to LOW and nFOUT to HIGH. Logic 0 enables the outputs. LVCMOS/LVTTL. See Table 7, Pin Configuration & Serial Programming Functions, on pg. 5.                                                                                 |

| 18<br>20<br>21      | S_CLOCK<br>S_DATA<br>S_LOAD | Input  | Internal pull-down resistors <sup>1</sup> | Serial programming input pins. LVCMOS/LVTTL. See Table 7, Pin Configuration & Serial Programming Functions, on pg. 5 for how these three pins are used in combination.                                                                                                               |

| 22                  | nP_LOAD                     | Input  | Internal pull-down resistor <sup>1</sup>  | Pin-configuration vs. serial programming control.  Determines when data present at M5:0 and N1:0 is loaded into M and N dividers vs. when serial programming occurs. LVCMOS/LVTTL. See Table 7, Pin Configuration & Serial Programming Functions, on pg. 5 for how this pin is used. |

| 23                  | REF_CLK1                    | lanat  | Internal pull-down resistor <sup>1</sup>  | Deference also le insurte IVOMOO/IVITI                                                                                                                                                                                                                                               |

| 24                  | REF_CLK0                    | Input  | Internal pull-down resistor <sup>1</sup>  | Reference clock inputs. LVCMOS/LVTTL.                                                                                                                                                                                                                                                |

| 25                  | REF_SEL                     | Input  | Internal pull-down resistor <sup>1</sup>  | Reference clock input selection. LVCMOS/LVTTL.<br>See Table 3, Reference Clock Input Selection, on<br>pg. 3. For the M2004-11, REF_SEL triggers Hitless<br>Switching (HS/PBO) when toggled.                                                                                          |

| 27                  | M0                          |        |                                           | . , ,                                                                                                                                                                                                                                                                                |

| 28                  | M1                          |        |                                           | M divider (feedback divider) inputs M5:0. See                                                                                                                                                                                                                                        |

| 29                  | M2                          | Innut  | Internal pull-down resistor <sup>1</sup>  | Table 4. Pin Selection of M Divider Using M5:0                                                                                                                                                                                                                                       |

| 30                  | M3<br>M4                    | Input  |                                           | Pins, on pg. 3. See also Table 7, Pin Configuration                                                                                                                                                                                                                                  |

| 31                  |                             |        |                                           | & Sérial Programming Functions, on pg. 5                                                                                                                                                                                                                                             |

| 32                  | M5                          |        | Internal pull-up resistor <sup>1</sup>    |                                                                                                                                                                                                                                                                                      |

| 34, 35, 36          | DNC                         |        |                                           | Do Not Connect.                                                                                                                                                                                                                                                                      |

Note 1: For typical values of internal pull-down and pull-up resistors, see DC Characteristics on pg. 7.

Table 2: Pin Descriptions

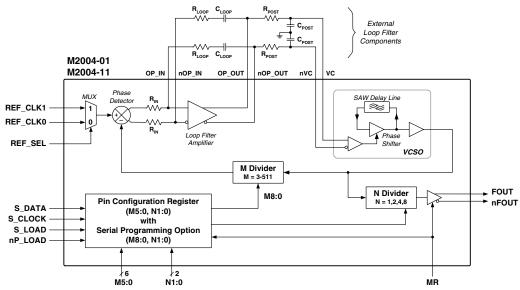

#### **DETAILED BLOCK DIAGRAM**

Figure 3: Detailed Block Diagram

#### **DEVICE CONFIGURATION TABLES**

#### **Reference Clock Input Selection**

|   | REF_SEL<br>Pin Setting<br>(Pin 25) | Reference Input Selection |

|---|------------------------------------|---------------------------|

| , | 0                                  | REF_CLK0                  |

|   | 1                                  | REF_CLK1                  |

Table 3: Reference Clock Input Selection

# M and N Pin Selection Option Pin Selection of M Divider Using M5:0 Pins

| M5:0 Pin<br>Settings <sup>1</sup><br>(Pins 32 - 27)<br>M5 - M0 | Definition                 | <b>Sample Input Clock Freq (MHz)</b> F <sub>VCSO</sub> = 622.08 <sup>2</sup> , 625.00 <sup>3</sup> |

|----------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------|

| 5 <sup>4</sup> 4 3 2 1 0                                       | Feedback Divider Value "M" |                                                                                                    |

| 0 0 0 0 1 1                                                    | M = 3 minimum              |                                                                                                    |

| 0 0 0 1 0 0                                                    | M = 4                      | 155.52 156.25                                                                                      |

| 0 0 1 0 0 0                                                    | M = 8                      | 77.76                                                                                              |

| 0 10000                                                        | M = 16                     | 38.80                                                                                              |

| 0 1 1 0 0 1                                                    | M = 25                     | 25.00                                                                                              |

| 1 00000                                                        | M = 32                     | 19.44                                                                                              |

| 1 11111                                                        | M = 63                     |                                                                                                    |

Table 4: Pin Selection of M Divider Using M5:0 Pins

Note 1: Bits M8:6 default to 0.

Note 2:  $F_{VCSO} = 622.08$  MHz (e.g., M2004-01-622.0800) Note 3:  $F_{VCSO} = 625.00$  MHz (e.g., M2004-01-625.0000) Note 4: M5 pin has a pull-up resister; M4-M0, pull-down.

# M and N Pin Selection Option (Continued) Pin Selection of N Divider Using N1:0 Pins

| N1:0 Settings<br>(Pin 13 and 12)<br>N1 N0 |   | N Divider<br>Value | Sample Output<br>Frequency (MHz) <sup>1</sup><br>(FOUT, nFOUT) |

|-------------------------------------------|---|--------------------|----------------------------------------------------------------|

| 0                                         | 0 | 1                  | 622.08                                                         |

| 0                                         | 1 | 2                  | 311.04                                                         |

| 1                                         | 0 | 4                  | 155.52                                                         |

| 1                                         | 1 | 8                  | 77.76                                                          |

Table 5: Pin Selection of N Divider Using N1:0 Pins Note 1:  $F_{VCSO} = 622.08MHz$  (e.g., M2004-01-622.0800)

#### Serial Programming Alternative (Using S\_DATA Pin)

| Serial<br>Bits | Settings per<br>Bit     | Defin                     | ition           |

|----------------|-------------------------|---------------------------|-----------------|

| T1:0           | 10<br>00                | Normal/Test<br>Normal Ope |                 |

| *No            | te: T1 and T0, used for | -                         |                 |

| N1:0           | 10                      | Output Divid              | ler Value "N"   |

|                | 0 0                     | N = 1                     | minimum         |

|                | 1 1                     | N = 8                     | maximum         |

| M8:0           | 876543210               | Feedback Di               | vider Value "M" |

| (              | 000000011               | M = 3                     | minimum         |

|                | 00010000                | M = 32                    |                 |

| (              | 000111111               | M = 63                    |                 |

|                | 11111111                | M = 511                   | maximum         |

Table 6: Serial Programming Alternative (Using S\_DATA Pin)

#### **FUNCTIONAL DESCRIPTION**

The M2004-01/-11 is a PLL (Phase Locked Loop) based clock generator that generates output clocks synchronized to one of two selectable input reference clocks. An internal high "Q" SAW delay line provides a low jitter clock signal.

The device can be pin-configured for feedback divider and output divider values. These divider values can also be set through serial programming. Output is LVPECL compatible. External loop filter component values set the PLL bandwidth to optimize jitter attenuation characteristics.

The M2004-11 adds Hitless Switching with Phase Build-out (HS/PBO) to provide SONET/SDH MTIE and TDEV compliance during a reference clock reselection using the internal mux or when using an external mux.

The M2004-01/-11 is ideal for clock jitter attenuation and frequency translation in 2.5 or 10 Gb optical network line card applications.

#### **Input Reference Clocks**

An internal input MUX is provided for input reference clock selection. One input reference clock is selected from between two single-ended LVCMOS / LVTTL clock inputs. The maximum input frequency is 175MHz.

#### **PLL Operation**

The M2004-01/-11 is a complete clock PLL. It uses a phase detector and configurable dividers to synchronize the output of the VCSO with the selected reference clock.

The "M Divider" divides the VCSO output frequency, feeding the result into the phase detector. The selected input reference clock is fed into the other input of the phase detector. The phase detector compares its two inputs. It then causes the VCSO to increase or decrease in speed as needed to phase- and frequency-lock the VCSO to the reference input.

The value of M directly affects closed loop bandwidth.

#### The M Divider

The relationship between the VCSO center frequency (Fvcso), the M divider, and the input reference frequency (Fref\_clk) is:

$$Fvcso = Fref clk \times M$$

The product of M and the input frequency must be such that it falls within the "lock" range of the VCSO.

See APR in AC Characteristics on pg. 8.

#### **N Divider and Outputs**

The M2004-01/-11 provides one differential LVPECL output pair: FOUT, nFOUT. By using the N divider, the output frequency can be the VCSO center frequency (Fvcso) or 1/2, 1/4, or 1/8 Fvcso.

The N1 and N0 pins select the value for the N divider.

See Table 5, Pin Selection of N Divider Using N1:0 Pins, on pg. 3.

When the N divider is included, the complete relationship for the output frequency (Fout) is defined as:

$Fout = \frac{Fvcso}{N} = Fref_clk \times \frac{M}{N}$

#### Configuration of M and N Dividers

The M and N dividers can be set by pin configuration or serial programming. The divider configuration of the M2004-01/-11 is reset when the input pin MR is set HIGH. MR is set LOW for divider configuration to be operational.

See Table 7, Pin Configuration & Serial Programming Functions, on pg. 5.

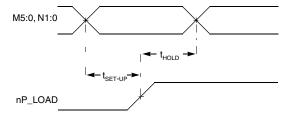

#### Pin Configuration M and N Dividers

The M2004-01/-11 can be pin-configured with the input pins M0 - M5, N0, and N1.

Pin configuration of dividers occurs when nP\_LOAD is LOW. The data on pins M5:0 and pins N1:0 is passed transparently (directly) to the M and N dividers.

On the LOW-to-HIGH (rising edge) transition of the nP LOAD input, the data is latched.

With nP\_LOAD set HIGH, the pin-configured values remain loaded in the M and N dividers; the dividers are unaffected by any change to the M5:0 or N1:0 inputs. As a result, the M5:0 and N1:0 pins can be used to set the power-up default values for M and N. (The dividers are also unaffected by any S\_DATA serial input as long as there is no rising edge transition of S\_LOAD.)

See Table 7, Pin Configuration & Serial Programming Functions, on pg. 5. See also Figure 8, Times for M5:0 and N1:0, on pg. 9.

#### **Serial Programming of M and N Dividers**

The M2004-01/-11 is serially programmed with S\_DATA, S\_CLOCK, and S\_LOAD.

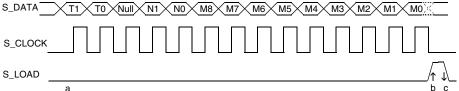

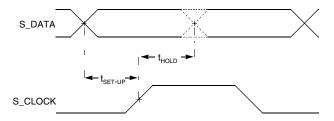

See Figure 4, Serial Configuration Timing Diagram, below.

Serial input mode is enabled when nP\_LOAD is HIGH and S\_LOAD is LOW (at point "a" in the the timing diagram, Figure 4). Data on the S\_DATA input pin is serially loaded into the configuration shift register with each rising edge of the S\_CLOCK input. (The T1 bit is input first, M0 last.)

When the shift register is full, its entire contents is loaded in parallel into the M and N dividers. This occurs on the rising edge of the S\_LOAD input (at point "b" in the timing diagram). This load is transparent; the dividers immediately contain the serially programmed values.

If S\_LOAD is held HIGH, any S\_DATA input is passed transparently (directly) to the M and N dividers on each rising edge of S\_CLOCK.

The data is latched on the falling edge transition of the S\_LOAD input (at point "c" in the timing diagram). With S\_LOAD set LOW, the serially programmed values remain in the M and N dividers, unaffected by any serial pin input.

See Table 7, Pin Configuration & Serial Programming Functions, below. See also Figure 8, Times for M5:0 and N1:0, on pg. 9.

#### **Pin Configuration & Serial Programming Functions**

L = Low; H = High; X = Don't care; ↑ = Rising Edge Transition; ↓ = Falling Edge Transition

|          |                 |           | Pin     |        |         |        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------------|-----------|---------|--------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MR       | nP_LOAD         | M5:0      | N1:0    | S_LOAD | S_CLOCK | S_DATA | . anotion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Н        | Χ               | Χ         | Χ       | Χ      | Χ       | Χ      | Resets the dividers and forces FOUT to LOW and nFOUT to HIGH. $\label{eq:control} % \begin{center} cent$ |

| Pin Con  | figuration of N | l and N D | ividers |        |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| L        | L               | Data      | Data    | Х      | Χ       | Χ      | Data on M5:0 and N1:0 input pins is passed directly (and become immediately transparent) to the M and N dividers respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| L        | 1               | Data      | Data    | L      | Х       | Х      | Data is latched into M and N dividers and remains loaded until next HIGH-to-LOW transition of nP_LOAD or a serial load occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Serial P | rogramming o    | f M and N | Divider | S      |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| L        | Н               | Χ         | Χ       | L      | 1       | Data   | Serial input mode. Data on the S_DATA pin is serially loaded into the shift register on each rising clock of S_CLOCK. (However, serial input does not affect the values in the M and N dividers.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| L        | Н               | Χ         | Χ       | 1      | L       | Data   | Entire contents of the shift register are passed (and become immediately transparent) to the M and N dividers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| L        | Н               | Χ         | Χ       | 1      | L       | Data   | M and N divider values are latched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| L        | Н               | Χ         | Χ       | L      | Χ       | Χ      | Serial input does not affect the values in the M and N dividers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| L        | Н               | Χ         | Χ       | Н      | 1       | Data   | Serial input affects dividers: S_DATA passed directly to M and N dividers as it is clocked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 7: Pin Configuration & Serial Programming Functions

#### **Serial Configuration Timing Diagram**

Points a, b, and c referred to in "Serial Programming of M and N Dividers" description above. The T1 bit is loaded first, M0 last.

Figure 4: Serial Configuration Timing Diagram

#### Hitless Switching and Phase Build-out \*

A proprietary automatic Hitless Switching (HS) function is included in the M2004-11. The HS function provides SONET/SDH MTIE and TDEV compliance during a reference clock reselection using the internal mux or when using an external mux (through detection of the resulting phase transient).\*\* A Phase Build-out (PBO) function is also incorporated to absorb most of the phase change in the reference clock input.

The combined HS/PBO function is armed after the device locks to the input clock reference. Once armed, HS/PBO is triggered by either:

- Changing REF\_SEL to switch the input reference clock.

- Detection at the phase detector of an input phase transient beyond 4 ns.

Once triggered, the HS function narrows loop bandwidth to control MTIE during locking to the new input phase. With proper configuration of the external loop filter, the output clocks will comply with MTIE and TDEV specifications for GR-253 (SONET) and ITU G.813 (SDH) during input reference clock changes.

The Phase Build-out (PBO) function enables the PLL to absorb most of the phase change of the input clock. The PBO function selects a new VCSO clock edge for the phase detector feedback clock, selecting the edge closest in phase to the new input clock phase. This reduces re-lock time, the generation of wander, and extra output clock cycles.

Note \*: The M2004-01 does not include HS/PBO.

Note \*\*:Transient-triggered HS/PBO is not suitable for use with an unstable reference clock that would induce phase jitter beyond 2 ns at the phase detector (e.g., Stratum DPLL clock sources and unstable recovered network clocks intended for loop timing configuration). Therefore, the M2004-11 also offers the internal mux-triggered HS/PBO capability.

When the PLL locks to within 2 ns of the input clock phase, the PLL returns to normal loop bandwidth and the HS/PBO function is re-armed.

#### **External Loop Filter**

To provide stable PLL operation, and thereby a low jitter output clock, the M2004-01/-11 requires the use of an external loop filter components. These are connected to the provided filter pins (see Figure 5). Due to the differential signal path design, the implementation consists of two identical complementary RC filters as shown in Figure 5, below.

Figure 5: External Loop Filter

PLL bandwidth is affected by the "M" value as well as the VCSO frequency. See Table 8, External Loop Filter Component Values M2004-01/-11, on pg. 6.

#### **PLL Simulator Tool Available**

A free PC software utility is available on the ICS website (www.icst.com). The M2000 Timing Modules PLL Simulator is a downloadable application that simulates PLL jitter and wander transfer characteristics. This enables the user to set appropriate external loop component values in a given application.

#### External Loop Filter Component Values <sup>1</sup> M2004-01/-11

VCSO Parameters:  $K_{VCO}$  = 800kHz/V,  $R_{IN}$  = 16k $\Omega$ , VCSO Bandwidth = 700kHz. See AC Characteristics on pg. 8 for PLL Loop Constants.

| Device Configuration                                              |        |        | Example External Loop Filter Component Values |         |                       |                   | Nominal Performance Using These Values |     |      |  |

|-------------------------------------------------------------------|--------|--------|-----------------------------------------------|---------|-----------------------|-------------------|----------------------------------------|-----|------|--|

| F <sub>Ref</sub> F <sub>VCSO</sub> M Divider<br>(MHz) (MHz) Value |        | R loop |                                               |         | PLL Loop<br>Bandwidth | Damping<br>Factor | Passband<br>Peaking (dB)               |     |      |  |

| 19.44                                                             | 622.08 | 32     | 13kΩ                                          | 0.47μF  | 33k $\Omega$          | 220pF             | 3.8kHz                                 | 5.6 | 0.06 |  |

| 19.44                                                             | 622.08 | 32     | 39k $\Omega$                                  | 0.022μF | 20k $\Omega$          | 220pF             | 12.7kHz                                | 7.7 | 0.03 |  |

| 19.44                                                             | 622.08 | 32     | $2.2 \mathrm{k}\Omega$                        | 10.0μF  | 22k $\Omega$          | 3300pF            | 710Hz                                  | 4.4 | 0.10 |  |

| 155.52                                                            | 622.08 | 4      | 3.9kΩ                                         | 0.47μF  | 39kΩ                  | 100pF             | 11.0kHz                                | 4.7 | 0.09 |  |

| 155.52                                                            | 622.08 | 4      | 750Ω                                          | 10.0μF  | 7.5k $\Omega$         | 1000pF            | 1.6kHz                                 | 4.2 | 0.10 |  |

Table 8: External Loop Filter Component Values M2004-01/-11

Note 1: K<sub>VCO</sub>, VCSO Bandwidth, M Divider Value, and External Loop Filter Component Values determine Loop Bandwidth, Damping Factor, and Passband Peaking. For PLL Simulator software, go to www.icst.com.

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Symbol          | Parameter            | Rating                       | Unit |

|-----------------|----------------------|------------------------------|------|

| V <sub>I</sub>  | Inputs               | -0.5 to $V_{\rm CC}$ +0.5    | V    |

| V <sub>O</sub>  | Outputs              | -0.5 to V <sub>CC</sub> +0.5 | V    |

| V <sub>CC</sub> | Power Supply Voltage | 4.6                          | V    |

| T <sub>S</sub>  | Storage Temperature  | -45 to +100                  | °C   |

Table 9: Absolute Maximum Ratings

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings ard stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in Recommended Conditions of Operation, DC Characteristics, or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### RECOMMENDED CONDITIONS OF OPERATION

| Symbo           | ol Parameter                  | Min   | Тур | Max   | Unit |

|-----------------|-------------------------------|-------|-----|-------|------|

| V <sub>cc</sub> | Positive Supply Voltage       | 3.135 | 3.3 | 3.465 | ٧    |

| T,              | Ambient Operating Temperature |       |     |       |      |

| ^               | Commercial                    | 0     |     | +70   | °C   |

|                 | Industrial                    | -40   |     | +85   | °C   |

Table 10: Recommended Conditions of Operation

### **ELECTRICAL SPECIFICATIONS**

#### **DC Characteristics**

Unless stated otherwise,  $V_{CC} = 3.3V \pm 5\%$ ,  $T_A = 0$  °C to +70 °C (commercial),  $F_{VCSO} = F_{OUT} = 622$ -675MHz, Outputs terminated with 50 $\Omega$  to  $V_{CC}$  - 2V  $T_A = -40$  °C to +85 °C (industrial)

|                 | Symbol                | Parameter                   |                                                             | Min                   | Тур | Max                   | Unit | Conditions                          |

|-----------------|-----------------------|-----------------------------|-------------------------------------------------------------|-----------------------|-----|-----------------------|------|-------------------------------------|

| Power Supply    | v V <sub>CC</sub>     | Positive Supply Voltage     |                                                             | 3.135                 | 3.3 | 3.465                 | ٧    |                                     |

|                 | I <sub>cc</sub>       | Power Supply Current        |                                                             |                       | 162 |                       | mA   | _                                   |

| LVCMOS /        | V <sub>IH</sub>       | Input High Voltage          | REF_CLK0, REF_CLK1,                                         | 2                     |     | V <sub>cc</sub> + 0.3 | V    |                                     |

| LVTTL<br>Inputs | V <sub>IL</sub>       | Input Low Voltage           | REF_SEL, MR, nP_LOAD, S_LOAD, S_CLOCK, S_DATA, N0:N1, M0:M5 | -0.3                  |     | 1.3                   | ٧    |                                     |

| Inputs with     | I <sub>IH</sub>       | Input High Current          | REF_CLK0, REF_CLK1,                                         |                       |     | 150                   | μΑ   | V <sub>CC</sub> = V <sub>IN</sub> = |

| Pull-down       | I <sub>IL</sub>       | Input Low Current           | REF_SEL, MR, nP_LOAD, S_LOAD, S_CLOCK, S_DATA, N0:N1, M0:M4 | -5                    |     |                       | μΑ   | - 3.456V                            |

|                 | R <sub>pulldown</sub> | Internal Pull-down Resistor |                                                             |                       | 51  |                       | kΩ   |                                     |

| Inputs with     | I <sub>IH</sub>       | Input High Current          |                                                             |                       |     | 5                     | μΑ   | V <sub>CC</sub> = 3.456V            |

| Pull-up         | I <sub>IL</sub>       | Input Low Current           | M5                                                          | -150                  |     |                       | μΑ   | $V_{IN} = 0 V$                      |

|                 | R <sub>pullup</sub>   | Internal Pull-up Resistor   |                                                             |                       | 51  |                       | kΩ   |                                     |

| All Inputs      | C <sub>IN</sub>       | Input Capacitance           | All Inputs                                                  |                       |     | 4                     | pF   |                                     |

| Differential    | $V_{OH}$              | Output High Voltage         |                                                             | V <sub>cc</sub> - 1.4 |     | V <sub>cc</sub> - 1.0 | ٧    |                                     |

| Outputs         | V <sub>OL</sub>       | Output Low Voltage          | FOUT, nFOUT                                                 | V <sub>cc</sub> - 2.0 |     | V <sub>cc</sub> - 1.7 | V    |                                     |

|                 | V <sub>P-P</sub>      | Peak to Peak Output Voltag  | e <sup>1</sup>                                              | 0.4                   |     | 0.85                  | V    |                                     |

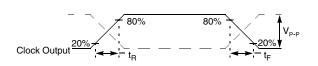

Note 1: Single-ended measurement. See Figure 6, Output Rise and Fall Time on pg. 9.

Table 11: DC Characteristics

### **ELECTRICAL SPECIFICATIONS (CONTINUED)**

**AC Characteristics**

Unless stated otherwise,  $V_{CC} = 3.3V \pm 5\%$ ,  $T_A = 0$  °C to +70 °C (commercial),  $F_{VCSO} = F_{OUT} = 622$ -675MHz, Outputs terminated with  $50\Omega$  to  $V_{CC}$  - 2V  $T_A = -40$  °C to +85 °C (industrial)

| Constants 1 R <sub>IN</sub>                           | PR  vco  in  W <sub>vcso</sub> | Input Frequency  Output Frequency  VCSO Pull-Range  VCO Gain  Internal Loop Resistor  VCSO Bandwidth  Single Side Band Phase Noise @ 622.08MHz | REF_CLK0, REF_CLK1 S_CLOCK FOUT, nFOUT Commercial Industrial  1kHz Offset 10kHz Offset | 1<br>38<br>±120<br>±50 | ±200<br>±150<br>800<br>16<br>700 | 175<br>50<br>700 | MHz MHz MHz ppm ppm kHz/V kΩ kHz dBc/Hz |            |

|-------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|----------------------------------|------------------|-----------------------------------------|------------|

| PLL Loop Constants 1  R <sub>IN</sub> BW  Phase Noise | PR vvco in Wvcso vn            | VCSO Pull-Range  VCO Gain  Internal Loop Resistor  VCSO Bandwidth  Single Side Band  Phase Noise  @ 622.08MHz                                  | FOUT, nFOUT  Commercial Industrial  1kHz Offset 10kHz Offset                           | ±120                   | ±150<br>800<br>16<br>700         |                  | MHz ppm ppm kHz/V kΩ kHz                |            |

| PLL Loop Constants 1  R <sub>IN</sub> BW  Phase Noise | PR vvco in Wvcso vn            | VCSO Pull-Range  VCO Gain  Internal Loop Resistor  VCSO Bandwidth  Single Side Band  Phase Noise  @ 622.08MHz                                  | Commercial Industrial  1kHz Offset 10kHz Offset                                        | ±120                   | ±150<br>800<br>16<br>700         | 700              | ppm<br>ppm<br>kHz/V<br>kΩ<br>kHz        |            |

| PLL Loop Constants 1  R <sub>IN</sub> BW  Phase Noise | vco IN W <sub>vcso</sub>       | VCO Gain Internal Loop Resistor VCSO Bandwidth Single Side Band Phase Noise @ 622.08MHz                                                        | 1kHz Offset 10kHz Offset                                                               |                        | ±150<br>800<br>16<br>700         |                  | ppm<br>kHz/V<br>kΩ<br>kHz               |            |

| PLL Loop Constants 1  R <sub>IN</sub> BW  Phase Noise | vco IN W <sub>vcso</sub>       | VCO Gain Internal Loop Resistor VCSO Bandwidth Single Side Band Phase Noise @ 622.08MHz                                                        | 1kHz Offset<br>10kHz Offset                                                            | ±50                    | 800<br>16<br>700                 |                  | kHz/V<br>kΩ<br>kHz                      |            |

| PLL Loop Constants 1 R <sub>IN</sub> BW  Phase Noise  | W <sub>VCSO</sub>              | Internal Loop Resistor VCSO Bandwidth Single Side Band Phase Noise @ 622.08MHz                                                                 | 10kHz Offset                                                                           |                        | 16<br>700                        |                  | kΩ<br>kHz                               |            |

| Constants 1 H <sub>IN</sub> BW  Phase Noise           | W <sub>VCSO</sub>              | VCSO Bandwidth Single Side Band Phase Noise @ 622.08MHz                                                                                        | 10kHz Offset                                                                           |                        | 700                              |                  | kHz                                     | -          |

| Фr<br>Phase Noise                                     | n                              | Single Side Band<br>Phase Noise<br>@622.08MHz                                                                                                  | 10kHz Offset                                                                           |                        |                                  |                  |                                         |            |

| Phase Noise                                           |                                | Phase Noise<br>@622.08MHz                                                                                                                      | 10kHz Offset                                                                           |                        | -72                              |                  | dBc/Hz                                  |            |

|                                                       |                                | @622.08MHz                                                                                                                                     |                                                                                        |                        |                                  |                  |                                         |            |

|                                                       | (t)                            |                                                                                                                                                |                                                                                        |                        | -94                              |                  | dBc/Hz                                  |            |

| i and Jiller                                          | (t)                            |                                                                                                                                                | 100kHz Offset                                                                          |                        | -123                             |                  | dBc/Hz                                  |            |

| J(t)                                                  |                                | Jitter (rms)                                                                                                                                   | 12kHz to 20MHz                                                                         |                        | 0.5                              |                  | ps                                      |            |

|                                                       |                                |                                                                                                                                                | 50kHz to 80MHz                                                                         |                        | 0.5                              |                  | ps                                      |            |

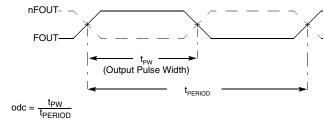

| ode                                                   | dc                             | Output Duty Cycle <sup>2</sup>                                                                                                                 | N = 2, 4, or 8                                                                         | 45                     | 50                               | 55               | %                                       |            |

|                                                       |                                |                                                                                                                                                | N = 1                                                                                  | 40                     | 50                               | 60               | %                                       |            |

|                                                       |                                | Output Rise Time <sup>2</sup>                                                                                                                  | F <sub>OUT</sub> =155.52MHz N = 4 (N1:0 = 10)                                          | 350                    | 450                              | 550              | ps                                      |            |

| t <sub>R</sub>                                        |                                | for FOUT, nFOUT                                                                                                                                | F <sub>OUT</sub> =311.04MHz N = 2 (N1:0 = 01)                                          | 325                    | 425                              | 500              | ps                                      | 20% to 80% |

|                                                       |                                |                                                                                                                                                | F <sub>OUT</sub> =622.08MHz N = 1 (N1:0 = 00)                                          | 200                    | 275                              | 350              | ps                                      | •          |

|                                                       |                                | <b>. .</b>                                                                                                                                     | F <sub>OUT</sub> =155.52MHz N = 4 (N1:0 = 10)                                          | 350                    | 450                              | 550              | ps                                      |            |

| t <sub>F</sub>                                        |                                | Output Fall Time <sup>2</sup> for FOUT, nFOUT                                                                                                  | F <sub>OUT</sub> =311.04MHz N = 2 (N1:0 = 01)                                          | 325                    | 425                              | 500              | ps                                      | 20% to 80% |

|                                                       |                                |                                                                                                                                                | F <sub>OUT</sub> =622.08MHz N = 1 (N1:0 = 00)                                          | 200                    | 275                              | 350              | ps                                      | •          |

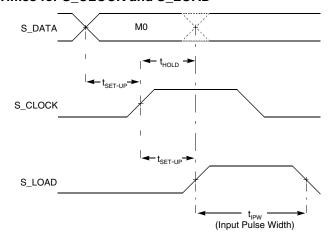

| +                                                     |                                | Setup Time <sup>3</sup>                                                                                                                        | M5:0, N1:0 to nP_LOAD                                                                  | _ 5                    |                                  |                  | ns                                      |            |

| 'SE                                                   | ETUP                           | Octup Time                                                                                                                                     | S_DATA to S_CLOCK                                                                      | _ 3                    |                                  |                  | 113                                     |            |

|                                                       |                                | _                                                                                                                                              | M5:0, N1:0 to nP_LOAD                                                                  |                        |                                  |                  |                                         |            |

| t <sub>HO</sub>                                       | OLD                            | Hold Time <sup>3</sup>                                                                                                                         | S_DATA to S_CLOCK                                                                      | 5                      |                                  |                  | ns                                      |            |

|                                                       |                                |                                                                                                                                                | S_CLOCK to S_LOAD                                                                      | <del>_</del>           |                                  |                  |                                         |            |

| t <sub>IPV</sub>                                      | PW                             | Input Pulse Width <sup>4</sup>                                                                                                                 | S_LOAD                                                                                 | 10                     |                                  |                  | ns                                      |            |

| t <sub>LO0</sub>                                      | OCK                            | PLL Lock Time                                                                                                                                  |                                                                                        |                        |                                  | 100              | ms                                      |            |

|                                                       |                                | Mean Time Interval Erro                                                                                                                        | or <sup>5</sup> M2004-11                                                               |                        | Complia                          | nt with GI       | R-253-C                                 | ORE        |

Table 12: AC Characteristics

Note 1: Parameters needed for PLL Simulator software; see Table 8, External Loop Filter Component Values M2004-01/-11 on pg. 6.

Note 2: See Parameter Measurement Information on pg. 9.

Note 3: See Figure 8, Times for M5:0 and N1:0 and Figure 9, Times for S\_DATA on pg. 9.

Note 4: See Figure 9, Times for S\_DATA on pg. 9.

Note 5: Requires proper loop filter settings. Consult factory.

#### PARAMETER MEASUREMENT INFORMATION

#### **Output Rise and Fall Time**

Figure 6: Output Rise and Fall Time

# Output Duty Cycle

Figure 7: Output Duty Cycle

#### Times for M5:0 and N1:0

Figure 8: Times for M5:0 and N1:0

#### Times for S DATA

Figure 9: Times for S\_DATA

#### Times for S\_CLOCK and S\_LOAD

Figure 10: Times for S\_CLOCK and S\_LOAD

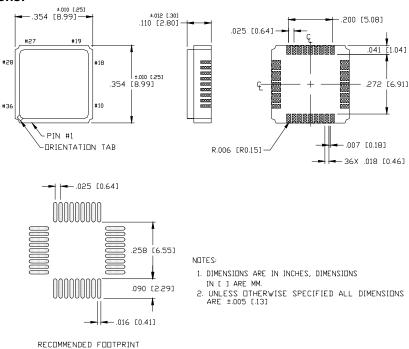

#### DEVICE PACKAGE - 9 x 9mm CERAMIC LEADLESS CHIP CARRIER

#### **Mechanical Dimensions:**

Figure 11: Device Package - 9 x 9mm Ceramic Leadless Chip Carrier

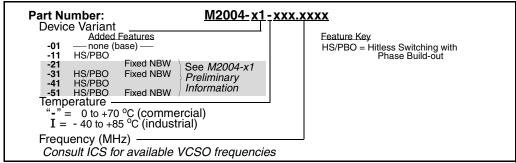

#### **ORDERING INFORMATION**

Figure 12: Ordering Information

#### **Example Part Numbers**

| For VCSO Freq (MHz) | Temperature | Part Number                              |

|---------------------|-------------|------------------------------------------|

| 622.08              | commercial  | M2004-01-622.0800 or M2004-11-622.0800   |

|                     | industrial  | M2004-01I 622.0800 or M2004-11I 622.0800 |

**Table 13: Example Part Numbers**

Consult ICS for the availability of other VCSO frequencies.

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.