Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 5 V, 16 Kbit (2 Kb x 8) ZEROPOWER® SRAM

### **Features**

- Integrated, ultra low power SRAM and powerfail control circuit

- Unlimited WRITE cycles

- READ cycle time equals WRITE cycle time

- Automatic power-fail chip deselect and WRITE protection

- WRITE protect voltages (V<sub>PFD</sub> = power-fail deselect voltage):

- M48Z02:  $V_{CC}$ = 4.75 to 5.5 V; 4.5 V  $\leq$  V<sub>PFD</sub>  $\leq$  4.75 V

- M48Z12:  $V_{CC}$ = 4.5 to 5.5 V; 4.2 V  $\leq$   $V_{PFD}$   $\leq$  4.5 V

- Self-contained battery in the CAPHAT<sup>™</sup> DIP package

- Pin and function compatible with JEDEC standard 2 K x 8 SRAMs

- RoHS compliant

- Lead-free second level interconnect

Contents M48Z02, M48Z12

## **Contents**

| 1 | Description                                             | 5  |

|---|---------------------------------------------------------|----|

| 2 | Operation modes                                         | 7  |

|   | 2.1 READ mode                                           | 7  |

|   | 2.2 WRITE mode                                          | 8  |

|   | 2.3 Data retention mode                                 | 10 |

|   | 2.4 V <sub>CC</sub> noise and negative going transients | 12 |

| 3 | Maximum ratings                                         | 13 |

| 4 | DC and AC parameters                                    | 14 |

| 5 | Package mechanical data                                 | 17 |

| 6 | Part numbering                                          | 19 |

| 7 | Environmental information                               | 20 |

| 8 | Revision history                                        | 21 |

M48Z02, M48Z12 List of tables

## **List of tables**

| Table 1.  | Signal names                                                           |    |

|-----------|------------------------------------------------------------------------|----|

| Table 2.  | Operating modes                                                        | 7  |

| Table 3.  | READ mode AC characteristics                                           | 8  |

| Table 4.  | WRITE mode AC characteristics                                          | 10 |

| Table 5.  | Absolute maximum ratings                                               | 13 |

| Table 6.  | Operating and AC measurement conditions                                |    |

| Table 7.  | Capacitance                                                            |    |

| Table 8.  | DC characteristics                                                     | 15 |

| Table 9.  | Power down/up AC characteristics                                       |    |

| Table 10. | Power down/up trip points DC characteristics                           | 16 |

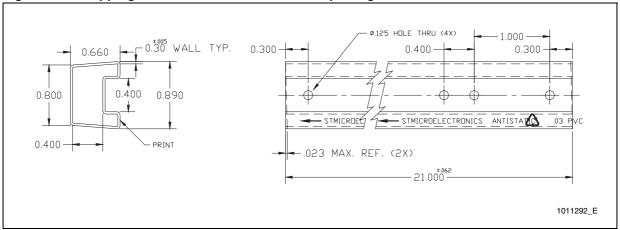

| Table 11. | PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package mechanical data | 17 |

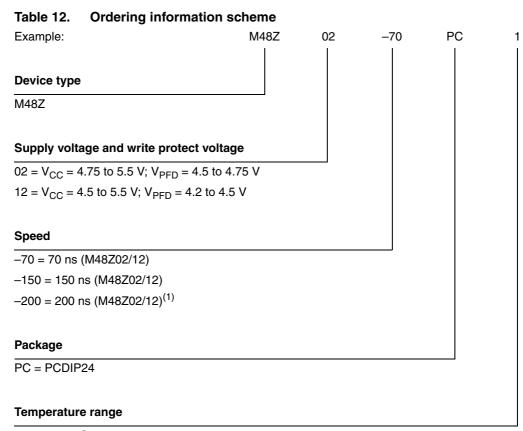

| Table 12. | Ordering information scheme                                            | 19 |

| Table 13. | Document revision history                                              | 21 |

List of figures M48Z02, M48Z12

# **List of figures**

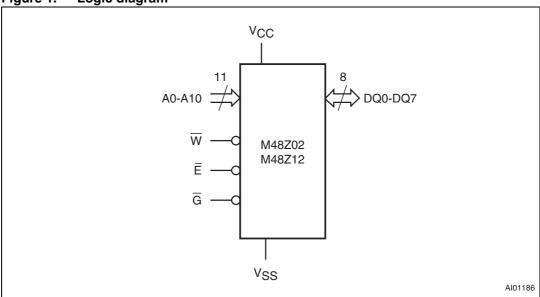

| Figure 1.  | Logic diagram                                                  | 5    |

|------------|----------------------------------------------------------------|------|

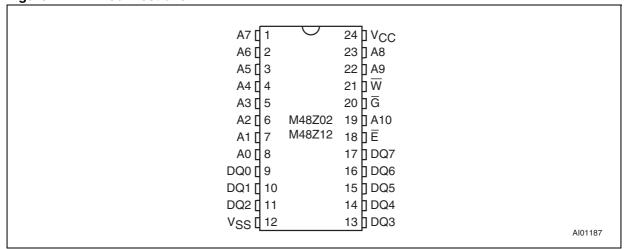

| Figure 2.  | DIP connections                                                | 6    |

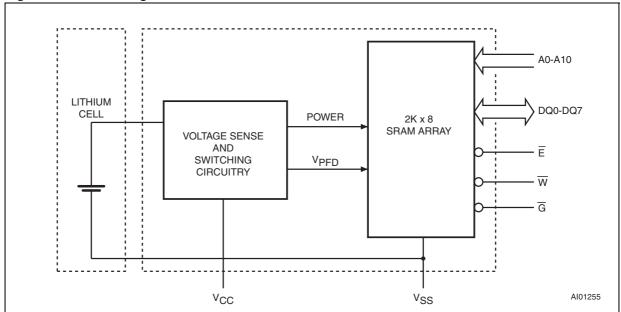

| Figure 3.  | Block diagram                                                  | 6    |

| Figure 4.  | READ mode AC waveforms                                         | 8    |

| Figure 5.  | WRITE enable controlled, WRITE AC waveform                     | 9    |

| Figure 6.  | Chip enable controlled, WRITE AC waveforms                     | 9    |

| Figure 7.  | Checking the BOK flag status                                   | . 11 |

| Figure 8.  | Supply voltage protection                                      | . 12 |

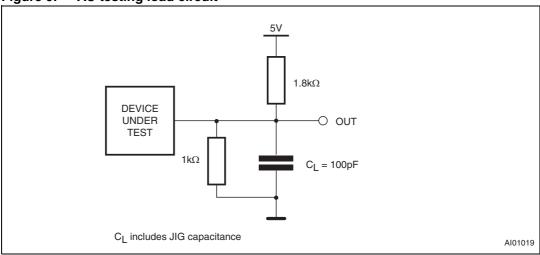

| Figure 9.  | AC testing load circuit                                        | . 14 |

| Figure 10. | Power down/up mode AC waveforms                                | . 15 |

| Figure 11. | PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package outline | . 17 |

| Figure 12. | Shipping tube dimensions for PCDIP24 package                   | . 18 |

| Figure 13  | Pocycling symbols                                              | 20   |

M48Z02, M48Z12 Description

### 1 Description

The M48Z02/12 ZEROPOWER $^{\circledR}$  RAM is a 2 K x 8 non-volatile static RAM which is pin and function compatible with the DS1220.

A special 24-pin, 600 mil DIP CAPHAT™ package houses the M48Z02/12 silicon with a long-life lithium button cell to form a highly integrated battery-backed memory solution.

The M48Z02/12 button cell has sufficient capacity and storage life to maintain data functionality for an accumulated time period of at least 10 years in the absence of power over commercial operating temperature range.

The M48Z02/12 is a non-volatile pin and function equivalent to any JEDEC standard 2 K x 8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the non-volatility of PROMs without any requirement for special WRITE timing or limitations on the number of WRITEs that can be performed.

Table 1. Signal names

| A0-A10          | Address inputs        |

|-----------------|-----------------------|

| DQ0-DQ7         | Data inputs / outputs |

| Ē               | Chip enable           |

| G               | Output enable         |

| W               | WRITE enable          |

| V <sub>CC</sub> | Supply voltage        |

| V <sub>SS</sub> | Ground                |

Description M48Z02, M48Z12

Figure 2. DIP connections

Figure 3. Block diagram

M48Z02, M48Z12 Operation modes

### 2 Operation modes

The M48Z02/12 also has its own power-fail detect circuit. The control circuitry constantly monitors the single 5 V supply for an out of tolerance condition. When  $V_{CC}$  is out of tolerance, the circuit write protects the SRAM, providing a high degree of data security in the midst of unpredictable system operation brought on by low  $V_{CC}$ . As  $V_{CC}$  falls below approximately 3 V, the control circuitry connects the battery which maintains data operation until valid power returns.

Table 2. Operating modes

| Mode     | V <sub>cc</sub>                                          | Ē        | G               | W               | DQ0-<br>DQ7      | Power               |

|----------|----------------------------------------------------------|----------|-----------------|-----------------|------------------|---------------------|

| Deselect | 475. 55.                                                 | $V_{IH}$ | Х               | Х               | High Z           | Standby             |

| WRITE    | 4.75 to 5.5 V<br>or                                      | $V_{IL}$ | Х               | $V_{IL}$        | D <sub>IN</sub>  | Active              |

| READ     | 4.5 to 5.5 V                                             | $V_{IL}$ | $V_{IL}$        | V <sub>IH</sub> | D <sub>OUT</sub> | Active              |

| READ     |                                                          | $V_{IL}$ | V <sub>IH</sub> | V <sub>IH</sub> | High Z           | Active              |

| Deselect | V <sub>SO</sub> to V <sub>PFD</sub> (min) <sup>(1)</sup> | Х        | Х               | Х               | High Z           | CMOS standby        |

| Deselect | ≤ V <sub>SO</sub> <sup>(1)</sup>                         | Х        | Х               | Х               | High Z           | Battery backup mode |

<sup>1.</sup> See Table 10 on page 16 for details.

Note:  $X = V_{IH}$  or  $V_{IL}$ ;  $V_{SO} =$  battery backup switchover voltage.

#### 2.1 READ mode

The M48Z02/12 is in the READ mode whenever  $\overline{W}$  (WRITE enable) is high and  $\overline{E}$  (chip enable) is low. The device architecture allows ripple-through access of data from eight of 16,384 locations in the static storage array. Thus, the unique address specified by the 11 Address Inputs defines which one of the 2,048 bytes of data is to be accessed. Valid data will be available at the data I/O pins within address access time ( $t_{AVQV}$ ) after the last address input signal is stable, providing that the  $\overline{E}$  and  $\overline{G}$  access times are also satisfied. If the  $\overline{E}$  and  $\overline{G}$  access times are not met, valid data will be available after the latter of the chip enable access time ( $t_{ELQV}$ ) or output enable access time ( $t_{GLQV}$ ).

The state of the eight three-state data I/O signals is controlled by  $\overline{E}$  and  $\overline{G}$ . If the outputs are activated before  $t_{AVQV}$ , the data lines will be driven to an indeterminate state until  $t_{AVQV}$ . If the address inputs are changed while  $\overline{E}$  and  $\overline{G}$  remain active, output data will remain valid for output data hold time ( $t_{AXQX}$ ) but will go indeterminate until the next address access.

Operation modes M48Z02, M48Z12

tAVAV A0-A10 **VALID** tAVQV tAXQX tELQV tEHQZ Ē tELQX tGLQV tGHQZ  $\overline{\mathsf{G}}$ tGLQX DQ0-DQ7 **VALID** AI01330

Figure 4. READ mode AC waveforms

Note: WRITE enable  $(\overline{W})$  = high.

Table 3. READ mode AC characteristics

|                   |                                         | M48Z02/M48Z12 |     |     |     |     |     |      |

|-------------------|-----------------------------------------|---------------|-----|-----|-----|-----|-----|------|

| Symbol            | Parameter <sup>(1)</sup>                | -7            | 70  | -1  | 50  | -2  | 00  | Unit |

|                   |                                         | Min           | Max | Min | Max | Min | Max |      |

| t <sub>AVAV</sub> | READ cycle time                         | 70            |     | 150 |     | 200 |     | ns   |

| t <sub>AVQV</sub> | Address valid to output valid           |               | 70  |     | 150 |     | 200 | ns   |

| t <sub>ELQV</sub> | Chip enable low to output valid         |               | 70  |     | 150 |     | 200 | ns   |

| t <sub>GLQV</sub> | Output enable low to output valid       |               | 35  |     | 75  |     | 80  | ns   |

| t <sub>ELQX</sub> | Chip enable low to output transition    | 5             |     | 10  |     | 10  |     | ns   |

| t <sub>GLQX</sub> | Output enable low to output transition  | 5             |     | 5   |     | 5   |     | ns   |

| t <sub>EHQZ</sub> | Chip enable high to output Hi-Z         |               | 25  |     | 35  |     | 40  | ns   |

| t <sub>GHQZ</sub> | Output enable high to output Hi-Z       |               | 25  |     | 35  |     | 40  | ns   |

| t <sub>AXQX</sub> | Address transition to output transition | 10            |     | 5   |     | 5   |     | ns   |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = 0$  to 70 °C or -40 to 85 °C;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

### 2.2 WRITE mode

The M48Z02/12 is in the WRITE mode whenever  $\overline{W}$  and  $\overline{E}$  are active. The start of a WRITE is referenced from the latter occurring falling edge of  $\overline{W}$  or  $\overline{E}$ . A WRITE is terminated by the earlier rising edge of  $\overline{W}$  or  $\overline{E}$ . The addresses must be held valid throughout the cycle.  $\overline{E}$  or  $\overline{W}$  must return high for a minimum of  $t_{EHAX}$  from chip enable or  $t_{WHAX}$  from WRITE enable prior to the initiation of another READ or WRITE cycle. Data-in must be valid  $t_{DVWH}$  prior to the end of WRITE and remain valid for  $t_{WHDX}$  afterward.  $\overline{G}$  should be kept high during WRITE cycles to avoid bus contention; although, if the output bus has been activated by a low on  $\overline{E}$  and  $\overline{G}$ , a low on  $\overline{W}$  will disable the outputs  $t_{WLOZ}$  after  $\overline{W}$  falls.

M48Z02, M48Z12 Operation modes

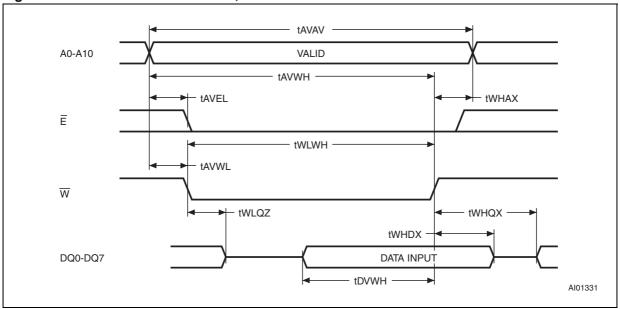

Figure 5. WRITE enable controlled, WRITE AC waveform

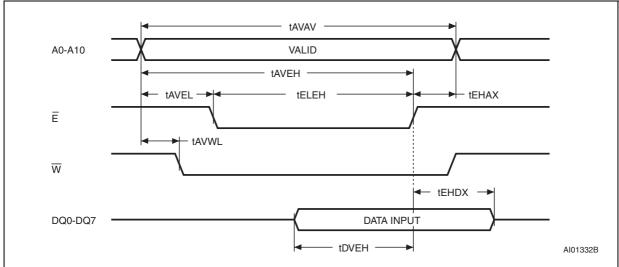

Figure 6. Chip enable controlled, WRITE AC waveforms

Operation modes M48Z02, M48Z12

Table 4. WRITE mode AC characteristics

|                   |                                         |     | M48Z02/M48Z12 |     |     |     |     |      |

|-------------------|-----------------------------------------|-----|---------------|-----|-----|-----|-----|------|

| Symbol            | Parameter <sup>(1)</sup>                | _   | 70            | -1  | 150 | -2  | 200 | Unit |

|                   |                                         | Min | Max           | Min | Max | Min | Max |      |

| t <sub>AVAV</sub> | WRITE cycle time                        | 70  |               | 150 |     | 200 |     | ns   |

| t <sub>AVWL</sub> | Address valid to WRITE enable low       | 0   |               | 0   |     | 0   |     | ns   |

| t <sub>AVEL</sub> | Address valid to chip enable 1 low      | 0   |               | 0   |     | 0   |     | ns   |

| t <sub>WLWH</sub> | WRITE enable pulse width                | 50  |               | 90  |     | 120 |     | ns   |

| t <sub>ELEH</sub> | Chip enable low to chip enable 1 high   | 55  |               | 90  |     | 120 |     | ns   |

| t <sub>WHAX</sub> | WRITE enable high to address transition | 0   |               | 10  |     | 10  |     | ns   |

| t <sub>EHAX</sub> | Chip enable high to address transition  | 0   |               | 10  |     | 10  |     | ns   |

| t <sub>DVWH</sub> | Input valid to WRITE enable high        | 30  |               | 40  |     | 60  |     | ns   |

| t <sub>DVEH</sub> | Input valid to chip enable high         | 30  |               | 40  |     | 60  |     | ns   |

| t <sub>WHDX</sub> | WRITE enable high to input transition   | 5   |               | 5   |     | 5   |     | ns   |

| t <sub>EHDX</sub> | Chip enable high to input transition    | 5   |               | 5   |     | 5   |     | ns   |

| t <sub>WLQZ</sub> | WRITE enable low to output Hi-Z         |     | 25            |     | 50  |     | 60  | ns   |

| t <sub>AVWH</sub> | Address valid to WRITE enable high      | 60  |               | 120 |     | 140 |     | ns   |

| t <sub>AVEH</sub> | Address valid to chip enable high       | 60  |               | 120 |     | 140 |     | ns   |

| t <sub>WHQX</sub> | WRITE enable high to output transition  | 5   |               | 10  |     | 10  |     | ns   |

Valid for ambient operating temperature: T<sub>A</sub> = 0 to 70 °C or -40 to 85 °C; V<sub>CC</sub> = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

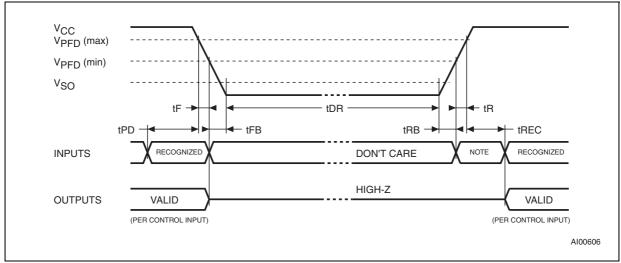

### 2.3 Data retention mode

With valid  $V_{CC}$  applied, the M48Z02/12 operates as a conventional BYTEWIDE<sup>TM</sup> static RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write protecting itself when  $V_{CC}$  falls within the  $V_{PFD}$  (max),  $V_{PFD}$  (min) window. All outputs become high impedance, and all inputs are treated as "don't care."

Note:

A power failure during a WRITE cycle may corrupt data at the currently addressed location, but does not jeopardize the rest of the RAM's content. At voltages below  $V_{PFD}$  (min), the user can be assured the memory will be in a write protected state, provided the  $V_{CC}$  fall time is not less than  $t_F$  The M48Z02/12 may respond to transient noise spikes on  $V_{CC}$  that reach into the deselect window during the time the device is sampling  $V_{CC}$ . Therefore, decoupling of the power supply lines is recommended.

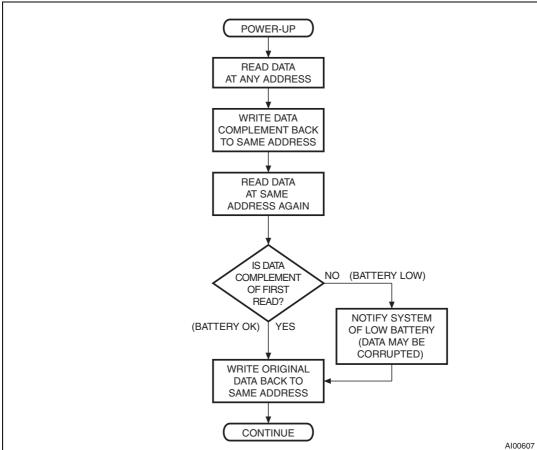

The power switching circuit connects external  $V_{CC}$  to the RAM and disconnects the battery when  $V_{CC}$  rises above  $V_{SO}$ . As  $V_{CC}$  rises, the battery voltage is checked. If the voltage is too low, an internal Battery Not OK ( $\overline{BOK}$ ) flag will be set. The  $\overline{BOK}$  flag can be checked after power up. If the  $\overline{BOK}$  flag is set, the first WRITE attempted will be blocked. The flag is automatically cleared after the first WRITE, and normal RAM operation resumes. Figure 7 on page 11 illustrates how a  $\overline{BOK}$  check routine could be structured.

For more information on a battery storage life refer to the application note AN1012.

M48Z02, M48Z12 Operation modes

Figure 7. Checking the BOK flag status

Operation modes M48Z02, M48Z12

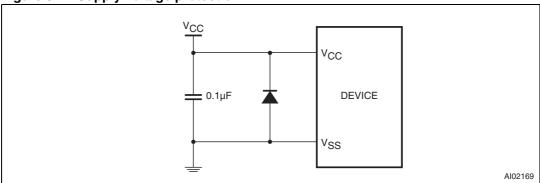

### 2.4 V<sub>CC</sub> noise and negative going transients

$I_{CC}$  transients, including those produced by output switching, can produce voltage fluctuations, resulting in spikes on the  $V_{CC}$  bus. These transients can be reduced if capacitors are used to store energy which stabilizes the  $V_{CC}$  bus. The energy stored in the bypass capacitors will be released as low going spikes are generated or energy will be absorbed when overshoots occur. A ceramic bypass capacitor value of 0.1  $\mu$ F (as shown in *Figure 8*) is recommended in order to provide the needed filtering.

In addition to transients that are caused by normal SRAM operation, power cycling can generate negative voltage spikes on  $V_{CC}$  that drive it to values below  $V_{SS}$  by as much as one volt. These negative spikes can cause data corruption in the SRAM while in battery backup mode. To protect from these voltage spikes, STMicroelectronics recommends connecting a Schottky diode from  $V_{CC}$  to  $V_{SS}$  (cathode connected to  $V_{CC}$ , anode to  $V_{SS}$ ). Schottky diode 1N5817 is recommended for through hole and MBRS120T3 is recommended for surface mount.

Figure 8. Supply voltage protection

M48Z02, M48Z12 Maximum ratings

### 3 Maximum ratings

Stressing the device above the rating listed in the absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 5. Absolute maximum ratings

| Symbol                          | Parameter                                                 | Value     | Unit |    |

|---------------------------------|-----------------------------------------------------------|-----------|------|----|

| T <sub>A</sub>                  | Ambient operating temperature                             | 0 to 70   | °C   |    |

| T <sub>STG</sub>                | Storage temperature (V <sub>CC</sub> off, oscillator off) | -40 to 85 | °C   |    |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 seconds                    | 260       | °C   |    |

| V <sub>IO</sub>                 | Input or output voltages                                  | -0.3 to 7 | V    |    |

| V <sub>CC</sub>                 | Supply voltage                                            |           |      | V  |

| I <sub>O</sub>                  | Output current                                            |           | 20   | mA |

| P <sub>D</sub>                  | Power dissipation                                         |           |      | W  |

Soldering temperature of the IC leads is to not exceed 260 °C for 10 seconds. Furthermore, the devices shall not be exposed to IR reflow nor preheat cycles (as performed as part of wave soldering). ST recommends the devices be hand-soldered or placed in sockets to avoid heat damage to the batteries.

#### Caution:

Negative undershoots below –0.3 V are not allowed on any pin while in the battery backup mode.

### 4 DC and AC parameters

This section summarizes the operating and measurement conditions, as well as the DC and AC characteristics of the device. The parameters in the following DC and AC characteristic tables are derived from tests performed under the measurement conditions listed in *Table 6: Operating and AC measurement conditions*. Designers should check that the operating conditions in their projects match the measurement conditions when using the quoted parameters.

Table 6. Operating and AC measurement conditions

| Parameter                                       |         | M48Z02      | M48Z12     | Unit |

|-------------------------------------------------|---------|-------------|------------|------|

| Supply voltage (V <sub>CC</sub> )               |         | 4.75 to 5.5 | 4.5 to 5.5 | V    |

| Ambient operating temperature (T <sub>A</sub> ) | Grade 1 | 0 to 70     | 0 to 70    | °C   |

| Load capacitance (C <sub>L</sub> )              |         | 100         | 100        | pF   |

| Input rise and fall times                       |         | ≤ 5         | ≤ 5        | ns   |

| Input pulse voltages                            |         | 0 to 3      | 0 to 3     | V    |

| Input and output timing ref. voltages           |         | 1.5         | 1.5        | V    |

Note: Output Hi-Z is defined as the point where data is no longer driven.

Figure 9. AC testing load circuit

Table 7. Capacitance

| Symbol              | Parameter <sup>(1)(2)</sup> | Min | Max | Unit |

|---------------------|-----------------------------|-----|-----|------|

| C <sub>IN</sub>     | Input capacitance           | -   | 10  | pF   |

| C <sub>IO</sub> (3) | Input / output capacitance  | -   | 10  | pF   |

- 1. Effective capacitance measured with power supply at 5 V. Sampled only, not 100% tested.

- 2. At 25°C, f = 1 MHz.

- 3. Outputs deselected.

Table 8. DC characteristics

| Symbol                         | Parameter                     | Test condition <sup>(1)</sup>           | Min  | Max                   | Unit |

|--------------------------------|-------------------------------|-----------------------------------------|------|-----------------------|------|

| I <sub>LI</sub>                | Input leakage current         | $0V \le V_{IN} \le V_{CC}$              |      | ±1                    | μΑ   |

| I <sub>LO</sub> <sup>(2)</sup> | Output leakage current        | $0V \le V_{OUT} \le V_{CC}$             |      | ±1                    | μΑ   |

| I <sub>CC</sub>                | Supply current                | Outputs open                            |      | 80                    | mA   |

| I <sub>CC1</sub>               | Supply current (standby) TTL  | $\overline{E} = V_IH$                   |      | 3                     | mA   |

| I <sub>CC2</sub>               | Supply current (standby) CMOS | $\overline{E} = V_{CC} - 0.2 \text{ V}$ |      | 3                     | mA   |

| V <sub>IL</sub>                | Input low voltage             |                                         | -0.3 | 0.8                   | V    |

| $V_{IH}$                       | Input high voltage            |                                         | 2.2  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                | Output low voltage            | I <sub>OL</sub> = 2.1 mA                |      | 0.4                   | V    |

| V <sub>OH</sub>                | Output high voltage           | $I_{OH} = -1 \text{ mA}$                | 2.4  |                       | V    |

- 1. Valid for ambient operating temperature:  $T_A = 0$  to 70 °C;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

- 2. Outputs deselected.

Figure 10. Power down/up mode AC waveforms

Note:

Inputs may or may not be recognized at this time. Caution should be taken to keep  $\overline{E}$  high as  $V_{CC}$  rises past  $V_{PFD}$  (min). Some systems may perform inadvertent WRITE cycles after  $V_{CC}$  rises above  $V_{PFD}$  (min) but before normal system operations begin. Even though a power on reset is being applied to the processor, a reset condition may not occur until after the system is running.

Table 9. Power down/up AC characteristics

| Symbol                        | Parameter <sup>(1)</sup>                                                   | Min | Max | Unit |

|-------------------------------|----------------------------------------------------------------------------|-----|-----|------|

| t <sub>PD</sub>               | E or W at V <sub>IH</sub> before power down                                | 0   | -   | μs   |

| t <sub>F</sub> <sup>(2)</sup> | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> fall time | 300 | -   | μs   |

| t <sub>FB</sub> (3)           | V <sub>PFD</sub> (min) to V <sub>SS</sub> V <sub>CC</sub> fall time        | 10  | -   | μs   |

| t <sub>R</sub>                | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> rise time | 0   | -   | μs   |

| t <sub>RB</sub>               | V <sub>SS</sub> to V <sub>PFD</sub> (min) V <sub>CC</sub> rise time        | 1   | -   | μs   |

| t <sub>REC</sub>              | E or W at V <sub>IH</sub> after power up                                   | 2   | -   | ms   |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = 0$  to 70 °C;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

Table 10. Power down/up trip points DC characteristics

| Symbol                         | Parameter <sup>(1)(2)</sup>      |        | Min | Тур | Max   | Unit |

|--------------------------------|----------------------------------|--------|-----|-----|-------|------|

| V <sub>PFD</sub>               | Power-fail deselect voltage      | M48Z02 | 4.5 | 4.6 | 4.75  | V    |

|                                | 1 ower-lail deselect voltage     | M48Z12 | 4.2 | 4.3 | 4.5   | V    |

| V <sub>SO</sub>                | Battery backup switchover voltag |        | 3.0 |     | V     |      |

| t <sub>DR</sub> <sup>(3)</sup> | Expected data retention time     | 10     |     |     | YEARS |      |

<sup>1.</sup> All voltages referenced to V<sub>SS</sub>.

<sup>2.</sup>  $V_{PFD}$  (max) to  $V_{PFD}$  (min) fall time of less than  $t_F$  may result in deselection/write protection not occurring until 200  $\mu$ s after  $V_{CC}$  passes  $V_{PFD}$  (min).

<sup>3.</sup>  $\rm \ V_{PFD}$  (min) to  $\rm V_{SS}$  fall time of less than  $\rm t_{FB}$  may cause corruption of RAM data.

<sup>2.</sup> Valid for ambient operating temperature:  $T_A = 0$  to 70 °C;  $V_{CC} = 4.75$  to 5.5 V or 4.5 to 5.5 V (except where noted).

<sup>3.</sup> At 25 °C,  $V_{CC} = 0 \text{ V}$ .

#### Package mechanical data 5

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

Α2 eА еЗ D Е PCDIP

Figure 11. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package outline

Note: Drawing is not to scale.

PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package mechanical Table 11.

| Symb |       | mm    |       |     | inches |       |

|------|-------|-------|-------|-----|--------|-------|

|      | Тур   | Min   | Max   | Тур | Min    | Max   |

| Α    |       | 8.89  | 9.65  |     | 0.350  | 0.380 |

| A1   |       | 0.38  | 0.76  |     | 0.015  | 0.030 |

| A2   |       | 8.38  | 8.89  |     | 0.330  | 0.350 |

| В    |       | 0.38  | 0.53  |     | 0.015  | 0.021 |

| B1   |       | 1.14  | 1.78  |     | 0.045  | 0.070 |

| С    |       | 0.20  | 0.31  |     | 0.008  | 0.012 |

| D    |       | 34.29 | 34.80 |     | 1.350  | 1.370 |

| Е    |       | 17.83 | 18.34 |     | 0.702  | 0.722 |

| e1   |       | 2.29  | 2.79  |     | 0.090  | 0.110 |

| e3   | 27.94 |       |       | 1.1 |        |       |

| eA   |       | 15.24 | 16.00 |     | 0.600  | 0.630 |

| L    |       | 3.05  | 3.81  |     | 0.120  | 0.150 |

| N    |       | 24    | •     |     | 24     |       |

Figure 12. Shipping tube dimensions for PCDIP24 package

Note: All dimensions are in inches.

18/22

M48Z02, M48Z12 Part numbering

## 6 Part numbering

<sup>1 = 0</sup> to 70  $^{\circ}$ C

1. Not recommended for new design. Contact local ST sales office for availability.

For a list of available options (e.g., speed, package) or for further information on any aspect of this device, please contact the ST sales office nearest you.

20/22

## 7 Environmental information

Figure 13. Recycling symbols

This product contains a non-rechargeable lithium (lithium carbon monofluoride chemistry) button cell battery fully encapsulated in the final product.

Recycle or dispose of batteries in accordance with the battery manufacturer's instructions and local/national disposal and recycling regulations.

M48Z02, M48Z12 Revision history

# 8 Revision history

Table 13. Document revision history

| Date        | Revision | Changes                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May-1999    | 1        | First issue                                                                                                                                                         |

| 09-Jul-2001 | 2        | Reformatted; temperature information added to tables ( <i>Table 5, 6, 7, 8, 3, 4, 9, 10</i> ); Figure updated ( <i>Figure 10</i> )                                  |

| 17-Dec-2001 | 2.1      | Remove references to "clock" in document                                                                                                                            |

| 20-May-2002 | 2.2      | Updated V <sub>CC</sub> noise and negative going transients text                                                                                                    |

| 01-Apr-2003 | 3        | v2.2 template applied; test condition updated (Table 10)                                                                                                            |

| 22-Apr-2003 | 3.1      | Fix error in ordering information ( <i>Table 12</i> )                                                                                                               |

| 12-Dec-2005 | 4        | Update template, Lead-free text, and remove references to 'crystal' and footnote ( <i>Table 8</i> , <i>12</i> )                                                     |

| 02-Nov-2007 | 5        | Reformatted document; added lead-free second level interconnect information to cover page and Section 5: Package mechanical data; updated Table 5, 6, 8, 9, 10, 12. |

| 03-Dec-2008 | 6        | Added Section 7: Environmental information; minor formatting changes.                                                                                               |

| 27-May-2010 | 7        | Updated Section 3, Table 11, text in Section 5; reformatted document.                                                                                               |

| 21-Jan-2011 | 8        | Updated <i>Table 12: Ordering information scheme</i> for 200 ns version of devices; updated <i>Section 7</i> ; added <i>Figure 12</i> ; minor textual updates.      |

| 07-Jun-2011 | 9        | Updated footnote of Table 5: Absolute maximum ratings.                                                                                                              |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

22/22 Doc ID 2420 Rev 9