Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 3V, 1G-bit NAND Flash Memory MX30LF1G18AC

# **Contents**

| 1.       | FEAT         | TURES                                                                          | 5  |

|----------|--------------|--------------------------------------------------------------------------------|----|

| 2.       | GEN          | ERAL DESCRIPTIONS                                                              | 6  |

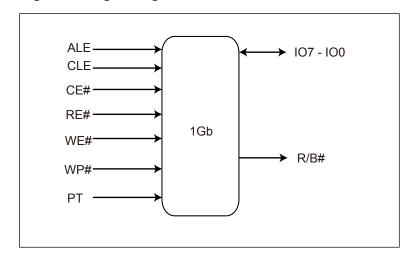

|          |              | Figure 1. Logic Diagram                                                        | 6  |

|          | 2-1.         | ORDERING INFORMATION                                                           | 7  |

| 3.       | PIN (        | CONFIGURATIONS                                                                 | 8  |

|          | 3-1.         | PIN DESCRIPTIONS                                                               | 10 |

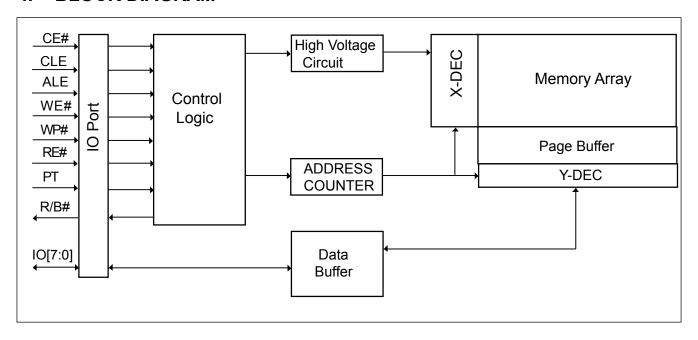

| 4.       | BLO          | CK DIAGRAM                                                                     | 12 |

| 5        | SCH          | EMATIC CELL LAYOUT AND ADDRESS ASSIGNMENT                                      | 13 |

| ٥.       | 0011         | Table 1. Address Allocation                                                    |    |

| 4.<br>5. | DEV          | CE OPERATIONS                                                                  |    |

| ٥.       | 6-1.         | Address Input/Command Input/Data Input                                         |    |

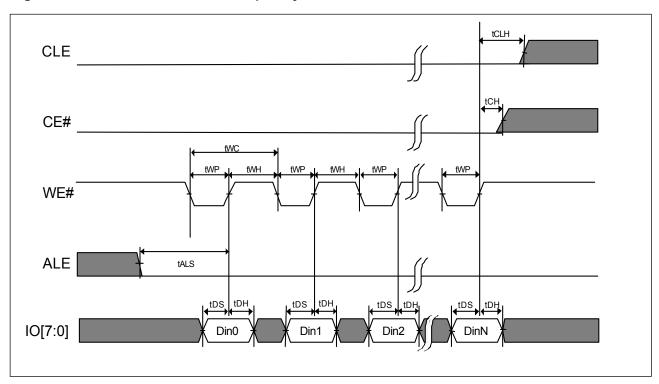

|          | <b>0-</b> 1. | Figure 2. AC Waveforms for Command / Address / Data Latch Timing               |    |

|          |              | Figure 3. AC Waveforms for Address Input Cycle                                 |    |

|          |              | Figure 4. AC Waveforms for Command Input Cycle                                 |    |

|          |              | Figure 5. AC Waveforms for Data Input Cycle                                    |    |

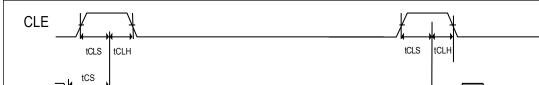

|          | 6-2.         | Page Read                                                                      | 16 |

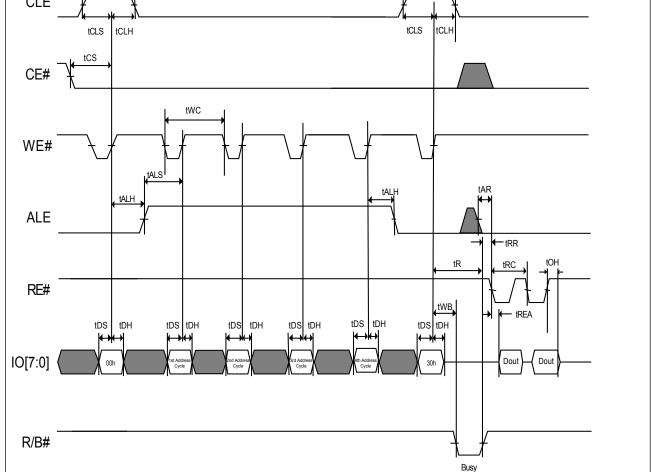

|          |              | Figure 6. AC Waveforms for Read Cycle                                          | 16 |

|          |              | Figure 7. AC Waveforms for Read Operation (Intercepted by CE#)                 |    |

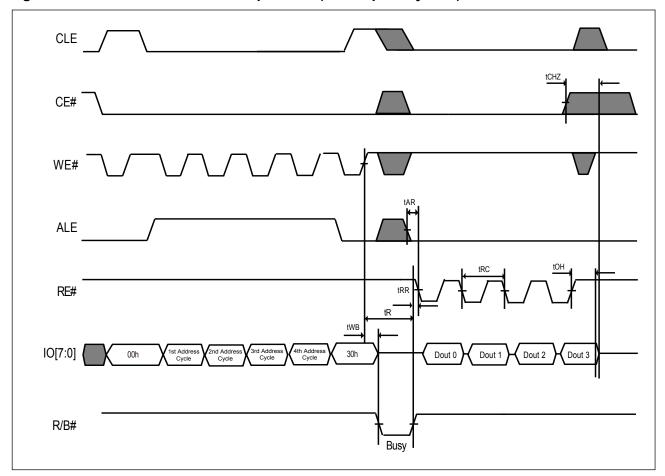

|          |              | Figure 8. AC Waveforms for Read Operation (with CE# Don't Care)                | 18 |

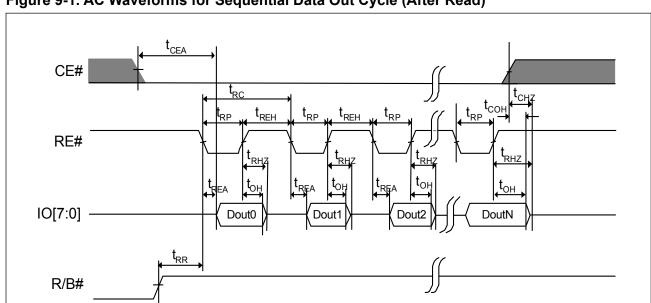

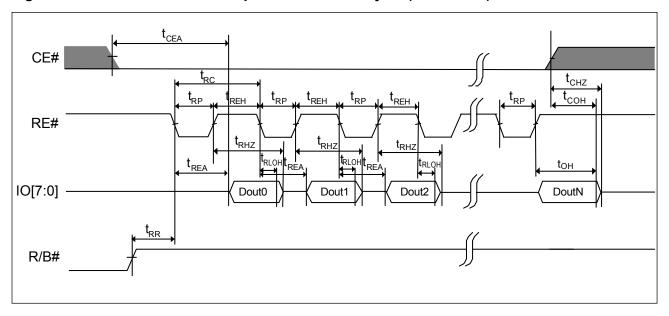

|          |              | Figure 9-1. AC Waveforms for Sequential Data Out Cycle (After Read)            |    |

|          |              | Figure 9-2. AC Waveforms for Sequential Data Out Cycle (After Read) - EDO Mode |    |

|          |              | Figure 10. AC Waveforms for Random Data Output                                 | 20 |

|          | 6-3.         | Cache Read Sequential                                                          |    |

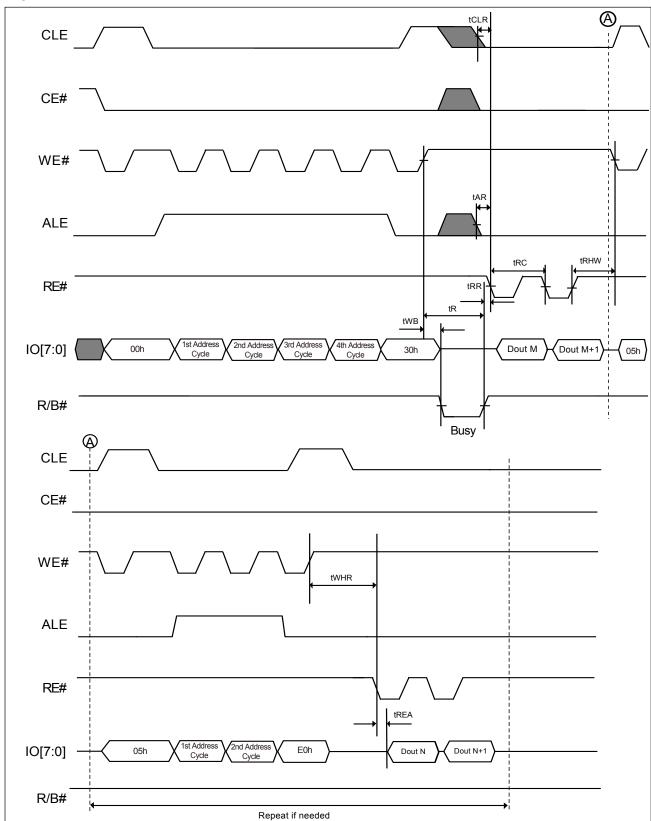

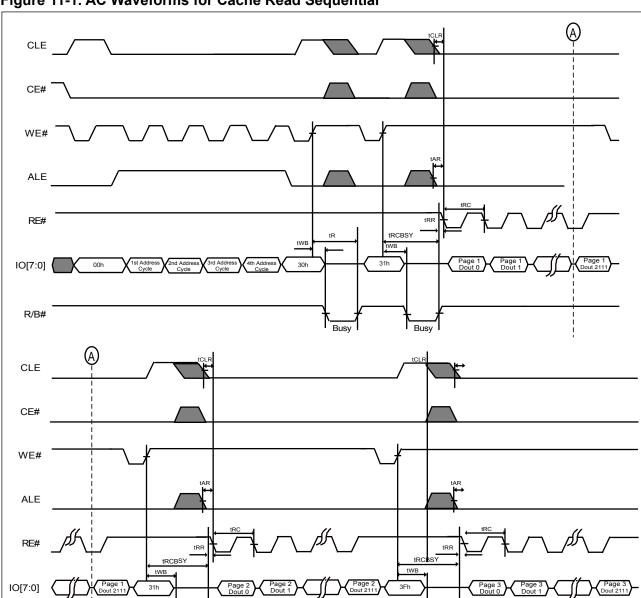

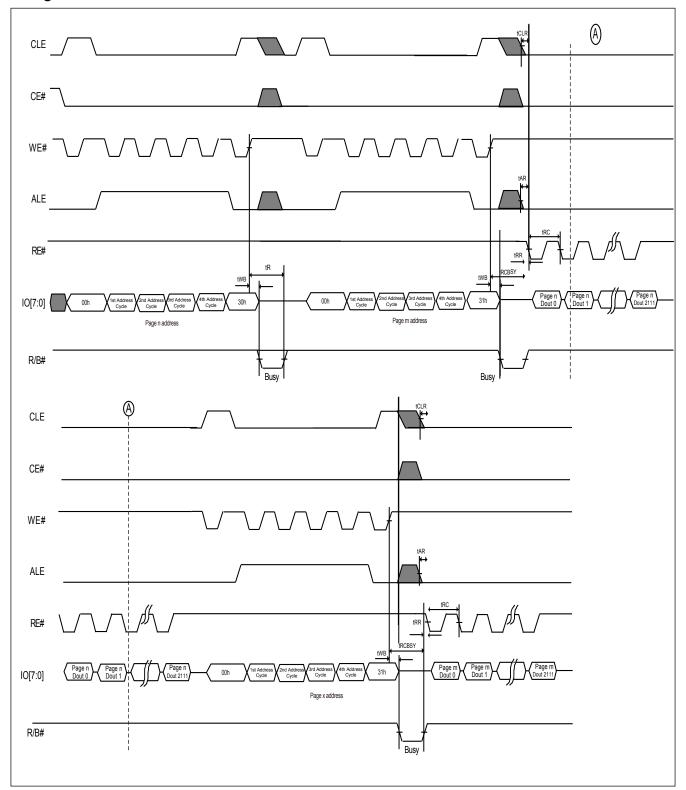

|          |              | Figure 11-1. AC Waveforms for Cache Read Sequential                            |    |

|          | 6-4.         | Cache Read Random                                                              | 23 |

|          |              | Figure 11-2. AC Waveforms for Cache Read Random                                | 24 |

|          | 6-5.         | Page Program                                                                   | 25 |

|          |              | Figure 12. AC Waveforms for Program Operation after Command 80H                | 25 |

|          |              | Figure 13. AC Waveforms for Random Data In (For Page Program)                  | 26 |

|          |              | Figure 14. AC Waveforms for Program Operation with CE# Don't Care              | 27 |

|          | 6-6.         | Cache Program                                                                  | 28 |

|          |              | Figure 15-1. AC Waveforms for Cache Program                                    | 29 |

|          |              | Figure 15-2. AC Waveforms for Sequence of Cache Program                        | 30 |

| 6-7.  | Block Erase                                                                                           | 31 |

|-------|-------------------------------------------------------------------------------------------------------|----|

|       | Figure 16. AC Waveforms for Erase Operation                                                           | 31 |

| 6-8.  | ID Read                                                                                               | 32 |

|       | Table 2. ID Codes Read Out by ID Read Command 90H                                                     | 32 |

|       | Table 3. The Definition of Byte2-Byte4 of ID Table                                                    | 33 |

|       | Figure 17-1. AC Waveforms for ID Read Operation                                                       | 34 |

|       | Figure 17-2. AC Waveforms for ID Read (ONFI Identifier) Operation                                     | 34 |

| 6-9.  | Status Read                                                                                           | 35 |

|       | Table 4. Status Output                                                                                |    |

|       | Figure 18. Bit Assignment (HEX Data)                                                                  | 36 |

|       | Figure 19. AC Waveforms for Status Read Operation                                                     | 36 |

| 6-10. | Block Protection Status Read                                                                          | 37 |

|       | Table 5. Block-Protection Status Output                                                               |    |

|       | Table 6. Address Cycle Definition of Block                                                            |    |

|       | Figure 20. AC Waveforms for Block Protection Status Read                                              |    |

| 6-11  | Reset                                                                                                 | 39 |

| •     | Figure 21. AC waveforms for Reset Operation                                                           |    |

| 6-12  | Parameter Page Read (ONFI)                                                                            |    |

| 0-12. | Figure 22. AC waveforms for Parameter Page Read (ONFI) Operation                                      |    |

|       | Figure 23. AC Waveforms for Parameter Page Read (ONFI) Random Operation (For 05h-E0h)                 |    |

|       | Table 7. Parameter Page (ONFI)                                                                        |    |

| 6-13  | Unique ID Read (ONFI)                                                                                 |    |

| U-13. | Figure 24. AC waveforms for Unique ID Read Operation                                                  |    |

|       | Figure 25. AC waveforms for Unique ID Read Operation (For 05h-E0h)                                    |    |

| 6 1 1 | Feature Set Operation (ONFI)                                                                          |    |

| 0-14. | Table 8-1. Definition of Feature Address                                                              |    |

|       | Table 8-2. Sub-Feature Parameter Table of Feature Address - 90h (Array Operation Mode)                |    |

|       | Table 8-3. Sub-Feature Parameter Table of Feature Address - A0h (Block Protection Operation) (note 1) |    |

|       | 6-14-1.Set Feature (ONFI)                                                                             |    |

|       | Figure 26. AC Waveforms for Set Feature (ONFI) Operation                                              |    |

|       | 6-14-2.Get Feature (ONFI)                                                                             |    |

|       | Figure 27. AC Waveforms for Get Feature (ONFI) Operation                                              |    |

|       | 6-14-3.Secure OTP (One-Time-Programmable) Feature                                                     |    |

|       | Figure 28. AC Waveforms for OTP Data Read                                                             |    |

|       | Figure 29. AC Waveforms for OTP Data Read with Random Data Output                                     | 50 |

|       | Figure 30. AC Waveforms for OTP Data Program                                                          |    |

|       | Figure 31. AC Waveforms for OTP Data Program with Random Data Input                                   | 52 |

|       | Figure 32. AC Waveforms for OTP Protection Operation                                                  |    |

|       | 6-14-4.Block Protection                                                                               | 54 |

|       | Table 9. Definition of Protection Bits                                                                | 54 |

|       | Figure 33. PT Pin and Block Protection Mode Operation                                                 | 55 |

| 7. | PAR         | PARAMETERS                                                                                                                                                                                                                                                                             |          |  |  |  |

|----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|    | 7-1.        | ABSOLUTE MAXIMUM RATINGS  Figure 34. Maximum Negative Overshoot Waveform  Figure 35. Maximum Positive Overshoot Waveform  Table 10. Operating Range  Table 11. DC Characteristics  Table 12. Capacitance  Table 13. AC Testing Conditions  Table 14. Program and Erase Characteristics |          |  |  |  |

|    |             | Table 15. AC Characteristics                                                                                                                                                                                                                                                           | 59       |  |  |  |

| 8. | OPE<br>8-1. | Table 16. Logic Table  Table 17. HEX Command Table  R/B#: Termination for The Ready/Busy# Pin (R/B#)  Figure 36. R/B# Pin Timing Information                                                                                                                                           | 60<br>61 |  |  |  |

|    | 8-2.        | Power On/Off Sequence  Figure 37. Power On/Off Sequence  8-2-1.WP# Signal  Figure 38-1. Enable Programming of WP# Signal  Figure 38-2. Disable Programming of WP# Signal  Figure 38-3. Enable Erasing of WP# Signal  Figure 38-4. Disable Erasing of WP# Signal                        |          |  |  |  |

| 9. | SOF         | TWARE ALGORITHM                                                                                                                                                                                                                                                                        | 66       |  |  |  |

|    | 9-1.        | Invalid Blocks (Bad Blocks) Figure 39. Bad Blocks Table 18. Valid Blocks                                                                                                                                                                                                               | 66       |  |  |  |

|    | 9-2.        | Bad Block Test Flow                                                                                                                                                                                                                                                                    |          |  |  |  |

|    | 9-3.        | Failure Phenomena for Read/Program/Erase Operations  Table 19. Failure Modes                                                                                                                                                                                                           |          |  |  |  |

|    | 9-4.        | Program                                                                                                                                                                                                                                                                                | 68       |  |  |  |

|    | 9-5.        | Erase  Figure 43. Erase Flow Chart  Figure 44. Read Flow Chart                                                                                                                                                                                                                         | 69       |  |  |  |

| 10 | . PAC       | KAGE INFORMATION                                                                                                                                                                                                                                                                       | 70       |  |  |  |

| 11 | . REV       | ISION HISTORY                                                                                                                                                                                                                                                                          | 72       |  |  |  |

#### 3V, 1Gb NAND Flash Memory

#### 1. FEATURES

- · 1G-bit SLC NAND Flash

- Bus: x8

- Page size: (2048+64) byte,

- Block size: (128K+4K) byte,

- ONFI 1.0 compliant

- Multiplexed Command/Address/Data

- User Redundancy

- 64-byte attached to each page

- Fast Read Access

- Latency of array to register: 25us

- Sequential read: 20ns

- Cache Read Support

- Page Program Operation

- Page program time: 300us(typ.)

- Cache Program Support

- Block Erase Operation

- Block erase time: 1ms (typ.)

- Single Voltage Operation:

- VCC: 2.7 3.6V

- Low Power Dissipation

- Max. 30mA

Active current (Read/Program/Erase)

- · Sleep Mode

- 50uA (Max) standby current

- Hardware Data Protection: WP# pin

#### Block Protection

- PT (Protection) pin: active high at power-on, which protects the entire chip. The pin has an internal weak pull down.

- Temporary protection/un-protection function (enabling by PT pin)

- Solid protection (enabling by PT pin)

- Device Status Indicators

- Ready/Busy (R/B#) pin

- Status Register

- Chip Enable Don't Care

- Simplify System Interface

- Unique ID Read support (ONFI)

- Secure OTP support

- High Reliability

- Endurance: typical 100K cycles (with 4-bit ECC per (512+16) Byte)

- Data Retention: 10 years

- Wide Temperature Operating Range

-40°C to +85°C

- · Package:

- 1) 48-TSOP(I) (12mm x 20mm)

- 2) 63-ball 9mmx11mm VFBGA

All packaged devices are RoHS Compliant and Halogen-free.

#### 2. GENERAL DESCRIPTIONS

The MX30LF1G18AC is a 1Gb SLC NAND Flash memory device. Its standard NAND Flash features and reliable quality of typical P/E cycles 100K (with ECC), which makes it most suitable for embedded system code and data storage.

The product family requires 4-bit ECC per (512+16)B.

The MX30LF1G18AC is typically accessed in pages of 2,112 bytes for read and program operations.

The MX30LF1G18AC array is organized as thousands of blocks, which is composed by 64 pages of (2,048+64) byte in two NAND strings structure with 32 serial connected cells in each string. Each page has an additional 64 bytes for ECC and other purposes. The device has an on-chip buffer of 2,112 bytes for data load and access.

The Cache Read Operation of the MX30LF1G18AC enables first-byte read-access latency of 25us and sequential read of 20ns and the latency time of next sequential page will be shorten from tR to tRCBSY.

The MX30LF1G18AC power consumption is 30mA during all modes of operations (Read/Program/Erase), and 50uA in standby mode.

Figure 1. Logic Diagram

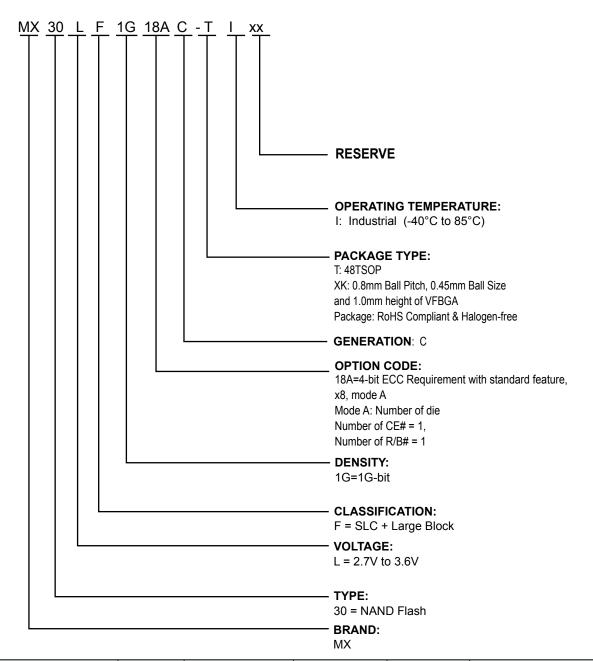

## 2-1. ORDERING INFORMATION

## **Part Name Description**

| Part Number      | Density | Organization | VCC Range | Package  | Temperature Grade |

|------------------|---------|--------------|-----------|----------|-------------------|

| MX30LF1G18AC-TI  | 1Gb     | x8           | 3V        | 48-TSOP  | Industrial        |

| MX30LF1G18AC-XKI | 1Gb     | x8           | 3V        | 63-VFBGA | Industrial        |

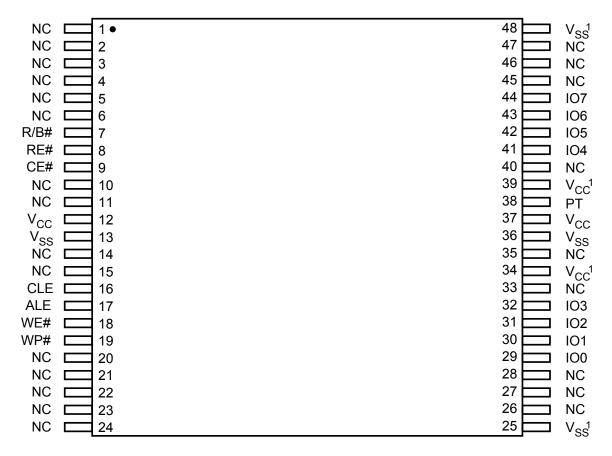

#### 3. PIN CONFIGURATIONS

#### **48-TSOP**

**Note 1.** These pins might not be connected internally. However, it is recommended to connect these pins to power(or ground) as designated for ONFI compatibility.

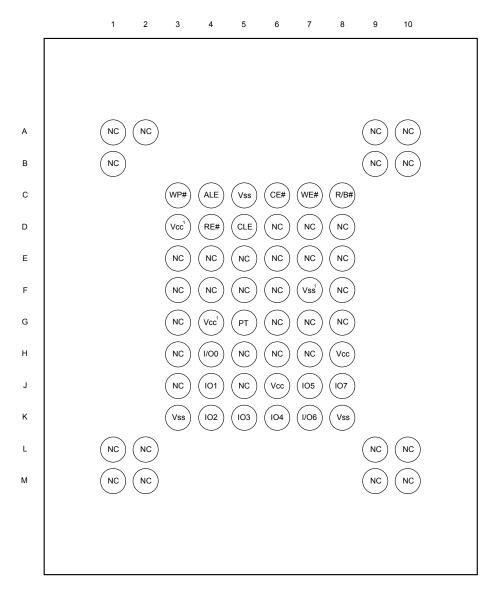

#### 63-ball 9mmx11mm VFBGA

**Note 1.** These pins might not be connected internally; however, it is recommended to connect these pins to power (or ground) as designated for ONFI compatibility.

## **3-1. PIN DESCRIPTIONS**

| SYMBOL    | PIN NAME                                                                                                                         |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 107 - 100 | Data I/O port                                                                                                                    |  |  |  |  |

| CE#       | Chip Enable (Active Low)                                                                                                         |  |  |  |  |

| RE#       | Read Enable (Active Low)                                                                                                         |  |  |  |  |

| WE#       | Write Enable (Active Low)                                                                                                        |  |  |  |  |

| CLE       | Command Latch Enable                                                                                                             |  |  |  |  |

| ALE       | Address Latch Enable                                                                                                             |  |  |  |  |

| WP#       | Write Protect (Active Low)                                                                                                       |  |  |  |  |

| PT        | PT (Protection) pin connecting to high for entire chip protected and enabling the Block Protection. A weak pull-down internally. |  |  |  |  |

| R/B#      | Ready/Busy (Open Drain)                                                                                                          |  |  |  |  |

| VSS       | Ground                                                                                                                           |  |  |  |  |

| VCC       | Power Supply for Device Operation                                                                                                |  |  |  |  |

| NC        | Not Connected Internally                                                                                                         |  |  |  |  |

#### **PIN FUNCTIONS**

The MX30LF1G18AC device is a sequential access memory that utilizes multiplexing input of Command/Address/Data.

#### I/O PORT: IO7 - IO0

The IO7 to IO0 pins are for address/command input and data output to/from the device.

#### **CHIP ENABLE: CE#**

The device goes into low-power Standby Mode when CE# goes high during a read operation and not at busy stage.

The CE# goes low to enable the device to be ready for standard operation. When the CE# goes high, the device is deselected. However, when the device is at busy stage, the device will not go to standby mode when CE# pin goes high.

#### **READ ENABLE: RE#**

The RE# (Read Enable) allows the data to be output by a tREA time after the falling edge of RE#. The internal address counter is automatically increased by one at the falling edge of RE#.

#### **WRITE ENABLE: WE#**

When the WE# goes low, the address/data/ command are latched at the rising edge of WE#.

#### COMMAND LATCH ENABLE: CLE

The CLE controls the command input. When the CLE goes high, the command data is latched at the rising edge of the WE#.

#### **ADDRESS LATCH ENABLE: ALE**

The ALE controls the address input. When the ALE goes high, the address is latched at the rising edge of WE#.

#### WRITE PROTECT: WP#

The WP# signal keeps low and then the memory will not accept the program/erase operation. It is recommended to keep WP# pin low during power on/off sequence. Please refer to **Figure 37. Power On/Off Sequence**.

#### READY/Busy: R/B#

The R/B# is an open-drain output pin. The R/B# outputs the ready/busy status of read/program/ erase operation of the device. When the R/B# is at low, the device is busy for read or program or erase operation. When the R/B# is at high, the read/ program/erase operation is finished.

Please refer to 8-1. R/B#: Termination for The Ready/Busy# Pin (R/B#) for details.

#### PT: Protection

When the PT pin is high at power on, the whole chip is protected even the WP# is at high; the unprotection procedure (through BP bits setting) is necessary before any program/erase operation. When the PT pin is connected to low or floating, the function of block protection is disabled.

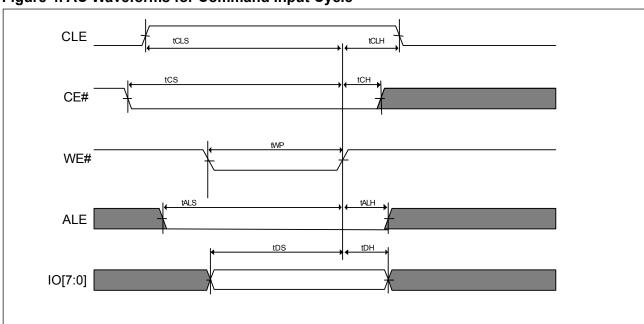

## 4. BLOCK DIAGRAM

#### 5. SCHEMATIC CELL LAYOUT AND ADDRESS ASSIGNMENT

MX30LF1G18AC is composed by 64 pages of (2,048+64)-byte in two NAND strings structure with 32 serial connected cells in each string. Each page has an additional 64 bytes for ECC and other purposes. The device has an on-chip buffer of 2,112 bytes for data load and access. Each 2K-Byte page has the two area, one is the main area which is 2048-bytes and the other is spare area which is 64-byte.

There are four address cycles for the address allocation, please refer to the table below.

**Table 1. Address Allocation**

| Addresses                  | 107 | 106 | IO5 | 104 | IO3 | IO2 | IO1 | 100 |

|----------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Column address - 1st cycle | A7  | A6  | A5  | A4  | A3  | A2  | A1  | A0  |

| Column address - 2nd cycle | L   | L   | L   | L   | A11 | A10 | A9  | A8  |

| Row address - 3rd cycle    | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

| Row address - 4th cycle    | A27 | A26 | A25 | A24 | A23 | A22 | A21 | A20 |

#### 6. DEVICE OPERATIONS

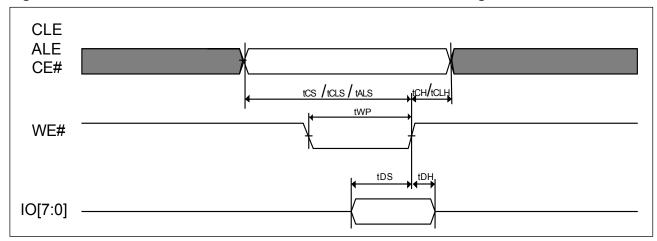

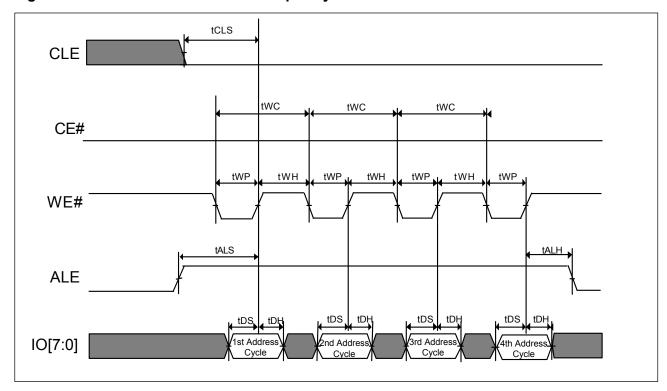

## 6-1. Address Input/Command Input/Data Input

Address input bus operation is for address input to select the memory address. The command input bus operation is for giving command to the memory. The data input bus is for data input to the memory device.

Figure 2. AC Waveforms for Command / Address / Data Latch Timing

Figure 3. AC Waveforms for Address Input Cycle

Figure 4. AC Waveforms for Command Input Cycle

Figure 5. AC Waveforms for Data Input Cycle

## 6-2. Page Read

Figure 6. AC Waveforms for Read Cycle

The MX30LF1G18AC array is accessed in Page of 2,112 bytes. External reads begins after the R/B# pin goes to READY.

The Read operation may also be initiated by writing the 00h command and giving the address (column and row address) and being confirmed by the 30h command, the MX30LF1G18AC begins the internal read operation and the chip enters busy state. The data can be read out in sequence after the chip is ready. Refer to Figure 6. AC Waveforms for Read Cycle.

If the host side uses a sequential access time (tRC) of less than 30ns, the data can be latched on the next falling edge of RE# as the waveform of EDO mode (Figure 9-2. AC Waveforms for Sequential Data Out Cycle (After Read) - EDO Mode).

To access the data in the same page randomly, a command of 05h may be written and only column address following and then confirmed by E0h command.

Figure 7. AC Waveforms for Read Operation (Intercepted by CE#)

17

Figure 8. AC Waveforms for Read Operation (with CE# Don't Care)

**Note:** The CE# "Don't Care" feature may simplify the system interface, which allows controller to directly download the code from flash device, and the CE# transitions will not stop the read operation during the latency time.

Figure 9-1. AC Waveforms for Sequential Data Out Cycle (After Read)

Figure 9-2. AC Waveforms for Sequential Data Out Cycle (After Read) - EDO Mode

Figure 10. AC Waveforms for Random Data Output

## 6-3. Cache Read Sequential

The cache read sequential operation is for throughput enhancement by using the internal cache buffer. It allows the consecutive pages to be read-out without giving next page address, which reduces the latency time from tR to tRCBSY between pages or blocks. While the data is read out on one page, the data of next page can be read into the cache buffer.

After writing the 00h command, the column and row address should be given for the start page selection, and followed by the 30h command for address confirmation. After that, the CACHE READ operation starts after a latency time tR and following a 31h command with the latency time of tRCBSY, the data can be readout sequentially from 1<sup>st</sup> column address (A[11:0]=000h) without giving next page address input. The 31h command is necessary to confirm the next cache read sequential operation and followed by a tRCBSY latency time before next page data is necessary. The CACHE READ SEQUENTIAL command is also valid for the consecutive page cross block.

The random data out (05h-E0h) command set is available to change the column address of the current page data in the cache register.

The user can check the chip status by the following method:

- R/B# pin ("0" means the data is not ready, "1" means the user can read the data)

- Status Register (SR[6] functions the same as R/B# pin, SR[5] indicates the internal chip operation, "0" means the chip is in internal operation and "1" means the chip is idle.) Status Register can be checked after the Read Status command (70h) is issued. Command 00h should be given to return to the cache read sequential operation.

To confirm the last page to be read-out during the cache read sequential operation, a 3Fh command is needed to replace the 31h command prior to the last data-out.

R/B#

Figure 11-1. AC Waveforms for Cache Read Sequential

#### 6-4. Cache Read Random

The main difference from the Cache Read Sequential operation is the Cache Read Random operation may allow the random page to be read-out with cache operation not just for the consecutive page only.

After writing the 00h command, the column and row address should be given for the start page selection, and followed by the 30h command for address confirmation. The column address is ignored in the cache read random operation. And then, the CACHE READ RANDOM operation starts after a latency time tR and following a 00h command with the selected page address and following a 31h command, the data can be read-out sequentially from the 1<sup>st</sup> column address (A[11:0] =000h) after the latency time of tRCBSY. After the previous selected page data out, a new selected page address can be given by writing the 00h-31h command set again. The CACHE READ RANDOM command is also valid for the consecutive page cross block.

The random data out (05h-E0h) command set is available to change the column address of the current page data in the cache register.

The user can check the chip status by the following method:

- R/B# pin ("0" means the data is not ready, "1" means the user can read the data)

- Status Register can be checked after the Read Status command (70h) is issued. (SR[6] behaves the same as R/B# pin, SR[5] indicates the internal chip operation, "0" means the chip is in internal operation and "1" means the chip is idle.) Command 00h should be given to return to the cache read operation.

To confirm the last page to be read-out during the cache read operation, a 3Fh command is needed to replace the 31h command prior to the last data-out.

Figure 11-2. AC Waveforms for Cache Read Random

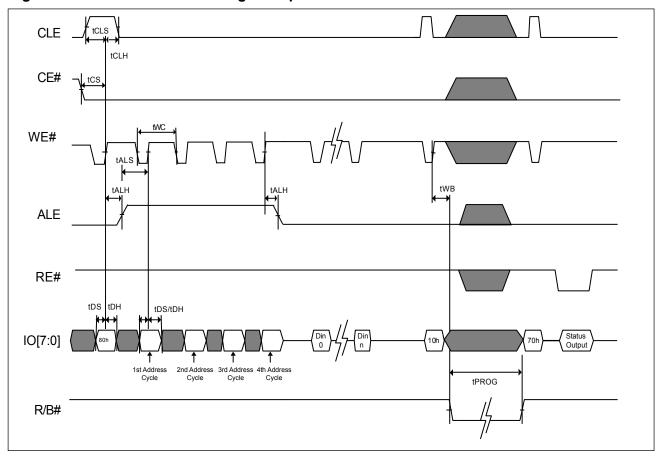

### 6-5. Page Program

The memory is programmed by page, which is 2,112 bytes. After Program load command (80h) is issued and the row and column address is given, the data will be loaded into the chip sequentially. Random Data Input command (85h) allows multi-data load in non-sequential address. After data load is complete, program confirm command (10h) is issued to start the page program operation. The page program operation in a block should start from the low address to high address. Partial program in a page is allowed up to 4 times. However, the random data input mode for programming a page is allowed and number of times is not limited.

The status of the program completion can be detected by R/B# pin or Status register bit SR[6].

The program result is shown in the chip status bit (SR[0]). SR[0] = 1 indicates the Page Program is not successful and SR[0] = 0 means the program operation is successful.

During the Page Program progressing, only the read status register command and reset command are accepted, others are ignored.

Figure 12. AC Waveforms for Program Operation after Command 80H