# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

#### **General Description**

The MAX30003 is a complete, biopotential, analog frontend solution for wearable applications. It offers high performance for clinical and fitness applications, with ultra-low power for long battery life. The MAX30003 is a single biopotential channel providing ECG waveforms and heart rate detection.

The biopotential channel has ESD protection, EMI filtering, internal lead biasing, DC leads-off detection, ultra-low power leads-on detection during standby mode, and extensive calibration voltages for built-in self-test. Soft power-up sequencing ensures no large transients are injected into the electrodes. The biopotential channel also has high input impedance, low noise, high CMRR, programmable gain, various low-pass and high-pass filter options, and a high resolution analog-to-digital converter. The biopotential channel is DC coupled, can handle large electrode voltage offsets, and has a fast recovery mode to quickly recover from overdrive conditions, such as defibrillation and electrosurgery.

The MAX30003 is available in a 28-pin TQFN and 30-bump wafer-level package (WLP), operating over the  $0^{\circ}$ C to +70°C commercial temperature range.

#### **Applications**

- Single-Lead Event Monitors for Arrhythmia Detection

- Single-Lead Wireless Patches for At-Home/ In-Hospital Monitoring

- Chest Band Heart Rate Monitors for Fitness Applications

- Bio Authentication and ECG-On-Demand Applications

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Clinical-Grade ECG AFE with High-Resolution Data Converter

- + 15.5 Bits Effective Resolution with  $5\mu V_{P-P}$  Noise

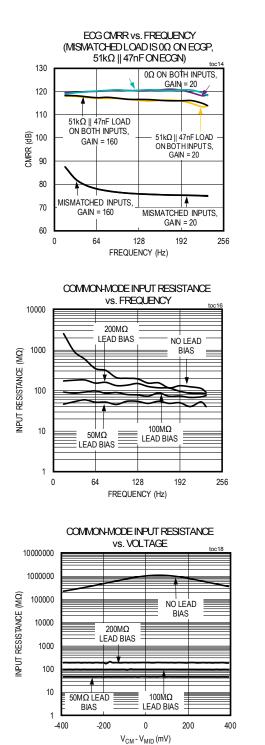

- Better Dry Starts Due to Much Improved Real World CMRR and High Input Impedance

- Fully Differential Input Structure with CMRR > 100dB

- Offers Better Common-Mode to Differential Mode Conversion Due to High Input Impedance

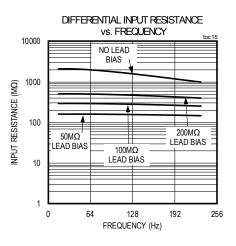

- High Input Impedance > 500MΩ for Extremely Low Common-to-Differential Mode Conversion

- Minimum Signal Attenuation at the Input During Dry Start Due to High Electrode Impedance

- High DC Offset Range of ±650mV (1.8V, typ) Allows to Be Used with Wide Variety of Electrodes

- High AC Dynamic Range of 65mV<sub>P-P</sub> Will Help the AFE Not Saturate in the Presence of Motion/Direct Electrode Hits

- Longer Battery Life Compared to Competing Solutions

85µW at 1.1V Supply Voltage

- Leads-On Interrupt Feature Allows to Keep µC in Deep Sleep Mode with RTC Off Until Valid Lead Condition is Detected

- Lead-On Detect Current: 0.7µA (typ)

- Built-In Heart Rate Detection with Interrupt Feature Eliminates the Need to Run HR Algorithm on the µController

- Robust R-R Detection in High Motion Environment at Extremely Low Power

- Configurable Interrupts Allows the µC Wake-Up Only on Every Heart Beat Reducing the Overall System Power

- High Accuracy Allows for More Physiological Data Extractions

- 32-Word FIFO Allows You to Wake Up µController Every 256ms with Full ECG Acquisition

- High-Speed SPI Interface

- Shutdown Current of 0.5µA (typ)

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

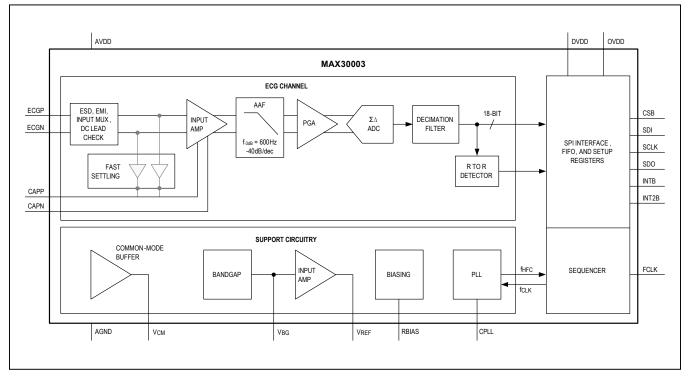

## **Functional Diagram**

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

#### **Absolute Maximum Ratings**

| AV <sub>DD</sub> to AGND0.3V to +2.0V                       |

|-------------------------------------------------------------|

| DV <sub>DD</sub> to DGND0.3V to +2.0V                       |

| $AV_{DD}$ to $DV_{DD}$ 0.3V to +0.3V                        |

| OV <sub>DD</sub> to DGND0.3V to +3.6V                       |

| AGND to DGND0.3V to +0.3V                                   |

| CSB, SCLK, SDI, FCLK to DGND0.3V to +3.6V                   |

| SDO, INTB, INT2B to                                         |

| DGND0.3V to the lower of (3.6V and OV <sub>DD</sub> + 0.3V) |

| All other pins to                                           |

| AGND0.3V to the lower of (2.0V and AV <sub>DD</sub> + 0.3V) |

| Maximum Current into Any Pin±50mA                           |

## Package Thermal Characteristics (Note 1)

#### TQFN

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$ ......29°C/W Junction-to-Case Thermal Resistance  $(\theta_{JC})$ ......2°C/W

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 28-Pin TQFN (derate 34.5mW/°C above +                 | 70°C)2758.6mW  |

| 30-Bump WLP (derate 24.3mW/°C                         |                |

| above +70°C)                                          | 1945.5mW       |

| Operating Temperature Range                           | 0°C to +70°C   |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (Soldering, 10sec)                   | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

#### WLP

Junction-to-Ambient Thermal Resistance (0JA) .......44°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, \text{f}_{FCLK} = 32.768 \text{kHz}, \text{T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted}. \text{Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, \text{T}_{A} = +25^{\circ}\text{C.}) \text{ (Note 2)}$

| PARAMETER                   | SYMBOL                                                                      | CONDITIONS                                                                               | MIN  | TYP   | MAX  | UNITS             |

|-----------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|-------|------|-------------------|

| ECG CHANNEL                 |                                                                             |                                                                                          |      |       |      |                   |

| AC Differential Input Dense |                                                                             | V <sub>AVDD</sub> = +1.1V, THD < 0.3%                                                    | -15  |       | +15  |                   |

| AC Differential Input Range |                                                                             | V <sub>AVDD</sub> = +1.8V, THD < 0.3%                                                    |      | ±32.5 |      | mV <sub>p-p</sub> |

| DC Differential Input Range |                                                                             | V <sub>AVDD</sub> = +1.1V, shift from nominal gain < 2%                                  | -300 |       | +300 | mV                |

|                             |                                                                             | V <sub>AVDD</sub> = +1.8V                                                                |      | ±650  |      | IIIV              |

| Common Mode Input Range     | V <sub>AVDD</sub> = +1.1V, from V <sub>MID</sub> , shi<br>nominal gain < 2% |                                                                                          | -150 |       | +150 |                   |

|                             |                                                                             | V <sub>AVDD</sub> = +1.8V, from V <sub>MID</sub> , shift from<br>nominal gain < 2%       |      | ±550  |      | mV                |

| Common Mode Rejection       | CMRR                                                                        | $0\Omega$ source impedance, f = 64Hz (Note 3)                                            | 105  | 115   |      | dB                |

| Ratio                       | CIVILAR                                                                     | (Note 4)                                                                                 |      | 77    |      | UD                |

|                             |                                                                             |                                                                                          |      | 0.82  |      | μV <sub>RMS</sub> |

| ECG Channel Input           |                                                                             | BW = 0.05 - 150Hz, G <sub>CH</sub> = 20x                                                 |      | 5.4   |      | μV <sub>p-p</sub> |

| Referred Noise              |                                                                             | $\mathbf{D}(\mathbf{M} = 0.05, 10) = \mathbf{C}_{\mathbf{M}} = 20^{12} (\text{Note } 2)$ |      | 0.53  | 1.0  | μV <sub>RMS</sub> |

|                             |                                                                             | BW = 0.05 - 40Hz, G <sub>CH</sub> = 20x (Note 3)                                         |      | 3.5   | 6.6  | μV <sub>p-p</sub> |

| Input Leakage Current       |                                                                             | T <sub>A</sub> = +25°C                                                                   | -1   | 0.1   | +1   | nA                |

|                             |                                                                             | Common-mode, DC                                                                          |      | 45    |      | GΩ                |

| Input Impedance (INA)       |                                                                             | Differential, DC                                                                         |      | 1500  |      | MΩ                |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

### **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, \text{f}_{FCLK} = 32.768 \text{kHz}, \text{T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, \text{T}_{A} = +25^{\circ}\text{C.}) \text{ (Note 2)}$

| PARAMETER                               | SYMBOL           |                                                          | MIN                                                                                      | TYP                               | MAX        | UNITS |             |

|-----------------------------------------|------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------|------------|-------|-------------|

| ECG Channel Total                       | THD              | V <sub>AVDD</sub> = +1.80<br>G <sub>CH</sub> = 20x, ele  |                                                                                          | 0.025                             |            | %     |             |

| Harmonic Distortion                     |                  |                                                          | V, $V_{IN} = 30 \text{mV}_{p-p}$ , $F_{IN} = 64 \text{Hz}$ ,<br>ectrode offset = ±300 mV |                                   |            | 0.3   | ,0          |

| ECG Channel Gain Setting                | G <sub>CH</sub>  | Programmable                                             | e, see register map                                                                      |                                   | 20 to 160  |       | V/V         |

|                                         |                  | V <sub>AVDD</sub> = +1.8<br>ECGP = ECG                   |                                                                                          | -2.5                              |            | +2.5  | %           |

| ECG Channel Gain Error                  |                  | V <sub>AVDD</sub> = +1.1<br>ECGP = ECG                   |                                                                                          | -4.5                              |            | +4.5  | %           |

| ECG Channel Offset Error                |                  | (Note 5)                                                 |                                                                                          |                                   | 0.1        |       | % of<br>FSR |

| ADC Resolution                          |                  |                                                          |                                                                                          |                                   | 18         |       | Bits        |

| ADC Sample Rate                         |                  | Programmable                                             | e, see register map                                                                      |                                   | 125 to 512 |       | SPS         |

| CAPP to CAPN Impedance                  | R <sub>HPF</sub> |                                                          | R <sub>HPF</sub> x C <sub>HPF</sub> ), C <sub>HPF</sub> =<br>etween CAPP and CAPN        | 320                               | 450        | 600   | kΩ          |

|                                         |                  | Fast recovery enabled (1.8V)Fast recovery enabled (1.1V) |                                                                                          |                                   | 160        |       |             |

| Analog High-Pass Filter Slew<br>Current |                  |                                                          |                                                                                          | Fast recovery enabled (1.1V)   55 |            |       | μA          |

| Guneni                                  |                  | Fast recovery                                            |                                                                                          | 0.09                              |            |       |             |

| Fast Settling Recovery Time             |                  | C <sub>HPF</sub> = 10µF,<br>see Table 3.                 | Note: varies by sample rate,                                                             |                                   | 500        |       | ms          |

|                                         |                  |                                                          | DLPF[0:1] = 01                                                                           |                                   | 40         |       |             |

| Digital Low-Pass Filter                 |                  | Linear phase<br>FIR filter.                              | DLPF[0:1] = 10                                                                           |                                   | 100        |       | Hz          |

|                                         |                  |                                                          | DLPF[0:1] = 11                                                                           |                                   | 150        |       |             |

| Digital High-Pass Filter                |                  | Phase-correcte                                           | d 1st-order IIR filter. DHPF = 1                                                         |                                   | 0.5        |       | Hz          |

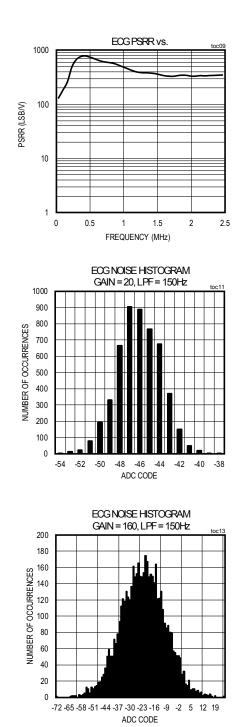

| ECG Power Supply Rejection              | PSRR             | Lead bias disa                                           | bled, DC                                                                                 |                                   | 107        |       | dB          |

|                                         |                  | Lead bias disa                                           | bled, f <sub>SW</sub> = 64Hz                                                             |                                   | 110        |       | dD          |

| ECG INPUT MUX                           |                  |                                                          |                                                                                          |                                   |            |       |             |

|                                         |                  |                                                          | DCLOFF_IMAG[2:0] = 001                                                                   |                                   | 5          |       |             |

|                                         |                  | D. H                                                     | DCLOFF_IMAG[2:0] = 010                                                                   |                                   | 10         |       |             |

| DC Lead Off Check                       |                  | Pullup/<br>pulldown                                      | DCLOFF_IMAG[2:0] = 011                                                                   |                                   | 20         |       | nA          |

|                                         |                  |                                                          | DCLOFF_IMAG[2:0] = 100                                                                   | MAG[2:0] = 100 50                 |            |       | 1           |

|                                         |                  |                                                          | DCLOFF_IMAG[2:0] = 101                                                                   |                                   |            |       |             |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

## **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, \text{f}_{FCLK} = 32.768 \text{kHz}, \text{T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, \text{T}_{A} = +25^{\circ}\text{C.}) \text{ (Note 2)}$

| PARAMETER                                          | SYMBOL            | CO                                                             | NDITIONS                                        | MIN                       | TYP MAX             | UNITS  |

|----------------------------------------------------|-------------------|----------------------------------------------------------------|-------------------------------------------------|---------------------------|---------------------|--------|

|                                                    |                   | DCLOFF_VTH[1:0]                                                | = 11 (Note 6)                                   | V <sub>MI</sub>           | <sub>D</sub> - 0.50 |        |

| DC Lead Off Comparator Low                         |                   | DCLOFF_VTH[1:0] = 10 (Note 7)<br>DCLOFF_VTH[1:0] = 01 (Note 8) |                                                 | V <sub>MI</sub>           | <sub>D</sub> - 0.45 |        |

| Threshold                                          |                   |                                                                |                                                 | V <sub>MID</sub> - 0.40   |                     | V      |

|                                                    |                   | DCLOFF_VTH[1:0]                                                | V <sub>MI</sub>                                 | <sub>D</sub> - 0.30       | 1                   |        |

|                                                    |                   | DCLOFF_VTH[1:0]                                                | = 11 (Note 6)                                   | V <sub>MIE</sub>          | <sub>0</sub> + 0.50 |        |

| DC Lead Off Comparator                             |                   | DCLOFF_VTH[1:0]                                                | = 10 (Note 7)                                   | V <sub>MIE</sub>          | <sub>0</sub> + 0.45 |        |

| High Threshold                                     |                   | DCLOFF_VTH[1:0]                                                | = 01 (Note 8)                                   | V <sub>MIC</sub>          | <sub>0</sub> + 0.40 | V      |

|                                                    |                   | DCLOFF_VTH[1:0]                                                | = 00                                            | V <sub>MIE</sub>          | <sub>D</sub> + 0.30 | 1      |

|                                                    |                   |                                                                | RBIASV[1:0] = 00                                |                           | 50                  |        |

| Lead Bias Impedance                                |                   | Lead bias<br>enabled                                           | RBIASV[1:0] = 01                                |                           | 100                 | MΩ     |

|                                                    |                   | enabled                                                        | RBIASV[1:0] = 10                                | :                         | 200                 | 1      |

| Lead Bias Voltage                                  | V <sub>MID</sub>  | Lead bias enabled                                              |                                                 | avdd <sup>/</sup><br>2.15 | V                   |        |

| Calibration Voltage                                |                   |                                                                | VMAG = 0                                        | (                         | 0.25                |        |

| Magnitude                                          |                   | Single-ended                                                   | VMAG = 1                                        | 0.50                      |                     | mV     |

| Calibration Voltage<br>Magnitude Error             |                   | Single-ended (Note                                             | -2                                              | +2                        | %                   |        |

| Calibration Voltage<br>Frequency                   |                   | Programmable, see register map 0.0156 to 256                   |                                                 |                           |                     | Hz     |

| Calibration Voltage Pulse                          |                   | Programmable,                                                  | FIFTY = 0                                       | 0.03052<br>to 62.474      |                     | ms     |

| Time                                               |                   | see register map                                               | FIFTY = 1                                       |                           | %                   |        |

| INTERNAL REFERENCE/COM                             | MON-MODE          |                                                                |                                                 |                           |                     |        |

| V <sub>BG</sub> Output Voltage                     | V <sub>BG</sub>   |                                                                |                                                 | 0                         | .650                | V      |

| V <sub>BG</sub> Output Impedance                   |                   |                                                                |                                                 |                           | 100                 | kΩ     |

| External V <sub>BG</sub> Compensation<br>Capacitor | C <sub>VBG</sub>  |                                                                |                                                 | 1                         |                     | μF     |

| V <sub>REF</sub> Output Voltage                    | V <sub>REF</sub>  | T <sub>A</sub> = +25°C                                         |                                                 | 0.995 1                   | .000 1.005          | V      |

| V <sub>REF</sub> Temperature Coefficient           | TC <sub>REF</sub> | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$                    | $_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ 10 |                           | 10                  | ppm/°C |

| V <sub>REF</sub> Buffer Line Regulation            |                   |                                                                |                                                 |                           | 330                 | μV/V   |

| V <sub>REF</sub> Buffer Load Regulation            |                   | I <sub>LOAD</sub> = 0 to 100μA                                 | A                                               |                           | 25                  | μV/μA  |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

## **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, \text{f}_{FCLK} = 32.768 \text{kHz}, \text{T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, \text{T}_{A} = +25^{\circ}\text{C.}) \text{ (Note 2)}$

| PARAMETER                                           | SYMBOL                                   |                                                               | CONDITIONS                           | MIN                        | TYP                        | MAX                       | UNITS |

|-----------------------------------------------------|------------------------------------------|---------------------------------------------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|-------|

| External V <sub>REF</sub> Compensation<br>Capacitor | C <sub>REF</sub>                         |                                                               |                                      | 1                          | 10                         |                           | μF    |

| V <sub>CM</sub> Output Voltage                      | V <sub>CM</sub>                          |                                                               |                                      |                            | 0.650                      |                           | V     |

| External V <sub>CM</sub> Compensation<br>Capacitor  | C <sub>CM</sub>                          |                                                               |                                      | 1                          | 10                         |                           | μF    |

| DIGITAL INPUTS (SDI, SCLK,                          | CSB, FCLK)                               |                                                               |                                      | •                          | -                          |                           |       |

| Input-Voltage High                                  | V <sub>IH</sub>                          |                                                               |                                      | 0.7 ×<br>V <sub>OVDD</sub> |                            |                           | V     |

| Input-Voltage Low                                   | VIL                                      |                                                               |                                      |                            |                            | 0.3×<br>V <sub>OVDD</sub> | V     |

| Input Hysteresis                                    | V <sub>HYS</sub>                         |                                                               |                                      |                            | 0.05×<br>V <sub>OVDD</sub> |                           | V     |

| Input Capacitance                                   | C <sub>IN</sub>                          |                                                               |                                      |                            | 10                         |                           | pF    |

| Input Current                                       | I <sub>IN</sub>                          |                                                               |                                      | -1                         |                            | +1                        | μA    |

| DIGITAL OUTPUTS (SDO, INT                           | B, INT2B)                                |                                                               |                                      |                            |                            |                           |       |

| Output Voltage High                                 | V <sub>OH</sub>                          | I <sub>SOURCE</sub> = 1                                       | I <sub>SOURCE</sub> = 1mA            |                            |                            |                           | V     |

| Output Voltage Low                                  | V <sub>OL</sub>                          | I <sub>SINK</sub> = 1mA                                       |                                      |                            |                            | 0.4                       | V     |

| Three-State Leakage Current                         |                                          |                                                               |                                      | -1                         |                            | +1                        | μA    |

| Three-State Output<br>Capacitance                   |                                          |                                                               |                                      |                            | 15                         |                           | pF    |

| POWER SUPPLY                                        |                                          |                                                               |                                      |                            |                            |                           |       |

| Analog Supply Voltage                               | V <sub>AVDD</sub>                        | Connect VAV                                                   | <sub>/DD</sub> to V <sub>DVDD</sub>  | 1.1                        |                            | 2.0                       | V     |

| Digital Supply Voltage                              | V <sub>DVDD</sub>                        | Connect VDV                                                   | / <sub>DD</sub> to V <sub>AVDD</sub> | 1.1                        |                            | 2.0                       | V     |

| Interface Supply Voltage                            | V <sub>OVDD</sub>                        | Power for I/C                                                 | ) drivers only                       | 1.65                       |                            | 3.6                       | V     |

|                                                     |                                          |                                                               | $V_{AVDD} = V_{DVDD} = +1.1V$        |                            | 76                         |                           |       |

|                                                     |                                          | ECG<br>channel                                                | $V_{AVDD} = V_{DVDD} = +1.8V$        |                            | 100                        |                           |       |

| Supply Current                                      | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> |                                                               | $V_{AVDD} = V_{DVDD} = +2.0V$        |                            | 109                        | 120                       | μA    |

|                                                     | עטעטי                                    | ULP Lead                                                      | T <sub>A</sub> = +70°C               |                            | 0.98                       |                           |       |

|                                                     |                                          | On Detect                                                     | T <sub>A</sub> = +25°C               |                            | 0.73                       | 2.5                       |       |

|                                                     |                                          | V <sub>OVDD</sub> = +1<br>(Note 10)                           | .65V, ECG channel at 512sps          |                            | 0.2                        |                           |       |

| Interface Supply Current                            | IOVDD                                    | V <sub>OVDD</sub> = +3.6V, ECG channel at 512sps<br>(Note 10) |                                      |                            | 0.6                        | 1.6                       | μA    |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

### **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, \text{f}_{FCLK} = 32.768 \text{kHz}, \text{T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, \text{T}_{A} = +25^{\circ}\text{C.}) \text{ (Note 2)}$

| PARAMETER        | SYMBOL | CONDITIONS                                                               |                             |  | TYP  | MAX | UNITS |

|------------------|--------|--------------------------------------------------------------------------|-----------------------------|--|------|-----|-------|

| Shutdown Current |        | $V_{AVDD} = V_{DVDD}$<br>= 2.0V                                          | T <sub>A</sub> = +70°C      |  | 0.79 |     |       |

|                  |        | – 2.0v<br>(Note 5)                                                       | T <sub>A</sub> = +25°C      |  | 0.51 | 2.5 | μA    |

|                  | ISOVDD | V <sub>OVDD</sub> = +3.6V, V <sub>AVDD</sub> = V <sub>DVDD</sub> = +2.0V |                             |  |      | 1.1 |       |

| ESD PROTECTION   |        |                                                                          |                             |  |      |     |       |

|                  |        | IEC61000-4-2                                                             | Contact Discharge (Note 11) |  | ±8   |     |       |

| ECGP, ECGN       |        | IEC61000-4-2                                                             | Air-Gap Discharge (Note 11) |  | ±15  |     | kV    |

|                  |        | НММ                                                                      |                             |  | ±8   |     |       |

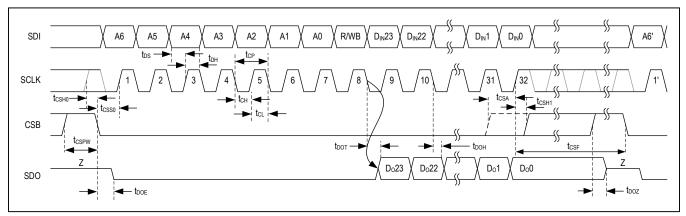

### **Timing Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DVDD} = +1.8V, V_{OVDD} = +2.5V, T_A = +25^{\circ}C.$ ) (Notes 2, 3)

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                                 | MIN | TYP | MAX | UNITS |  |  |  |  |  |  |

|-------------------------------------|-------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|--|--|--|--|--|

| TIMING CHARACTERISTICS              |                   |                                                                                            |     |     |     |       |  |  |  |  |  |  |

| SCLK Frequency                      | fsclk             |                                                                                            | 0   |     | 12  | MHz   |  |  |  |  |  |  |

| SCLK Period                         | t <sub>CP</sub>   |                                                                                            | 83  |     |     | ns    |  |  |  |  |  |  |

| SCLK Pulse Width High               | t <sub>CH</sub>   |                                                                                            | 15  |     |     | ns    |  |  |  |  |  |  |

| SCLK Pulse Width Low                | t <sub>CL</sub>   |                                                                                            | 15  |     | •   | ns    |  |  |  |  |  |  |

| CSB Fall to SCLK Rise<br>Setup Time | t <sub>CSS0</sub> | To 1st SCLK rising edge (RE)                                                               | 15  |     |     | ns    |  |  |  |  |  |  |

| CSB Fall to SCLK Rise<br>Hold Time  | t <sub>CSH0</sub> | Applies to inactive RE preceding 1st RE                                                    | 0   |     |     | ns    |  |  |  |  |  |  |

| CSB Rise to SCLK Rise<br>Hold Time  | t <sub>CSH1</sub> | Applies to 32nd RE, executed write                                                         | 10  |     |     | ns    |  |  |  |  |  |  |

| CSB Rise to SCLK Rise               | t <sub>CSA</sub>  | Applies to 32nd RE, aborted write sequence                                                 | 15  |     |     | ns    |  |  |  |  |  |  |

| SCLK Rise to CSB Fall               | t <sub>CSF</sub>  | Applies to 32nd RE                                                                         | 100 |     |     | ns    |  |  |  |  |  |  |

| CSB Pulse-Width High                | t <sub>CSPW</sub> |                                                                                            | 20  |     |     | ns    |  |  |  |  |  |  |

| SDI-to-SCLK Rise Setup Time         | t <sub>DS</sub>   |                                                                                            | 8   |     |     | ns    |  |  |  |  |  |  |

| SDI to SCLK Rise Hold Time          | t <sub>DH</sub>   |                                                                                            | 8   |     |     | ns    |  |  |  |  |  |  |

|                                     |                   | C <sub>LOAD</sub> = 20pf                                                                   |     |     | 40  | ns    |  |  |  |  |  |  |

| SCLK Fall to SDO Transition         | t <sub>DOT</sub>  | $C_{LOAD} = 20 \text{pf}, V_{AVDD} = V_{DVDD} \ge 1.8 \text{V}, V_{DVDD} \ge 2.5 \text{V}$ |     |     | 20  | ns    |  |  |  |  |  |  |

| SCLK Fall to SDO Hold               | tDOH              | C <sub>LOAD</sub> = 20pf                                                                   | 2   |     |     | ns    |  |  |  |  |  |  |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

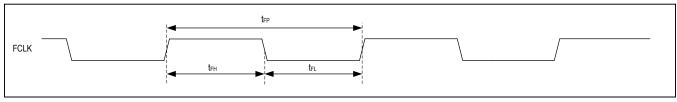

### **Timing Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V$  to +2.0V,  $V_{OVDD} = +1.65V$  to +3.6V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DVDD} = +1.8V$ ,  $V_{OVDD} = +2.5V$ ,  $T_A = +25^{\circ}$ C.) (Notes 2, 3)

| PARAMETER             | SYMBOL            | CONDITIONS                            |  | TYP    | MAX | UNITS |

|-----------------------|-------------------|---------------------------------------|--|--------|-----|-------|

| CSB Fall to SDO Fall  | t <sub>DOE</sub>  | Enable time, C <sub>LOAD</sub> = 20pf |  |        | 30  | ns    |

| CSB Rise to SDO Hi-Z  | t <sub>DOZ</sub>  | Disable time                          |  |        | 35  | ns    |

| FCLK Frequency        | f <sub>FCLK</sub> | External reference clock              |  | 32.768 |     | kHz   |

| FCLK Period           | t <sub>FP</sub>   |                                       |  | 30.52  |     | μs    |

| FCLK Pulse-Width High | t <sub>FH</sub>   | 50% duty cycle assumed                |  | 15.26  |     | μs    |

| FCLK Pulse-Width Low  | t <sub>FL</sub>   | 50% duty cycle assumed                |  | 15.26  |     | μs    |

**Note 2:** Limits are 100% tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 3: Guaranteed by design and characterization. Not tested in production.

**Note 4:** One electrode drive with <10 $\Omega$  source impedance, the other driven with 51k $\Omega$  in parallel with a 47nF per IEC60601-2-47.

**Note 5:** Inputs connected to  $51k\Omega$  in parallel with a 47nF to V<sub>CM</sub>.

**Note 6:** Use this setting only for  $V_{AVDD} = V_{DVDD} \ge 1.65V$ .

**Note 7:** Use this setting only for  $V_{AVDD} = V_{DVDD} \ge 1.55V$ .

**Note 8:** Use this setting only for  $V_{AVDD} = V_{DVDD} \ge 1.45V$ .

**Note 9:** This specification defines the accuracy of the calibration voltage source as applied to the ECG input, not as measured through the ADC channel.

Note 10:  $f_{SCLK}$  = 4MHz, burst mode, EFIT = 8,  $C_{SDO}$  =  $C_{INTB}$  = 50pF.

Note 11: ESD test performed with  $1k\Omega$  series resistor designed to withstand 8kV surge voltage.

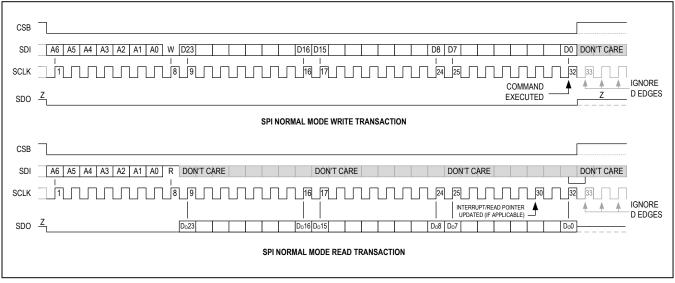

Figure 1a. SPI Timing Diagram

Figure 1b. FCLK Timing Diagram

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

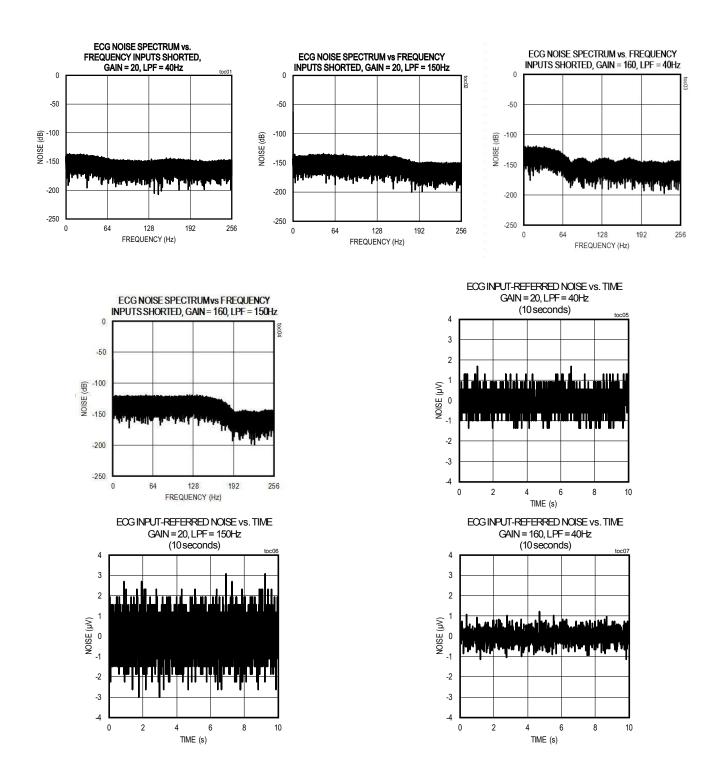

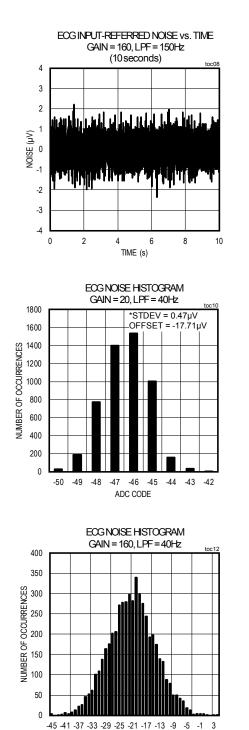

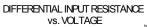

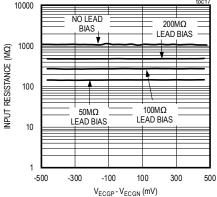

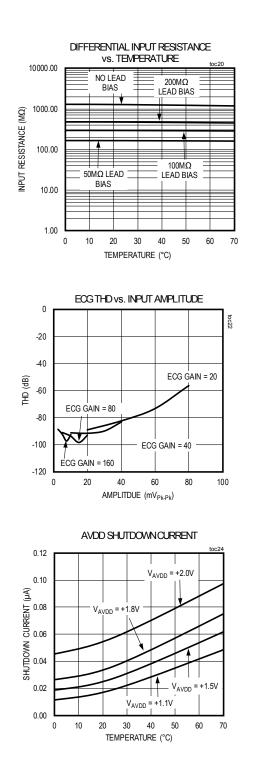

## **Typical Operating Characteristics**

(V<sub>DVDD</sub> = V<sub>AVDD</sub> = +1.8V, V<sub>OVDD</sub> = 2.5V, T<sub>A</sub> = +25°C, unless otherwise noted.)

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

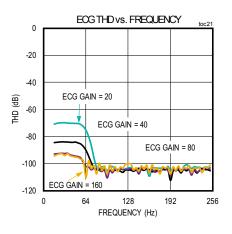

## **Typical Operating Characteristics (continued)**

(V<sub>DVDD</sub> = V<sub>AVDD</sub> = +1.8V, V<sub>OVDD</sub> = 2.5V, T<sub>A</sub> = +25°C, unless otherwise noted.)

ADC CODE

www.maximintegrated.com

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

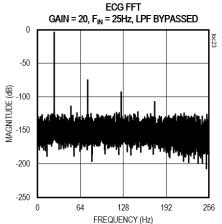

### **Typical Operating Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = 2.5V, T_A = +25^{\circ}C, unless otherwise noted.)$

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

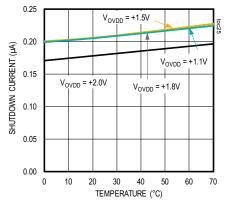

### **Typical Operating Characteristics (continued)**

(V<sub>DVDD</sub> = V<sub>AVDD</sub> = +1.8V, V<sub>OVDD</sub> = 2.5V, T<sub>A</sub> = +25°C, unless otherwise noted.)

OVDD SHUTDOWN CURRENT

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

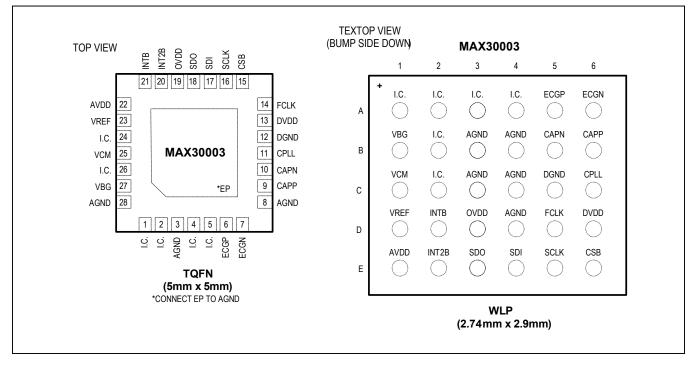

## **Pin Configurations**

### **Pin Description**

| PIN                   | BUMP                      |      | FUNCTION                                                                                                                                            |

|-----------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN                  | WLP                       | NAME | FUNCTION                                                                                                                                            |

| 1, 2, 4, 5, 24,<br>26 | A1, A2, A3,<br>A4, B2, C2 | I.C. | Internally Connected. Connect to AGND.                                                                                                              |

| 3,8,28                | B3, B4, C3,<br>C4, D4     | AGND | Analog Power and Reference Ground. Connect into the printed circuit board ground plane.                                                             |

| 6                     | A5                        | ECGP | ECG Positive Input                                                                                                                                  |

| 7                     | A6                        | ECGN | ECG Negative Input                                                                                                                                  |

| 9                     | B6                        | CAPP | Analog High-Pass Filter Input. Connect a $1\mu$ F X7R capacitor (CHPF) between CAPP and CAPN to form a 0.5Hz high-pass response in the ECG channel. |

| 10                    | В5                        | CAPN | Analog High-Pass Filter Input. Connect a $1\mu$ F X7R capacitor (CHPF) between CAPP and CAPN to form a 0.5Hz high-pass response in the ECG channel. |

| 11                    | C6                        | CPLL | PLL Loop Filter Input. Connect 1nF COG cap between CPLL and AGND.                                                                                   |

| 12                    | C5                        | DGND | Digital Ground for Both Digital Core and I/O Pad Drivers. Recommended to connect to AGND plane.                                                     |

| 13                    | D6                        | DVDD | Digital Core Supply Voltage. Connect to AVDD                                                                                                        |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

## **Pin Description (continued)**

| PIN  | PIN BUMP |                  | FUNCTION                                                                                                                     |  |  |  |  |

|------|----------|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TQFN | WLP      | NAME             | FUNCTION                                                                                                                     |  |  |  |  |

| 14   | D5       | FCLK             | External 32.768kHz Clock that Controls the Sampling of the Internal Sigma-Delta Converters and Decimator.                    |  |  |  |  |

| 15   | E6       | CSB              | Active-Low Chip-Select Input. Enables the serial interface.                                                                  |  |  |  |  |

| 16   | E5       | SCLK             | Serial Clock Input. Clocks data in and out of the serial interface when CSB is low.                                          |  |  |  |  |

| 17   | E4       | SDI              | Serial Data Input. SDI is sampled into the device on the rising edge of SCLK when CSB is low.                                |  |  |  |  |

| 18   | E3       | SDO              | Serial Data Output. SDO will change state on the falling edge of SCLK when CSB is low. SDO is three-stated when CSB is high. |  |  |  |  |

| 19   | D3       | OVDD             | Logic Interface Supply Voltage                                                                                               |  |  |  |  |

| 20   | E2       | INT2B            | Interrupt 2 Output. INT2B is an active-low status output. It can be used to interrupt an external device.                    |  |  |  |  |

| 21   | D2       | INTB             | Interrupt Output. INTB is an active low status output. It can be used to interrupt an external device.                       |  |  |  |  |

| 22   | E1       | AVDD             | Analog Core Supply Voltage. Connect to DVDD.                                                                                 |  |  |  |  |

| 23   | D1       | V <sub>REF</sub> | ADC Reference Buffer Output. Connect a 10 $\mu$ F X5R ceramic capacitor between V <sub>REF</sub> and AGND.                   |  |  |  |  |

| 25   | C1       | V <sub>CM</sub>  | Common Mode Buffer Output. Connect a $10\mu F$ X5R ceramic capacitor between $V_{CM}$ and AGND.                              |  |  |  |  |

| 27   | B1       | V <sub>BG</sub>  | Bandgap Noise Filter Output. Connect a 1.0 $\mu F$ X7R ceramic capacitor between $V_{BG}$ and AGND.                          |  |  |  |  |

| EP   | _        | _                | Exposed Paddle. Connect to AGND.                                                                                             |  |  |  |  |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

#### **Detailed Description**

#### **ECG Channel**

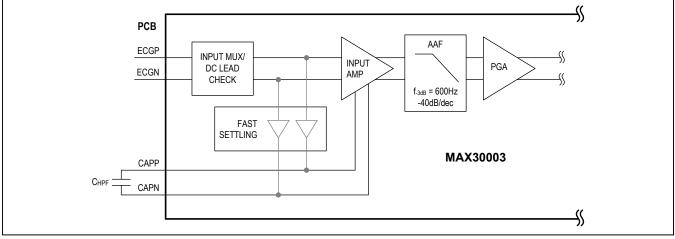

Figure 2 illustrates the ECG channel block diagram, excluding the ADC. The channel comprises an input MUX, a fast-recovering instrumentation amplifier, an antialias filter, and a programmable gain amplifier. The MUX includes several features such as ESD protection, EMI filtering, lead biasing, leads off checking, and ultra-low power leads-on checking. The output of this analog channel drives a high-resolution ADC.

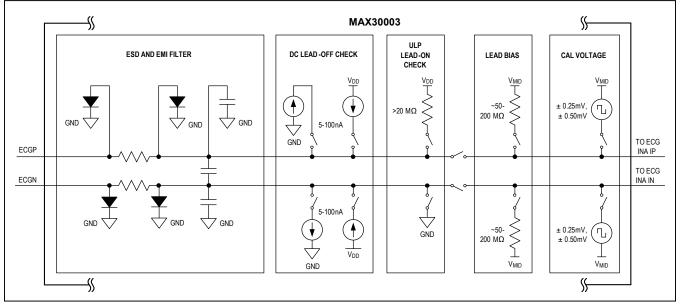

#### Input MUX

The ECG input MUX shown in Figure 3 contains integrated ESD and EMI protection, DC leads off detect current sources, lead-on detect, series isolation switches, lead biasing, and a programmable calibration voltage source to enable channel built in self-test.

#### **EMI Filtering and ESD Protection**

EMI filtering of the ECGP and ECGN inputs consists of a single pole, low pass, differential, and common mode filter with the pole located at approximately 2MHz. The ECGP and ECGN inputs also have input clamps that protect the inputs from ESD events.

Figure 2. ECG Channel Input Amplifier and PGA Excluding the ADC

Figure 3. ECG Input MUX

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

- ±8kV using the Contact Discharge method specified in IEC61000-4-2 ESD

- ±15kV using the Air Gap Discharge method specified in IEC61000-4-2 ESD

- ±8kV HBM

- For IEC61000-4-2 ESD protection, use 1kΩ series resistors on ECGP and ECGN that is rated to withstand 8kV surge voltages.

#### DC Leads-Off Detection and ULP Leads-On Detection

The input MUX leads-off detect circuitry consists of programmable sink/source DC current sources that allow for DC leads-off detection, while the channel is powered up in normal operation and an ultra-low-power (ULP) leads-on detect while the channel is powered-down.

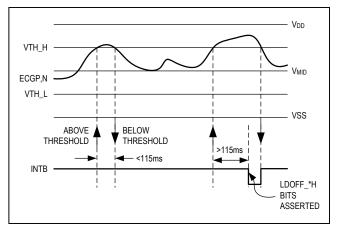

The MAX30003 accomplishes DC leads-off detection by applying a DC current to pull the ECG input voltage up to above  $V_{MID}$  +  $V_{TH}$  or down to below  $V_{MID}$  -  $V_{TH}$ . The current sources have user selectable values of 0nA, 5nA, 10nA, 20nA, 50nA, and 100nA that allow coverage of dry and wet electrode impedance ranges. Supported thresholds are  $V_{MID} \pm 0.30V$  (recommended),  $V_{MID} \pm 0.40V$ ,  $V_{MID} \pm$ 0.45V, and V<sub>MID</sub>  $\pm$  0.50V. A threshold of 400mV, 450mV, and 500mV should only be used when  $V_{AVDD} \ge 1.45V$ , 1.55V, and 1.65V, respectively. A dynamic comparator protects against false flags generated by the input amplifier and input chopping. The comparator checks for a minimum continuous violation (or threshold exceeded) of 115ms to 140ms depending on the setting of FMSTR[1:0] before asserting any one of the LDOFF \* interrupt flags (Figure 4). See registers CNFG\_GEN (0x10) and CNFG\_EMUX 0x14) for configuration settings and see Table 1 for recommended values given electrode type and supply voltage. The ULP lead on detect operates by pulling ECGN low with a pulldown resistance larger than  $5m\Omega$  and pulling ECGP high with a pullup resistance larger than  $15M\Omega$ . A low-power comparator determines if ECGP is pulled below a predefined threshold that occurs when both electrodes make contact with the body. When the impedance between ECGP and ECGN is less than 20mΩ, an interrupt LONINT is asserted, alerting the µC to a leads-on condition.

A 0nA/V<sub>MID</sub>  $\pm$  300mV selection is available allowing monitoring of the input compliance of the INA during non-DC lead-off checks.

#### Lead Bias

The MAX30003 limits the ECGP and ECGN DC input common mode range to V<sub>MID</sub>  $\pm$ 150mV. This range can be maintained either through external/internal lead-biasing.

Internal DC lead-biasing consists of 50M\Omega, 100M\Omega, or 200M\Omega selectable resistors to  $V_{MID}$  that drive the

Figure 4. Lead-Off Detect Behavior

electrodes within the input common mode requirements of the ECG channel and can drive the connected body to the proper common mode voltage level. See register CNFG\_GEN (0x10) to select a configuration.

#### **Isolation Switches**

The series switches in the MAX30003 isolate ECGP and ECGN pins (subject) from the internal signal path. the series switches are disabled by default. They must be enabled to record ECG.

#### **Calibration Voltage Sources**

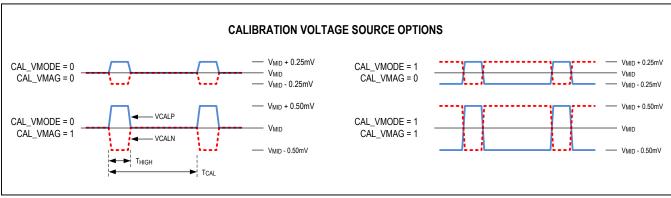

Calibration voltage sources are available to provide  $\pm 0.25 \text{mV} (0.5 \text{mV}_{\text{P-P}})$  or  $\pm 0.5 \text{mV} (1.0 \text{mV}_{\text{P-P}})$  inputs to the ECG channel with programmable frequency and duty cycle. The sources can be unipolar/bipolar relative to V<sub>MID</sub>.

<u>Figure 5</u> illustrates the possible calibration waveforms. Frequency selections are available in 4X increments from 15.625mHz to 256Hz with selected pulse widths varying from 30.5µs to 31.723ms and 50% duty cycle. Signals can be single-ended, differential, or common mode. This flexibility allows end-to-end channel-testing of the ECG signal path.

When applying calibration voltage sources with the device connected to a subject, the series input switches must be disconnected so as not to drive signals into the subject. See registers CNFG\_CAL (0x12) and CNFG\_EMUX (0x14) to select configuration.

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

# Table 1. Recommended Lead Bias, Current Source Values,and Thresholds for Electrode Impedance

|                         |        | ELECTRODES IMPEDANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |                |              |               |               |                |  |  |  |  |

|-------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|--------------|---------------|---------------|----------------|--|--|--|--|

| IDC<br>VTH              | <100kΩ | 100kΩ -<br>200kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 200kΩ -<br>400kΩ | 400kΩ -<br>1MΩ | 1ΜΩ -<br>2ΜΩ | 2ΜΩ - 4<br>ΜΩ | 4ΜΩ -<br>10ΜΩ | 10ΜΩ -<br>20ΜΩ |  |  |  |  |

| I <sub>DC</sub> = 10nA  |        | All settings of $R_b$<br>$V_{TH} = V_{MID}$<br>$\pm 300 \text{mV}, \pm 400 \text{mV}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                |              |               |               |                |  |  |  |  |

| I <sub>DC</sub> = 20nA  |        | All settings of $R_b$ All settings of $V_{TH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                |              |               |               |                |  |  |  |  |

| I <sub>DC</sub> = 50nA  |        | $\begin{array}{c} \mbox{All settings} & \mbox{of } R_b & \mbox{of } R_b & \mbox{V}_{TH} = & \mbox{V}_{MID} & \mbox{tings of } V_{TH} & \mbox{V}_{MID} & \mbox{tings} & \mbox{tings of } V_{TH} & \mbox{tings} & \mbo$ |                  |                |              |               |               |                |  |  |  |  |

| I <sub>DC</sub> = 100nA |        | $\begin{array}{c} 500 \text{mV} \\ \hline 500 \text{mV} \\ \hline 500 \text{mV} \\ \hline 500 \text{mV} \\ \hline \\ \text{All settings of R}_{\text{b}} \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \hline \\ \hline \\ \text{All settings of V}_{\text{TH}} \\ \hline \\ \hline \\ \hline \\ \\ \hline \\ \hline \\ \hline \\ \hline \\ \hline \\ \hline$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                |              |               |               |                |  |  |  |  |

Figure 5. Calibration Voltage Source Options

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

#### Gain Settings and Input Range

The device's ECG channel contains an input instrumentation amplifier that provides low-noise, fixed-gain amplification of the differential signal, rejects differential DC voltage due to electrode polarization, rejects common-mode interference primarily due to AC mains interference, and provides high input impedance to guarantee high CMRR even in the presence of severe electrode impedance mismatch (see Figure 2). The differential DC rejection corner frequency is set by an external capacitor (C<sub>HPF</sub>) placed between pins CAPP and CAPN, refer to Table 2 for appropriate value selection. There are three recommended options for the cutoff frequency: 4.4Hz, 0.4Hz, and 0.04Hz. Setting the cutoff frequency to 4.4Hz provides the most motion artifact rejection at the expense of ECG waveform quality, making it best suited for heart rate monitoring. For ambulatory applications requiring more robust ECG waveforms with moderate motion artifact rejection, 0.4Hz is recommended. Select 0.04Hz for patient monitoring applications in which ECG waveform quality is the primary concern and poor rejection of motion artifacts can be tolerated. The high-pass corner frequency is calculated by the following equation:

#### 1/(2r x R<sub>HPF</sub> x C<sub>HPF</sub>)

RHPF is specified in the Electrical Characteristics table.

Following the instrumentation amplifier is a 2-pole active anti-aliasing filter with a 600Hz -3dB frequency that provides 57dB of attenuation at half the modulator sampling rate (approximately 16kHz) and a PGA with programmable gains of 1, 2, 4, and 8V/V for an overall gain of 20, 40, 80, and 160V/V. The instrumentation amplifier and PGA are chopped to minimize offset and 1/f noise. Gain settings are configured via the CNFG\_ECG (0x15) register. The useable common-mode range is  $V_{MID} \pm 150$ mV, internal lead biasing can be used to meet this requirement. The useable DC differential range is  $\pm 300$ mV to allow for electrode polarization voltages on each electrode. The input AC differential range is  $\pm 32.5$ mV or  $\pm 65$ mV<sub>P-P</sub>.

#### **Fast Recovery Mode**

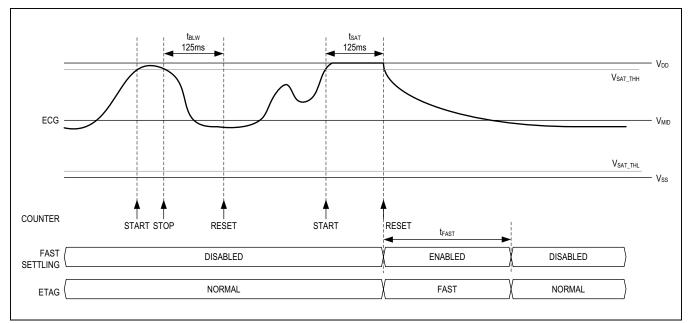

The input instrumentation amplifier has the ability to rapidly recover from an excessive overdrive event such as a defibrillation pulse, high-voltage external pacing, and electro-surgery interference. There are two modes of recovery that can be used: automatic or manual recovery. The mode is programmed by the FAST[1:0] bits in the MNGR\_DYN (0x05) register.

Automatic mode engages once the saturation counter exceeds approximately 125ms ( $t_{SAT}$ ). The counter is activated the first time the ADC output exceeds the symmetrical threshold defined by the FAST\_TH[5:0] bits

in the MNGR\_DYN (0x05) register and accumulates the time that the ADC output exceeds either the positive or negative threshold. If the saturation counter exceeds 125ms, it triggers the fast settling mode (if enabled) and resets. The saturation counter can also be reset prior to triggering the fast settling mode if the ADC output falls below the threshold continuously for 125ms ( $t_{BLW}$ ). This feature is designed to avoid false triggers due to the QRS complex. Once triggered, fast settling mode will be engaged for 500ms, see Figure 6. ECG samples are tagged if they were taken while fast settling mode was asserted.

In manual mode, a user algorithm running on the host microcontroller or an external stimulus input will generate the trigger to enter fast recovery mode. The host microcontroller then enables the manual fast recovery mode in the MNGR\_DYN (0x05) register. The manual fast recovery mode can be of a much shorter duration than the automatic mode and allows for more rapid recovery. One such example is recovery from external high-voltage pacing signals in a few milliseconds to allow the observation of a subsequent p-wave.

# Table 2. ECG Analog HPF CornerFrequency Selection

| C <sub>HPF</sub> | HPF CORNER FREQUENCY |

|------------------|----------------------|

| 0.1µ             | ≤ 5Hz                |

| 1.0µ             | ≤ 0.5Hz              |

| 10µ              | ≤ 0.05Hz             |

# Table 3. Fast Recovery Mode RecoveryTime vs. Number of Samples

| SAMPLE<br>RATE (sps) | NUMBER OF<br>SAMPLES | RECOVERY TIME<br>(APPROXIMATE) (ms) |

|----------------------|----------------------|-------------------------------------|

| 512                  | 255                  | 498                                 |

| 256                  | 127                  | 496                                 |

| 128                  | 63                   | 492                                 |

| 500                  | 249                  | 498                                 |

| 250                  | 124                  | 496                                 |

| 125                  | 64                   | 512                                 |

| 200                  | 99                   | 495                                 |

| 199.8                | 99                   | 495.5                               |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

Figure 6. Automatic Fast Settling Behavior

#### **Decimation Filter**

The decimation filter consists of a Cascaded Integrator Comb (CIC) decimation filter to the data rate followed by a programmable FIR filter to implement HPF and LPF selections.

The high-pass filter options include a 1st-order IIR Butterworth filter with a 0.4Hz corner frequency along with a pass through setting for DC coupling. Low-

pass filter options include a 12-tap linear phase (constant group delay) FIR filter with 40Hz, 100Hz, or 150Hz corner frequencies. See register CNFG\_ECG (0x15) to configure the filters. Table 4 illustrates the ECG latency in samples and time for each ADC data rate.

# Table 4. ECG Latency in Samples and Time as a Function of ECG Data Rate and Decimation

| ECG                          | CHANNEL SETTIN        | NGS | LATENCY                           |                                |                     |                  |  |

|------------------------------|-----------------------|-----|-----------------------------------|--------------------------------|---------------------|------------------|--|

| INPUT<br>SAMPLE RATE<br>(Hz) | SAMPLE RATE DATA RATE |     | WITHOUT<br>LFP (INPUT<br>SAMPLES) | WITH LPF<br>(INPUT<br>SAMPLES) | WITHOUT<br>LFP (ms) | WITH LPF<br>(ms) |  |

| 32,768                       | 512                   | 64  | 650                               | 1,034                          | 19.836              | 31.555           |  |

| 32,000                       | 500                   | 64  | 650                               | 1,034                          | 20.313              | 32.313           |  |

| 32,768                       | 256                   | 128 | 2,922                             | 3,690                          | 89.172              | 112.610          |  |

| 32,000                       | 250                   | 128 | 2,922                             | 3,690                          | 91.313              | 115.313          |  |

| 32,000                       | 200                   | 160 | 1,242                             | 2,202                          | 38.813              | 68.813           |  |

| 31,968                       | 199.8                 | 160 | 1,242                             | 2,202                          | 38.851              | 68.881           |  |

| 32,768                       | 128                   | 256 | 3,370                             | 4,906                          | 102.844             | 149.719          |  |

| 32,000                       | 125                   | 256 | 3,370                             | 4,906                          | 105.313             | 153.313          |  |

# Ultra-Low Power, Single-Channel Integrated Biopotential (ECG, R-to-R Detection) AFE

#### **Noise Measurements**

Table 5 shows the noise performance of the ECG channel of MAX30003 referred to the ECG inputs.

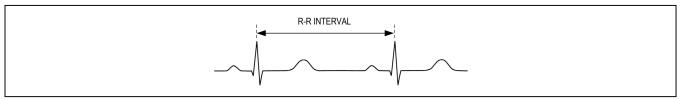

#### **R-to-R Detection**