Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

The MAX1303 multirange, low-power, 16-bit, successive-approximation, analog-to-digital converter (ADC) operates from a single +5V supply and achieves throughput rates up to 115ksps. A separate digital supply allows digital interfacing with 2.7V to 5.25V systems using the SPI-/QSPITM-/MICROWIRE®-compatible serial interface. Partial power-down mode reduces the supply current to 1.3mA (typ). Full power-down mode reduces the power-supply current to 1µA (typ).

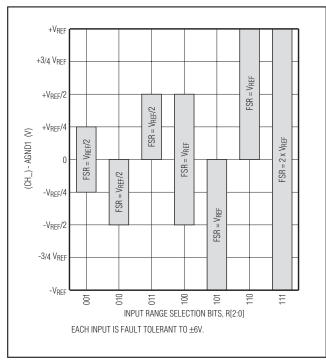

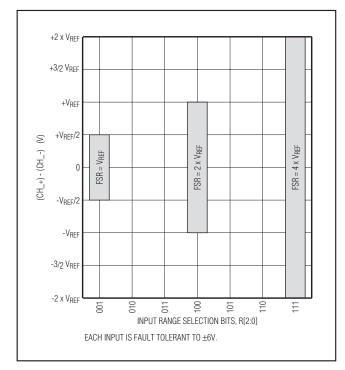

The MAX1303 provides four (single-ended) or two (true differential) analog input channels. Each analog input channel is independently software programmable for seven single-ended input ranges (0V to +VREF/2, -VREF/2 to OV, OV to +VREF, -VREF to OV, ±VREF/4, ±V<sub>RFF</sub>/2, and ±V<sub>RFF</sub>), and three differential input ranges (±VREF/2, ±VREF, ±2 x VREF).

An on-chip +4.096V reference offers a small convenient ADC solution. The MAX1303 also accepts an external reference voltage between 3.800V and 4.136V.

The MAX1303 is available in a 20-pin TSSOP package, and is specified for operation from -40°C to +85°C.

### **Applications**

Industrial Control Systems **Data-Acquisition Systems Avionics** Robotics

### Features

- ♦ Software-Programmable Input Range for Each Channel

- **♦** Single-Ended Input Ranges 0V to +VREF/2, -VREF/2 to 0V, 0V to +VREF, -VREF to 0V, ±VREF/4, ±VREF/2, and ±VREF

- **♦ Differential Input Ranges** ±VREF/2, ±VREF, and ±2 x VREF

- ♦ Four Single-Ended or Two Differential Analog

- **♦** ±6V Overvoltage Tolerant Inputs

- ♦ Internal or External Reference

- ♦ 115ksps Maximum Sample Rate

- ♦ Single +5V Power Supply

- ◆ 20-Pin TSSOP Package

### **Ordering Information**

| PART         | PIN-PACKAGE | CHANNELS |

|--------------|-------------|----------|

| MAX1303AEUG+ | 20 TSSOP    | 4        |

| MAX1303BEUG+ | 20 TSSOP    | 4        |

Note: All devices are specified over the -40°C to +85°C operating temperature range.

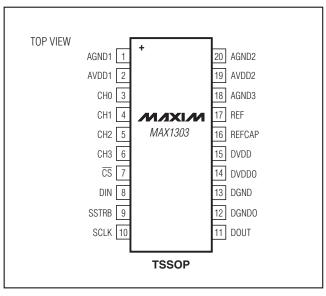

## **Pin Configuration**

QSPI is a trademark of Motorola. Inc. MICROWIRE is a registered trademark of National Semiconductor Corp.

MIXIM

Maxim Integrated Products 1

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **ABSOLUTE MAXIMUM RATINGS**

| AVDD1 to AGND1                   | 0.3V to +6V      | CH0-CH7 to AGND1                        | 6V to +6V                         |

|----------------------------------|------------------|-----------------------------------------|-----------------------------------|

| AVDD2 to AGND2                   | 0.3V to +6V      | REF, REFCAP to AGND1                    | 0.3V  to  (VAVDD1 + 0.3V)         |

| DVDD to DGND                     | 0.3V to +6V      | Continuous Current (any pin)            | ±50mA                             |

| DVDDO to DGNDO                   | 0.3V to +6V      | Continuous Power Dissipation (Multilaye | er board, T <sub>A</sub> = +70°C) |

| DVDD to DVDDO                    | 0.3V to +6V      | 20-Pin TSSOP (derate 13.6mW/°C ab       | ove +70°C)1084mW                  |

| DVDD, DVDDO to AVDD1             | 0.3V to +6V      | Operating Temperature Range             | 40°C to +85°C                     |

| AVDD1, DVDD, DVDDO to AVDD2      | 0.3V to +6V      | Junction Temperature                    | +150°C                            |

| DGND, DGNDO, AGND3, AGND2 to AGN | ND10.3V to +0.3V | Storage Temperature Range               |                                   |

| CS, SCLK, DIN, DOUT, SSTRB to    |                  | Lead Temperature (soldering, 10s)       | +300°C                            |

| DGNDO0.3\                        |                  | Soldering Temperature (reflow)          | +260°C                            |

|                                  |                  |                                         |                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(VAVDD1 = VAVDD2 = VDVDD = VDVDD0 = 5V, VAGND1 = VVDGND = VDGND0 = VAGND2 = VAGND3 = 0V, fclk = 3.5MHz (50% duty cycle), external clock mode, VREF = 4.096V (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range (<math>\pm VREF$ ), CDOUT = 50pF, CSSTRB = 50pF, TA = -40°C to  $\pm VREF$ 0, unless otherwise noted. Typical values are at TA =  $\pm VREF$ 1.

| PARAMETER                                   | SYMBOL       | CONDITIONS                                 |                                 | MIN        | TYP   | MAX  | UNITS              |

|---------------------------------------------|--------------|--------------------------------------------|---------------------------------|------------|-------|------|--------------------|

| DC ACCURACY (Notes 1, 2)                    |              |                                            |                                 |            |       |      |                    |

| Resolution                                  |              |                                            |                                 | 16         |       |      | Bits               |

| Integral Naplinearity                       | INL          | MAX1303A                                   | MAX1303A                        |            | ±1.0  | ±2   | LSB                |

| Integral Nonlinearity                       | IINL         | MAX1303B                                   |                                 |            | ±1.0  | ±4   | LOD                |

| Differential Nonlinearity                   | DNL          | No missing codes                           |                                 | -1         |       | +2   | LSB                |

| Transition Noise                            |              | External or internal re-                   | ference                         |            | 1     |      | LSB <sub>RMS</sub> |

|                                             |              | Single-ended inputs                        | Unipolar                        |            | 0     | ±10  |                    |

| Offset Error                                |              | Single-ended inputs                        | Bipolar                         |            | -1.0  | ±10  | mV                 |

| Oliset Elloi                                |              | Differential inputs                        | Unipolar                        |            | 0     | ±20  | IIIV               |

|                                             |              | (Note 3)                                   | Bipolar                         |            | -2.0  | ±20  |                    |

| Channel-to-Channel Gain<br>Matching         |              | Unipolar or bipolar                        |                                 |            | 0.025 |      | %FSR               |

| Channel-to-Channel Offset Error<br>Matching |              | Unipolar or bipolar                        |                                 |            | 1.0   |      | mV                 |

| 0" 17                                       |              | Unipolar                                   |                                 |            | 10    |      | 10.0               |

| Offset Temperature Coefficient              |              | Bipolar                                    |                                 |            | 5     |      | ppm/°C             |

| Coin France                                 |              | Unipolar                                   |                                 |            |       | ±0.5 | 0/ FCD             |

| Gain Error                                  |              | Bipolar                                    |                                 |            |       | ±0.3 | %FSR               |

| Cain Temperature Coefficient                |              | Unipolar                                   |                                 |            | 1.5   |      | nnm/0C             |

| Gain Temperature Coefficient                |              | Bipolar                                    |                                 |            | 1.0   |      | ppm/°C             |

| Unipolar Endpoint Overlap                   |              | Negative unipolar full unipolar zero-scale | scale to positive               | 0          | 20    |      | LSB                |

| DYNAMIC SPECIFICATIONS fin(                 | SINE-WAVE) = | 5kHz, V <sub>IN</sub> = FSR - 0.0          | 5dB, f <sub>SAMPLE</sub> = 130k | sps (Notes | 1, 2) |      |                    |

|                                             |              | Differential inputs, FS                    | R = 2 x V <sub>REF</sub>        |            | 90    |      |                    |

| Cienal to Naisa Plus Dieta tia              | CINIAD       | Single-ended inputs,                       |                                 | 88         |       | -10  |                    |

| Signal-to-Noise Plus Distortion             | SINAD        |                                            |                                 | 85         |       | dB   |                    |

|                                             |              | Single-ended inputs,                       | FSR = V <sub>REF</sub> /4       | 80         | 82    |      |                    |

2 /**U**/**IXI/U**I

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDDO} = 5V$ ,  $V_{AGND1} = V_{VDGND} = V_{DGNDO} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5$ MHz (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50$ pF,  $C_{SSTRB} = 50$ pF,  $T_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.)

| PARAMETER                                              | SYMBOL            | CONDITIONS                                                        | MIN                  | TYP | MAX                  | UNITS |

|--------------------------------------------------------|-------------------|-------------------------------------------------------------------|----------------------|-----|----------------------|-------|

|                                                        |                   | Differential inputs, FSR = 2 x V <sub>REF</sub>                   |                      | 90  |                      |       |

| Cional ta Naisa Datia                                  | SNR               | Single-ended inputs, FSR = V <sub>REF</sub>                       |                      | 88  |                      | dB    |

| Signal-to-Noise Ratio                                  | SINK              | Single-ended inputs, FSR = V <sub>REF</sub> /2                    |                      | 85  |                      | aв    |

|                                                        |                   | Single-ended inputs, FSR = V <sub>REF</sub> /4                    |                      | 82  |                      |       |

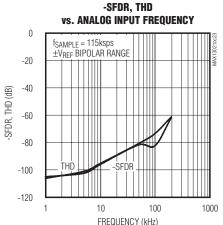

| Total Harmonic Distortion (Up to the 5th Harmonic)     | THD               |                                                                   |                      | -98 |                      | dB    |

| Spurious-Free Dynamic Range                            | SFDR              |                                                                   | 92                   | 99  |                      | dB    |

| Aperture Delay                                         | t <sub>AD</sub>   | Figure 19                                                         |                      | 15  |                      | ns    |

| Aperture Jitter                                        | taj               | Figure 19                                                         |                      | 100 |                      | ps    |

| Channel-to-Channel Isolation                           |                   |                                                                   |                      | 105 |                      | dB    |

| CONVERSION RATE                                        |                   |                                                                   |                      |     |                      |       |

|                                                        |                   | External clock mode, Figure 1                                     |                      |     | 114                  |       |

| Byte-Wide Throughput Rate                              | fSAMPLE           | External acquisition mode, Figure 2                               |                      | 84  |                      |       |

|                                                        |                   | Internal clock mode, Figure 3                                     |                      |     | 106                  |       |

| ANALOG INPUTS (CH0-CH3, AG                             | ND1)              |                                                                   |                      |     |                      |       |

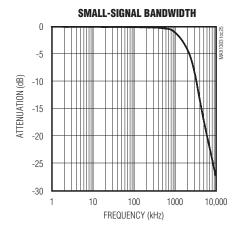

| Small-Signal Bandwidth                                 |                   | All input ranges, V <sub>IN</sub> = 100mV <sub>P-P</sub> (Note 2) |                      | 1.5 |                      | MHz   |

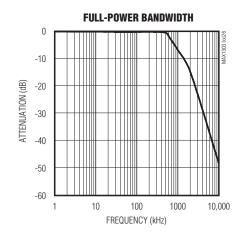

| Full-Power Bandwidth                                   |                   | All input ranges, V <sub>IN</sub> = 4V <sub>P-P</sub> (Note 2)    |                      | 700 |                      | kHz   |

|                                                        |                   | R[2:1] = 001                                                      | -V <sub>REF</sub> /4 |     | +V <sub>REF</sub> /4 |       |

|                                                        |                   | R[2:1] = 010                                                      | -V <sub>REF</sub> /2 |     | 0                    |       |

|                                                        |                   | R[2:1] = 011                                                      | 0                    |     | +V <sub>REF</sub> /2 |       |

| Input Voltage Range (Table 6)                          | V <sub>CH</sub> _ | R[2:1] = 100                                                      | -V <sub>REF</sub> /2 |     | +V <sub>REF</sub> /2 | V     |

|                                                        |                   | R[2:1] = 101                                                      | -VREF                |     | 0                    |       |

|                                                        |                   | R[2:1] = 110                                                      | 0                    |     | +V <sub>REF</sub>    |       |

|                                                        |                   | R[2:1] = 111                                                      | -VREF                |     | +V <sub>REF</sub>    |       |

| True-Differential Analog Common-<br>Mode Voltage Range | VCMDR             | DIF/SGL = 1 (Note 4)                                              | -4.75                |     | +5.50                | V     |

| Common-Mode Rejection Ratio                            | CMRR              | $DIF/\overline{SGL} = 1$ , input voltage range = $\pm V_{REF}/4$  |                      | 75  |                      | dB    |

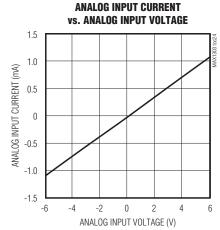

| Input Current                                          | ICH_              | -VREF < VCH_ < +VREF                                              | -1500                |     | +650                 | μΑ    |

| Input Capacitance                                      | C <sub>CH</sub> _ |                                                                   |                      | 5   |                      | рF    |

| Input Resistance                                       | R <sub>CH</sub> _ |                                                                   |                      | 6   |                      | kΩ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDD0} = 5V$ ,  $V_{AGND1} = V_{VDGND} = V_{DGND0} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5$ MHz (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50$ pF,  $C_{SSTRB} = 50$ pF,  $C_{AB} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $C_{AB} = -40$ °C.)

| PARAMETER                            | SYMBOL            | CONDITIONS                                                                                                                  | MIN                         | TYP   | MAX                         | UNITS  |

|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|-----------------------------|--------|

| INTERNAL REFERENCE (Bypass           | REFCAP w          | ith 0.1μF to AGND1 and REF with 1.0μF to                                                                                    | AGND1)                      |       |                             |        |

| Reference Output Voltage             | V <sub>REF</sub>  |                                                                                                                             | 4.056                       | 4.096 | 4.136                       | V      |

| Reference Temperature<br>Coefficient | TC <sub>REF</sub> |                                                                                                                             |                             | ±30   |                             | ppm/°C |

| Reference Short-Circuit Current      | 1                 | REF shorted to AGND1                                                                                                        |                             | 10    |                             | νος Λ  |

| Reference Short-Circuit Current      | IREFSC            | REF shorted to AVDD                                                                                                         |                             | -1    |                             | mA     |

| Reference Load Regulation            |                   | I <sub>REF</sub> = 0 to 0.5mA                                                                                               |                             | 0.1   | 10                          | mV     |

| EXTERNAL REFERENCE (REFCA            | AP = AVDD)        |                                                                                                                             |                             |       |                             |        |

| Reference Input Voltage Range        | V <sub>REF</sub>  |                                                                                                                             | 3.800                       |       | 4.136                       | V      |

| REFCAP Buffer Disable<br>Threshold   | VRCTH             | (Note 5)                                                                                                                    | V <sub>AVDD1</sub><br>- 0.4 |       | V <sub>AVDD1</sub><br>- 0.1 | V      |

| Reference Input Current              | I <sub>REF</sub>  | V <sub>REF</sub> = +4.096V, external clock mode, external acquisition mode, internal clock mode, or partial power-down mode |                             | 90    | 200                         | μΑ     |

|                                      |                   | V <sub>REF</sub> = +4.096V, full power-down mode                                                                            |                             | ±0.1  | ±10                         |        |

| Reference Input Resistance           | R <sub>REF</sub>  | External clock mode, external acquisition mode, internal clock mode, or partial power-down mode                             | 20                          | 45    |                             | kΩ     |

|                                      |                   | Full power-down mode                                                                                                        |                             | 40    |                             | MΩ     |

| DIGITAL INPUTS (DIN, SCLK, CS        | 5)                |                                                                                                                             | ·                           |       |                             |        |

| Input High Voltage                   | VIH               |                                                                                                                             | 0.7 x<br>VDVDDO             |       |                             | V      |

| Input Low Voltage                    | V <sub>IL</sub>   |                                                                                                                             |                             |       | 0.3 x<br>V <sub>DVDDO</sub> | ٧      |

| Input Hysteresis                     | V <sub>HYST</sub> |                                                                                                                             |                             | 0.2   |                             | V      |

| Input Leakage Current                | I <sub>IN</sub>   | V <sub>IN</sub> = 0 to V <sub>DVDDO</sub>                                                                                   | -10                         |       | +10                         | μΑ     |

| Input Capacitance                    | C <sub>IN</sub>   |                                                                                                                             |                             | 10    |                             | рF     |

| DIGITAL OUTPUTS (DOUT, SSTE          | RB)               |                                                                                                                             |                             |       |                             |        |

| Output Low Voltage                   | 1/0               | V <sub>DVDDO</sub> = 4.75V, I <sub>SINK</sub> = 10mA                                                                        |                             |       | 0.4                         | V      |

| Output Low Voltage                   | V <sub>OL</sub>   | V <sub>DVDDO</sub> = 2.7V, I <sub>SINK</sub> = 5mA                                                                          |                             |       | 0.4                         | V      |

| Output High Voltage                  | Voн               | ISOURCE = 0.5mA                                                                                                             | V <sub>DVDDO</sub> - 0.4    |       |                             | V      |

| DOUT Tri-State Leakage Current       | IDDO              | CS = DVDDO                                                                                                                  | -10                         |       | +10                         | μΑ     |

| POWER REQUIREMENTS (AVDD             | 1 and AGND        | 1, AVDD2 and AGND2, DVDD and DGND, D                                                                                        | VDDO and                    | DGNDC | ))                          |        |

| Analog Supply Voltage                | AVDD1             |                                                                                                                             | 4.75                        |       | 5.25                        | V      |

| Digital Supply Voltage               | DVDD              |                                                                                                                             | 4.75                        |       | 5.25                        | V      |

4 \_\_\_\_\_\_*NIXI/*H

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDD0} = 5V$ ,  $V_{AGND1} = V_{VDGND} = V_{DGND0} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5$ MHz (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50$ pF,  $C_{SSTRB} = 50$ pF,  $C_{AB} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{AB} = +25$ °C.)

| PARAMETER                      | SYMBOL             | COND                                            | MIN                     | TYP  | MAX  | UNITS |      |

|--------------------------------|--------------------|-------------------------------------------------|-------------------------|------|------|-------|------|

| Preamplifier Supply Voltage    | AVDD2              |                                                 |                         | 4.75 |      | 5.25  | V    |

| Digital I/O Supply Voltage     | DVDDO              |                                                 | _                       | 2.70 |      | 5.25  | V    |

| AVDD1 Supply Current           | lavdd1             | External clock mode, external acquisition       | Internal reference      |      | 3    | 3.5   | mA   |

| AVDD I Supply Culterit         | IAVDDT             | mode, or internal clock mode External reference |                         |      | 2.5  | 3     | IIIA |

| DVDD Supply Current            | IDVDD              | External clock mode, mode, or internal cloc     | ·                       |      | 0.9  | 2     | mA   |

| AVDD2 Supply Current           | I <sub>AVDD2</sub> | External clock mode, mode, or internal cloc     | '                       |      | 17.5 | 25    | mA   |

| DVDDO Supply Current           | IDVDDO             | External clock mode, mode, or internal cloc     | !                       |      | 0.2  | 1     | mA   |

| Total Complex Comment          |                    | Partial power-down m                            | Partial power-down mode |      |      |       | mA   |

| Total Supply Current           |                    | Full power-down mod                             | Full power-down mode    |      |      |       | μΑ   |

| Power-Supply Rejection Ratio   | PSRR               | All analog input range                          | All analog input ranges |      |      |       | LSB  |

| TIMING CHARACTERISTICS (Fig    | jures 14 and       | 15)                                             |                         |      |      |       | _    |

|                                |                    | External clock mode                             |                         | 272  |      | 62    |      |

| SCLK Period                    | tcp                | External acquisition m                          | node                    | 228  |      | 62    | μs   |

|                                |                    | Internal clock mode                             |                         | 100  |      | 83    |      |

|                                |                    | External clock mode                             |                         | 109  |      |       |      |

| SCLK High Pulse Width (Note 6) | tcH                | External acquisition m                          | 92                      |      |      | ns    |      |

|                                |                    | Internal clock mode                             |                         | 40   |      |       |      |

|                                |                    | External clock mode                             |                         | 109  |      |       |      |

| SCLK Low Pulse Width (Note 6)  | tcL                | External acquisition m                          | node                    | 92   |      |       | ns   |

|                                |                    | Internal clock mode                             |                         | 40   |      |       |      |

| DIN to SCLK Setup              | t <sub>DS</sub>    |                                                 |                         | 40   |      |       | ns   |

| DIN to SCLK Hold               | tDH                |                                                 |                         |      |      |       | ns   |

| SCLK Fall to DOUT Valid        | t <sub>DO</sub>    |                                                 |                         |      |      | 40    | ns   |

| CS Fall to DOUT Enable         | t <sub>DV</sub>    |                                                 |                         |      |      | 40    | ns   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDD0} = 5V$ ,  $V_{AGND1} = V_{VDGND} = V_{DGND0} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5$ MHz (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50$ pF,  $C_{SSTRB} = 50$ pF,  $T_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.)

| PARAMETER                   | SYMBOL | CONDITIONS            | MIN | TYP | MAX | UNITS |

|-----------------------------|--------|-----------------------|-----|-----|-----|-------|

| CS Rise to DOUT Disable     | tTR    |                       |     |     | 40  | ns    |

| CS Fall to SCLK Rise Setup  | tcss   |                       | 40  |     |     | ns    |

| CS High Minimum Pulse Width | tcspw  |                       | 40  |     |     | ns    |

| SCLK Fall to CS Rise Hold   | tcsh   |                       | 0   |     |     | ns    |

| SSTRB Rise to CS Fall Setup |        | (Note 4)              | 40  |     |     | ns    |

| DOUT Rise/Fall Time         |        | $C_L = 50pF$          |     | 10  |     | ns    |

| SSTRB Rise/Fall Time        |        | C <sub>L</sub> = 50pF |     | 10  |     | ns    |

- **Note 1:** Parameter tested at V<sub>AVDD1</sub> = V<sub>AVDD2</sub> = V<sub>DVDD</sub> = V<sub>DVDD0</sub> = 5V.

- Note 2: See definitions in the Parameter Definitions section at the end of the data sheet.

- Note 3: Guaranteed by correlation with single-ended measurements.

- Note 4: Not production tested. Guaranteed by design.

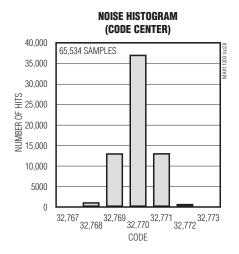

- Note 5: To ensure external reference operation, V<sub>REFCAP</sub> must exceed (V<sub>AVDD1</sub> 0.1V). To ensure internal reference operation, V<sub>REFCAP</sub> must be below (V<sub>AVDD1</sub> 0.4V). Bypassing REFCAP with a 0.1µF or larger capacitor to AGND1 sets V<sub>REFCAP</sub> ≈ 4.096V. The transition point between internal reference mode and external reference mode lies between the REFCAP buffer disable threshold minimum and maximum values (Figures 16 and 17).

- Note 6: The SCLK duty cycle can vary between 40% and 60%, as long as the t<sub>CL</sub> and t<sub>CH</sub> timing requirements are met.

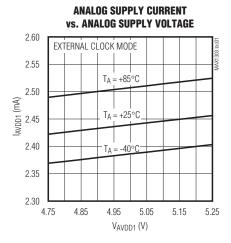

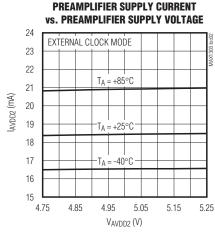

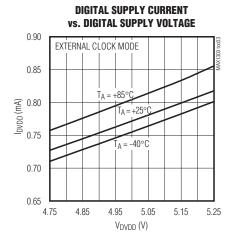

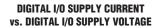

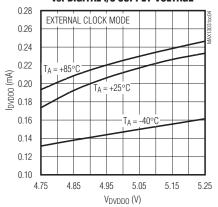

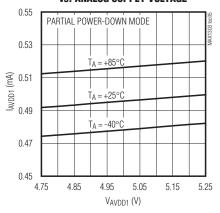

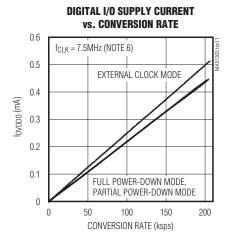

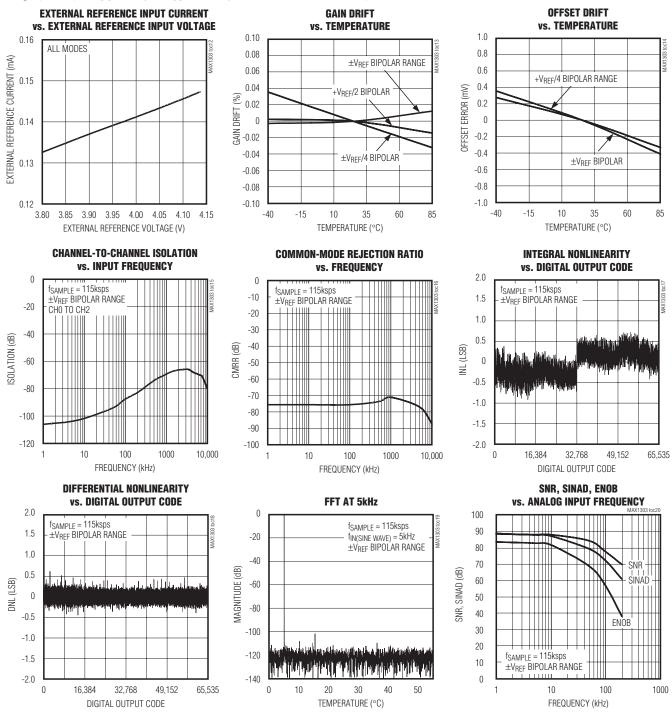

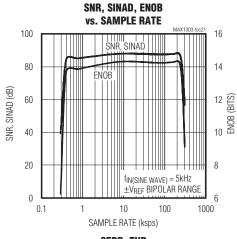

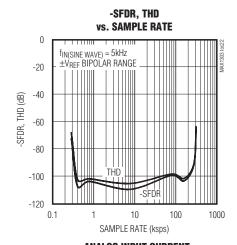

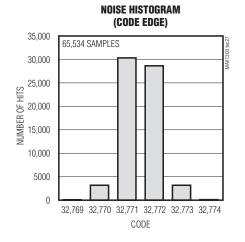

## Typical Operating Characteristics

(VAVDD1 = VAVDD2 = VDVDD = VDVDD0 = 5V, VAGND1 = VDGND = VDGND0 = VAGND2 = VAGND3 = 0V, fCLK = 3.5MHz (50% duty cycle), external clock mode, VREF = 4.096V (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range (±VREF), CDOUT = 50pF, CSSTRB = 50pF; unless otherwise noted.)

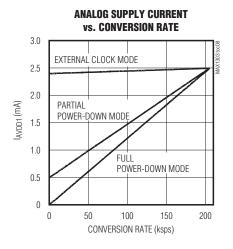

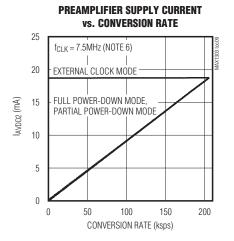

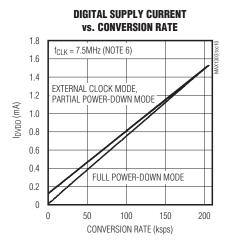

## Typical Operating Characteristics (continued)

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDD0} = 5V$ ,  $V_{AGND1} = V_{DGND} = V_{DGND0} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5MHz$  (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50pF$ ,  $C_{SSTRB} = 50pF$ ; unless otherwise noted.)

# ANALOG SUPPLY CURRENT vs. Analog Supply Voltage

# PREAMPLIFIER SUPPLY CURRENT vs. PREAMPLIFIER SUPPLY VOLTAGE

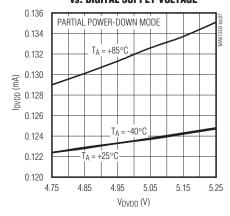

## DIGITAL SUPPLY CURRENT vs. DIGITAL SUPPLY VOLTAGE

### Typical Operating Characteristics (continued)

(VAVDD1 = VAVDD2 = VDVDD = VDVDD0 = 5V, VAGND1 = VDGND = VDGND0 = VAGND2 = VAGND3 = 0V, fCLK = 3.5MHz (50% duty cycle), external clock mode, VREF = 4.096V (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range (±VREF), CDOUT = 50pF, CSSTRB = 50pF; unless otherwise noted.)

**Note 6:** For partial power-down and full power-down modes, external clock mode was used for a burst of continuous samples. Partial power-down or full power-down modes were entered thereafter. By using this method, the conversion rate was found by averaging the number of conversions over the time starting from the first conversion to the end of the partial power-down or full power-down modes.

## **Typical Operating Characteristics (continued)**

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDD0} = 5V$ ,  $V_{AGND1} = V_{DGND} = V_{DGND0} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5$ MHz (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50$ pF,  $C_{SSTRB} = 50$ pF; unless otherwise noted.)

## Typical Operating Characteristics (continued)

(VAVDD1 = VAVDD2 = VDVDD = VDVDD0 = 5V, VAGND1 = VDGND = VDGND0 = VAGND2 = VAGND3 = 0V, fCLK = 3.5MHz (50% duty cycle), external clock mode, VREF = 4.096V (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range (±VREF), CDOUT = 50pF, CSSTRB = 50pF; unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{AVDD1} = V_{AVDD2} = V_{DVDD} = V_{DVDD0} = 5V$ ,  $V_{AGND1} = V_{DGND} = V_{DGND0} = V_{AGND2} = V_{AGND3} = 0V$ ,  $f_{CLK} = 3.5$ MHz (50% duty cycle), external clock mode,  $V_{REF} = 4.096V$  (external reference operation), REFCAP = AVDD1, maximum single-ended bipolar input range ( $\pm V_{REF}$ ),  $C_{DOUT} = 50$ pF,  $C_{SSTRB} = 50$ pF; unless otherwise noted.)

## **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AGND1  | Analog Ground 1. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.                                                                                                                                                                                                                                                 |

| 2   | AVDD1  | Analog Supply Voltage 1. Connect AVDD1 to a +4.75V to +5.25V power-supply voltage. Bypass AVDD1 to AGND1 with a 0.1µF capacitor.                                                                                                                                                                                                  |

| 3   | CH0    | Analog Input Channel 0                                                                                                                                                                                                                                                                                                            |

| 4   | CH1    | Analog Input Channel 1                                                                                                                                                                                                                                                                                                            |

| 5   | CH2    | Analog Input Channel 2                                                                                                                                                                                                                                                                                                            |

| 6   | CH3    | Analog Input Channel 3                                                                                                                                                                                                                                                                                                            |

| 7   | CS     | Active-Low Chip-Select Input. When $\overline{CS}$ is low, data is clocked into the device from DIN on the rising edge of SCLK. With $\overline{CS}$ low, data is clocked out of DOUT on the falling edge of SCLK. When $\overline{CS}$ is high, activity on SCLK and DIN is ignored and DOUT is high impedance.                  |

| 8   | DIN    | Serial Data Input. When $\overline{\text{CS}}$ is low, data is clocked in on the rising edge of SCLK. When $\overline{\text{CS}}$ is high, transitions on DIN are ignored.                                                                                                                                                        |

| 9   | SSTRB  | Serial-Strobe Output. When using the internal clock, SSTRB rising edge transitions indicate that data is ready to be read from the device. When operating in external clock mode, SSTRB is always low. SSTRB does not tri-state, regardless of the state of $\overline{\text{CS}}$ , and therefore requires a dedicated I/O line. |

| 10  | SCLK   | Serial Clock Input. When $\overline{\text{CS}}$ is low, transitions on SCLK clock data into DIN and out of DOUT. When $\overline{\text{CS}}$ is high, transitions on SCLK are ignored.                                                                                                                                            |

| 11  | DOUT   | Serial Data Output. When $\overline{\text{CS}}$ is low, data is clocked out of DOUT with each falling SCLK transition. When $\overline{\text{CS}}$ is high, DOUT is high impedance.                                                                                                                                               |

| 12  | DGNDO  | Digital I/O Ground. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.                                                                                                                                                                                                                                              |

| 13  | DGND   | Digital Ground. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.                                                                                                                                                                                                                                                  |

| 14  | DVDDO  | Digital I/O Supply Voltage Input. Connect DVDDO to a +2.7V to +5.25V power-supply voltage. Bypass DVDDO to DGNDO with a 0.1µF capacitor.                                                                                                                                                                                          |

| 15  | DVDD   | Digital-Supply Voltage Input. Connect DVDD to a +4.75V to +5.25V power-supply voltage. Bypass DVDD to DGND with a 0.1µF capacitor.                                                                                                                                                                                                |

| 16  | REFCAP | Bandgap-Voltage Bypass Node. For external reference operation, connect REFCAP to AVDD. For internal reference operation, bypass REFCAP with a 0.01µF capacitor to AGND1 (VREFCAP ≈ 4.096V).                                                                                                                                       |

| 17  | REF    | Reference-Buffer Output/ADC Reference Input. For external reference operation, apply an external reference voltage from 3.800V to 4.136V to REF. For internal reference operation, bypassing REF with a $1\mu\text{F}$ capacitor to AGND1 sets $V_{\text{REF}} = 4.096V \pm 1\%$ .                                                |

| 18  | AGND3  | Analog Signal Ground 3. AGND3 is the ADC negative reference potential. Connect AGND3 to AGND1. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.                                                                                                                                                                   |

| 19  | AVDD2  | Analog Supply Voltage 2. Connect AVDD2 to a +4.75V to +5.25V power-supply voltage. Bypass AVDD2 to AGND2 with a 0.1µF capacitor.                                                                                                                                                                                                  |

| 20  | AGND2  | Analog Ground 2. This ground carries approximately five times more current than AGND1. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.                                                                                                                                                                           |

### **Detailed Description**

The MAX1303 multirange, low-power, 16-bit successive-approximation ADC operates from a single +5V supply and has a separate digital supply allowing digital interface with 2.7V to 5.25V systems. This 16-bit ADC has internal track-and-hold (T/H) circuitry that supports single-ended and fully differential inputs. For single-ended conversions, the valid analog input voltage range spans from -VREF below ground to +VREF above ground. The maximum allowable differential input voltage spans from -2 x VREF to +2 x VREF. Data can be converted in a variety of software-programmable channel and data-acquisition configurations. Microprocessor ( $\mu P$ ) control is made easy through an SPI-/QSPI-/MICROWIRE-compatible serial interface.

The MAX1303 has four single-ended analog input channels or two differential channels. Each analog input channel is independently software programmable for seven single-ended input ranges (0V to +VREF/2, -VREF/2 to 0V, 0V to +VREF, -VREF to 0V,  $\pm$ VREF/4,  $\pm$ VREF/2, and  $\pm$ VREF) and three differential input ranges ( $\pm$ VREF/2,  $\pm$ VREF, and  $\pm$ 2 x VREF). Additionally, all analog input channels are fault tolerant to  $\pm$ 6V. A fault condition on an idle channel does not affect the conversion result of other channels.

### **Power Supplies**

To maintain a low-noise environment, the MAX1303 provides separate power supplies for each section of circuitry. Table 1 shows the four separate power supplies. Achieve optimal performance using separate AVDD1, AVDD2, DVDD, and DVDDO supplies. Alternatively, connect AVDD1, AVDD2, and DVDD together as close to the device as possible for a convenient power connection. Connect AGND1, AGND2, AGND3, DGND, and DGNDO together as close as possible to the device. Bypass each supply to the corresponding ground using a 0.1µF capacitor (Table 1). If significant low-frequency noise is present, add a 10µF capacitor in parallel with the 0.1µF bypass capacitor.

### **Converter Operation**

The MAX1303 ADC features a fully differential, successive-approximation register (SAR) conversion technique and an on-chip T/H block to convert voltage signals into a 16-bit digital result. Both single-ended and differential configurations are supported with programmable unipolar and bipolar signal ranges.

Table 1. MAX1303 Power Supplies and Bypassing

|                        | • •                         |                                |                                  |                |

|------------------------|-----------------------------|--------------------------------|----------------------------------|----------------|

| POWER<br>SUPPLY/GROUND | SUPPLY VOLTAGE<br>RANGE (V) | TYPICAL SUPPLY<br>CURRENT (mA) | CIRCUIT SECTION                  | BYPASSING      |

| DVDDO/DGNDO            | 2.7 to 5.25                 | 0.2                            | Digital I/O                      | 0.1µF to DGNDO |

| AVDD2/AGND2            | 4.75 to 5.25                | 17.5                           | Analog Circuitry                 | 0.1µF to AGND2 |

| AVDD1/AGND1            | 4.75 to 5.25                | 3.0                            | Analog Circuitry                 | 0.1µF to AGND1 |

| DVDD/DGND              | 4.75 to 5.25                | 0.9                            | Digital Control Logic and Memory | 0.1µF to DGND  |

**Table 2. Analog Input Configuration Byte**

| BIT<br>NUMBER | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | START   | Start Bit. The first logic 1 after $\overline{\text{CS}}$ goes low defines the beginning of the analog input configuration byte.                                                                                                                                                                                                                                                                                                                                                                     |

| 6             | C2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5             | C1      | Channel-Select Bits. SEL[2:0] select the analog input channel to be configured (Tables 4 and 5).                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4             | C0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3             | DIF/SGL | Differential or Single-Ended Configuration Bit. DIF/SGL = 0 configures the selected analog input channel for single-ended operation. DIF/SGL = 1 configures the channel for differential operation. In single-ended mode, input voltages are measured between the selected input channel and AGND1, as shown in Table 4. In differential mode, the input voltages are measured between two input channels, as shown in Table 5. Be aware that changing DIF/SGL adjusts the FSR, as shown in Table 6. |

| 2             | R2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1             | R1      | Input-Range-Select Bits. R[2:0] select the input voltage range, as shown in Table 6 and Figure 6.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0             | R0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### **Track-and-Hold Circuitry**

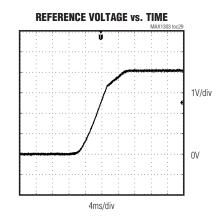

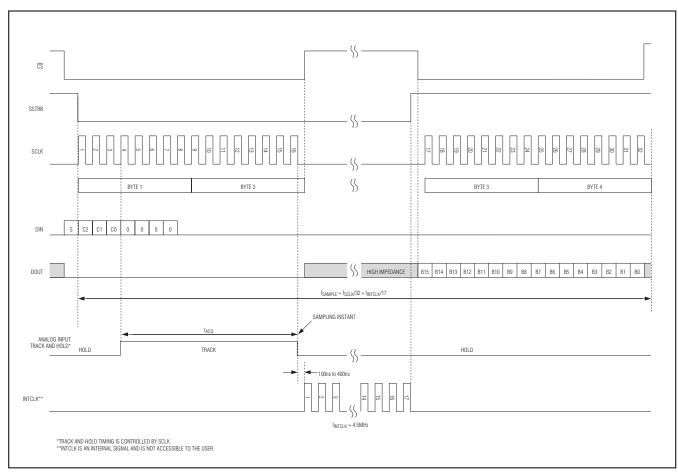

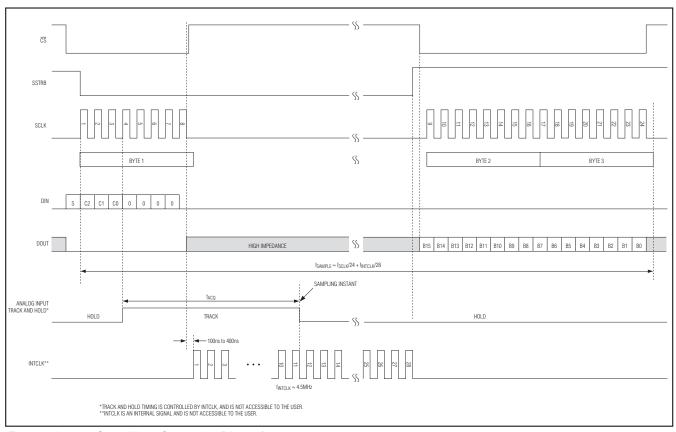

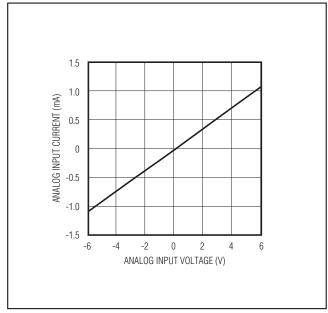

The MAX1303 features a switched-capacitor T/H architecture that allows the analog input signal to be stored as charge on sampling capacitors. See Figures 1, 2, and 3 for T/H timing and the sampling instants for each operating mode. The MAX1303 analog input circuitry buffers the input signal from the sampling capacitors, resulting in a constant analog input impedance with varying input voltage (Figure 4).

### **Analog Input Circuitry**

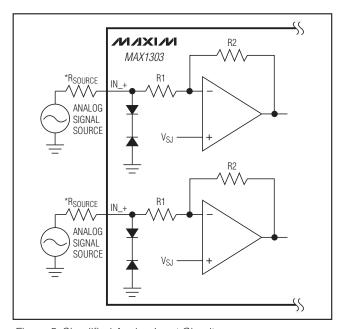

Select differential or single-ended conversions using the associated analog input configuration byte (Table 2). The analog input signal source must be capable of driving the ADC's  $6k\Omega$  input resistance (Figure 5).

Figure 5 shows the simplified analog input circuit. The analog inputs are ±6V fault tolerant and are protected by back-to-back diodes. The summing junction voltage,

V<sub>SJ</sub>, is a function of the channel's input common-mode voltage:

$$V_{SJ} = \left(\frac{R1}{R1 + R2}\right) \times 2.375V + \left(1 + \left(\frac{R1}{R1 + R2}\right)\right) \times V_{CM}$$

As a result, the analog input impedance is relatively constant over the input voltage as shown in Figure 4.

Single-ended conversions are internally referenced to AGND1 (Tables 3 and 4). In differential mode, IN+ and IN- are selected according to Tables 3 and 5. When configuring differential channels, the differential pair follows the analog configuration byte for the positive channel. For example, to configure CH2 and CH3 for a  $\pm V_{REF}$  differential conversion, set the CH2 analog configuration byte for a differential conversion with the  $\pm V_{REF}$  range (1010 1100). To initiate a conversion for the CH2 and CH3 differential pair, issue the command 1010 0000.

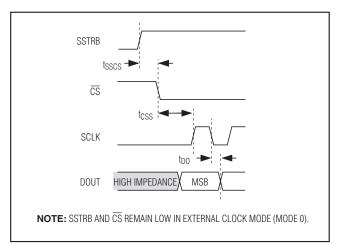

Figure 1. External Clock-Mode Conversion (Mode 0)

Figure 2. External Acquisition-Mode Conversion (Mode 1)

Figure 3. Internal Clock-Mode Conversion (Mode 2)

Figure 4. Analog Input Current vs. Input Voltage

Figure 5. Simplified Analog Input Circuit

**Table 3. Input Data Word Formats**

|                                           | DATA BIT      |    |    |    |         |    |    |    |  |

|-------------------------------------------|---------------|----|----|----|---------|----|----|----|--|

| OPERATION                                 | D7<br>(START) | D6 | D5 | D4 | D3      | D2 | D1 | D0 |  |

| Conversion-Start Byte<br>(Tables 4 and 5) | 1             | C2 | C1 | C0 | 0       | 0  | 0  | 0  |  |

| Analog-Input Configuration Byte (Table 2) | 1             | C2 | C1 | C0 | DIF/SGL | R2 | R1 | R0 |  |

| Mode-Control Byte<br>(Table 7)            | 1             | M2 | M1 | MO | 1       | 0  | 0  | 0  |  |

Table 4. Channel Selection in Single-Ended Mode (DIF/ $\overline{SGL} = 0$ )

| CHAN | NEL-SELE | СТ ВІТ |     | CHANNEL |     |     |     |     |     |     |       |

|------|----------|--------|-----|---------|-----|-----|-----|-----|-----|-----|-------|

| C2   | C1       | CO     | CH0 | CH1     | CH2 | СНЗ | CH4 | CH5 | CH6 | CH7 | AGND1 |

| 0    | 0        | 0      | +   |         |     |     |     |     |     |     | -     |

| 0    | 0        | 1      |     | +       |     |     |     |     |     |     | -     |

| 0    | 1        | 0      |     |         | +   |     |     |     |     |     | -     |

| 0    | 1        | 1      |     |         |     | +   |     |     |     |     | -     |

| 1    | 0        | 0      |     |         |     |     | +   |     |     |     | -     |

| 1    | 0        | 1      |     |         |     |     |     | +   |     |     | -     |

| 1    | 1        | 0      |     |         |     |     |     |     | +   |     | -     |

| 1    | 1        | 1      |     |         |     |     |     |     |     | +   | -     |

Table 5. Channel Selection in True-Differential Mode (DIF/ $\overline{\text{SGL}} = 1$ )

| CHANNEL-SELECT BIT |    |    | CHANNEL  |     |     |     |          |     |     |     |       |

|--------------------|----|----|----------|-----|-----|-----|----------|-----|-----|-----|-------|

| C2                 | C1 | C0 | СН0      | CH1 | CH2 | СНЗ | CH4      | CH5 | СН6 | CH7 | AGND1 |

| 0                  | 0  | 0  | +        | -   |     |     |          |     |     |     |       |

| 0                  | 0  | 1  |          |     |     |     | RESERVED |     |     |     |       |

| 0                  | 1  | 0  |          |     | +   | -   |          |     |     |     |       |

| 0                  | 1  | 1  | RESERVED |     |     |     |          |     |     |     |       |

| 1                  | 0  | 0  |          |     |     |     | +        | -   |     |     |       |

| 1                  | 0  | 1  | RESERVED |     |     |     |          |     |     |     |       |

| 1                  | 1  | 0  |          |     |     |     |          |     | +   | -   |       |

| 1                  | 1  | 1  |          |     |     |     | RESERVED |     |     |     |       |

### **Analog Input Bandwidth**

The MAX1303 input-tracking circuitry has a 1.5MHz small-signal bandwidth. The 1.5MHz input bandwidth makes it possible to digitize high-speed transient events. Harmonic distortion increases when digitizing signal frequencies above 15kHz as shown in the -SFDR, THD vs. Analog Input Frequency plot in the *Typical Operating Characteristics*.

### **Analog Input Range and Fault Tolerance**

Figure 6 illustrates the software-selectable single-ended analog input voltage range that produces a valid digital output. Each analog input channel can be independently programmed to one of seven single-ended input ranges by setting the R[2:0] control bits with DIF/SGL = 0.

Figure 7 illustrates the software-selectable differential analog input voltage range that produces a valid digital output. Each analog input differential pair can be inde-

pendently programmed to one of three differential input ranges by setting the R[2:0] control bits with DIF/SGL = 1.

Regardless of the specified input voltage range and whether the channel is selected, each analog input is ±6V fault tolerant. The analog input fault protection is active whether the device is unpowered or powered.

Any voltage beyond FSR, but within the  $\pm 6V$  fault-tolerant range, applied to an analog input results in a full-scale output voltage for that channel.

Clamping diodes with breakdown thresholds in excess of 6V protect the MAX1303 analog inputs during ESD and other transient events (Figure 5). The clamping diodes do not conduct during normal device operation, nor do they limit the current during such transients. When operating in an environment with the potential for high-energy voltage and/or current transients, protect the MAX1303 externally.

Figure 6. Single-Ended Input Voltage Ranges

Figure 7. Differential Input Voltage Ranges

### **Differential Common-Mode Range**

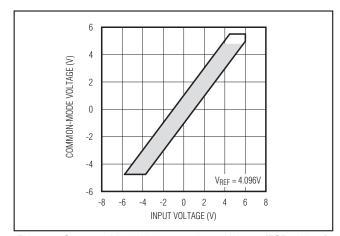

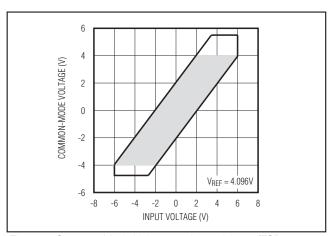

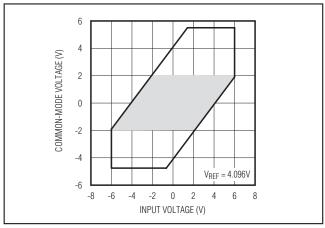

The MAX1303 differential common-mode range (VCMDR) must remain within -4.75V to +5.5V to obtain valid conversion results. The differential common-mode range is defined as:

$$V_{CMDR} = \frac{(CH_+) + (CH_-)}{2}$$

In addition to the common-mode input voltage limitations, each individual analog input must be limited to ±6V with respect to AGND1.

The range-select bits R[2:0] in the analog input configuration bytes determine the full-scale range for the corresponding channel (Tables 2 and 6). Figures 8, 9, and 10 show the valid analog input voltage ranges for the MAX1303 when operating with FSR = V<sub>REF</sub>/2, FSR = V<sub>REF</sub>, and FSR = 2 x V<sub>REF</sub>, respectively. The shaded area contains the valid common-mode voltage ranges that support the entire FSR.

### **Digital Interface**

The MAX1303 features a serial interface that is compatible with SPI/QSPI and MICROWIRE devices. DIN, DOUT, SCLK,  $\overline{CS}$ , and SSTRB facilitate bidirectional communication between the MAX1303 and the master at SCLK rates up to 10MHz (internal clock mode, mode 2), 3.67MHz (external clock mode, mode 0), or 4.39MHz (external acquisition mode, mode 1). The master, typically a microcontroller, should use the CPOL = 0, CPHA = 0, SPI transfer format, as shown in the timing diagrams of Figures 1, 2, and 3.

The digital interface is used to:

- Select single-ended or true-differential input channel configurations

- Select the unipolar or bipolar input range

- Select the mode of operation:

External clock (mode 0)

External acquisition (mode 1)

Internal clock (mode 2)

Reset (mode 4)

Partial power-down (mode 6)

Full power-down (mode 7)

Initiate conversions and read results

#### Chip Select (CS)

CS enables communication with the MAX1303. When CS is low, data is clocked into the device from DIN on the rising edge of SCLK and data is clocked out of DOUT on the falling edge of SCLK. When CS is high, activity on SCLK and DIN is ignored and DOUT is high impedance allowing DOUT to be shared with other peripherals. SSTRB is never high impedance and therefore cannot be shared with other peripherals.

Figure 8. Common-Mode Voltage vs. Input Voltage (FSR =  $V_{REF}$ )

Figure 9. Common-Mode Voltage vs. Input Voltage (FSR =  $2 \times V_{REF}$ )

Figure 10. Common-Mode Voltage vs. Input Voltage (FSR =  $4 \times V_{REF}$ )

**Table 6. Range-Select Bits**

| DIF/SGL | R2 | R1 | R0 | MODE                                                                                                           | TRANSFER FUNCTION |  |

|---------|----|----|----|----------------------------------------------------------------------------------------------------------------|-------------------|--|

| 0       | 0  | 0  | 0  | No Range Change*                                                                                               | _                 |  |

| 0       | 0  | 0  | 1  | Single-Ended Bipolar -V <sub>REF</sub> /4 to +V <sub>REF</sub> /4 Full-Scale Range (FSR) = V <sub>REF</sub> /2 | Figure 11         |  |

| 0       | 0  | 1  | 0  | Single-Ended<br>Unipolar -V <sub>REF</sub> /2 to 0V<br>FSR = V <sub>REF</sub> /2                               | Figure 12         |  |

| 0       | 0  | 1  | 1  | Single-Ended<br>Unipolar 0 to +V <sub>REF</sub> /2<br>FSR = V <sub>REF</sub> /2                                | Figure 13         |  |

| 0       | 1  | 0  | 0  | Single-Ended<br>Bipolar -V <sub>REF</sub> /2 to +V <sub>REF</sub> /2<br>FSR = V <sub>REF</sub>                 | Figure 11         |  |

| 0       | 1  | 0  | 1  | Single-Ended<br>Unipolar -V <sub>REF</sub> to 0V<br>FSR = V <sub>REF</sub>                                     | Figure 12         |  |

| 0       | 1  | 1  | 0  | Single-Ended<br>Unipolar 0V to +V <sub>REF</sub><br>FSR = V <sub>REF</sub>                                     | Figure 13         |  |

| 0       | 1  | 1  | 1  | DEFAULT SETTING Single-Ended Bipolar -V <sub>REF</sub> to +V <sub>REF</sub> FSR = 2 x V <sub>REF</sub>         | Figure 11         |  |

| 1       | 0  | 0  | 0  | No Range Change**                                                                                              | _                 |  |

| 1       | 0  | 0  | 1  | Differential Bipolar -V <sub>REF</sub> /2 to +V <sub>REF</sub> /2 FSR = V <sub>REF</sub>                       | Figure 11         |  |

| 1       | 0  | 1  | 0  | Reserved                                                                                                       |                   |  |

| 1       | 0  | 1  | 1  | Reserved                                                                                                       |                   |  |

| 1       | 1  | 0  | 0  | Differential Bipolar -V <sub>REF</sub> to +V <sub>REF</sub> FSR = 2 x V <sub>REF</sub>                         | Figure 11         |  |

| 1       | 1  | 0  | 1  | Reserved                                                                                                       |                   |  |

| 1       | 1  | 1  | 0  | Reserved —                                                                                                     |                   |  |

| 1       | 1  | 1  | 1  | Differential Bipolar -2 x V <sub>REF</sub> to +2 x V <sub>REF</sub> FSR = 4 x V <sub>REF</sub> Figure 11       |                   |  |

<sup>\*</sup>Conversion-Start Byte (see Table 3).

<sup>\*\*</sup>Mode-Control Byte (see Table 3).

### Serial Strobe Output (SSTRB)

As shown in Figures 2 and 3, the SSTRB transitions high to indicate that the ADC has completed a conversion and results are ready to be read by the master. SSTRB remains low in the external clock mode (Figure 1) and consequently may be left unconnected. SSTRB is driven high or low regardless of the state of  $\overline{\text{CS}}$ , therefore SSTRB cannot be shared with other peripherals.

#### Start Bit

Communication with the MAX1303 is accomplished using the three input data word formats shown in Table 3. Each input data word begins with a start bit. The start bit is defined as the first high bit clocked into DIN with  $\overline{\text{CS}}$  low when any of the following are true:

- Data conversion is not in process and all data from the previous conversion has clocked out of DOUT.

- The device is configured for operation in external clock mode (mode 0) and previous conversion-result bits B15–B3 have clocked out of DOUT.

- The device is configured for operation in external acquisition mode (mode 1) and previous conversionresult bits B15–B7 have clocked out of DOUT.

- The device is configured for operation in internal clock mode, (mode 2) and previous conversionresult bits B15–B4 have clocked out of DOUT.

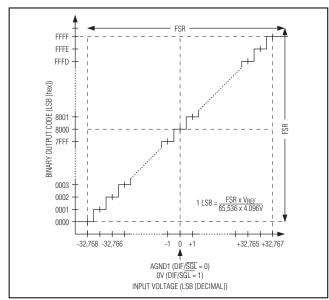

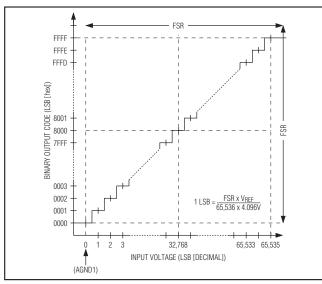

### **Output Data Format**

Output data is clocked out of DOUT in offset binary format on the falling edge of SCLK, MSB first (B15). For output binary codes, see the *Transfer Function* section and Figures 11, 12, and 13.

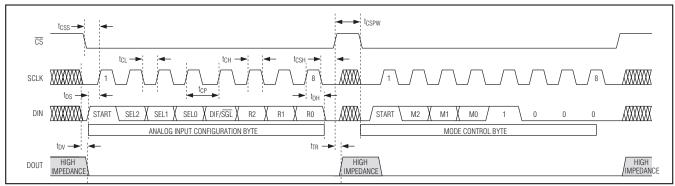

### **Configuring Analog Inputs**

Each analog input has two configurable parameters:

- Single-ended or true-differential input

- Input voltage range

These parameters are configured using the analog input configuration byte as shown in Table 2. Each analog input has a dedicated register to store its input configuration information. The timing diagram of Figure 14 shows how to write to the analog input configuration registers. Figure 15 shows DOUT and SSTRB timing.

### **Transfer Function**

An ADC's transfer function defines the relationship between the analog input voltage and the digital output code. Figures 11, 12, and 13 show the MAX1303 transfer functions. The transfer function is determined by the following characteristics:

- Analog input voltage range

- Single-ended or differential configuration

### • Reference voltage

The axes of an ADC transfer function are typically in least significant bits (LSBs). For the MAX1303, an LSB is calculated using the following equation:

$$1 LSB = \frac{FSR \times V_{REF}}{2^{N} \times 4.096V}$$

where N is the number of bits (N = 16) and FSR is the full-scale range (see Figures 6 and 7).

Figure 11. Ideal Bipolar Transfer Function, Single-Ended or Differential Input

Figure 12. Ideal Unipolar Transfer Function, Single-Ended Input, -FSR to 0

Figure 13. Ideal Unipolar Transfer Function, Single-Ended Input, 0 to +FSR

#### **Mode Control**

The MAX1303 contains one byte-wide mode-control register. The timing diagram of Figure 14 shows how to use the mode-control byte, and the mode-control byte format is shown in Table 7. The mode-control byte is used to select the conversion method and to control the power modes of the MAX1303.

### Selecting the Conversion Method

The conversion method is selected using the mode-control byte (see the *Mode Control* section), and the conversion is initiated using a conversion start command (Table 3, and Figures 1, 2, and 3). The MAX1303 converts analog signals to digital data using one of three methods:

- External Clock Mode, Mode 0 (Figure 1)

- Highest maximum throughput (see the Electrical Characteristics table)

- User controls the sample instant

- $\overline{\text{CS}}$  remains low during the conversion

- User supplies SCLK throughout the ADC conversion and reads data at DOUT

- External Acquisition Mode, Mode 1 (Figure 2)

- Lowest maximum throughput (see the *Electrical Characteristics* table)

- User controls the sample instant

- User supplies two bytes of SCLK, then drives <del>CS</del> high to relieve processor load while the ADC converts

- After SSTRB transitions high, the user supplies two bytes of SCLK and reads data at DOUT

- Internal Clock Mode, Mode 2 (Figure 3)

- High maximum throughput (see the *Electrical Characteristics* table)

- The internal clock controls the sampling instant

- User supplies one byte of SCLK, then drives CS high to relieve processor load while the ADC converts

- After SSTRB transitions high, the user supplies two bytes of SCLK and reads data at DOUT

#### External Clock Mode (Mode 0)

The MAX1303's fastest maximum throughput rate is achieved operating in external clock mode. SCLK controls both the acquisition and conversion of the analog signal, facilitating precise control over when the analog signal is captured. The analog input sampling instant is at the falling edge of the 14th SCLK (Figure 1).

Since SCLK drives the conversion in external clock mode, the SCLK frequency should remain constant while the conversion is clocked. The minimum SCLK frequency prevents droop in the internal sampling capacitor voltages during conversion.

SSTRB remains low in the external clock mode, and as a result may be left unconnected if the MAX1303 will always be used in the external clock mode.

**Table 7. Mode-Control Byte**

| BIT NUMBER | BIT NAME | DESCRIPTION                                                                                                        |

|------------|----------|--------------------------------------------------------------------------------------------------------------------|

| 7          | START    | Start Bit. The first logic 1 after $\overline{\text{CS}}$ goes low defines the beginning of the mode-control byte. |

| 6          | M2       |                                                                                                                    |

| 5          | M1       | Mode-Control Bits. M[2:0] select the mode of operation as shown in Table 8.                                        |

| 4          | MO       |                                                                                                                    |

| 3          | 1        | Bit 3 must be a logic 1 for the mode-control byte.                                                                 |

| 2          | 0        | Bit 2 must be a logic 0 for the mode-control byte.                                                                 |

| 1          | 0        | Bit 1 must be a logic 0 for the mode-control byte.                                                                 |

| 0          | 0        | Bit 0 must be a logic 0 for the mode-control byte.                                                                 |

Figure 14. Analog Input Configuration Byte and Mode-Control Byte Timing

Figure 15. DOUT and SSTRB Timing

#### External Acquisition Mode (Mode 1)

The slowest maximum throughput rate is achieved with the external acquisition method. SCLK controls the acquisition of the analog signal in external acquisition mode, facilitating precise control over when the analog signal is captured. The internal clock controls the conversion of the analog input voltage. The analog input sampling instant is at the falling edge of the 16th SCLK (Figure 2).

For the external acquisition mode,  $\overline{\text{CS}}$  must remain low for the first 15 clock cycles and then rise on or after the falling edge of the 16th SCLK cycle as shown in Figure 2. For optimal performance, idle DIN and SCLK during the conversion. With careful board layout, transitions at DIN and SCLK during the conversion have a minimal impact on the conversion result.

After the conversion is complete, SSTRB asserts high and  $\overline{\text{CS}}$  can be brought low to read the conversion result. SSTRB returns low on the rising SCLK edge of the subsequent start bit.

### Internal Clock Mode (Mode 2)

In internal clock mode, the internal clock controls both acquisition and conversion of the analog signal. The internal clock starts approximately 100ns to 400ns after the falling edge of the eighth SCLK and has a rate of about 4.5MHz. The analog input sampling instant occurs at the falling edge of the 11th internal clock signal (Figure 3).

For the internal clock mode,  $\overline{\text{CS}}$  must remain low for the first seven SCLK cycles and then rise on or after the falling edge of the eighth SCLK cycle. After the conversion is complete, SSTRB asserts high and  $\overline{\text{CS}}$  can be brought low to read the conversion result. SSTRB returns low on the rising SCLK edge of the subsequent start bit.

#### Reset (Mode 4)

As shown in Table 8, set M[2:0] = 100 to reset the MAX1303 to its default conditions. The default conditions are full power operation with each channel configured for  $\pm V_{REF}$ , bipolar, single-ended conversions using external clock mode (mode 0).

### Partial Power-Down Mode (Mode 6)

As shown in Table 8, when M[2:0] = 110, the device enters partial power-down mode. In partial power-down, all analog portions of the device are powered down except for the reference voltage generator and bias supplies.

To exit partial power-down, change the mode by issuing one of the following mode-control bytes (see the *Mode Control* section):

- External-clock-mode control byte

- External-acquisition-mode control byte

- Internal-clock-mode control byte

- Reset byte

- Full power-down-mode control byte

This prevents the MAX1303 from inadvertently exiting partial power-down mode because of a  $\overline{\text{CS}}$  glitch in a noisy digital environment.

### Table 8. Mode-Control Bits M[2:0]

| M2 | M1 | MO | MODE                     |  |  |

|----|----|----|--------------------------|--|--|

| 0  | 0  | 0  | External Clock (DEFAULT) |  |  |

| 0  | 0  | 1  | External Acquisition     |  |  |

| 0  | 1  | 0  | Internal Clock           |  |  |

| 0  | 1  | 1  | Reserved                 |  |  |

| 1  | 0  | 0  | Reset                    |  |  |

| 1  | 0  | 1  | Reserved                 |  |  |

| 1  | 1  | 0  | Partial Power-Down       |  |  |

| 1  | 1  | 1  | Full Power-Down          |  |  |

#### Full Power-Down Mode (Mode 7)

When M[2:0] = 111, the device enters full power-down mode and the total supply current falls to  $1\mu$ A (typ). In full power-down, all analog portions of the device are powered down. When using the internal reference, upon exiting full power-down mode, allow 10ms for the internal reference voltage to stabilize prior to initiating a conversion.

To exit full power-down, change the mode by issuing one of the following mode-control bytes (see the *Mode Control* section):

- External-clock-mode control byte

- External-acquisition-mode control byte

- Internal-clock-mode control byte

- Reset byte

- Partial power-down-mode control byte

This prevents the MAX1303 from inadvertently exiting full power-down mode because of a  $\overline{\text{CS}}$  glitch in a noisy digital environment.

#### **Power-On Reset**

The MAX1303 powers up in normal operation configured for external clock mode with all circuitry active (Tables 7 and 8). Each analog input channel (CH0-CH7) is set for single-ended conversions with a  $\pm V_{REF}$  bipolar input range (Table 6).

Allow the power supplies to stabilize after power-up. Do not initiate any conversions until the power supplies have stabilized. Additionally, allow 10ms for the internal reference to stabilize when  $C_{REF}=1.0\mu F$  and  $C_{RECAP}=0.1\mu F$ . Larger reference capacitors require longer stabilization times.

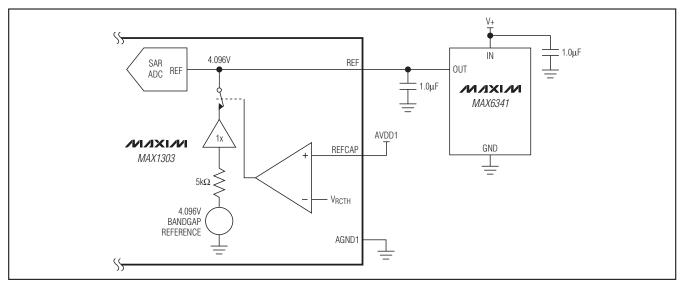

### Internal or External Reference

The MAX1303 operates with either an internal or external reference. The reference voltage impacts the ADC's FSR (Figures 11, 12, and 13). An external reference is recommended if more accuracy is required than the internal reference provides, and/or multiple converters require the same reference voltage.

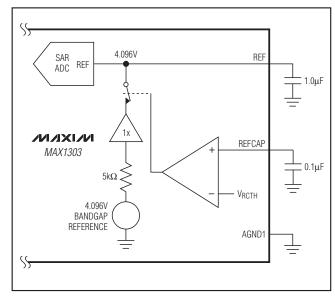

#### Internal Reference

The MAX1303 contains an internal 4.096V bandgap reference. This bandgap reference is connected to REFCAP through a nominal  $5k\Omega$  resistor (Figure 16). The voltage at REFCAP is buffered creating 4.096V at REF. When using the internal reference, bypass REFCAP with a 0.1 $\mu$ F or greater capacitor to AGND1 and bypass REF with a 1.0 $\mu$ F or greater capacitor to AGND1.

#### External Reference

For external reference operation, disable the internal reference and reference buffer by connecting REFCAP to AVDD1. With AVDD1 connected to REFCAP, REF becomes a high-impedance input and accepts an external reference voltage. The MAX1303 external reference current varies depending on the applied reference voltage and the operating mode (see the External Reference Input Current vs. External Reference Input Voltage in the *Typical Operating Characteristics*).

Figure 16. Internal Reference Operation

Figure 17. External Reference Operation

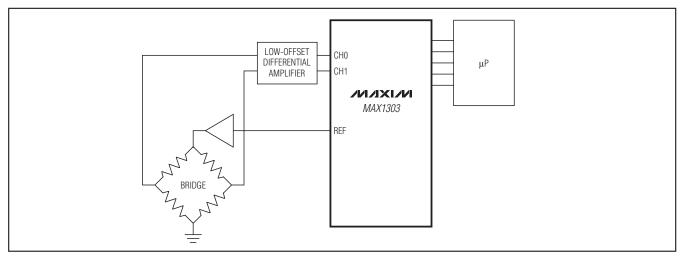

Figure 18. Bridge Application

# Applications Information Noise Reduction

Additional samples can be taken and averaged (oversampling) to remove the effect of transition noise on conversion results. The square root of the number of samples determines the improvement in performance. For example, with 2/3 LSB<sub>RMS</sub> (4 LSB<sub>P-P</sub>) transition noise, 16 ( $4^2 = 16$ ) samples must be taken to reduce the noise to 1 LSB<sub>P-P</sub>.

#### Interface with 4-20mA Signals

Figure 18 illustrates a simple interface between the MAX1303 and a 4–20mA signal. 4–20mA signaling can be used as a binary switch (4mA represents a logic-low