# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

EVALUATION KIT

AVAILABLE

4-Channel, Automotive Class D Audio Amplifier

## **General Description**

The MAX13301 combines four high-efficiency Class D amplifiers with integrated diagnostic hardware for reliable automotive audio systems, and delivers up to 80W at 10% THD+N per channel into  $4\Omega$  when operating from a 24V supply.

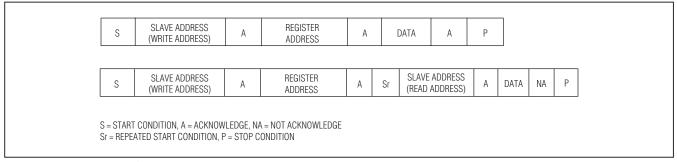

The internal diagnostics evaluate each channel's output impedance to check for shorts across the outputs, to the battery, or to ground. The I<sup>2</sup>C interface allows the system to query critical device parameters such as device temperature and output clipping. The device is programmable to four different I<sup>2</sup>C addresses.

The audio amplifiers feature single-ended analog inputs with a common negative input. The MAX13301 has a fixed gain of 26dB.

The Class D amplifier has 10 programmable switching frequencies between 300kHz and 750kHz.

The BTL outputs are protected against short circuits and thermal overload. The outputs can be configured as a 2-, 3-, or 4-channel amplifier. The device provides 50V load-dump protection, and is offered in the thermally enhanced, 48-pin TSSOP-EPR package operating over the -40°C to +125°C temperature range.

#### **Applications**

Car Stereo

Rear-Seat Entertainment Units

**Discrete Amplifier Modules**

Active Loudspeaker Systems

Typical Operating Circuit appears at end of data sheet.

Radio Head Units

Mobile Surround Systems

## **Features**

- High Output Power (10% THD+N)

- $\diamond$  2 x 160W into 2Ω at 24V  $\diamond$  4 x 80W into 4Ω at 24V

- ♦ 2 Channels Can Be Paralleled

- Feedback After the Filter

Improves THD+N

- Low Output Impedance

- ♦ High-Frequency Response

- ♦ Improved Damping of Complex Loads

- ♦ Enables Low-Cost Inductors

- 102dB SNR

- ♦ Low 0.04% THD+N

- ♦ 70dB PSRR

- On-Board Diagnostics

- ♦ Short-to-Battery/GND

- ♦ Open/Shorted Load

- ♦ Tweeter Detect

- Protection and Monitoring Functions:

- ♦ Short-Circuit Protection

- ♦ 50V Load-Dump Protection

- ♦ Programmable Clip Detection

- OC Offset Detection

- ♦ Open Battery/GND Tolerant

- ♦ Thermal-Overload Protection

- ♦ Thermal Warning Indication

- Four-Address I<sup>2</sup>C Control Interface

- Low-Power Shutdown Mode

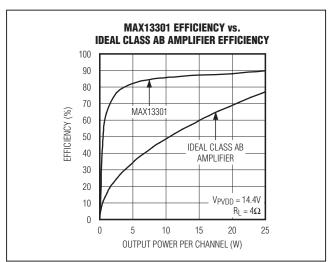

- Up to 90.5% Efficiency

- ♦ -40°C to +125°C Ambient Operating Temperature

- ♦ 48-Pin TSSOP-EPR (Top Side Exposed Pad) Package

- ♦ AEC-Q100 Qualified

## **Ordering Information**

| PART           | PIN-PACKAGE   | SUPPLY VOLTAGE<br>RANGE (V) |  |  |  |  |

|----------------|---------------|-----------------------------|--|--|--|--|

| MAX13301AUM/V+ | 48 TSSOP-EPR* | 6 to 25.5                   |  |  |  |  |

|                |               |                             |  |  |  |  |

*Note:* The device operates over the -40°C to +125°C operating

temperature range.

N denotes an automotive qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EPR = Top side exposed pad.

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| PVDD to PGND                  | 0.3V to +30V                       |

|-------------------------------|------------------------------------|

| PVDD to PGND (t < 200ms)      | 0.3V to +50V                       |

| PVDD Ramp Rate                | 25V/ms                             |

| V <sub>DD5</sub> , CM to PGND | 0.3V to +6V                        |

| CP to PGND(VPVDD -            | 0.3V) to (VCHOLD + 0.3V)           |

| CHOLD to PVDD                 | 0.3V to +6V                        |

| OUT_ to PGND, FB_ to PGND     | 0.3V to (V <sub>PVDD</sub> + 0.3V) |

| VDD to GND                    | 0.3V to +6V                        |

| REF to GND                    | 0.3V to +6V                        |

| SCL, SDA, SYNC to GND         | 0.3V to +6V                        |

| MUTE_CL1, CL0, FLT_OT, EN to GND<br>IN_ to GND<br>GND to PGND                                                                                                 | 0.3V to +6V                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Continuous Power Dissipation (Notes 1 and 2<br>TSSOP (derate 16.7mW/°C above 70°C)                                                                            | /                                                            |

| Operating Temperature Range<br>Junction Temperature Range<br>Storage Temperature Range<br>Lead Temperature (soldering, 10s)<br>Soldering Temperature (reflow) | 40°C to +125°C<br>40°C to +150°C<br>65°C to +150°C<br>4300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# PACKAGE THERMAL CHARACTERISTICS (Notes 1 and 2)

TSSOP

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$ ..........60°C/W Junction-to-Case Thermal Resistance  $(\theta_{JC})$ ............1°C/W

- Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

- **Note 2:** The 48-pin TSSOP-EPR package has a top side exposed pad for enhanced thermal management. Connect this exposed pad to an external heatsink to ensure the device is adequately cooled. The maximum power dissipation in the device is a function of this external heatsink and other system parameters. See the *Thermal Information* section for more information.

## **ELECTRICAL CHARACTERISTICS**

$(V_{PVDD} = 14.4V, V_{DD} = V_{DD5} = 5V, V_{GND} = V_{PGND} = 0V, f_{SW} = 500kHz, MAP.COMP[2:0] = (see Table 20 for applicable setting), TA = -40°C to +125°C; typical values are at TA = +25°C, unless otherwise noted.) (Note 3)$

| PARAMETER                             | SYMBOL           | CONDITIONS                                          | MIN  | ТҮР                  | MAX  | UNITS |

|---------------------------------------|------------------|-----------------------------------------------------|------|----------------------|------|-------|

| AMPLIFIER DC CHARACTERIS              | TICS             |                                                     |      |                      |      |       |

|                                       |                  |                                                     | 8    |                      | 25.5 |       |

| Supply Voltage Range                  | Vpvdd            | Operational                                         | 6    |                      |      | V     |

|                                       | V <sub>DD5</sub> |                                                     | 4.75 | 5                    | 5.5  |       |

|                                       | VDD              |                                                     | 4.5  | 5                    | 5.5  |       |

| PVDD UVLO Threshold                   |                  | Falling                                             | 5.2  | 5.35                 | 5.6  | V     |

| PVDD OVLO Threshold                   |                  | Rising                                              | 26   | 27                   | 30   | V     |

| PVDD OVLO Response Timing             |                  | Rising                                              | 4    | 14                   | 55   | μs    |

| OUT_ and FB_ Voltage                  |                  | OV active                                           |      | V <sub>PVDD</sub> /2 |      | V     |

| Vee LIV/ Threehold                    |                  | Falling                                             | 4.2  |                      | 4.35 |       |

| V <sub>DD</sub> UV Threshold          |                  | Rising                                              |      | 4.5                  | 4.6  | V     |

| VDD UV Threshold Hysteresis           |                  |                                                     | 0.1  | 0.2                  |      | V     |

| V <sub>DD</sub> UV Threshold Deglitch |                  |                                                     |      | 1                    |      | μs    |

|                                       | IPVDD            |                                                     |      | 70                   |      | μA    |

| Quiescent Supply Current              | IVDD5            | $I_{VDD5}$ RL = $\infty$ , play mode (CTRL2 = 0x0F) |      | 60                   | 72   |       |

|                                       | Ivdd             |                                                     |      | 50                   | 75   | mA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(VPVDD = 14.4V, VDD = VDD5 = 5V, VGND = VPGND = 0V, fSW = 500kHz, MAP.COMP[2:0] = (see Table 20 for applicable setting), T_A = -40°C to +125°C; typical values are at T_A = +25°C, unless otherwise noted.) (Note 3)$

| PARAMETER                                | SYMBOL    | CON                                                               | DITIONS                                        | MIN | TYP   | MAX | UNITS |  |

|------------------------------------------|-----------|-------------------------------------------------------------------|------------------------------------------------|-----|-------|-----|-------|--|

|                                          | IPVDD_    | TA = +25°C, VEN =                                                 | OV                                             |     | 7     |     |       |  |

| PVDD Shutdown Supply Current             | SHDN      | $T_A = T_{MIN}$ to +85°C                                          |                                                |     | 17    | μA  |       |  |

|                                          | IVDD5_    | T <sub>A</sub> = +25°C, V <sub>EN</sub> =                         |                                                | 0.1 |       |     |       |  |

| V <sub>DD5</sub> Shutdown Supply Current | SHDN      | $T_A = T_{MIN}$ to +85°C                                          | $V_{\rm EN} = 0V$                              |     |       | 2   | μA    |  |

| Vez Chutdown Cupply Current              |           | $T_A = +25^{\circ}C, V_{EN} =$                                    | 0V                                             |     | 0.1   |     |       |  |

| V <sub>DD</sub> Shutdown Supply Current  | IVDD_SHDN | TA = TMIN to +85°C                                                | C, VEN = OV                                    |     |       | 2   | μA    |  |

| Ctondby Cupply Current                   | IVDD5     |                                                                   |                                                |     | 1     |     |       |  |

| Standby Supply Current                   | IVDD      | $CTRL2 = 0x20, V_{EN}$                                            | ] = 5V                                         |     | 10    |     | mA    |  |

| Output Leakage                           |           | VOUT_ = 14.4V                                                     |                                                |     |       | 200 |       |  |

| Oulpul Leakage                           |           | $V_{OUT} = 0V$                                                    |                                                |     |       | 1   | μA    |  |

| Output Discharge Current                 |           | CTRL3.DIS = 1                                                     |                                                |     | 8     |     | mA    |  |

| R <sub>DS(ON)</sub> per Output           |           | Excluding wire bon                                                | d resistance                                   |     | 70    |     | mΩ    |  |

| FB_ Resistance                           |           |                                                                   |                                                |     | 310   |     | kΩ    |  |

| Output Offset                            | Vos       | TA = +25°C, mute r<br>no input signal                             | +25°C, mute mode (CTRL2 = 0x00),<br>put signal |     |       | 15  | mV    |  |

|                                          |           | TA = TMIN to TMAX                                                 |                                                |     | 100   |     |       |  |

| OUT_ Output Impedance                    |           |                                                                   |                                                |     | 100   |     | mΩ    |  |

| AMPLIFIER AC CHARACTERIS                 | rics      |                                                                   |                                                |     |       |     |       |  |

|                                          |           | THD+N = 1%, R <sub>L</sub> = 4 $\Omega$ , V <sub>PVDD</sub> = 24V |                                                |     | 66    |     |       |  |

| Output Power                             | Роит      | THD+N = 10%, RL                                                   |                                                | 80  |       | W   |       |  |

|                                          | 1001      | THD+N = 10%, RL parallel mode                                     |                                                | 160 |       |     |       |  |

| Signal-Path Gain                         |           |                                                                   |                                                |     | 26    |     | dB    |  |

| Channel-to-Channel Gain<br>Tracking      |           |                                                                   |                                                | -1  | +0.1  | +1  | dB    |  |

|                                          |           | IN0+, IN1+, IN2+, I                                               | N3+                                            |     | 20    |     |       |  |

| Input Resistance                         |           | IN-                                                               |                                                |     | 5     |     | kΩ    |  |

| Mute Attenuation                         |           | Guaranteed by des only                                            | ign, test is functional                        | 90  | 100   |     | dB    |  |

|                                          |           |                                                                   | IN-                                            | 5   | 10    |     |       |  |

| Precharge Current                        |           | CTRL1.PRE = 1                                                     | IN_+                                           | 1   | 2     |     | mA    |  |

|                                          |           | $V_{DD} = 4.5V$ to 5.5V                                           |                                                |     | 70    |     | 1     |  |

| Power-Supply Rejection Ratio             |           | VPVDD = 1VP-P ripple, 100Hz to 10kHz<br>VPVDD = 8V to 25.5V       |                                                |     | 60    |     | dB    |  |

|                                          |           |                                                                   |                                                |     | 68    |     |       |  |

| REF Voltage                              |           | $C_{\text{REF}(\text{MIN})} = 1 \mu F$                            |                                                |     | 2.224 |     | V     |  |

| REF Output Impedance                     |           | DC                                                                |                                                |     | 800   |     | Ω     |  |

| Input Voltage Range                      |           | AC-coupled                                                        |                                                |     |       | 1.2 | VRMS  |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PVDD} = 14.4V, V_{DD} = V_{DD5} = 5V, V_{GND} = V_{PGND} = 0V, f_{SW} = 500kHz, MAP.COMP[2:0] = (see Table 20 for applicable setting), T_A = -40°C to +125°C; typical values are at T_A = +25°C, unless otherwise noted.) (Note 3)$

| PARAMETER                                       | SYMBOL | COND                                                                          | ITIONS                                     | MIN           | ТҮР  | MAX  | UNITS          |  |

|-------------------------------------------------|--------|-------------------------------------------------------------------------------|--------------------------------------------|---------------|------|------|----------------|--|

| Total Harmonic Distortion Plus                  | THD+N  | $P_{OUT} = 10W, R_L = 4$<br>20kHz AES17 filter, f                             |                                            | 0.04          | 0.14 | - %  |                |  |

| Noise                                           |        | POUT = 1W to 10W,<br>to 20kHz AES17 filte                                     | $R_L = 4\Omega$ , BW = 22Hz<br>r, f = 1kHz |               | 0.1  | 70   |                |  |

|                                                 |        | A-weighted, VPVDD =                                                           | = 24V                                      |               | 100  |      |                |  |

| Noise                                           | Ν      | 22Hz to 22kHz, V <sub>PVE</sub>                                               | DD = 24V                                   |               | 140  |      | ↓<br>↓<br>VRMS |  |

|                                                 |        | A-weighted, CTRL5.S<br>SSEN = 1, VPVDD = 2                                    |                                            |               | 100  |      |                |  |

| Crosstalk                                       |        | POUT_ = 4W, f = 1kH                                                           | Hz to 10kHz                                |               | 60   |      | dB             |  |

| Efficiency                                      | η      | $R_L = 4\Omega$ , $P_{OUT} = 20$<br>V <sub>DD</sub> supplied from a<br>supply |                                            |               | 88   |      | %              |  |

| Internal Switching Frequency<br>Adjust Range    |        | 6 to 15 clock-divider                                                         | range                                      | 300           |      | 750  | kHz            |  |

| ONE-TIME DIAGNOSTICS                            |        |                                                                               |                                            |               |      |      |                |  |

| Short-to-Ground Detection                       |        | CTRL2.STBY = 0, CT                                                            | TRL3.SDET = 1                              |               | 75   |      | Ω              |  |

| Short-to-PVDD Detection<br>Threshold            |        | CTRL2.STBY = 1, CTRL3.SDET = 1                                                |                                            |               | 6    |      | V              |  |

| Open-Load Detection                             |        | CTRL3.LDM = 1, power amplifier mode<br>CTRL3.LDM = 0, line-driver mode        |                                            | 70            | 100  |      | Ω              |  |

|                                                 |        |                                                                               |                                            | 200           | 300  |      |                |  |

|                                                 |        | 15kHz < f < 25kHz,                                                            | CTRL3.HCL = 0                              | 160           | 291  | 500  |                |  |

| Low-Current Threshold                           |        | $T_A = +25^{\circ}C,$<br>CTRL3.TW = 1                                         | CTRL3.HCL = 1                              | 200           | 364  | 625  | - mA           |  |

|                                                 |        | f < 20Hz,                                                                     | CTRL3.HCL = 0                              | 0.65          | 1.15 | 1.85 |                |  |

| High-Current Threshold                          |        | CTRL3.TW = 0                                                                  | CTRL3.HCL = 1                              | 0.9 1.65 2.15 |      | 2.15 | - A            |  |

| CONTINUOUS DIAGNOSTICS                          |        |                                                                               |                                            |               |      |      |                |  |

| Differential Output Offset Voltage<br>Threshold |        | No audio in play mo                                                           | de                                         | 0.56          | 1.04 | 1.6  | V              |  |

|                                                 |        |                                                                               | CTRL1.CLVL[1:0]<br>= 11                    | 1             |      |      |                |  |

|                                                 |        | D. 10                                                                         | CTRL1.CLVL[1:0]<br>= 01                    |               | 3    |      |                |  |

| Clip-Detect Threshold                           |        | $R_L = 4\Omega$                                                               | CTRL1.CLVL[1:0]<br>= 10                    |               | 5    |      | - %THDN        |  |

|                                                 |        |                                                                               | CTRL1.CLVL[1:0]<br>= 00                    |               | 10   |      | 1              |  |

# ELECTRICAL CHARACTERISTICS (continued)

$(VPVDD = 14.4V, VDD = VDD5 = 5V, VGND = VPGND = 0V, fSW = 500kHz, MAP.COMP[2:0] = (see Table 20 for applicable setting), T_A = -40°C to +125°C; typical values are at T_A = +25°C, unless otherwise noted.) (Note 3)$

| PARAMETER                       | SYMBOL            | CONE                               | DITIONS          | MIN  | TYP       | MAX  | UNITS |  |

|---------------------------------|-------------------|------------------------------------|------------------|------|-----------|------|-------|--|

|                                 |                   | OUT shorted<br>to ground/PVDD,     | CTRL3.HCL = 0    |      | 1.03      |      |       |  |

| Short-to-Ground/PVDD            |                   | $CTRL1.CL_TH = 1$                  | CTRL3.HCL = 1    |      | 1.28      |      | Δ.    |  |

| Short-to-Ground/PVDD            |                   | OUT shorted                        | CTRL3.HCL = 0    |      | 3.09      |      | - A   |  |

|                                 |                   | to ground/PVDD,<br>CTRL1.CL_TH = 0 | CTRL3.HCL = 1    |      | 3.86      |      |       |  |

| Level 1 Output Current Limit    | ILIM1             | CTRL3.HCL = 0                      |                  | 5.5  | 7         |      | A     |  |

| Level 2 Output Current Limit    | I <sub>LIM2</sub> | CTRL3.HCL = 1                      |                  | 7    | 8.75      |      | A     |  |

| THERMAL PROTECTION              |                   |                                    |                  |      |           |      |       |  |

| Thermal Warning Range 1         |                   | Guaranteed monoto                  | nic              |      | 110       |      | °C    |  |

| Thermal Warning Range 2         |                   | Guaranteed monoto                  | nic              |      | 120       |      | °C    |  |

| Thermal Warning Range 3         |                   | Guaranteed monoto                  | nic              |      | 130       |      | °C    |  |

| Thermal Warning Range 4         |                   | Guaranteed monoto                  | nic              |      | 140       |      | °C    |  |

| Thermal Shutdown Level          |                   | Guaranteed monoto                  | nic              | 150  | 165       |      | °C    |  |

| Thermal Warning Hysteresis      |                   |                                    |                  |      | 5         |      | °C    |  |

| Thermal Shutdown Hysteresis     |                   |                                    |                  | 15   |           |      | °C    |  |

| CHARGE PUMP                     |                   | 1                                  |                  | ·    |           |      |       |  |

| Switching Frequency             |                   | $f_{CP} = f_{SW}$                  |                  | 300  |           | 750  | kHz   |  |

| Soft-Start Time                 |                   |                                    |                  |      | 100       |      | μs    |  |

| Charge-Pump Output<br>Impedance |                   | Guaranteed by FET measurement      | RDS(ON)          |      | 1.8       |      | Ω     |  |

| Output Voltage                  |                   |                                    |                  | ,    | VPVDD + 5 |      | V     |  |

| INTERNAL OSCILLATOR             |                   | 1                                  |                  |      |           |      | ,     |  |

| SYNC I/O Frequency Range        |                   | 2x switching frequer               | псу              | 0.6  |           | 1.5  | MHz   |  |

| Frequency                       |                   | Spread-spectrum di                 | sabled           | 17.1 | 18        | 18.9 | MHz   |  |

| DIGITAL INTERFACE (SCL, SD      | A, ADDR, CL       | 0, MUTE_CL1, EN, S                 | SYNC, FLT_OT)    |      |           |      |       |  |

| SYNC High                       |                   | CTRL1.CM[1:0] = 0                  | 1, ISOURCE = 3mA | 4.5  |           |      | V     |  |

| SYNC Low                        |                   | CTRL1.CM[1:0] = 0                  | 1, Isink = 3mA   |      |           | 0.4  | V     |  |

| Input Voltage High              | Vinh              |                                    |                  | 2.0  |           |      | V     |  |

| Input Voltage Low               | VINL              |                                    |                  |      |           | 0.8  | V     |  |

| Input Voltage Hysteresis        |                   |                                    |                  |      | 300       |      | mV    |  |

| Input Leakage Current           |                   | SDA, SCL, CLO, MU                  | TE_CL1, FLT_OT   |      |           | ±10  | μA    |  |

| Output Low Voltage              |                   | SDA, CLO, MUTE_C<br>FLT_OT         | L1, ISINK = 3mA, |      |           | 0.4  | V     |  |

| Dulldown Current                |                   | MUTE_CL1                           |                  |      | 5         | 13   |       |  |

| Pulldown Current                |                   | EN                                 |                  |      | 10        | 18   | - μΑ  |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PVDD} = 14.4V, V_{DD} = V_{DD5} = 5V, V_{GND} = V_{PGND} = 0V, f_{SW} = 500 \text{kHz}, MAP.COMP[2:0] = (see Table 20 for applicable setting), TA = -40°C to +125°C; typical values are at TA = +25°C, unless otherwise noted.) (Note 3)$

| PARAMETER                  | SYMBOL         | CONDITIONS                        | MIN      | TYP | MAX | UNITS |

|----------------------------|----------------|-----------------------------------|----------|-----|-----|-------|

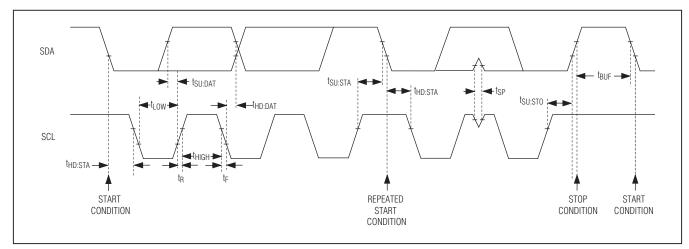

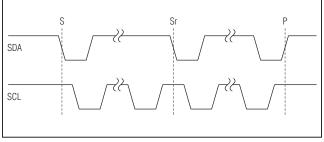

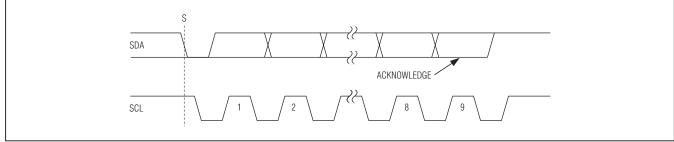

| I <sup>2</sup> C TIMING    | ·              |                                   | <b>!</b> |     |     |       |

| Output Fall Time           | tOF            | C <sub>BUS</sub> = 10pF to 400pF  |          |     | 250 | ns    |

| Pin Capacitance            |                |                                   |          |     | 10  | pF    |

| Clock Frequency            | fscl           |                                   |          |     | 400 | kHz   |

| SCL Low Time               | tLOW           |                                   | 1.3      |     |     | μs    |

| SCL High Time              | thigh          |                                   | 0.6      |     |     | μs    |

| START Condition Hold Time  | thd:Sta        | Repeated START condition          | 0.6      |     |     | μs    |

| START Condition Setup Time | tsu:sta        | Repeated START condition          | 0.6      |     |     | μs    |

| Data Hold Time             | thd:dat        |                                   | 0        |     | 900 | ns    |

| Data Setup Time            | tsu:dat        |                                   | 100      |     |     | ns    |

| Input Rise Time            | t <sub>R</sub> | SCL, SDA                          |          |     | 300 | ns    |

| Input Fall Time            | tF             | SCL, SDA                          |          |     | 300 | ns    |

| STOP Condition Setup Time  | tsu:sto        |                                   | 0.6      |     |     | μs    |

| Bus Free Time              | tBUF           | Between START and STOP conditions | 1.3      |     |     | μs    |

| Maximum Bus Capacitance    | CBUS           | Per bus line                      |          |     | 400 | pF    |

**Note 3:** All units are 100% production tested at  $T_A = +25^{\circ}C$ . All temperature limits are guaranteed by design.

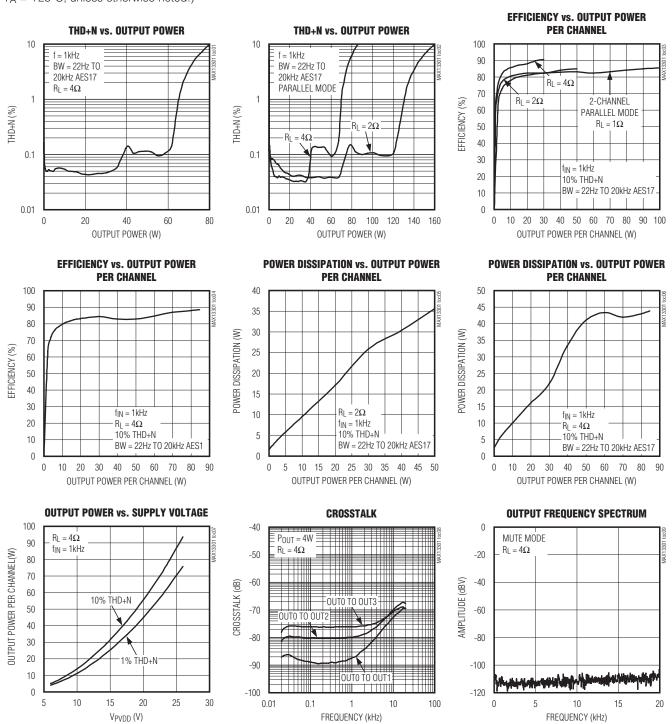

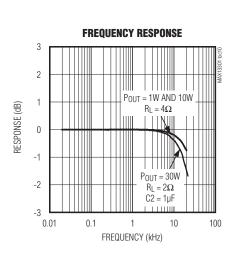

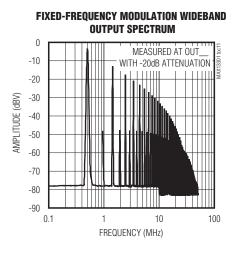

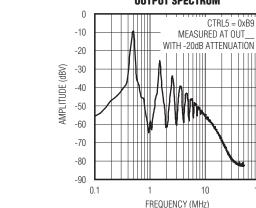

# **Typical Operating Characteristics**

$(V_{PVDD} = 24V, V_{DD} = V_{DD5} = 5V, V_{GND} = V_{PGND} = 0V, f_{SW} = 500 \text{kHz}, MAP.COMP[2:0] = 011, see Table 32 for LC filter value, T_A = +25°C, unless otherwise noted.)$

MAX13301

## **Typical Operating Characteristics (continued)**

$(V_{PVDD} = 24V, V_{DD} = V_{DD5} = 5V, V_{GND} = V_{PGND} = 0V, f_{SW} = 500 \text{kHz}, MAP.COMP[2:0] = 011, see Table 32 for LC filter value, T_A = +25°C, unless otherwise noted.)$

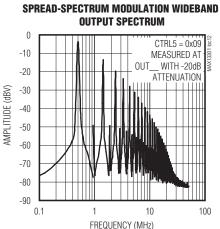

SPREAD-SPECTRUM MODULATION WIDEBAND OUTPUT SPECTRUM

100

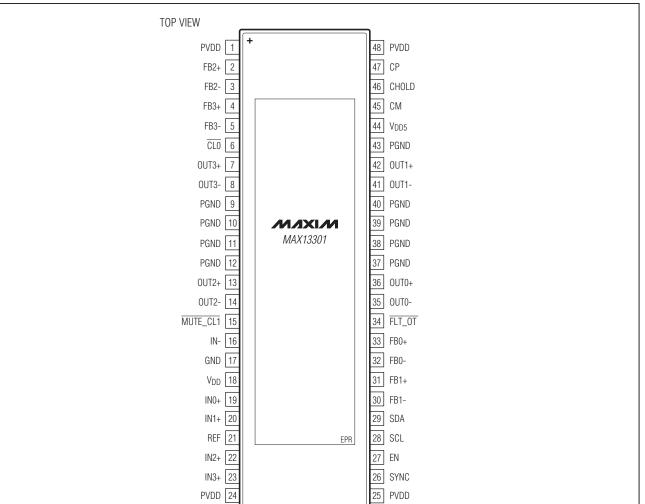

# Pin Configuration

# **Pin Description**

| PIN           | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 24, 25, 48 | PVDD | Audio Output Power-Supply Input. Bypass each PVDD to its PGND pair locally with $0.1\mu$ F and $4.7\mu$ F ceramic capacitors. Each PVDD/PGND pair consists of one PVDD and two PGNDs. The PVDD/PGND pairs are 1 and 9-10, 48 and 39-40, 24 and 11-12, and 25 and 37-38. Bypassing PVDD locally minimizes the area of di/dt loops. An additional $1000\mu$ F, low-ESR electrolytic capacitor should be placed from 1 and 48 to PGND and 24 and 25 to PGND. |

| 2             | FB2+ | Output 2 Positive Feedback. Connect to the LC filter's positive output through a 150 $\Omega$ ±1% resistor.                                                                                                                                                                                                                                                                                                                                               |

| 3             | FB2- | Output 2 Negative Feedback. Connect to the LC filter's negative output through a 150 $\pm$ 1% resistor.                                                                                                                                                                                                                                                                                                                                                   |

TSSOP

# Pin Description (continued)

| 4         FB3+         Output 3 Positive Feedback. Connect to the LC filter's positive output through a 150Ω ±1% resistor.           5         FB3-         Output 3 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.           6         CLD         Active-Low Open-Drain Olip 0 Output. CLD is configurable to provide clipping indication for outputs 0 and 1 or or all four outputs.           7         OUT3+         Channel 3 Power Amplifier Positive Output           9-12,         PGND         Audio Output Power Ground           13         OUT2+         Channel 2 Power Amplifier Positive Output           14         OUT2-         Channel 2 Power Amplifier Positive Output           14         OUT2-         Channel 2 Power Amplifier Positive Output           14         OUT2-         Channel 2 Power Amplifier Positive Output           15         MUTE_CLT         Nate Input or Active-Low Open-Drain Olip 1 Output. MUTE_CLT is configurable as a mute input or as an open-drain olip indicator output X and 3. This pin also selects the low bit of the IP2 address and is latched upon the rising edge of the EN pin. MUTE_CLT and a simitemal Sup aduldown.           16         IN-         Common Audio Negative Input. IN- has 5kΩ of input resistance. Bypass to analog ground with 2µE or 4 x 0R_1 = 0.           17         GND         Analog Ground         SV Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor of at least 0.47µE to INA+.                                                                                                                                                                              | PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5         FB3-<br>resistor.         Output 3 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ± 1%<br>resistor.           6         GL0         Active-Low Open-Drain Clip 0 Output. GL0 is configurable to provide clipping indication for outputs<br>0 and 1 or for all four outputs.           7         OUT3+         Channel 3 Power Amplifier Positive Output           8         OUT3-         Channel 3 Power Amplifier Negative Output           9-12,<br>37-40, 43         PGND         Audio Output Power Ground           13         OUT2-         Channel 2 Power Amplifier Positive Output           14         OUT2-         Channel 2 Power Amplifier Negative Output           14         OUT2-         Channel 2 Power Amplifier Positive Output.           15         MUTE_CL1         Mute Input or Active-Low Open-Drain Clip 1 Output. MUTE_CL1 is configurable as a mute input or<br>as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute<br>all four outputs. As an output. MUTE_CL1 provides clipping indication for outputs 2 and 3. This<br>pin also selects the low bit of the 12C address and is latched upon the rising edge of the EN pin.<br>MUTE_CL1 has an internal Sup Auldown.           16         IN-         Common Audio Negative Input. IN- has SkΩ of input resistance. Bypass to analog ground with 2µF<br>or 4 × ClN_+.           19         IN0+         Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN0+.           20         I                                                                                                               | 4   | FB3+            |                                                                                                                                                                                                                                                                                                                 |

| b         CLU         0 and 1 or for all four outputs.           7         OUT3+         Channel 3 Power Amplifier Positive Output           8         OUT3-         Channel 3 Power Amplifier Negative Output           9-12,<br>37-40, 43         PGND         Audio Output Power Ground           13         OUT2+         Channel 2 Power Amplifier Negative Output           14         OUT2-         Channel 2 Power Amplifier Negative Output           15         MUTE_CL1         Mule Input or Active-Low Open-Orain Clip 1 Output. MUTE_CL1 is configurable as a mute input or<br>as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute<br>all four outputs. As an output. MUTE_CL1 provides clipping indication for outputs 2 and 3. This<br>pin also selects the low bit of the I/2 address and is latched upon the rising edge of the EN pin.<br>MUTE_CL1 has an internal Sub_ApulIdown.           16         IN-         Common Audio Negative Input. IN- has 5kQ of input resistance. Bypass to analog ground with 2µF<br>or 4 × CIN_+.           18         VpD         5V Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. VpD<br>provides power to the analog and digital circuitry.           19         IN0+         Channel 1 Audio Input. IN0+ has 20kQ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN1+.           21         REF         2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.           22         IN1+         Channel 3 Audio Inpu                                                                                                                              | 5   | FB3-            | Output 3 Negative Feedback. Connect to the LC filter's negative output through a 150 $\Omega$ ±1%                                                                                                                                                                                                               |

| 8         OUT3-         Channel 3 Power Amplifier Negative Output           9-12,<br>37-40, 43         PGND         Audio Output Power Ground           13         OUT2+         Channel 2 Power Amplifier Negative Output           14         OUT2-         Channel 2 Power Amplifier Negative Output           14         OUT2-         Channel 2 Power Amplifier Negative Output           15         MUTE_CLT         Mute Input or Active-Low Open-Drain Clip 1 Output. MUTE_CLT is configurable as a mute input or<br>as an open-drain clip indicator output. When configured as an input, drive MUTE_CLT low to mute<br>all four outputs. As an output, MUTE_CLT provides clipping indication for outputs 2 and 3. This<br>pin also selects the low bid to the 12C address and is latched upon the rising edge of the EN pin.<br>MUTE_CLT has an internal 5µA pulldown.           16         IN-         Common Audio Negative Input. IN- has 5kΩ of input resistance. Bypass to analog ground with 2µF<br>or 4 x CIN_+.           17         GND         Analog Ground           18         VDD         SV Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor of at least<br>0.47µF to IN0+.           20         IN1+         Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN1+.           21         REF         2.2V Reference Output. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN3+.           23         IN3+         Channel 3 Audio Input. IN2+ has                                                                                                                            | 6   | CLO             |                                                                                                                                                                                                                                                                                                                 |

| 9-12,<br>37-40, 43         PGND         Audio Output Power Ground           13         OUT2+         Channel 2 Power Amplifier Positive Output           14         OUT2-         Channel 2 Power Amplifier Negative Output           15         MUTE_CL1         Mute Input or Active-Low Open-Drain Clip 1 Output. MUTE_CLT is configurable as a mute input or<br>as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute<br>all four outputs. As an output. MUTE_CL1 provides Clipping indication for outputs 2 and 3. This<br>pin also selects the low bit of the I/2 address and is latched upon the rising edge of the EN pin.<br>MUTE_CL1 has an internal SµA puldown.           16         IN-         Common Audio Negative Input. IN- has 5kΩ of input resistance. Bypass to analog ground with 2µF<br>or 4 x ClN_+.           17         GND         Analog Ground           18         VDD         SV Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. Vpp<br>provides power to the analog and digital circuitry.           19         IN0+         Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN1+.           21         REF         2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.           22         IN3+         Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN3+.           23         IN3+         Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of a                                                                               | 7   | OUT3+           | Channel 3 Power Amplifier Positive Output                                                                                                                                                                                                                                                                       |

| 37-40, 43     PGND     Audio Output Power Ground       13     OUT2+     Channel 2 Power Amplifier Positive Output       14     OUT2-     Channel 2 Power Amplifier Positive Output       15     MUTE_CL1     Mute Input or Active-Low Open-Drain Clip 1 Output. MUTE_CL1 is configurable as a mute input or as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute all four outputs. As an output, MUTE_CLT provides Clipping indication for outputs 2 and 3. This pin also selects the low bit of the I <sup>2</sup> C address and is latched upon the rising edge of the EN pin. MUTE_CL1 has an internal SµA pulldown.       16     IN-     Common Audio Negative Input. IN- has SkΩ of input resistance. Bypass to analog ground with 2µF or 4 x ClN_+.       17     GND     Analog Ground       18     VpD     SV Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. VpD provides power to the analog and digital circuitry.       19     IN0+     Channel 0 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN0+.       20     IN1+     Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN3+.       21     REF     2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.       23     IN3+     Channel 2 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN3+.       24     SYNC     Sync I/O.1 m aster mode, SYNC outputs a clock signal that is synchronized to that of the mo                                                                                         | 8   | OUT3-           | Channel 3 Power Amplifier Negative Output                                                                                                                                                                                                                                                                       |

| 14       OUT2-       Channel 2 Power Amplifier Negative Output         15       MUTE_CL1       Mute Input or Active-Low Open-Drain Clip 1 Output. MUTE_CL1 is configurable as a mute input or as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute all four outputs. As an output, MUTE_CL T provides clipping indication for outputs 2 and 3. This pin also selects the low bit of the I/C address and is latched upon the rising edge of the EN pin. MUTE_CLT has an internal 5μA pulldown.         16       IN-       Common Audio Negative Input. IN- has 5kΩ of input resistance. Bypass to analog ground with 2μF or 4 x ClN_+.         17       GND       Analog Ground         18       VDD       5V Analog Power-Supply Input. Bypass with a 2.2μF or larger ceramic capacitor to GND. Vpp provides power to the analog and digital circuitry.         19       IN0+       Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47μF to IN0+.         20       IN1+       Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47μF to IN1+.         21       REF       2.2V Reference Output. Bypass REF to GND with a 1μF ceramic capacitor.         22       IN2+       Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47μF to IN3+.         23       IN3+       Channel 3 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47μF to IN3+.         26       SYNC <td< td=""><td></td><td>PGND</td><td>Audio Output Power Ground</td></td<>                                              |     | PGND            | Audio Output Power Ground                                                                                                                                                                                                                                                                                       |

| Mute Input or Active-Low Open-Drain Clip 1 Output. MUTE_CL1 is configurable as a mute input or<br>as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute<br>all four outputs. As an output, MUTE_CL1 provides clipping indication for outputs 2 and 3. This<br>pin also selects the low bit of the I2C address and is latched upon the rising edge of the EN pin.<br>MUTE_CL1 has an internal 5µA pulldown.           16         IN-         Common Audio Negative Input. IN- has 5kΩ of input resistance. Bypass to analog ground with 2µF<br>or 4 x Cln_++.           17         GND         Analog Ground           18         VpD         SV Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. VpD<br>provides power to the analog and digital circuitry.           19         IN+         Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN0+.           20         IN1+         Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN0+.           21         REF         2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.           22         IN2+         Channel 3 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN2+.           23         IN3+         Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN2+.           26         SYNC         Symc I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the<br>modulator. In slave m           | 13  | OUT2+           | Channel 2 Power Amplifier Positive Output                                                                                                                                                                                                                                                                       |

| 15       Autre_CLT       as an open-drain clip indicator output. When configured as an input, drive MUTE_CLT low to mute all four outputs. As an output, MUTE_CLT provides clippin glidication for outputs 2 and 3. This pin also selects the low bit of the I/C address and is latched upon the rising edge of the EN pin. MUTE_CLT has an internal 5µA pulldown.         16       IN-       Common Audio Negative Input. IN- has 5kΩ of input resistance. Bypass to analog ground with 2µF or 4 x CIN_+.         17       GND       Analog Ground         18       VpD       SV Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. VpD provides power to the analog and digital circuitry.         19       IN0+       Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN0+.         20       IN1+       Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN1+.         21       REF       2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.         22       IN2+       Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN2+.         23       IN3+       Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN3+.         24       SYNC       Sync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator. <t< td=""><td>14</td><td>OUT2-</td><td>Channel 2 Power Amplifier Negative Output</td></t<> | 14  | OUT2-           | Channel 2 Power Amplifier Negative Output                                                                                                                                                                                                                                                                       |

| 16       IN-       or 4 x CIN_+.         17       GND       Analog Ground         18       VpD       5V Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. VpD provides power to the analog and digital circuitry.         19       IN0+       Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN0+.         20       IN1+       Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN1+.         21       REF       2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.         22       IN2+       Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN2+.         23       IN3+       Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN3+.         26       SYNC       Sync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the modulator. In slave mode, SYNC bis a clock input and serves as the clock source for the modulator.         27       EN       Enable Input. Connect EN to Vpp for normal operation. Connect EN to GND to place the device in a low-power mode. There is an internal 10µA pulldown on EN.         28       SCL       I/C Serial-Clock Input         29       SDA       I/C Serial-Clock Input         30       FB1-       Output 1 Negative Feedback. Connect t                                                                                                                                                                                                          | 15  | MUTE_CL1        | as an open-drain clip indicator output. When configured as an input, drive MUTE_CL1 low to mute all four outputs. As an output, MUTE_CL1 provides clipping indication for outputs 2 and 3. This pin also selects the low bit of the I <sup>2</sup> C address and is latched upon the rising edge of the EN pin. |

| 18         VDD         5V Analog Power-Supply Input. Bypass with a 2.2µF or larger ceramic capacitor to GND. VDD provides power to the analog and digital circuitry.           19         IN0+         Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN0+.           20         IN1+         Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN1+.           21         REF         2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.           22         IN2+         Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN2+.           23         IN3+         Channel 3 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN2+.           26         SYNC         Sync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.           27         EN         Enable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a low-power mode. There is an internal 10µA pulldown on EN.           28         SCL         I²C Serial-Data Input and Output           30         FB1-         Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.           31         FB1+         Output 1 Negative Feedback. Connect to the LC filter's negative                                                                                                           | 16  | IN-             |                                                                                                                                                                                                                                                                                                                 |

| 18VDDprovides power to the analog and digital circuitry.19IN0+Channel 0 Audio Input. IN0+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN0+.20IN1+Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN1+.21REF2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.22IN2+Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN2+.23IN3+Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47µF to IN3+.26SYNCSync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the<br>modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.27ENEnable Input. Connect EN to VDp for normal operation. Connect EN to GND to place the device in a<br>low-power mode. There is an internal 10µA pulldown on EN.28SCLI²C Serial-Dota Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.31FB1+Output 1 Positive Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                 | 17  | GND             | Analog Ground                                                                                                                                                                                                                                                                                                   |

| 19IN0+0.47μF to IN0+.20IN1+Channel 1 Audio Input. IN1+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47μF to IN1+.21REF2.2V Reference Output. Bypass REF to GND with a 1μF ceramic capacitor.22IN2+Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47μF to IN2+.23IN3+Channel 3 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47μF to IN2+.26SYNCSync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the<br>modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.27ENEnable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a<br>low-power mode. There is an internal 10μA pulldown on EN.28SCLI²C Serial-Clock Input29SDAI²C Serial-Data Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.31FB1+Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18  | V <sub>DD</sub> |                                                                                                                                                                                                                                                                                                                 |

| 20IN1+0.47μF to IN1+.21REF2.2V Reference Output. Bypass REF to GND with a 1μF ceramic capacitor.22IN2+Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47μF to IN2+.23IN3+Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47μF to IN3+.26SYNCSync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the<br>modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.27ENEnable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a<br>low-power mode. There is an internal 10μA pulldown on EN.28SCLIPC Serial-Clock Input29SDAIPC Serial-Data Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.31FB1+Output 1 Positive Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19  | IN0+            |                                                                                                                                                                                                                                                                                                                 |

| 22       IN2+       Channel 2 Audio Input. IN2+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN2+.         23       IN3+       Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least 0.47µF to IN3+.         26       SYNC       Sync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.         27       EN       Enable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a low-power mode. There is an internal 10µA pulldown on EN.         28       SCL       I²C Serial-Clock Input         29       SDA       I²C Serial-Data Input and Output         30       FB1-       Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.         31       FB1+       Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.         32       FB0-       Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20  | IN1+            |                                                                                                                                                                                                                                                                                                                 |

| 22IN2+0.47μF to IN2+.23IN3+Channel 3 Audio Input. IN3+ has 20kΩ of input resistance. Connect a series capacitor of at least<br>0.47μF to IN3+.26SYNCSync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the<br>modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.27ENEnable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a<br>low-power mode. There is an internal 10μA pulldown on EN.28SCLI²C Serial-Clock Input29SDAI²C Serial-Data Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21  | REF             | 2.2V Reference Output. Bypass REF to GND with a 1µF ceramic capacitor.                                                                                                                                                                                                                                          |

| 23IN3+0.47μF to IN3+.26SYNCSync I/O. In master mode, SYNC outputs a clock signal that is synchronized to that of the<br>modulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.27ENEnable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a<br>low-power mode. There is an internal 10μA pulldown on EN.28SCLI²C Serial-Clock Input29SDAI²C Serial-Data Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.31FB1+Output 1 Positive Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22  | IN2+            |                                                                                                                                                                                                                                                                                                                 |

| 26SYNCmodulator. In slave mode, SYNC is a clock input and serves as the clock source for the modulator.27ENEnable Input. Connect EN to VDD for normal operation. Connect EN to GND to place the device in a<br>low-power mode. There is an internal 10µA pulldown on EN.28SCLI²C Serial-Clock Input29SDAI²C Serial-Data Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.31FB1+Output 1 Positive Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23  | IN3+            |                                                                                                                                                                                                                                                                                                                 |

| 27ENlow-power mode. There is an internal 10μA pulldown on EN.28SCLI²C Serial-Clock Input29SDAI²C Serial-Data Input and Output30FB1-Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.31FB1+Output 1 Positive Feedback. Connect to the LC filter's positive output through a 150Ω ±1% resistor.32FB0-Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1%<br>resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26  | SYNC            |                                                                                                                                                                                                                                                                                                                 |

| 29       SDA       I²C Serial-Data Input and Output         30       FB1-       Output 1 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.         31       FB1+       Output 1 Positive Feedback. Connect to the LC filter's positive output through a 150Ω ±1% resistor.         32       FB0-       Output 0 Negative Feedback. Connect to the LC filter's negative output through a 150Ω ±1% resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27  | EN              |                                                                                                                                                                                                                                                                                                                 |