Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

The MAX1361/MAX1362 low-power, 10-bit, 4-channel, analog-to-digital converters (ADCs) feature a digitally programmable window comparator with an interrupt output for automatic system-monitoring applications. Once configured, monitor mode automatically asserts an interrupt when any analog input exceeds the programmed upper or lower thresholds, without interaction to the host. The MAX1361/MAX1362 respond to the SMBus™ alert, allowing quick identification of the alarming device on a shared interrupt. A programmable delay between monitoring intervals lowers power consumption at reduced monitoring rates.

In addition, the MAX1361/MAX1362 integrate an internal voltage reference, a clock, and a 1.7MHz, high-speed, I<sup>2</sup>C-compatible, 2-wire, serial interface. The optimized interface allows a maximum conversion rate of 94.4ksps in normal mode while reading back the conversion results. Each of the four analog inputs is configurable for single-ended or fully differential operation and unipolar or bipolar operation. Two scan modes utilize on-chip random access memory (RAM) to allow eight conversions of a selected channel or scanning of a group of channels to reduce interface overhead.

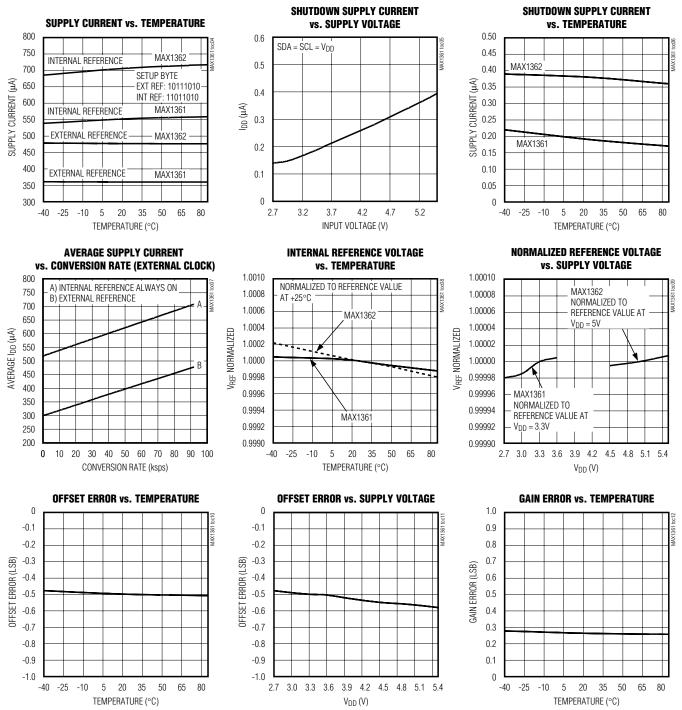

These devices operate from a single 2.7V to 3.6V (MAX1361) or 4.5V to 5.5V (MAX1362) supply and require only 436µA at the maximum sampling rate of 150ksps in monitor mode and 670µA at the maximum sampling rate of 94.4ksps. AutoShutdown™ powers down the devices between conversions, reducing supply current to less than 0.5µA when idle.

The full-scale analog-input range is determined by the internal reference or by an externally applied reference voltage ranging from 1V to VDD. The MAX1361 features a 2.048V internal reference, and the MAX1362 features a 4.096V internal reference.

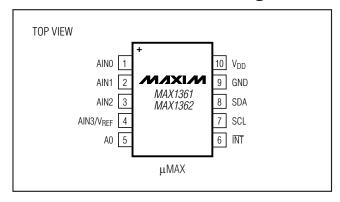

The MAX1361/MAX1362 are available in a 10-pin µMAX® package and are specified over the extended -40°C to +85°C temperature range. For 12-bit applications, refer to the pin-compatible MAX1363/MAX1364 data sheet.

#### **Applications**

System Monitoring/Supervision Servers/Workstations High Reliability Power Supplies Medical Instrumentation

## Features

Monitor Mode

**Programmable Lower/Upper Trip Threshold Alarm-Status Register Records Fault Events SMBus Alert Response Programmable Sampling Intervals**

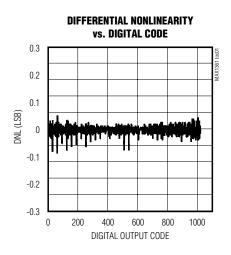

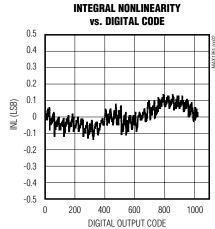

- ♦ 10-Bit I<sup>2</sup>C-Compatible ADC ±1 LSB INL, ±1 LSB DNL

- ♦ 4-Channel Single-Ended or 2-Channel Fully **Differential Inputs**

- ♦ Software Programmable Bipolar/Unipolar Conversions

- **♦** Fast Sampling Rate 94.4ksps While Continuously Reading Conversions 150ksps in Monitor Mode

- ♦ High-Speed I<sup>2</sup>C-Compatible Serial Interface 100kHz/400kHz Standard/Fast Mode Up to 1.7MHz High-Speed Mode 4 Available I<sup>2</sup>C Slave Addresses

- ♦ Single Supply 2.7V to 3.6V (MAX1361) 4.5V to 5.5V (MAX1362)

- **♦ Internal Reference** 2.048V (MAX1361) 4.096V (MAX1362)

- ♦ External Reference: 1V to V<sub>DD</sub>

- **♦ Low Power** 436µA in Monitor Mode (150ksps) 670µA at 94.4ksps 6µA at 1ksps 0.5µA in Power-Down Mode

- ♦ Small Package 10-Pin µMAX

SMBus is a trademark of Intel Corporation. AutoShutdown is a trademark of Maxim Integrated Products, Inc. µMAX is a registered trademark of Maxim Integrated Products, Inc.

Typical Operating Circuit and Pin Configuration appear at end of data sheet.

## **Ordering Information/Selector Guide**

| PART         | TEMP RANGE     | PIN-PACKAGE | I <sup>2</sup> C SLAVE ADDRESS | SUPPLY VOLTAGE (V) |

|--------------|----------------|-------------|--------------------------------|--------------------|

| MAX1361EUB+  | -40°C to +85°C | 10 μMAX     | 0110100/0110101                | 2.7 to 3.6         |

| MAX1361MEUB+ | -40°C to +85°C | 10 μMAX     | 0110110/0110111                | 2.7 to 3.6         |

+Denotes a lead(Pb)-free/RoHS-compliant package.

Ordering Information/Selector Guide continued at end of data sheet.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +6V                         | Operating Temperature Range40°C to +85°C |

|-----------------------------------------------------------|------------------------------------------|

| AIN0-AIN3, A0, REF to GND0.3V to (V <sub>DD</sub> + 0.3V) | Junction Temperature+150°C               |

| SDA, SCL, INT to GND0.3V to +6V                           | Storage Temperature Range60°C to +150°C  |

| Maximum Current Into Any Pin±50mA                         | Lead Temperature (soldering, 10s)+300°C  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)     | Soldering Temperature (reflow)+260°C     |

| 10-Pin µMAX (derate 8.6mW/°C above +70°C)689.7mW          |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX1361),\ V_{DD}=4.5V\ to\ 5.5V\ (MAX1362),\ V_{REF}=2.048V\ (MAX1361),\ V_{REF}=4.096V\ (MAX1362),\ C_{REF}=0.1\mu F,\ f_{SCL}=1.7MHz,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                               | SYMBOL        | CONDITIONS                                                                      | MIN  | TYP  | MAX  | UNITS  |

|-----------------------------------------|---------------|---------------------------------------------------------------------------------|------|------|------|--------|

| DC ACCURACY (fSAMPLE = 94.4)            | ksps) (Note 1 | )                                                                               | •    |      |      | •      |

| Resolution                              |               |                                                                                 | 10   |      |      | Bits   |

| Relative Accuracy                       | INL           | (Note 2)                                                                        |      |      | ±1   | LSB    |

| Differential Nonlinearity               | DNL           | No missing codes                                                                |      |      | ±1   | LSB    |

| Offset Error                            |               |                                                                                 |      |      | ±1   | LSB    |

| Offset-Error Temperature<br>Coefficient |               | Relative to FSR                                                                 |      | 0.3  |      | ppm/°C |

| Gain Error                              |               | (Note 3)                                                                        |      |      | ±1   | LSB    |

| Gain Temperature Coefficient            |               | Relative to FSR                                                                 |      | 0.3  |      | ppm/°C |

| Channel-to-Channel Offset<br>Matching   |               |                                                                                 |      | ±0.1 |      | LSB    |

| Channel-to-Channel Gain<br>Matching     |               |                                                                                 |      | ±0.1 |      | LSB    |

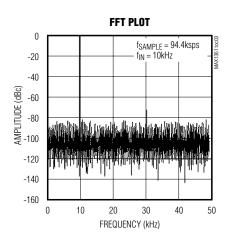

| DYNAMIC PERFORMANCE (fings              | SINE-WAVE) =  | 10kHz, V <sub>IN(P-P)</sub> = V <sub>REF</sub> , f <sub>SAMPLE</sub> = 94.4ksps | s)   |      |      | •      |

| Signal-to-Noise Plus Distortion         | SINAD         |                                                                                 |      | 60   |      | dB     |

| Total Harmonic Distortion               | THD           | Up to the 5th harmonic                                                          |      | -70  |      | dB     |

| Spurious-Free Dynamic Range             | SFDR          |                                                                                 |      | 70   |      | dB     |

| Full-Power Bandwidth                    |               | SINAD > 57dB                                                                    |      | 3.0  |      | MHz    |

| Full-Linear Bandwidth                   |               | -3dB point                                                                      |      | 5.0  |      | MHz    |

| CONVERSION RATE                         |               |                                                                                 |      |      |      |        |

| Conversion Time (Note 4)                | tconv         | Internal clock                                                                  |      |      | 6.8  |        |

| Conversion Time (Note 4)                | ICONV         | External clock                                                                  | 10.6 |      |      | μs     |

|                                         |               | Internal clock, SCAN[1:0] = 01                                                  |      | 53   |      |        |

| Throughput Rate (Note 5)                | fSAMPLE       | External clock                                                                  |      |      | 94.4 | ksps   |

|                                         |               | Monitor mode, SCAN[1:0] = 10                                                    |      |      | 150  |        |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX1361),\ V_{DD}=4.5V\ to\ 5.5V\ (MAX1362),\ V_{REF}=2.048V\ (MAX1361),\ V_{REF}=4.096V\ (MAX1362),\ C_{REF}=0.1\mu F,\ f_{SCL}=1.7MHz,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                                    | SYMBOL                   |                         | CONDITIONS                                             | MIN                  | TYP      | MAX                   | UNITS  |

|----------------------------------------------|--------------------------|-------------------------|--------------------------------------------------------|----------------------|----------|-----------------------|--------|

| Track/Hold Acquisition Time                  |                          |                         |                                                        | 800                  |          |                       | ns     |

| Internal Clock Frequency                     |                          |                         |                                                        |                      | 2.8      |                       | MHz    |

| Asserting Delevi (Nets C)                    |                          | External clock,         | fast mode                                              |                      | 60       |                       |        |

| Aperture Delay (Note 6)                      | t <sub>AD</sub>          | External clock,         | high-speed mode                                        |                      | 30       |                       | ns     |

| ANALOG INPUT (AIN0-AIN3)                     | •                        |                         |                                                        |                      |          |                       |        |

| Input Voltage Range, Single-                 |                          | Unipolar                |                                                        | 0                    |          | V <sub>REF</sub>      | V      |

| Ended and Differential (Note 7)              |                          | Bipolar                 |                                                        | -V <sub>REF</sub> /2 |          | +V <sub>REF</sub> /2  | V      |

| Input Multiplexer Leakage<br>Current         |                          | ON/OFF leakag           | ge current, V <sub>AIN</sub> _ = 0V or V <sub>DD</sub> |                      | ±0.01    | ±1                    | μΑ     |

| Input Capacitance                            | CIN                      |                         |                                                        |                      | 22       |                       | pF     |

| INTERNAL REFERENCE (Note 8)                  |                          |                         |                                                        |                      |          |                       |        |

| Reference Voltage                            | V <sub>REF</sub>         | T <sub>A</sub> = +25°C  | MAX1361                                                | 2.027                | 2.048    | 2.068                 | V      |

| Therefore voltage                            | VKEF                     | 1A = +23 C              | MAX1362                                                | 4.055                | 4.096    | 4.137                 | V      |

| Reference-Voltage Temperature<br>Coefficient | TCV <sub>REF</sub>       |                         |                                                        |                      | 25       |                       | ppm/°C |

| REF Short-Circuit Current                    |                          |                         |                                                        |                      |          | 2                     | mA     |

| REF Source Impedance                         |                          |                         |                                                        |                      | 1.5      |                       | kΩ     |

| EXTERNAL REFERENCE                           |                          | •                       |                                                        |                      |          |                       |        |

| REF Input Voltage Range                      | V <sub>REF</sub>         | (Note 9)                |                                                        | 1                    |          | V <sub>DD</sub>       | V      |

| REF Input Current                            | I <sub>REF</sub>         | fsample = 94.4          | ksps                                                   |                      |          | 40                    | μΑ     |

| DIGITAL INPUTS/OUTPUTS (SCL                  | ., SDA, A <sub>0</sub> ) |                         |                                                        |                      |          |                       |        |

| Input High Voltage                           | VIH                      |                         |                                                        | 0.7 x V <sub>D</sub> | D        |                       | V      |

| Input Low Voltage                            | VIL                      |                         |                                                        |                      |          | 0.3 x V <sub>DD</sub> | V      |

| Input Hysteresis                             | Vi n co T                | SCL, SDA                | 0.1 x V <sub>DD</sub>                                  |                      |          | V                     |        |

| Imput Hysteresis                             | VHYST                    | Ao                      |                                                        | 0.1 x                | $V_{DD}$ | \ \ \                 |        |

| Input Current                                | I <sub>IN</sub>          |                         |                                                        |                      |          | ±10                   | μΑ     |

| Input Capacitance                            | CIN                      |                         |                                                        |                      |          | 15                    | pF     |

| Output Low Voltage                           | VoL                      | I <sub>SINK</sub> = 3mA |                                                        |                      |          | 0.4                   | V      |

| INT OUTPUT                                   |                          |                         |                                                        |                      |          |                       |        |

| Output Low Voltage                           |                          | I <sub>SINK</sub> = 3mA |                                                        |                      |          | 0.4                   | V      |

| INT Leakage Current                          |                          | No faults detec         | eted                                                   |                      |          | ±10                   | μΑ     |

| Output Capacitance                           |                          |                         |                                                        |                      | 15       |                       | pF     |

| POWER REQUIREMENTS                           |                          |                         |                                                        |                      |          |                       |        |

| Supply Voltage                               | V <sub>DD</sub>          | MAX1361                 |                                                        | 2.7                  |          | 3.6                   | V      |

| Cappiy Voltage                               | עט י                     | MAX1362                 |                                                        | 4.5                  |          | 5.5                   | v      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX1361),\ V_{DD}=4.5V\ to\ 5.5V\ (MAX1362),\ V_{REF}=2.048V\ (MAX1361),\ V_{REF}=4.096V\ (MAX1362),\ C_{REF}=0.1\mu F,\ f_{SCL}=1.7MHz,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                    | SYMBOL | CONDITIONS                                                       |                                          |                    | MIN | TYP   | MAX  | UNITS |  |

|------------------------------|--------|------------------------------------------------------------------|------------------------------------------|--------------------|-----|-------|------|-------|--|

|                              |        |                                                                  | fsample = 150ksps,                       | Internal reference |     | 660   | 1600 |       |  |

|                              |        |                                                                  | monitor mode (Note 10)                   | External reference |     | 436   | 1350 |       |  |

|                              |        |                                                                  | fsample =                                | Internal reference |     | 900   | 1150 |       |  |

|                              |        |                                                                  | 94.4ksps, external clock                 | External reference |     | 670   | 900  |       |  |

|                              |        | MANAGO                                                           | fsample =                                | Internal reference |     | 530   |      |       |  |

|                              |        | MAX1361                                                          | 40ksps, internal clock                   | External reference |     | 230   |      |       |  |

|                              |        |                                                                  | fSAMPLE =                                | Internal reference |     | 380   |      |       |  |

|                              |        |                                                                  | 10ksps,<br>internal clock                | External reference |     | 60    |      |       |  |

| Supply Current               | lDD    |                                                                  | fSAMPLE = 1ksps,                         | Internal reference |     | 330   |      |       |  |

|                              |        |                                                                  | internal clock                           | External reference |     | 6     |      | μA    |  |

|                              |        | fSAMPLE = 150ksps, monitor m (Note10)  fSAMPLE = 94.4ksps, clock | fsample = 150ksps,                       | Internal reference |     | 666   | 1600 | μΑ    |  |

|                              |        |                                                                  | monitor mode<br>(Note10)                 | External reference |     | 436   | 1350 |       |  |

|                              |        |                                                                  | f <sub>SAMPLE</sub> = 94.4ksps, external | Internal reference |     | 900   | 1150 |       |  |

|                              |        |                                                                  |                                          | External reference |     | 670   | 900  |       |  |

|                              |        |                                                                  | fsample = 40ksps,                        | Internal reference |     | 530   |      |       |  |

|                              |        | IVIAX 1302                                                       | internal clock                           | External reference |     | 230   |      |       |  |

|                              |        |                                                                  | fSAMPLE = 10ksps, internal               | Internal reference |     | 380   |      |       |  |

|                              |        |                                                                  | clock                                    | External reference |     | 60    |      |       |  |

|                              |        |                                                                  | fSAMPLE = 1ksps,                         | Internal reference |     | 330   |      |       |  |

|                              |        |                                                                  | internal clock                           | External reference |     | 6     |      |       |  |

| Shutdown Current             |        | Internal reference on                                            |                                          |                    |     | 330   |      | μΑ    |  |

|                              |        | Internal refe                                                    |                                          | 0.5                | 10  |       |      |       |  |

| Power-Supply Rejection Ratio | PSRR   | Full-scale i                                                     | nput (Note 11)                           |                    |     | ±0.01 | ±0.5 | LSB/V |  |

\_\_\_\_\_\_*NIXIM*

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX1361),\ V_{DD}=4.5V\ to\ 5.5V\ (MAX1362),\ V_{REF}=2.048V\ (MAX1361),\ V_{REF}=4.096V\ (MAX1362),\ C_{REF}=0.1\mu F,\ f_{SCL}=1.7MHz,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                                                        | SYMBOL            | CONDITIONS                                             | MIN     | TYP N | ΙΑΧ | UNITS |

|------------------------------------------------------------------|-------------------|--------------------------------------------------------|---------|-------|-----|-------|

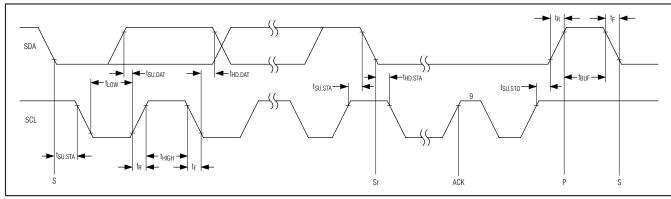

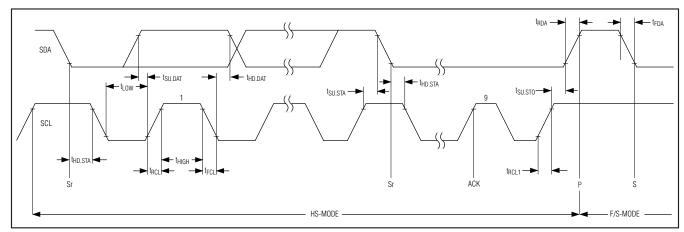

| TIMING CHARACTERISTICS FOR                                       | FAST MOD          | E (Figures 1a, 2)                                      | •       |       |     |       |

| Serial Clock Frequency                                           | f <sub>SCL</sub>  |                                                        |         |       | 400 | kHz   |

| Bus Free Time Between a<br>STOP (P) and a<br>START (S) Condition | tBUF              |                                                        | 1.3     |       |     | μs    |

| Hold Time for START (S)<br>Condition                             | tHD, STA          |                                                        | 0.6     |       |     | μs    |

| Low Period of the SCL Clock                                      | t <sub>LOW</sub>  |                                                        | 1.3     |       |     | μs    |

| High Period of the SCL Clock                                     | thigh             |                                                        | 0.6     |       |     | μs    |

| Setup Time for a Repeated START Condition (Sr)                   | tsu, sta          |                                                        | 0.6     |       |     | μs    |

| Data Hold Time                                                   | thd, dat          |                                                        | 0       | (     | 900 | ns    |

| Data Setup Time                                                  | tsu, dat          |                                                        | 100     |       |     | ns    |

| Rise Time of Both SDA and SCL<br>Signals, Receiving              | t <sub>R</sub>    | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 0       |       | 300 | ns    |

| Fall Time of SDA Transmitting                                    | tϝ                | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 0       |       | 300 | ns    |

| Setup Time for STOP (P) Condition                                | tsu, sto          |                                                        | 0.6     |       |     | μs    |

| Capacitive Load for Each Bus Line                                | СВ                |                                                        |         | 2     | 400 | pF    |

| Pulse Width of Spike Suppressed                                  |                   |                                                        |         |       | 50  | ns    |

| TIMING CHARACTERISTICS FOR                                       | HIGH-SPEE         | ED MODE (C <sub>B</sub> = 400pF, Figures 1a, 2) (No    | ote 12) |       |     |       |

| Serial-Clock Frequency                                           | fsclh             | (Note 13)                                              |         |       | 1.7 | MHz   |

| Hold Time, Repeated START<br>Condition (Sr)                      | tHD, STA          |                                                        | 160     |       |     | ns    |

| Low Period of the SCL Clock                                      | tLOW              | (Note 13)                                              | 320     |       |     | ns    |

| High Period of the SCL Clock                                     | tHIGH             |                                                        | 120     |       |     | ns    |

| Setup Time for a Repeated<br>START Condition (Sr)                | tsu, sta          |                                                        | 160     |       |     | ns    |

| Data Hold Time                                                   | thd, dat          | (Note 14)                                              | 0       |       | 150 | ns    |

| Data Setup Time                                                  | tsu, dat          |                                                        | 10      |       |     | ns    |

| Rise Time of SCL Signal                                          | tRCL              | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 20      |       | 80  | ns    |

| Rise Time of SCL Signal After<br>Acknowledge Bit                 | t <sub>RCL1</sub> | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 20      |       | 160 | ns    |

| Fall Time of SCL Signal                                          | tFCL              | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 20      |       | 80  | ns    |

| Rise Time of SDA Signal                                          | trda              | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 20      |       | 160 | ns    |

| Fall Time of SDA Signal                                          | t <sub>FDA</sub>  | Measured from 0.3V <sub>DD</sub> to 0.7V <sub>DD</sub> | 20      |       | 160 | ns    |

| Setup Time for STOP (P) Condition                                | tsu, sto          |                                                        | 160     |       |     | ns    |

| Capacitive Load for Each Bus                                     | СВ                |                                                        |         | 4     | 400 | pF    |

| Pulse Width of Spike Suppressed                                  |                   |                                                        | 0       |       | 10  | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V\ (MAX1361),\ V_{DD}=4.5V\ to\ 5.5V\ (MAX1362),\ V_{REF}=2.048V\ (MAX1361),\ V_{REF}=4.096V\ (MAX1362),\ C_{REF}=0.1\mu F,\ f_{SCL}=1.7MHz,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

- Note 1: Devices configured for unipolar single-ended inputs.

- **Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after the gain and offset have been calibrated.

- Note 3: Offset nulled.

- **Note 4:** Conversion time is defined as the number of clock cycles needed for conversion multiplied by the clock period. Conversion time does not include acquisition time. SCL is the conversion clock in the external clock mode.

- **Note 5:** The throughput rate of the I<sup>2</sup>C bus is limited to 94.4ksps. The MAX1361/MAX1362 can perform conversions up to 150ksps in monitor mode when not reading back results on the I<sup>2</sup>C bus.

- Note 6: A filter on the SDA and SCL inputs suppresses noise spikes and delays the sampling instant.

- Note 7: The absolute input voltage range for the analog inputs (AIN0-AIN3) is from GND to V<sub>DD</sub>.

- Note 8: When the internal reference is configured to be available at AIN3/REF (SEL[2:1] = 11), decouple AIN3/REF to GND with a 0.01μF capacitor.

- Note 9: ADC performance is limited by the converter's noise floor, typically 300µV<sub>P-P</sub>.

- Note 10: Maximum conversion throughput in internal clock mode when the data is not clocked out.

- Note 11: For the MAX1361, PSRR is measured as

$$\frac{\left[ \left[ V_{FS}(3.6V) - V_{FS}(2.7V) \right] \times \frac{2^{N} - 1}{V_{REF}} \right]}{(3.6V - 2.7V)}$$

and for the MAX1362, PSRR is measured as

$$\[ V_{FS}(5.5V) - V_{FS}(4.5V) \times \frac{2^{N} - 1}{V_{REF}} \]$$

- **Note 12:**  $C_B$  = total capacitance of one bus line in pF.

- Note 13: fsci H must meet the minimum clock low time plus the rise/fall times.

- Note 14: A master device must provide a data hold time for SDA (referred to V<sub>IL</sub> of SCL) to bridge the undefined region of SCL's falling edge.

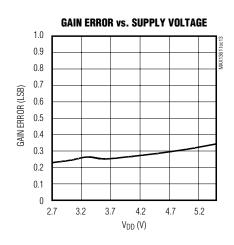

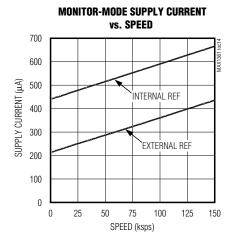

## **Typical Operating Characteristics**

$(V_{DD} = 3.3V \text{ (MAX1361)}, V_{DD} = 5V \text{ (MAX1362)}, f_{SCL} = 1.7MHz, external clock, f_{SAMPLE} = 94.4ksps, single-ended, unipolar, T_A = +25°C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{DD} = 3.3V \text{ (MAX1361)}, V_{DD} = 5V \text{ (MAX1362)}, f_{SCL} = 1.7MHz, external clock, f_{SAMPLE} = 94.4ksps, single-ended, unipolar, T_A = +25°C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{DD} = 3.3V \text{ (MAX1361)}, V_{DD} = 5V \text{ (MAX1362)}, f_{SCL} = 1.7MHz, external clock, f_{SAMPLE} = 94.4ksps, single-ended, unipolar, T_A = +25°C, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME                  | FUNCTION                                                                               |

|-----|-----------------------|----------------------------------------------------------------------------------------|

| 1   | AIN0                  | Analog Input                                                                           |

| 2   | AIN1                  | Analog Input                                                                           |

| 3   | AIN2                  | Analog Input                                                                           |

| 4   | AIN3/V <sub>REF</sub> | Analog Input or Reference Input or Output. See Table 3.                                |

| 5   | A0                    | I <sup>2</sup> C Address Select Input. Connect to V <sub>DD</sub> or GND. See Table 1. |

| 6   | ĪNT                   | Active-Low, Open-Drain Interrupt Output                                                |

| 7   | SCL                   | I <sup>2</sup> C Clock Input                                                           |

| 8   | SDA                   | I <sup>2</sup> C Data Input/Output                                                     |

| 9   | GND                   | Ground                                                                                 |

| 10  | V <sub>DD</sub>       | Positive Supply Voltage. Bypass V <sub>DD</sub> to GND with a 0.1µF capacitor.         |

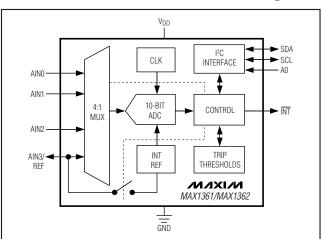

## **Functional Diagram**

Figure 1a. F/S-Mode 2-Wire Serial-Interface Timing

Figure 1b. HS-Mode 2-Wire Serial-Interface Timing

## **Detailed Description**

The MAX1361/MAX1362 4-channel ADCs use successive-approximation conversion techniques and fully differential input track/hold (T/H) circuitry to capture and convert analog signals to a serial 10-bit digital output. The MAX1361/MAX1362 feature a monitor mode with programmable trip thresholds and window comparator. The monitor function asserts an interrupt when any channel violates the programmed upper or lower thresholds. SMBus alert response allows the host microcontroller ( $\mu$ C) to quickly identify which device caused the interrupt. A programmable delay between monitoring intervals lowers power consumption at lower monitor rates.

The MAX1361/MAX1362 integrate an internal voltage reference and clock. The software configures the analog inputs for unipolar/bipolar and single-ended/fully differential operation. Integrated first-in/first-out (FIFO) allows conversion of all channels, or eight conversions

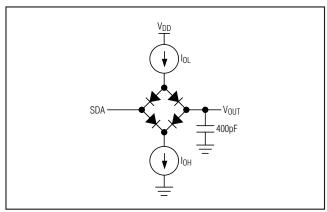

Figure 2. Load Circuits

on a selected channel to reduce interface overhead. An  $I^2C$ -compatible serial interface complies with standard, fast, and high-speed (1.7MHz) modes.

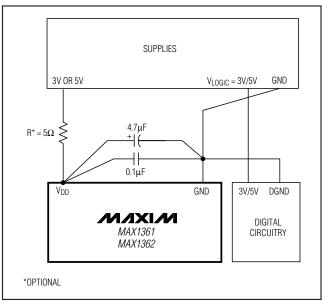

#### **Power Supply**

The MAX1361 (2.7V to 3.6V) and MAX1362 (4.5V to 5.5V) operate from a single supply and consume 670  $\mu$ A (typ) at sampling rates up to 94.4ksps and 436  $\mu$ A in monitor mode at 150ksps. The MAX1361 features a 2.048V internal reference and the MAX1362 features a 4.096V internal reference. All devices can be configured for use with an external reference from 1V to VDD. Bypass VDD to GND using a 0.1  $\mu$ F or greater ceramic capacitor for best performance.

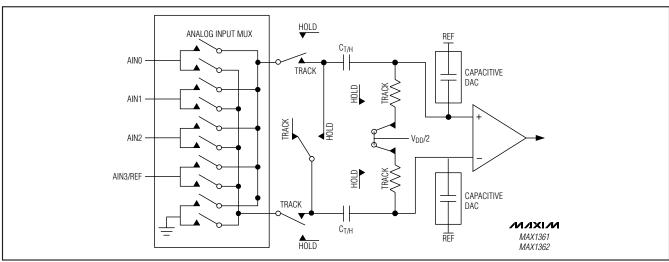

#### Analog Input and Track/Hold

The MAX1361/MAX1362 analog-input architecture contains an analog-input multiplexer (MUX), fully differential T/H, comparator, and a fully differential switched capacitive digital-to-analog converter (DAC). Figure 3 shows the equivalent input circuit for the MAX1361/MAX1362.

In single-ended mode, the analog-input MUX connects CT/H between the analog input selected by CS[3:0] and GND (see the *Configuration/Setup Bytes (Write Cycle)* section). In differential mode, the analog-input MUX connects CT/H to the plus and minus analog inputs selected by CS[3:0].

During the acquisition interval, the T/H switches are in the track position, and  $C_{T/H}$  charges to the analog-input signal. At the end of the acquisition interval, the T/H switches move to the hold position, retaining the charge on  $C_{T/H}$  as a stable sample of the input signal.

During the conversion, a switched capacitive DAC adjusts to restore the comparator input voltage to 0V within the limits of 10-bit resolution. This action requires

10 conversion clock cycles and is equivalent to transferring a charge of 11pF x ( $V_{\rm IN+}$  -  $V_{\rm IN-}$ ) from C<sub>T/H</sub> to the binary-weighted capacitive DAC, forming a digital representation of the analog-input signal.

Use a low source impedance to ensure an accurate sample. A source impedance of up to  $1.5 k\Omega$  does not significantly degrade sampling accuracy. For larger source impedances, connect a 100pF capacitor from the analog input to GND or buffer the input.

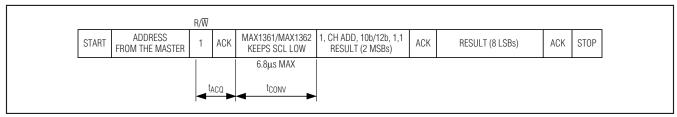

In internal clock mode, the T/H circuitry enters track mode on the eighth rising clock edge of the address byte (see the *Slave Address* section). The T/H circuitry enters hold mode on the falling clock edge of the acknowledge bit of the address byte (the ninth clock pulse). The conversions are then internally clocked, during which time the MAX1361/MAX1362 hold SCL low.

In external clock mode, the T/H circuitry enters track mode after a valid address on the rising edge of the clock during the read bit ( $R/\overline{W}=1$ , bit 8). Hold mode is entered on the rising edge of the second clock pulse during the shifting out of the 1st byte of the result. The next 10 clock cycles perform the conversions (see Figure 13).

The time required for the T/H circuitry to acquire an input signal is a function of the input sample capacitance. If the analog-input source impedance is high, the acquisition-time constant lengthens and more time must be allowed between conversions. The acquisition time (tACQ) is the minimum time needed for the signal to be acquired. It is calculated by:

tacq ≥ 7 x (Rsource + Rin) x Cin

Figure 3. Equivalent Input Circuit

10 \_\_\_\_\_\_ /I/XI/M

where Rsource is the analog-input source impedance,  $R_{IN}=2.5k\Omega$ , and  $C_{IN}=22pF$ . For internal clock mode,  $t_{ACQ}=1.5/f_{SCL}$ , and for external clock mode  $t_{ACQ}=2/f_{SCL}$ .

#### **Analog-Input Bandwidth**

The MAX1361/MAX1362 feature input-tracking circuitry with a 5MHz small-signal bandwidth. The 5MHz input bandwidth makes it possible to digitize high-speed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. To avoid high-frequency signals from aliasing into the frequency band of interest, use anti-aliasing filtering.

#### **Analog-Input Range and Protection**

Internal protection diodes clamp the analog inputs to  $V_{DD}$  and GND. These diodes allow the analog inputs to swing from ( $V_{GND}$  - 0.3V) to ( $V_{DD}$  + 0.3V) without causing damage to the device. For accurate conversions the inputs must remain within 50mV below GND or above  $V_{DD}$ .

#### Single-Ended/Differential Input

The SE/DIF of the configuration byte configures the MAX1361/MAX1362 analog-input circuitry for single-ended or differential input. In single-ended mode (SE/DIF = 1), the digital conversion results are the difference between the analog input selected by CS[3:0] and GND. In differential mode (SE/DIF = 0), the digital conversion results are the difference between the plus and the minus analog inputs selected by CS[3:0] (see Tables 5 and 6).

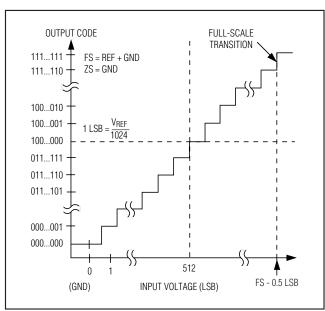

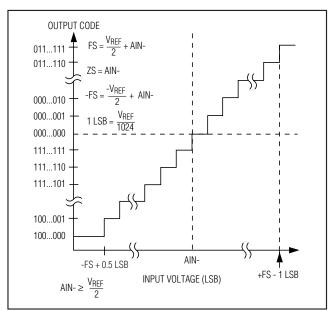

#### Unipolar/Bipolar

Unipolar mode sets the differential input range from 0 to VREF. A negative differential analog input in unipolar mode causes the digital output code to be zero. Selecting bipolar mode sets the differential input range to  $\pm V_{REF}/2$ . The digital output code is binary in unipolar mode and two's complement in bipolar mode. (See the *Transfer Functions* section.)

In single-ended mode the MAX1361/MAX1362 always operate in unipolar mode. The analog inputs are internally referenced to GND with a full-scale input range from 0 to  $V_{REF}$  (Table 7).

#### Reference

SEL[1:0] of the setup byte controls the reference and the AIN3/REF configuration. When AIN3/REF is configured as a reference input or reference output (SEL0 = 1), differential conversions on AIN3/REF appear as if AIN3/REF is connected to GND. A single-ended conversion in scan mode on AIN3/REF is ignored by an internal limiter that sets the highest available channel at AIN2 (Table 2).

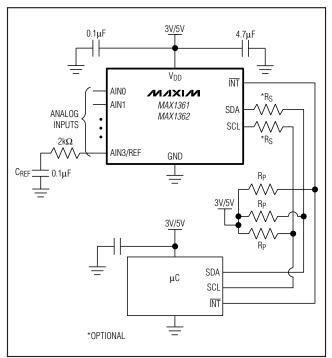

#### Internal Reference

The internal reference is 2.048V for the MAX1361 and 4.096V for the MAX1362. SEL0 of the setup byte controls whether AIN3/REF is used for an analog input or a reference (SEL0 = 0 selects AIN3/REF as AIN3, and SEL0 = 1 selects AIN3/REF as REF). Decouple AIN3/REF to GND with a 0.1µF capacitor and a  $2k\Omega$  resistor in series when AIN3/REF is configured as an internal reference output (SEL[1:0] = 11). See the Typical Operating Circuit. Once powered up, the reference remains on until reconfigured. Do not use the reference to supply current for external circuitry.

#### External Reference

The external reference ranges from 1V to V<sub>DD</sub>. For maximum conversion accuracy, the reference must deliver 40 $\mu$ A and have an impedance of 500 $\Omega$  or less. For noisy or high-output-impedance references, insert a 0.1 $\mu$ F bypass capacitor to GND as close to AIN3/REF as possible.

#### **Clock Modes**

The clock mode determines the conversion clock and the data acquisition and conversion time. The clock mode also affects the scan mode. The state of the setup byte's INT/EXT clock bit determines the clock mode. At power-up, the MAX1361/MAX1362 default to internal clock mode (INT/EXT clock = 0).

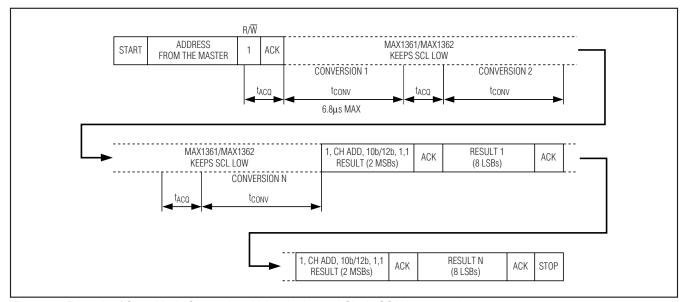

#### Internal Clock

See the Configuration/Setup Bytes (Write Cycle) section. In internal clock mode (INT/EXT clock = 0), the MAX1361/ MAX1362 use an internal oscillator for the conversion clock. The MAX1361/MAX1362 begin tracking the analog input after a valid address on the eighth rising edge of the clock. On the falling edge of the ninth clock, the analog signal is acquired and the conversion begins. While converting, the MAX1361/MAX1362 hold SCL low (clock stretching). After completing the conversion, the results are stored in internal memory. For scan-mode configurations with multiple conversions (see the Scan Modes section), all conversions happen in succession with each additional result stored in memory. Once all conversions are complete, the MAX1361/MAX1362 release SCL, allowing it to go high. The master can now clock the results out in the same order as the scan conversion.

The converted results are read back in a FIFO sequence. If AIN3/REF is configured as a reference input or output, AIN3/REF is excluded from multichannel scan. If reading continues past the final result stored in memory, the pointer wraps around and points to the first result. Only the current conversion results are read from memory. The MAX1361/MAX1362 must

be addressed with a read command to obtain new conversion results.

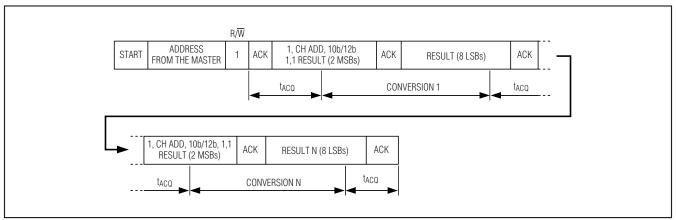

#### External Clock

See the *Configuration/Setup Bytes (Write Cycle)* section. When configured for external clock mode (INT/EXT = 1), the MAX1361/MAX1362 use SCL as the conversion clock. In external clock mode, the MAX1361/MAX1362 begin tracking the analog input on the eighth rising clock edge of a valid slave address byte. Two SCL clock cycles later, the analog signal is acquired and the conversion begins. Unlike internal clock mode, converted data is clocked out immediately in the format described in the *Reading a Conversion (Read Cycle)* section.

The device continuously converts input channels dictated by the scan mode until given a not acknowledge (NACK). There is no need to readdress the device with a read command to obtain new conversion results.

The conversion must complete in 1ms or droop on the T/H capacitor degrades conversion results. Use internal clock mode if the SCL clock period exceeds 60µs.

Use external clock mode for conversion rates from 40ksps to 94.4ksps. Use internal clock mode for conversions under 40ksps. Internal clock mode consumes less power. Monitor mode always uses internal clock mode regardless of conversion rate.

## \_Applications Section

#### **Power-On Reset**

The configuration and setup registers default to a single-ended, unipolar, single-channel conversion on AIN0 using the internal clock with  $V_{DD}$  as the reference and AIN3/REF configured as an analog input. The memory contents are unknown at power-up (see the <code>Software Description</code> section).

#### I<sup>2</sup>C-Compatible 2-Wire Serial Interface

The MAX1361/MAX1362 use an I<sup>2</sup>C-compatible 2-wire interface consisting of a serial-data line (SDA) and serial-clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX1361/MAX1362 and the master at rates up to 1.7MHz. The master (typically a microcontroller) initiates data transfer on the bus and generates the SCL signal to permit data transfer. The MAX1361/MAX1362 behave as I<sup>2</sup>C slave devices that transfer and receive data.

SDA and SCL must be pulled high for proper  $I^2C$  operation. This is typically done with pullup resistors (750 $\Omega$  or greater). Series resistors (Rs) are optional (see the *Typical Operating Circuit* section). The resistors protect the input architecture of the MAX1361/MAX1362 from

high voltage spikes on the bus lines and minimize crosstalk and undershoot of the bus signals.

One bit transfers during each SCL clock cycle. A minimum of nine clock cycles is required to transfer a byte in or out of the MAX1361/MAX1362 (8 bits and an ACK/NACK). The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the *START and STOP Conditions* section). Both SDA and SCL remain high when the bus is not busy.

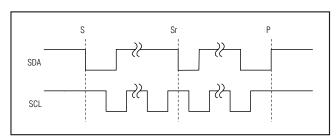

#### START and STOP Conditions

The master initiates a transmission with a START condition (S), which is a high-to-low transition on SDA while SCL is high. The master terminates a transmission with a STOP condition (P), which is a low-to-high transition on SDA while SCL is high (Figure 4). A repeated START condition (Sr) can be used in place of a STOP condition to leave the bus active and the mode unchanged (see the HS I<sup>2</sup>C Mode section).

#### Acknowledge and Not-Acknowledge Conditions

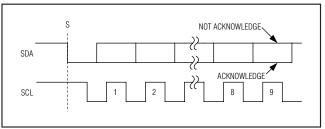

Data transfers are framed with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX1361/MAX1362 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse (Figure 5).

Figure 4. START and STOP Conditions

Figure 5. Acknowledge Bits

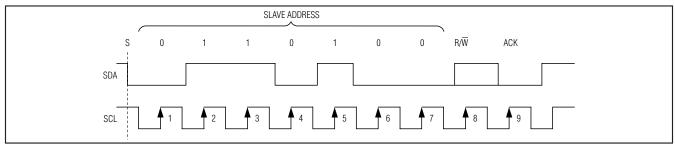

Figure 6. MAX1361/MAX1362 Slave Address Byte

Table 1. I<sup>2</sup>C Slave Selection Table

| A0 STATE | SUFFIX | ADDRESS |

|----------|--------|---------|

| Low      | EUB    | 0110100 |

| High     | EUB    | 0110101 |

| Low      | MEUB   | 0110110 |

| High     | MEUB   | 0110111 |

To generate a not-acknowledge condition, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse, and leaves SDA high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master reattempts communication at a later time.

#### Slave Address

The MAX1361/MAX1362 have a 7-bit I<sup>2</sup>C slave address. The slave address is selected using A0. The MAX1361/MAX1362 (EUB and MEUB) have 2 base address options, allowing up to 4 devices concurrently per I<sup>2</sup>C bus (see Table 1).

The MAX1361/MAX1362 continuously wait for a START condition followed by its slave address. When the device recognizes its slave address, it is ready to accept or send data depending on the  $R\overline{W}$  bit (Figure 6).

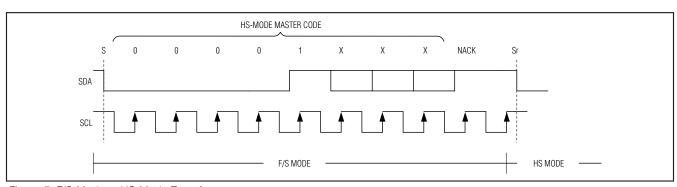

#### HS I<sup>2</sup>C Mode

At power-up, the MAX1361/MAX1362 bus timing is set for fast mode (F/S mode, up to 400kHz  $I^2$ C clock), which limits the conversion rate to approximately 22ksps. Switch to high-speed mode (HS mode, up to 1.7MHz  $I^2$ C clock) to achieve conversion rates up to 94.4ksps. The MAX1361/MAX1362 convert up to 150ksps in monitor mode, regardless of  $I^2$ C mode. If conversion results are unread,  $I^2$ C bandwidth limitations do not apply in monitor mode.

Select HS mode by addressing all devices on the bus with the HS-mode master code 0000 1XXX (X = don't care). After successfully receiving the HS-mode master code, the MAX1361/MAX1362 issue a NACK, allowing SDA to be pulled high for one clock cycle (Figure 7).

After the NACK, the MAX1361/MAX1362 operate in HS mode. Send a repeated START (Sr) followed by a slave address to initiate HS-mode communication. If the master generates a STOP condition the MAX1361/MAX1362 return to F/S mode. Use a repeated START condition (Sr) in place of a STOP condition to leave the bus active and the mode unchanged.

Figure 7. F/S-Mode to HS-Mode Transfer

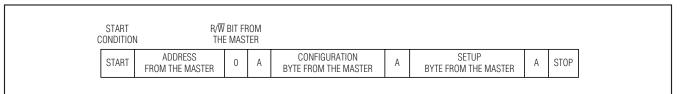

Figure 8. Example of Writing Setup and Control Bytes

| START<br>CONDITIO | DN             |                 | R/W BIT F |          |        |         |    | MONITO<br>ETUP B |      |   |                                  |   |            |

|-------------------|----------------|-----------------|-----------|----------|--------|---------|----|------------------|------|---|----------------------------------|---|------------|

| START             | ADD<br>FROM TH | RESS<br>E MASTE | ER 0      | А        |        | ETUP BY |    | 1                | А    |   | ARM RESET, SCAN<br>SPEED, INT_EN | А |            |

| СН                | ) LT [11:4]    | А               | CH O LT [ | 3:0]; UT | [11:8] | А       | СН | 0 UT [           | 7:0] | А | CH 1 LT [11:4]                   | А | • • • STOP |

Figure 9. Example of Extended Setup-Byte Writing

## Table 2. Configuration Byte Format\*

| BIT    | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7(MSB) | CONFIG | The configuration byte always starts with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6      | SCAN1  | SCAN1, SCAN0 = [0,0], scans from channel 0 to the upper channel chosen by CS1, CS0. SCAN1, SCAN0 = [0,1], converts a single channel chosen by CS1, CS0 eight times.                                                                                                                                                                                                                                                                                                                                                         |

| 5      | SCAN0  | SCAN1, SCAN0 = [1,0] monitor mode monitors from channel 0 to the upper channel chosen by CS1, CS0. SCAN1, SCAN0 = [1,1], single channel conversion for the channel is chosen by CS0, CS1.                                                                                                                                                                                                                                                                                                                                   |

| 4      | CS3    | CS2 CS2 — [1 1] anables readback of manitar mode setup data                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3      | CS2    | CS3, CS2 = [1,1] enables readback of monitor-mode setup data.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2      | CS1    | Selects the upper limit of the channel range used for the conversion sequence in scan modes SCAN = [0,0]                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1      | CS0    | and monitor modes SCAN = [1,0].  Selects the conversion channel when SCAN = [0,1] or when SCAN = [1,1].  (Tables 5 and 6)                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0      | SE/DIF | 1 = single-ended inputs. 0 = differential inputs. AIN0 and AIN1 form the first differential pair and AIN2 and AIN3 form the second differential pair. (See Tables 4 and 5.) Selects single-ended or differential conversions. In single-ended mode, input signal voltages are referenced to GND. In differential mode, the voltage difference between two channels is measured. When single-ended mode is used, the MAX1361/MAX1362 perform unipolar conversions regardless of the UNI/BIP bit in the setup byte. (Table 7) |

<sup>\*</sup>Power-on defaults: 0x01

### **Software Description**

#### **Configuration/Setup Bytes (Write Cycle)**

A write cycle begins with the bus master issuing a START condition followed by 7 address bits and a write bit (R/ $\overline{W}$  = 0). If the address byte is successfully received, the MAX1361/MAX1362 (slave) issue an ACK. The master then writes to the slave. If the most significant bit (MSB) is 1, the slave recognizes the received byte as the setup byte (Table 4). If the MSB is 0, the slave recognizes that byte as the configuration byte (Table 2). Write to the configuration byte before writing to the setup byte (Figure 8). If enabling  $\overline{\text{RESET}}$  in the setup byte, rewrite the configuration byte after writing the setup byte, since  $\overline{\text{RESET}}$  clears the contents of the configuration byte back to the power-up state.

When the monitor-setup bit of the setup byte is set to 1, writing extends up to 13 bytes to clock in monitor-setup data. Terminate writing monitor-setup data at any time by issuing a STOP or repeated START condition. If the slave receives a byte successfully, it issues an ACK (Figure 9).

**Note:** When operating in HS mode, a STOP condition returns the bus into F/S mode (see the  $HS\ l^2C\ Mode$  section).

#### **Automatic Shutdown**

AutoShutdown occurs between conversions when the MAX1361/MAX1362 are idle. When operating in external clock mode, issue a STOP, NACK, or repeated START condition to place the devices in idle mode and benefit from automatic shutdown. A STOP condition is not necessary in internal clock mode for automatic shutdown because power-down occurs once all conversions are complete. Shutdown reduces supply current to less than 0.5µA (external reference mode, typ) and 300µA (internal reference mode, typ).

When idle, the MAX1361/MAX1362 continuously wait for a START condition followed by their slave address. Upon reading a valid address byte, the MAX1361/MAX1362 power up. The internal reference requires 10ms to wake up. Therefore, power up the internal reference 10ms prior to conversion or leave the reference continuously powered. Wake-up is transparent when using an external reference or VDD as the reference.

Automatic shutdown results in dramatic power savings, particularly at slow conversion rates with internal clock. For example, using an external reference at a conversion rate of 10ksps, the average supply current for the MAX1361 is 60 $\mu$ A (typ) and drops to 6 $\mu$ A (typ) at 1ksps. At 0.1ksps, the average supply current is just 1 $\mu$ A. Table 3 shows AIN3/REF configuration and reference power-down state.

#### Scan Modes

SCAN1 and SCAN0 of the configuration byte set the scan-mode configuration. When configuring AIN3/REF for reference input or output (SEL0 = 1), AIN3/REF is excluded from a multichannel scan. The scanned results write to memory in the same order as the conversion. Start a conversion sequence by initiating a read with the desired scan mode. Read the results from memory in the order they were converted (see the Reading a Conversion (Read Cycle) section).

Selecting channel scan mode [0,0] starts converting from channel 0 up to the channel chosen by CS1, CS0.

Selecting channel scan mode [0,1] converts the channel selected by CS1, CS0 eight times and returns eight consecutive results.

Selecting monitor mode [1,0] initiates a continuous conversion scan sequence from channel 0 to the channel selected by CS1, CS0. See the *Monitor Mode* section for more details.

Selecting channel scan mode [1,1] performs a single conversion on the channel selected by CS1, CS0 and returns the result.

Table 3. Reference Voltage and AIN3/REF Format

| SEL1 | SEL0 | INT REF<br>POWERDOWN | REFERENCE VOLTAGE  | AIN3/REF         | INTERNAL<br>REFERENCE STATE |

|------|------|----------------------|--------------------|------------------|-----------------------------|

| 0    | 0    | X                    | $V_{DD}$           | Analog input     | Always off                  |

| 0    | 1    | Х                    | External reference | Reference input  | Always off                  |

| 1    | 0    | 0                    | Internal reference | Analog input     | Always off                  |

| 1    | 0    | 1                    | Internal reference | Analog input     | Always on                   |

| 1    | 1    | 0                    | Internal reference | Reference output | Always off                  |

| 1    | 1    | 1                    | Internal reference | Reference output | Always on                   |

Table 4. Setup-Byte Format\*

| BIT     | NAME                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 (MSB) | Setup                 | Setup byte always starts with 1.                                                                                                                                                                                                                                                                                                                                                                           |

| 6       | REF/AIN SEL1          | When [0,0], REF/AIN3 = AIN3, REF = V <sub>DD</sub> . When [0,1], REF/AIN3 = REF, REF = external reference. When [1,0], REF/AIN3 = AIN3, REF = internal reference.                                                                                                                                                                                                                                          |

| 5       | REF/AIN SEL0          | When [1,1], REF/AIN3 = REF, REF = internal reference.  (Table 3)                                                                                                                                                                                                                                                                                                                                           |

| 4       | INT REF Power<br>Down | 1 = internal reference always powered up. 0 = internal reference always powered down. (Table 3)                                                                                                                                                                                                                                                                                                            |

| 3       | ĪNT/EXT Clock         | 0 = internal clock.<br>1 = external clock (MAX1361/MAX1362 use the SCL clock for conversions).                                                                                                                                                                                                                                                                                                             |

| 2       | ŪNĪ/BIP               | 0 = unipolar. 1 = bipolar. Selects unipolar or bipolar conversion mode. In unipolar mode, analog signal in 0 to V <sub>REF</sub> range can be converted. In differential bipolar mode, input signal can range from -V <sub>REF</sub> /2 to +V <sub>REF</sub> /2. When single-ended mode is chosen, the SE/DIF bit of configuration byte overrides UNI/BIP, and conversions are performed in unipolar mode. |

| 1       | Reset                 | 1 = no action.<br>0 = resets $\overline{\text{INT}}$ and configuration register. Setup register and channel trip thresholds are unaffected.                                                                                                                                                                                                                                                                |

| 0       | Monitor Setup         | 0 = no action. 1 = extends writing up to 13 bytes (104 bits) of alarm reset mask. Scans speed selection and alarm thresholds. See the <i>Configuring Monitor Mode</i> section.                                                                                                                                                                                                                             |

<sup>\*</sup>Power-on defaults: 0x82

## Table 5. Channel Selection in Single-Ended Mode (SE/DIF = 1)

| CS1 | CS0 | CH0 | CH1 | CH2 | СНЗ |

|-----|-----|-----|-----|-----|-----|

| 0   | 0   | +   |     |     |     |

| 0   | 1   |     | +   |     |     |

| 1   | 0   |     |     | +   |     |

| 1   | 1   |     |     |     | +   |

# Table 6. Channel Selection in Differential Mode ( $SE/\overline{DIF} = 0$ )

| CS1 | CS0 | CH0 | CH1 | CH2 | СНЗ |

|-----|-----|-----|-----|-----|-----|

| 0   | 0   | +   | ı   |     |     |

| 0   | 1   | -   | +   |     |     |

| 1   | 0   |     |     | +   | -   |

| 1   | 1   |     |     | ı   | +   |

## Table 7. SE/DIF and UNI/BIP Table

| SE/DIF | UNI/BIP | MODE                          |

|--------|---------|-------------------------------|

| 0      | 0       | Differential inputs, unipolar |

| 0      | 1       | Differential inputs, bipolar  |

| 1      | 0       | Single-ended inputs, unipolar |

| 1      | 1       | Single-ended inputs, unipolar |

#### Reading a Conversion (Read Cycle)

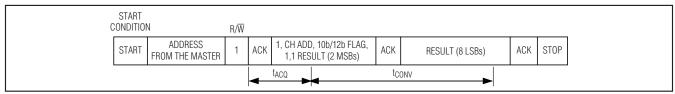

Initiate a read cycle to start a conversion sequence and to obtain conversion results. See the <code>Scan Modes</code> section for details on the channel-scan sequence. Read cycles begin with the bus master issuing a START condition followed by 7 address bits and a read bit ( $R/\overline{W}=1$ ). After successfully receiving the address byte, the MAX1361/MAX1362 (slave) issue an ACK. The master then reads from the slave. (See Figures 10–13.)

The result is transmitted in 2 bytes. The 1st byte consists of a leading 1 followed by a 2-bit binary channel address tag, a  $12/\overline{10}$  bit flag (0 for the MAX1361/MAX1362), 2 bits of 1s, the first 2 bits of the data result, and the expected ACK from the master. The 2nd byte

#### **Table 8. Data Format**

| HIGH | CH1 | СНО | 12/10              | HIGH | HIGH | DATA<br>(MSB) | D8  |     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |              |

|------|-----|-----|--------------------|------|------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------|

| 1    | 0/1 | 0/1 | 0 = 10b<br>1 = 12b | 1    | 1    | 0/1           | 0/1 | ACK | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | ACK/<br>NACK |

Figure 10. Example of Reading the Conversion Result—External Clock Mode

Figure 11. Example of a Single Conversion Using the Internal Clock, SCAN = 1,1

Figure 12. Example of Scan-Mode Conversions Using the Internal Clock, SCAN = 0,0 and 0,1

Figure 13. Example of Scan-Mode Conversions Using the External Clock, SCAN = 0,0 and 0,1

contains D7-D0. To read the next conversion result, issue an ACK. To stop reading, issue a NACK.

When the MAX1361/MAX1362 receive a NACK, they release SDA allowing the master to generate a STOP or a repeated START condition.

#### **Monitor Mode**

#### Monitor-Mode Overview

The MAX1361/MAX1362 automatically monitor up to four input channels. For systems with limited  $I^2C$  bandwidth, monitor mode allows the  $\mu C$  to set a window by programming lower and upper thresholds during initialization, and only intervening if the MAX1361/MAX1362 detect an alarm condition. This allows an interrupt-driven approach as an alternative to continuously polling the ADC with the  $\mu C$ . Monitor mode reduces processor overhead and conserves  $I^2C$  bandwidth.

The following shows an example of events in monitor mode:

- 1) Fault condition(s) detected, INT asserted.

- 2) Host  $\mu$ C services interrupt and send SMBus alert to identify the alarming device. The MAX1361/MAX1362 respond with the I<sup>2</sup>C slave address, pending arbitration rules. (See the *SMBus Alert* section.)

- 3) The MAX1361/MAX1362 release the INT.

- Host-µC reads the alarm-status register, latchedfault register, and current-conversion results to determine the alarming channel(s) and course of action.

- Host μC services alarm(s); adjusts system parameters as needed and/or adjust lower and upper thresholds.

- 6) Clears the alarm register. See the *Configuring Monitor Mode* section.

- 7) Monitor mode resumes.

- 8) If there is still an active fault, the device asserts INT again. See step 1.

Writing SCAN1 and SCAN0 bits = [1,0] in the configuration byte activates monitor mode. The MAX1361/MAX1362 scan from channels 0 up to the channel selected by [CS1:CS0] at a rate determined by the scan delay bits. The MAX1361/MAX1362 compare the conversion results with the lower and upper thresholds for each channel. When any conversion exceeds the threshold, the MAX1361/MAX1362 assert an interrupt by pulling  $\overline{\text{INT}}$  low (if enabled). The MAX1361/MAX1362 set the corresponding flag bit in the alarmstatus register and write conversion results to the latched-fault register to record the event causing the alarm condition.

INT active state is randomly delayed with respect to the conversion. Depending on the number of channels scanned and the position in the channel scan sequence, the maximum possible delay for asserting INT is five conversion periods (34µs typ, delay = 0,0,0).

#### **Configuring Monitor Mode**

To write monitoring setup data, set the monitor-setup bit (bit 0 in setup byte) to 1 to extend writing up to 104 bits (13 bytes) of monitoring setup data. The number of bits written to the MAX1361/MAX1362 depends on whether the part is in single-ended or differential mode and whether the upper channel limit is set by [CS1:CS0] (Table 9).

Terminate writing at any time by using a STOP or repeated START condition. Previous monitoring setup data not overwritten remains valid.

#### **Table 9. Monitor-Mode Setup Data Format**

| Alarm reset, scan speed, INT_EN , (24 bits) | AIN1 thresholds<br>(skip if differential mode, or<br>CS1, CS0 < 1) (24 bits) | AIN2 thresholds (skip if<br>CS1, CS0 < 2)<br>(24 bits) | AIN3 thresholds (skip if differential mode, or CS1, CS0 < 3) (24 bits) |

|---------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------|

|---------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------|

### Table 10. Alarm Reset, Scan Speed Register, and INT\_EN Data Format

| RESET<br>ALARM CH 0 | RESET<br>ALARM CH 1 | RESET<br>ALARM CH 2 | RESET<br>ALARM CH 3 | DELAY 2 | DELAY 1 | DELAY 0 | INT_EN |

|---------------------|---------------------|---------------------|---------------------|---------|---------|---------|--------|

| 0/1                 | 0/1                 | 0/1                 | 0/1                 | 0/1     | 0/1     | 0/1     | 0/1    |

**Table 11. Delay Settings**

| DELAY 2 | DELAY 1 | DELAY 0 | MONITOR-MODE<br>CONVERSION RATE<br>(ksps) |

|---------|---------|---------|-------------------------------------------|

| 0       | 0       | 0       | 150.0*                                    |

| 0       | 0       | 1       | 75.0                                      |

| 0       | 1       | 0       | 37.5                                      |

| 0       | 1       | 1       | 18.8                                      |

| 1       | 0       | 0       | 9.4                                       |

| 1       | 0       | 1       | 4.7                                       |

| 1       | 1       | 0       | 2.3                                       |

| 1       | 1       | 1       | 1.2                                       |

\*When using delay = [0,0,0] in internal reference mode and AlN3/REF configured as a REF output, the MAX1361/MAX1362 may exhibit a code-dependant gain error due to insufficient internal reference drive. Gain error caused by this phenomenon is typically less than 1%FSR (0.1 $\mu$ F C<sub>REF</sub> in series with a 2 $\kappa$ C resistor) and increases with a larger C<sub>REF</sub>. Avoid this gain error by using an external reference, V<sub>DD</sub>, as a reference or use an internal reference with AlN3/REF as an analog input (see Table 4). Alternatively, choose delay bits other than [0,0,0] to lower the conversion rate.

A 1 written to the reset alarm CH\_ clears the alarm, otherwise no action occurs (Table 10). Deassert INT by clearing all alarms or by initiating an SMBus alert during an alarm condition (see the *SMBus Alert* section)

The Delay 2, Delay 1, and Delay 0 bits set the speed of monitoring by changing the delay between conversions. Delay 2, 1, and 0 = 000 sets the maximum possible speed; 001 divides the maximum speed by approximately 2. Increasing delay values further divides the previous speed by two (Table 11).

INT\_EN controls the open-drain INT output. Set INT\_EN to 1 to enable the hardware interrupt. Set INT\_EN to 0 to disable the hardware interrupt output. The INT output is high impedance when disabled or when there are no alarms. The master can also poll the alarm status register at any time to check the alarm status.

Repeat clocking channel threshold data up to the channel programmed by CS1 and CS0 (Table 12). For differential input mode, omit odd channels; the lower and upper threshold data applies to channel pairs. There is no need to clock in dummy data for odd (or even) channels (Table 6).

Table 12. Lower and Upper Threshold Data Format

| BYTE | В7  | В6  | B5           | B4        | В3  | B2  | B1           | В0        | ACKNOWLEDGE |

|------|-----|-----|--------------|-----------|-----|-----|--------------|-----------|-------------|

| 1    | X   | Х   | LT9<br>(MSB) | LT8       | LT7 | LT6 | LT5          | LT4       | ACK         |

| 2    | LT3 | LT2 | LT1          | LT0 (LSB) | X   | Х   | UT9<br>(MSB) | UT8       | ACK         |

| 3    | UT7 | UT6 | UT5          | UT4       | UT3 | UT2 | UT1          | UT0 (LSB) | ACK         |

X = Don't care. ACK = Acknowledge.

#### Table 13. Readback-Mode Format

|   |   | LIHRESHOLDS | AIN1 THRESHOLDS<br>(SKIP IF DIFFERENTIAL<br>MODE OR CS1, CS0 < 1) | AIN2 THRESHOLDS<br>(SKIP IF CS1, CS0 < 2) | AIN3 THRESHOLDS<br>(SKIP IF DIFFERENTIAL<br>MODE OR CS1, CS0 < 3) |    |        |         |         |         |         |

|---|---|-------------|-------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------|----|--------|---------|---------|---------|---------|

| 1 | 1 | 1           | 1                                                                 | D2                                        | D1                                                                | D0 | INT_EN | 24 bits | 24 bits | 24 bits | 24 bits |

### Table 14. Reading in Monitor-Mode Data Format

| ALARM-STATUS REGISTER | LATCHED-FAULT REGISTER                                   | CURRENT-CONVERSION RESULTS                               |  |  |

|-----------------------|----------------------------------------------------------|----------------------------------------------------------|--|--|

| 8 bits                | 16, 32, 48, or 64 bits (depends on CSO, CS1, and SE/DIF) | 16, 32, 48, or 64 bits (depends on CSO, CS1, and SE/DIF) |  |  |

#### Table 15. Alarm-Status Register

| CH0 UP | CH0 LOW | OW CH1 UP CH1 LOW CH2 UP |     | CH2 UP | CH2 LOW | CH3 UP | CH3 LOW |

|--------|---------|--------------------------|-----|--------|---------|--------|---------|

| 0/1    | 0/1     | 0/1                      | 0/1 | 0/1    | 0/1     | 0/1    | 0/1     |

<sup>0 =</sup> Not-alarm condition.

# Table 16. Latched-Fault and Current-Conversion Register

| AIN0        | AIN1        | AIN2        | AIN3        |

|-------------|-------------|-------------|-------------|

| 16-bit read | 16-bit read | 16-bit read | 16-bit read |