Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

#### **General Description**

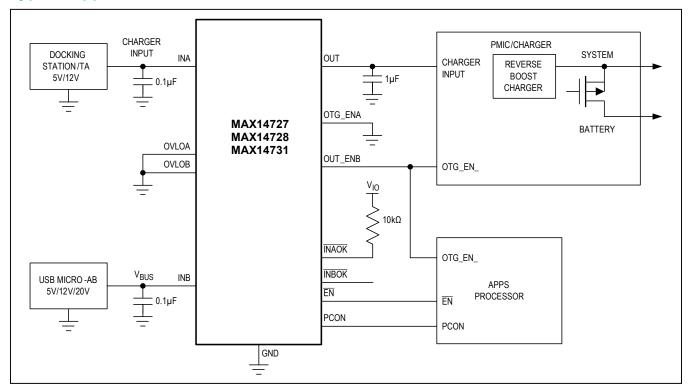

The MAX14727/MAX14728/MAX14731 provide protection to valuable consumer circuits against two positive voltage faults up to +28V<sub>DC</sub>. An internal clamp also protects the devices from surges up to 100V. The devices automatically select the input source, with channel A being the primary supply.

These devices feature reverse bias-blocking capabilities. Unlike other overvoltage protectors, when the devices are disabled, the voltage applied to OUT does not feed back into either INA or INB. These devices also feature two OTG enable pins (OTG\_ENA, OTG\_ENB) that allow OUT voltage to supply the corresponding input when OUT is higher than the output startup voltage.

These overvoltage-protection devices feature high-voltage, low on-resistance ( $73m\Omega$ , typ) internal FETs, effectively minimizing a voltage drop across the device. When the input voltage exceeds the overvoltage threshold, the internal FET is turned off to prevent damage to the protected components. The devices also have thermal-shutdown protection against overload conditions.

The overvoltage-protection threshold can be adjusted with optional external resistors to any voltage between 4V and 14V. The devices automatically choose the appropriate internal trip thresholds when the overvoltage-lockout input is set lower than the external OVLO select voltage. The internal OVLO are preset to 13.75V (typ) (MAX14727), 10V (typ) (MAX14728), or 5.92V (typ) (MAX14731).

The devices are specified over the extended -40°C to +85°C temperature range, and are available in a 30-bump, wafer-level package (WLP).

#### **Applications**

- Smartphones

- Tablets

- e-Readers

#### **Benefits and Features**

- Protects Portable Devices with Dual-Input Power

- Wide Operating Input-Voltage Protection from 3V to 28V

- · 5A Continuous-Current Capability

- Integrated 73mΩ (typ) nMOSFET Switch

- Allows Flexible and Precise Design in OVLO Implementation

- Wide Adjustable OVLO Threshold Range from 4V to 14V

- · OTG Enables Allow OUT Supply INA/INB

- Preset Accurate Internal OVLO Thresholds: 13.75V ±2% (MAX14727) 10V ±2% (MAX14728) 5.92V ±2% (MAX14731)

- Increases System Reliability Through Premium Security

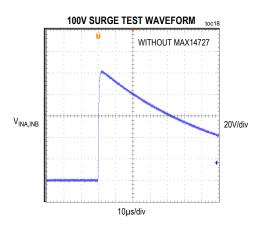

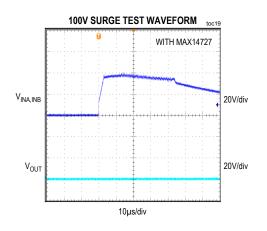

- Surge Immunity Over +100V

- · Soft-Start to Minimize In-Rush Current

- Internal 15ms Startup Debounce

- · Thermal Shutdown Protection

- Minimizes Board Space With Compact Package

- 30-Bump, 2.6mm x 2.2mm WLP

Ordering Information appears at end of data sheet.

# **Typical Application Circuit**

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

#### **Absolute Maximum Ratings**

| (All voltages are referenced to GND.)    |              | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|------------------------------------------|--------------|-------------------------------------------------------|

| INA, INB (Note 1)                        | 0.3V to +30V | WLP (derate 20.25mW/°C above +70°C)1620mW             |

| OUT                                      | 0.3V to +16V | Operating Temperature Range40°C to +85°C              |

| INA, OUT                                 | 16V to +30V  | Junction Temperature+150°C                            |

| INB, OUT                                 | 16V to +30V  | Storage Temperature Range65°C to +150°C               |

| OTG_ENA, OTG_ENB,                        |              | Soldering Temperature (reflow)+260°C                  |

| PCON, INAOK, INBOK, EN                   | 0.3V to +6V  |                                                       |

| OVLOA, OVLOB                             | 0.3V to +16V |                                                       |

| Continuous-Current into INA, INB, OUT (N | ote 2)       |                                                       |

| WLP                                      | ±5A          |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- **Note 1:** Survive-to-burst pulse up to 100V, with  $2\Omega$  series resistance and hot plugs recur. Above the input clamp voltage, input must be a surge in nature with limited energy.

- Note 2: Limited by the PCB thermal design.

#### **Package Thermal Characteristics (Note 3)**

WLP

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .....49.38°C/W

Note 3: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{INA,INB}$  = 3V to 28V,  $V_{OUT}$  = 3V to 14V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{INA,INB}$  = 5V,  $T_A$  = +25°C) (Notes 4, 5)

| PARAMETER                           | SYMBOL                | CONDITIONS                                                                                                                     |     | TYP   | MAX  | UNITS |

|-------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|-------|

| Input Startup-Voltage Threshold     | V <sub>IN_ST</sub>    |                                                                                                                                |     | 2.65  | 3.2  | V     |

| Input Sustaining Voltage            | V <sub>IN_SU</sub>    | I <sub>OUT</sub> = 0A                                                                                                          |     | 1.95  | 2.35 | V     |

| Input Valid-Voltage Threshold       | V <sub>IN_VAL</sub>   |                                                                                                                                | 3.9 | 4.1   | 4.3  | V     |

| Input Clamp Voltage                 | V <sub>IN_CLAMP</sub> | I <sub>INA,INB</sub> = 10mA, T <sub>A</sub> = +25°C                                                                            |     | 34    |      | V     |

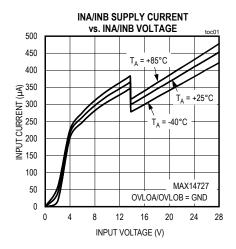

| Input Supply Current                | I <sub>INA,INB</sub>  | V <sub>OVLOA,OVLOB</sub> = 0V, V <sub>INA,INB</sub> = 5V,<br>INAOK, INBOK is unconnected,<br>I <sub>OUT</sub> = 0A (Note 6)    |     | 230   | 360  | μА    |

| Output Startup-Voltage<br>Threshold | V <sub>OUTST</sub>    |                                                                                                                                |     | 2.65  | 3.2  | V     |

| Output Sustaining Voltage           | V <sub>OUTSU</sub>    | I <sub>INA,INB</sub> = 0A                                                                                                      |     | 1.95  | 2.35 | V     |

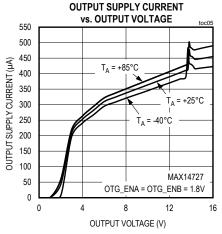

| Output Supply Current               | I <sub>OUT</sub>      | V <sub>OVLOA,OVLOB</sub> = 0V, V <sub>OUT</sub> = 5V,<br>I <sub>INA,INB</sub> = 0A, V <sub>OTG_ENA,OTG_ENB</sub> = 1.8V        |     | 275   | 420  | μA    |

| Output Shutdown Current             | I <sub>SHDN</sub>     | V <sub>OVLOA,OVLOB</sub> = 3V, V <sub>OUT</sub> = 5V,<br>V <sub>INA,INB</sub> = 0V, V <sub>OTG_ENA,OTG_ENB</sub> = 0V          |     | 6.5   | 14   | μA    |

| Input Leakage Voltage               |                       | V <sub>OUT</sub> = 14V, INA, INB unconnected,<br>V <sub>OTG_ENA,OTG_ENB</sub> = 0V                                             |     | 0.001 | 0.1  | V     |

| Input Discharge Current             |                       | V <sub>INA,INB</sub> = V <sub>OUT</sub> = 5V, INA, INB discharge current after an OTG_ENA, OTG_ENB transition from high to low |     | 130   | 200  | mA    |

# **Electrical Characteristics (continued)**

$(V_{INA,INB}=3V\ to\ 28V,\ V_{OUT}=3V\ to\ 14V,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{INA,INB}=5V,\ T_A=+25^{\circ}C)$  (Notes 4, 5)

| PARAMETER                                        | SYMBOL                | co                                                                                                                                                 | MIN                                                         | TYP  | MAX   | UNITS |    |

|--------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-------|-------|----|

| OVP (INA,INB TO OUT)                             | •                     |                                                                                                                                                    |                                                             |      | ,     |       |    |

| On-Resistance (INA to OUT)                       | R <sub>ONA</sub>      | V <sub>INA</sub> = 5V, I <sub>OUT</sub> = 100mA, T <sub>A</sub> = +25°C                                                                            |                                                             |      | 68    | 115   | mΩ |

| On-Resistance (INB to OUT)                       | R <sub>ONB</sub>      | V <sub>INB</sub> = 5V, I <sub>OUT</sub> =                                                                                                          | = 100mA, T <sub>A</sub> = +25°C                             |      | 68    | 115   | mΩ |

|                                                  |                       | NAN/4 4707                                                                                                                                         | V <sub>IN</sub> rising                                      | 13.5 | 13.75 | 14.0  |    |

|                                                  |                       | MAX14727                                                                                                                                           | V <sub>IN</sub> falling                                     | 13.0 |       |       |    |

| Internal Over older a Trial avel                 |                       | MAX14728                                                                                                                                           | V <sub>IN</sub> rising                                      | 9.85 | 10    | 10.15 | V  |

| Internal Overvoltage-Trip Level                  | V <sub>IN</sub> OVLO  | WAX 14728                                                                                                                                          | V <sub>IN</sub> falling                                     | 9.5  |       |       | V  |

|                                                  |                       | MAY44704                                                                                                                                           | V <sub>IN</sub> rising                                      | 5.83 | 5.92  | 6.01  |    |

|                                                  |                       | MAX14731                                                                                                                                           | V <sub>IN</sub> falling                                     | 5.6  |       |       |    |

| OVLOA, OVLOB Set Threshold                       | V <sub>OVLO_TH</sub>  |                                                                                                                                                    |                                                             | 1.2  |       | 1.24  | V  |

| Adjustable OVLOA, OVLOB<br>Threshold Range       | V <sub>OVLO_EXT</sub> |                                                                                                                                                    |                                                             | 4    |       | 14    | ٧  |

| External OVLOA,OVLOB Select Threshold            | V <sub>OVLO_SEL</sub> |                                                                                                                                                    |                                                             | 0.2  | 0.25  | 0.3   | ٧  |

| Active OUT Discharge Current                     | l <sub>OUT_DIS</sub>  | V <sub>OUT</sub> = V <sub>INA,INB</sub><br>current during a tr<br>channel A and B v                                                                |                                                             | 130  |       | mA    |    |

| DIGITAL SIGNALS (INAOK, INB                      | OK, OTG_ENA           | , OTG_ENB, PCO                                                                                                                                     | N, EN)                                                      |      |       |       |    |

| INAOK, INBOK Output Low<br>Voltage               | V <sub>OL</sub>       | V <sub>I/O</sub> = 3.3V, I <sub>SINK</sub> = 1mA                                                                                                   |                                                             |      |       | 0.4   | V  |

| INAOK, INBOK Leakage<br>Current                  |                       | V <sub>I/O</sub> = 3.3V, ĪNAC                                                                                                                      | K, INBOK deasserted                                         |      |       | 1     | μA |

| OTG_ENA, OTG_ENB, PCON, EN Input Logic-High      | V <sub>IH</sub>       |                                                                                                                                                    |                                                             | 1.6  |       |       | V  |

| OTG_ENA, OTG_ENB, PCON, EN Input Logic-Low       | V <sub>IL</sub>       |                                                                                                                                                    |                                                             |      |       | 0.4   | V  |

| OTG_ENA, OTG_ENB, PCON, EN Input Leakage Current | I <sub>IN</sub>       | $0V \le V_{IN} \le V_{IL} \text{ or } V_{IH} \le V_{IN} \le 5.5V$                                                                                  |                                                             | -1   |       | +1    | μA |

| TIMING CHARACTERISTICS                           |                       |                                                                                                                                                    |                                                             |      |       |       |    |

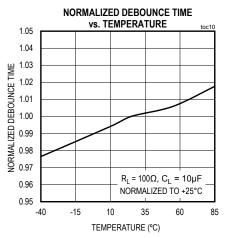

| INA, INB Debounce Time                           | t <sub>DEB</sub>      |                                                                                                                                                    | charge pump on (10% of $= 100\Omega$ , $C_{LOAD} = 10\mu F$ |      | 17    |       | ms |

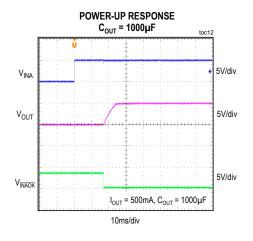

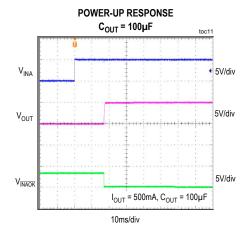

| INA, INB Soft-Start Time                         | t <sub>SS</sub>       | V <sub>INA,INB</sub> = 5V, <u>INAOK</u> , <u>INBOK</u> assert to<br>V <sub>OUT</sub> = 90% of V <sub>INA,INB</sub> ,<br>C <sub>LOAD</sub> = 1000μF |                                                             |      | 5     |       | ms |

| INA, INB Break-Before-Make<br>Time               | t <sub>BBM</sub>      | V <sub>INB</sub> = 5V, V <sub>INA</sub> =<br>C <sub>LOAD</sub> = 10μF                                                                              | 0V to 5V or 5V to 0V,                                       |      | 8     |       | ms |

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

#### **Electrical Characteristics (continued)**

$(V_{INA,INB} = 3V \text{ to } 28V, V_{OUT} = 3V \text{ to } 14V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{INA,INB} = 5V, T_A = +25^{\circ}\text{C}$ ) (Notes 4, 5)

| PARAMETER                              | SYMBOL               | CONDITIONS MIN TYP MAX                                                                                                     |           | UNITS |    |    |

|----------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|-------|----|----|

| OUT Discharge Pulse Duration           | t <sub>OUT_DIS</sub> |                                                                                                                            | 7.2 8 8.8 |       | ms |    |

| INA, INB OVP Turn-Off<br>Response Time | t <sub>OFF</sub>     | From $V_{INA,INB} > V_{OVLOA,OVLOB}$ to $V_{OUT} = 80\%$ of $V_{INA,INB}$ , $R_{LOAD} = 100\Omega$                         |           | 100   |    | ns |

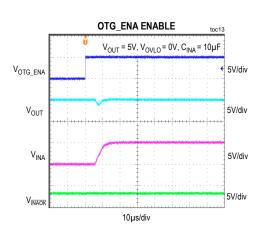

| OTG Turn-On Time                       | t <sub>OTG_ON</sub>  | Time from OTG_ENA, OTG_ENB high to $V_{INA,INB}$ = 80% of $V_{OUT}$ , $V_{OUT}$ = 5V, $C_{INA,INB}$ = 10 $\mu$ F           | 30        |       | μs |    |

| INA, INB Discharge Pulse<br>Duration   |                      | V <sub>INA,INB</sub> = V <sub>OUT</sub> = 5V, current pulse duration after an OTG_ENA, OTG_ENB transition from high to low | 16        |       | ms |    |

| THERMAL PROTECTION                     |                      |                                                                                                                            |           |       |    |    |

| Thermal Shutdown                       | T <sub>SHDN</sub>    |                                                                                                                            | 150       |       | °C |    |

| Thermal Hysteresis                     | T <sub>HYST</sub>    |                                                                                                                            | 20        |       | °C |    |

| ESD PROTECTION                         |                      |                                                                                                                            |           |       |    |    |

| Human Body Model                       |                      | INA, INB                                                                                                                   | ±15       |       | kV |    |

| IEC 61000-4-2 Contact<br>Discharge     |                      | INA, INB                                                                                                                   | ±8        |       | kV |    |

| IEC 61000-4-2 Air Gap<br>Discharge     |                      | INA, INB                                                                                                                   | ±15       |       | kV |    |

- Note 4: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design and not production tested.

- Note 5: The input is considered not present when it is lower than a rough threshold of  $T_P = 1.5V$  (typ). When the B path is active and the INA >  $T_P$  is connected, the device goes to the A path (since it has the priority), but the INA has to be higher than the startup voltage to turn on the switch.

- Note 6: When both inputs are connected, supply current is drawn from the highest one.

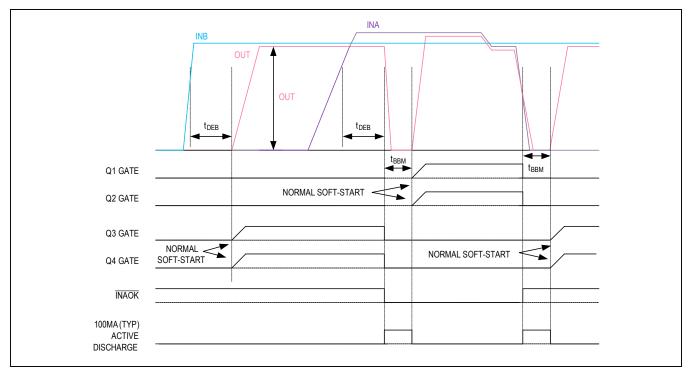

Figure 1. Automatic Switch Operation, PCON = 0

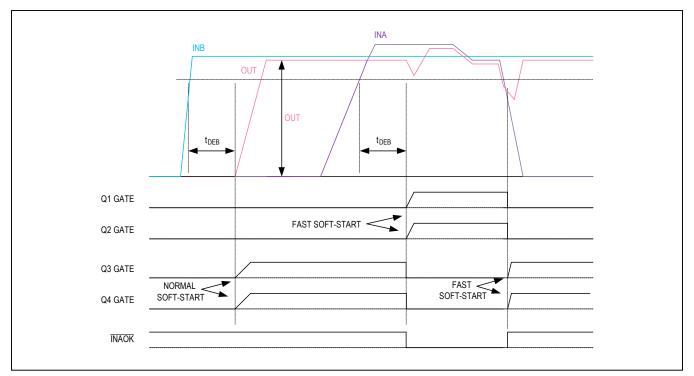

Figure 2. Automatic Switch Operation, PCON = 1

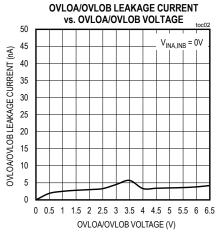

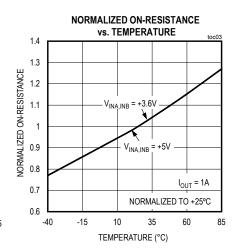

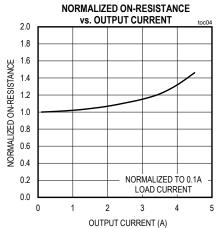

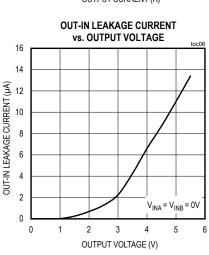

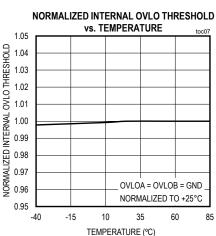

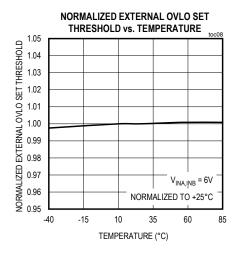

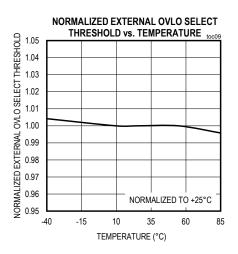

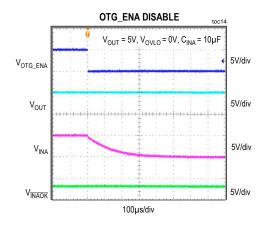

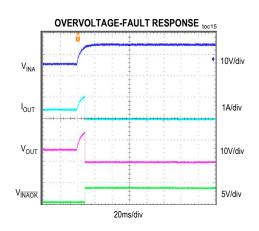

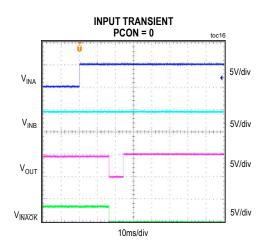

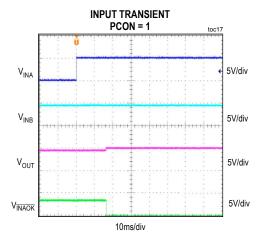

#### **Typical Operating Characteristics**

$(V_{INA,\ INB}$  = +5V, OVLO = GND,  $C_{IN}$  = 0.1 $\mu$ F,  $C_{OUT}$  = 1 $\mu$ F,  $T_A$  = +25°C, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

$(V_{INA,\ INB}$  = +5V, OVLO = GND,  $C_{IN}$  = 0.1 $\mu$ F,  $C_{OUT}$  = 1 $\mu$ F,  $T_A$  = +25°C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

$(V_{INA,\ INB}$  = +5V, OVLO = GND,  $C_{IN}$  = 0.1 $\mu$ F,  $C_{OUT}$  = 1 $\mu$ F,  $T_A$  = +25°C, unless otherwise noted.)

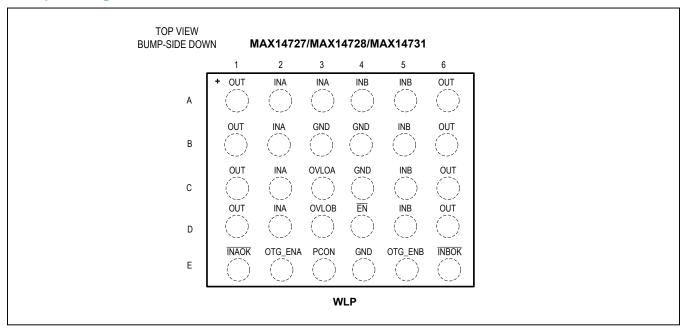

# **Bump Configurations**

# **Bump Description**

| BUMP                              | NAME    | FUNCTION                                                                                                                                                                                                                                                                  |

|-----------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A6, B1, B6,<br>C1, C6, D1, D6 | OUT     | Overvoltage-Protection Output. Bypass OUT with a 1µF ceramic capacitor. Externally connect all OUT together.                                                                                                                                                              |

| A2, A3, B2,<br>C2, D2             | INA     | Overvoltage-Protection Input A. Bypass INA with a 0.1µF ceramic capacitor as close as possible to the device. Externally connect all INA together.                                                                                                                        |

| A4, A5, B5, C5,<br>D5             | INB     | Overvoltage-Protection Input B. Bypass INB with a 0.1µF ceramic capacitor as close as possible to the device as possible. Externally connect all INB together.                                                                                                            |

| B3, B4, C4, E4                    | GND     | Ground                                                                                                                                                                                                                                                                    |

| C3                                | OVLOA   | Overvoltage-Lockout Input A. Connect OVLOA to GND to use internal OVLO threshold for channel A. Connect OVLOA to a resistor divider for different voltage threshold for channel A.                                                                                        |

| D3                                | OVLOB   | Overvoltage-Lockout Input B. Connect OVLOB to GND to use internal OVLO threshold for channel B. Connect OVLOB to a resistor divider for different voltage threshold for channel B.                                                                                        |

| D4                                | ĒN      | Active-Low Enable for Both OVP. When $\overline{EN}$ is high, both channels are off. When $\overline{EN}$ is low, both channels are active. $\overline{EN}$ does not affect $\overline{INAOK}$ or $\overline{INBOK}$ .                                                    |

| E1                                | ĪNAOK   | Open-Drain Flag Output. $\overline{\text{INAOK}}$ is driven low after INA voltage is stable between minimum $V_{\text{IN}}$ and $V_{\text{OVLO}}$ when OTG_ENA = 0. Connect a pullup resistor from $\overline{\text{INAOK}}$ to the logic I/O voltage of the host system. |

| E2                                | OTG_ENA | Enable Input for Channel A OTG Supply Operation. When OTG_ENA is low, channel A OTG operation is disabled. When OTG_ENA is high, channel A OTG operation is enabled, and OUT is connected to INA.                                                                         |

| E3                                | PCON    | Path Overlap Control. When PCON is low, there is a break-before-make time, 8ms (typ). When PCON is high, there is no break-before-make time. See the <i>Automatic Switch Operation</i> section.                                                                           |

# **Bump Description (continued)**

| BUMP | NAME    | FUNCTION                                                                                                                                                                                                                                                                  |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E5   | OTG_ENB | Enable Input for Channel B OTG Supply Operation. When OTG_ENB is low, channel B OTG operation is disabled. When OTG_ENB is high, channel B OTG operation is enabled, and OUT is connected to INB.                                                                         |

| E6   | ĪNBOK   | Open-Drain Flag Output. $\overline{\text{INBOK}}$ is driven low after INB voltage is stable between minimum $V_{\text{IN}}$ and $V_{\text{OVLO}}$ when OTG_ENB = 0. Connect a pullup resistor from $\overline{\text{INBOK}}$ to the logic I/O voltage of the host system. |

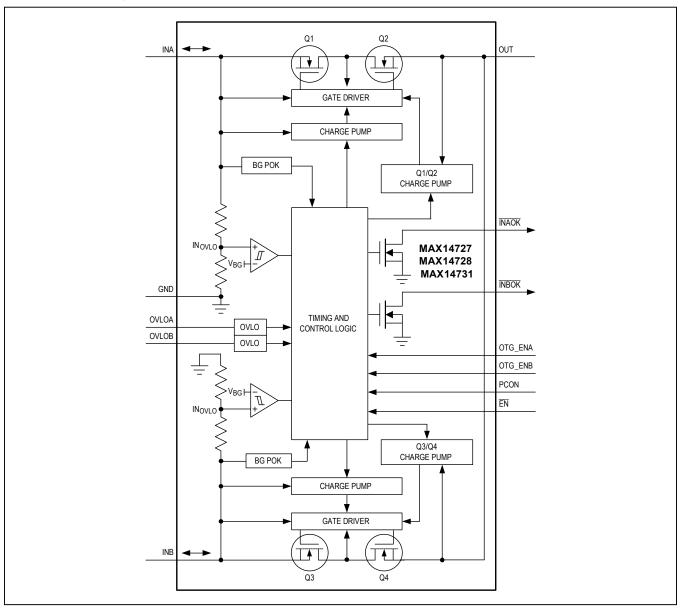

# **Functional Diagram**

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

#### **Detailed Description**

The MAX14727/MAX14728/MAX14731 provide overvoltage protection for applications with two input sources. The devices feature low on-resistance and protect low-voltage systems against voltage faults up to 28V<sub>DC</sub>. An internal clamp also protects the devices from surges up to 100V. If the input voltage exceeds the overvoltage threshold, the output is disconnected from the input to prevent damage to the protected components. The 15ms debounce time prevents false turn-on of the internal FETs during startup.

#### **Automatic Input Power Path Control**

Automatic power path select has two modes of operation based on PCON. At least one of the inputs has to cross the startup voltage (2.75V, typ) at power-up for the circuitry to work. INA always has priority and INB only takes over INA when either INB is the only present input or when INB is valid (> 4.1V, typ) and INA is invalid (< 4.1V, typ) (Figure 1 and Figure 2).

#### When PCON = 0 (Figure 1):

When there is an input source change, the device has a break-before-make time (8ms, typ) with active discharge of 100mA (typ) during the off period. Additionally, during the off period, the battery-charger mode can reset so the charger can draw the proper amount of current.

INAOK and INBOK assert when the appropriate INA, INB is above the sustaining voltage (1.9V, typ) and below the OVLOA, OVLOB threshold.

#### When PCON = 1 (Figure 2):

When INA is detected valid while INB is valid, channel B is turned off and channel A is turned on quickly, with a higher soft-start current. Therefore, the transition from INB charging to INA charging is without shutoff. When INA becomes invalid while INB is still valid, channel B is turned on immediately, without debounce time, by using a higher soft-start current again.

INAOK and INBOK assert when the respective INA,INB is above valid voltage (4.1V, typ) and below the OVLOA, OVLOB threshold.

**Table 1. Functionality Table**

| OVLOA<br>OVLOB | OTG_ENA | OTG_ENB | ĒN | ĪNAOK                   | INBOK                   | CHANNEL A               | CHANNEL B            |

|----------------|---------|---------|----|-------------------------|-------------------------|-------------------------|----------------------|

| 0              | 0       | 0       | 0  | INA status<br>(Note 7)  | INB status<br>(Note 7)  | (Note 8)                | (Note 8)             |

| 0              | 0       | 0       | 1  | INA status<br>(Note 9)  | INB status<br>(Note 9)  | Open                    | Open                 |

| 0              | 0       | 1       | 0  | INA status<br>(Note 7)  | High                    | Based on INA status     | Close                |

| 0              | 0       | 1       | 1  | INA status<br>(Note 9)  | High                    | Open                    | Open                 |

| 0              | 1       | 0       | 0  | High                    | INB status<br>(Note 7)  | Close                   | Based on INB status  |

| 0              | 1       | 0       | 1  | High                    | INB status<br>(Note 9)  | Open                    | Open                 |

| 0              | 1       | 1       | 0  | High                    | High                    | Close                   | Close                |

| 0              | 1       | 1       | 1  | High                    | High                    | Open                    | Open                 |

| 1              | х       | Х       | Х  | High when<br>OVLOA high | High when<br>OVLOB high | Open when<br>OVLOA high | Open when OVLOB high |

X = Don't care.

Note 7: PCON = 0, INAOK, INBOK asserts low when respective INA,INB is greater than sustaining voltage (1.9V, typ). PCON = 1, INAOK, and INBOK assert low when respective INA,INB is greater than valid voltage (4.1V, typ).

Note 8: INA always has priority. INB takes over INA when INB is the only present input or when INB is valid (above 4.1V, typ) and INA is invalid (below 4.1V, typ).

**Note 9:** When EN is high, both channels are open and the minimum input functionality voltage is startup voltage (2.75V, typ).

#### Soft-Start

To minimize inrush current, the devices feature a soft-start capability to slowly turn on the internal FETs. Soft-start begins when  $\overline{\text{INAOK}}$  and  $\overline{\text{INBOK}}$  are asserted, and ends after 15ms (typ).

#### Overvoltage Lockout (OVLOA, OVLOB)

Connect OVLOA, OVLOB to ground to use the internal OVLO comparator with the internally set OVLO value. When INA, INB go above the overvoltage-lockout threshold ( $V_{IN}$  OVLO), OUT is disconnected from INA, INB and INAOK and INBOK is deasserted. When INA, INB drops below  $V_{IN}$  OVLO, the debounce time starts counting. After the debounce time, OUT follows INA, INB again and INAOK and INBOK is asserted.

The OVLOA, OVLOB input can be used as an additional enable input (Table 2).

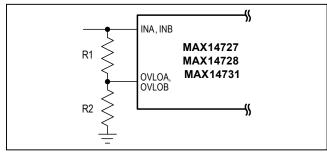

#### **External OVLO Adjustment Functionality**

When an external resistor-divider is connected to OVLOA, OVLOB, and  $V_{OVLOA}$ ,  $V_{OVLOB}$  exceeds the OVLOA, OVLOB select voltage ( $V_{OVLO\_SEL}$ ), the internal OVLOA, OVLOB comparator read INA,INB by the external resistor-divider.

R1 =  $1M\Omega$  is a good starting value for minimum current consumption. Since  $V_{IN\_OVLO}$ ,  $V_{OVLO\_TH}$ , and R1 are known, R2 can be calculated from the following formula:

$$V_{IN\_OVLO} = V_{OVLO\_TH} \times \left[1 + \frac{R1}{R2}\right]$$

This external resistor-divider is completely independent from the internal resistor-divider.

**Table 2. Truth Table**

| SWITCH OF | PEN/CLOSE | OVLOA, OVLOB |      |  |

|-----------|-----------|--------------|------|--|

| SWITCH OF | EN/CLUSE  | Low High     |      |  |

| FN        | Low       | Close        | Open |  |

| EN        | High      | Open         | Open |  |

Figure 3. External OVLO Adjustment

www.maximintegrated.com

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

#### **Reverse-Bias Blocking**

The devices feature reverse-bias blocking. When INA, INB voltage is below the input startup voltage and OTG\_ENA and OTG\_ENB is low, the switch between INA, INB and OUT is open and the two back-to-back diodes of the two series switches block reverse bias. Therefore, when the voltage is applied at the output, current does not travel back to the input.

#### **OTG Enable**

The devices feature reverse-turn-on capability. OTG\_ENA and OTG\_ENB can be used to turn on the switch for OUT to feed back to INA, INB when voltage applied at OUT is above the startup voltage (2.75V, typ). When OTG\_ENA, OTG\_ENB is high, INAOK and INBOK is deasserted. During the OTG operation, if INA, INB go above OVLOA, OVLOB, the OVP switch turns off. It is recommended that power be supplied to OUT prior to OTG operation. Power is also removed from OUT prior to disabling OTG operation. When either OTG\_ENA or OTG\_ENB is on, the internal power path control is disabled.

#### **Thermal-Shutdown Protection**

The devices feature thermal-shutdown protection to protect the device from overheating. The internal FETs turn off when the junction temperature exceeds +150°C (typ). The device returns to normal operation once the temperature drops by approximately 20°C (typ).

#### **Applications Information**

#### **Input Bypass Capacitor**

For most applications, bypass INA and INB to GND with a  $0.1\mu F$  ceramic capacitor as close as possible to the device. If the power source has significant inductance due to long lead length, take care to prevent overshoots due to the LC tank circuit and provide protection by clamping the overshoot.

#### **Output Capacitor**

The slow turn-on time provides a soft-start function that allows the device to charge an output capacitor up to  $1000\mu F$  without turning off due to an overcurrent condition.

When PCON = 0, the output is actively discharged during the channel B to channel A switchover event. The inductance of the input cable with a small input capacitance (0.1 $\mu$ F) would cause an input voltage drop. This might trigger a switch back to channel B and output latchoff. Therefore, the output capacitor should be limited so that the input voltage stays above a valid voltage during the output recharge event. Usually, the output capacitor value of 33 $\mu$ F or less is recommended for 1m charger cable.

#### **Extended ESD Protection**

ESD-protection structures are incorporated on all pins to protect against electrostatic discharges up to ≤ 2kV (Human Body Model) encountered during handling and assembly. INA and INB are further protected against ESD up to ±15kV (Human Body Model), ±15kV (Air-Gap Discharge method described in IEC 61000-4-2) and ±8kV (Contact discharge method described in IEC 61000-4-2) without damage.

The ESD structures withstand high ESD both in normal operation and when the device is powered down. After an ESD event, the devices continue to function without latchup.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### **Human Body Model ESD Protection**

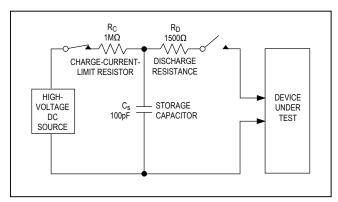

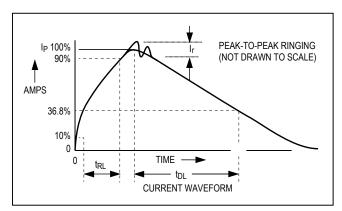

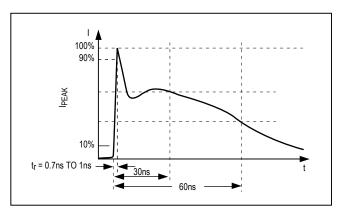

Figure 4 shows the HBM and Figure 5 shows the current waveform it generates when discharged into a

Figure 4. Human Body ESD Test Model

Figure 5. Human Body Current Waveform

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

low-impedance state. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

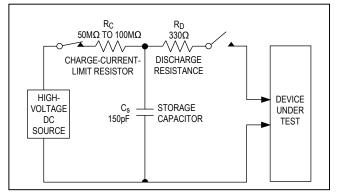

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 6 shows the IEC 61000-4-2 model. Figure 7 shows the current waveform for the IEC 61000-4-2 ESD contact discharge test.

Figure 6. IEC 61000-4-2 ESD Test Model

Figure 7. IEC 61000-4-2 ESD Generator Current Waveform

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

# **Ordering Information/Selector Guide**

| PART         | OVLO<br>(V) | PIN-<br>PACKAGE | TEMP           |

|--------------|-------------|-----------------|----------------|

| MAX14727EWV+ | 13.75       | 30 WLP          | -40°C TO +85°C |

| MAX14728EWV+ | 10          | 30 WLP          | -40°C TO +85°C |

| MAX14731EWV+ | 5.92        | 30 WLP          | -40°C TO +85°C |

<sup>+</sup>Denotes a lead(Pb)-free package/RoHS-compliant package.

# **Chip Information**

PROCESS: BiCMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE  | OUTLINE        | LAND                           |

|---------|----------|----------------|--------------------------------|

| TYPE    | CODE     | NO.            | PATTERN NO.                    |

| 30 WLP  | W302F2+1 | <u>21-0762</u> | Refer to Application Note 1891 |

# Dual-Input, Bidirectional Overvoltage Protector with Automatic Path Control

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                  | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------------------|------------------|

| 0                  | 3/15             | Initial release                                              | _                |

| 1                  | 6/15             | Removed future product references from MAX14728 and MAX14731 | 4, 15            |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.