Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

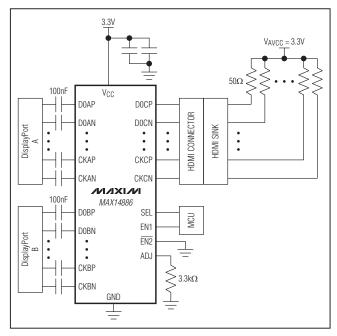

The MAX14886 high-speed, low-skew, active redriver multiplexer is ideal for switching between outputs of dual-graphics systems and signal conditioning to meet HDMI<sup>™</sup> v.1.4 compliance up to 2.25Gbps at an external HDMI connector. It is used for switching between integrated (e.g., Intel or AMD) and discrete graphics (e.g., NVIDIA or ATI GPU). The device is VESA DisplayPort™ Interoperability Guideline v.1.1a-compliant (requires external DDC logic) and integrates seamlessly with an external HDMI connector on the motherboard.

The device accommodates differential inputs as low as 200mV and drives transition minimized differential signaling (TMDS®) outputs to 1000mV (typ). A precision resistor on the output level adjust pin (ADJ) allows differentiated output back-termination resistors of  $400\Omega$  (typ) to better meet HDMI mask jitter compliance, while maintaining full TMDS swing requirements. The device supports AC-(DisplayPort) or DC-(HDMI) coupling directly to the graphics IC and must be DC-coupled to the HDMI connector. In addition, the device features current backflow protection at the HDMI connector and a low-power, active-high or active-low shutdown mode.

The device operates with a single +3.3V supply, is specified over the 0°C to +70°C commercial temperature range, and is available in a 5mm x 5mm, 40-pin TQFN package.

#### **Applications**

**Dual Graphics Notebook Computers** Dual Mode DisplayPort to HDMI External Switches or Adapters

### **Features**

- ♦ Single +3.3V Supply

- ♦ Meets HDMI v.1.4 Eye Mask Up to 2.25Gbps

- ♦ Meets VESA DisplayPort Interoperability Guideline v.1.1a (Requires External DDC Logic)

- **♦ Low-Power Shutdown Mode Active High or Active Low**

- ♦ Output Level Adjust (ADJ) for Output Back-**Termination Without Amplitude Loss**

- ♦ Seamless Integration into Dual-Graphics Systems with External HDMI Connector

**DC-Coupled HDMI Outputs Mate Directly to HDMI Connector**

AC- or DC-Coupled TMDS-Formatted Inputs

### **Ordering Information**

| PART         | TEMP RANGE   | PIN-PACKAGE |

|--------------|--------------|-------------|

| MAX14886CTL+ | 0°C to +70°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package.

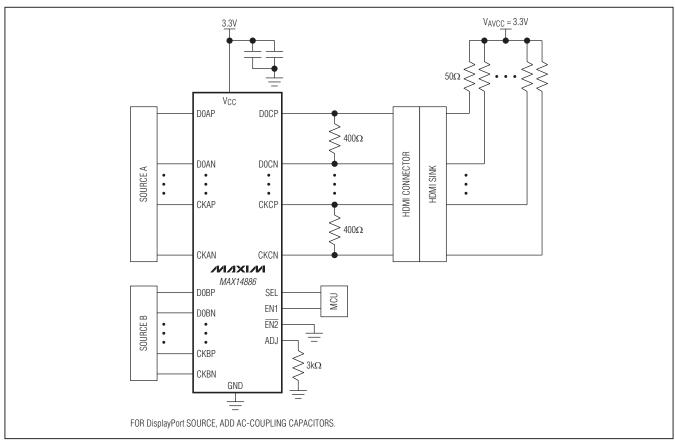

## **Typical Operating Circuit**

HDMI is a trademark of HDMI Licensing, LLC. DisplayPort is a trademark of Video Electronics Standards

TMDS is a registered trademark of Silicon Image, Inc.

MIXIM

Association (VESA).

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)        |                      |

|--------------------------------------|----------------------|

| VCC                                  | 0.3V to +4.0V        |

| EN1, EN2, SEL, ADJ                   | 0.3V to (VCC + 0.3V) |

| D_CP, D_CN, CKCP, CKCN Short-        | Circuit              |

| Output Current                       | ±30mA                |

| All Other Pins Short-Circuit Current | ±5mA                 |

| O '' D D' ' ' ' /T.                  | 7000)                |

| Continuous Power Dissipation (TA:    | = +/0°C)             |

| Operating Temperature Range       | 0°C to +70°C   |

|-----------------------------------|----------------|

| Storage Temperature Range         | 65°C to +150°C |

| Maximum Junction Temperature      | +150°C         |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

TOFN

**Note 1:** Package thermal resistances were obtained using method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.3V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C, R_{ADJ} = 3.3k\Omega, C_{CL} = 100nF, typical values are at T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                 | SYMBOL          | CONDITIONS                                               | MIN             | TYP | MAX             | UNITS |

|-------------------------------------------|-----------------|----------------------------------------------------------|-----------------|-----|-----------------|-------|

| DC PERFORMANCE                            |                 |                                                          |                 |     |                 |       |

| Supply Voltage                            | Vcc             |                                                          | 3               |     | 3.6             | V     |

| Supply Current                            | Icc             | EN1 = high, EN2 = low                                    |                 |     | 52.5            | mA    |

| Total Supply Current                      | IGND            | $50$ Ω termination to AVCC, $V_{AVCC} = +3.3V$ (Note 3)  |                 |     | 105             | mA    |

| Shutdown Supply Current                   | ISHUT           | $EN1 = low or \overline{EN2} = high$                     |                 |     | 100             | μA    |

| Single-Ended Input Termination Resistance | R <sub>IN</sub> | DC                                                       | 40              |     | 60              | Ω     |

| Single-Ended Output Voltage<br>High       | Voн             | DC, VAVCC = +3.3V (Notes 3, 4)                           | VAVCC<br>- 0.01 |     | VAVCC<br>+ 0.01 | V     |

| Single-Ended Output Voltage<br>Low        | VoL             | DC, V <sub>A</sub> V <sub>C</sub> C = +3.3V (Notes 3, 4) | VAVCC<br>- 0.6  |     | VAVCC<br>- 0.45 | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VCC = +3.3V, TA = 0^{\circ}C \text{ to } +70^{\circ}C, RADJ = 3.3k\Omega, CCL = 100nF, typical values are at TA = +25^{\circ}C.)$  (Note 2)

| PARAMETER                      | SYMBOL                        | CONDITIONS                             | MIN | TYP | MAX  | UNITS   |  |

|--------------------------------|-------------------------------|----------------------------------------|-----|-----|------|---------|--|

| AC PERFORMANCE                 |                               |                                        |     |     |      |         |  |

| Differential Input Return Loss | SDD11                         | 150MHz ≤ f ≤ 1.25GHz                   |     |     | -8   | dB      |  |

| Input Frequency Range          | fini                          | Clock                                  | 25  |     | 225  | MHz     |  |

| Input Frequency hange          | fIN                           | Data                                   | 225 |     | 1125 | IVII IZ |  |

| Differential Input Range       | VIDIFF                        |                                        | 200 |     | 1600 | mV      |  |

| Differential Output Voltage    | Vodiff                        | $50\Omega$ single termination          | 900 |     | 1250 | mV      |  |

| Output Rise/Fall Time          | t <sub>R/F</sub>              | 20% to 80%, 2.25Gbps                   |     |     | 80   | ps      |  |

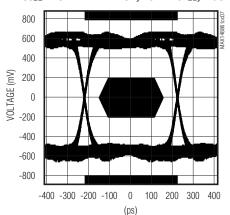

| Deterministic Jitter           | tDJ                           | K28.5 pattern, up to 2.25Gbps (Note 4) |     |     | 0.04 | UI      |  |

| Random Jitter                  | t <sub>RJ</sub>               | D10.2 pattern, 2.25Gbps (Note 4)       |     |     | 1.1  | psRMS   |  |

| Lane-to-Lane Skew              | tsk                           |                                        |     | 50  |      | ps      |  |

| Propagation Delay              | tpD                           |                                        |     | 250 |      | ps      |  |

| CONTROL LOGIC (EN1, EN2, SI    | CONTROL LOGIC (EN1, EN2, SEL) |                                        |     |     |      |         |  |

| Input Logic-Low Voltage        | VIL                           |                                        |     |     | 0.6  | V       |  |

| Input Logic-High Voltage       | VIH                           |                                        | 1.4 |     |      | V       |  |

| Input Logic Hysteresis         | VHYST                         |                                        |     | 50  |      | mV      |  |

| Input Pulldown/Pullup Resistor | RIPULL                        |                                        |     | 400 |      | kΩ      |  |

| Shutdown Recovery Time         | tshut                         |                                        |     | 20  |      | μs      |  |

| TMDS Mux Switching Time        | tMUX                          |                                        |     | 50  |      | ns      |  |

| ESD PROTECTION                 |                               |                                        |     |     |      |         |  |

| All Pins                       |                               | Human Body Model                       |     | ±8  |      | kV      |  |

Note 2: All units are production tested at TA = +70°C. Specifications over temperature are guaranteed by design.

Note 3: AVCC is an external supply.

Note 4: Guaranteed by design; not production tested.

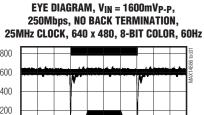

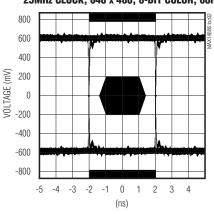

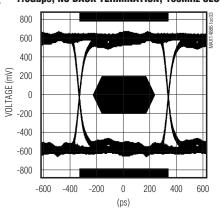

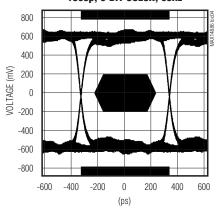

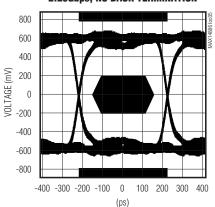

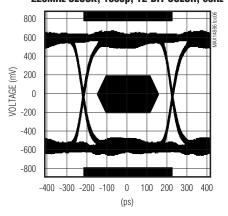

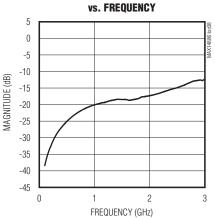

## **Typical Operating Characteristics**

$(VCC = +3.3V, TA = +25^{\circ}C, RADJ = 3.3k\Omega, unless otherwise noted.)$

800 600 400 VOLTAGE (mV) 200 0 -200 -400 -600 -800 -3 -2 0 2 -1 1 (ns)

EYE DIAGRAM, VIN = 200mV<sub>P-P</sub>, 250Mbps, NO BACK TERMINATION. 25MHz CLOCK, 640 x 480, 8-BIT COLOR, 60Hz

EYE DIAGRAM, VIN = 1600mVp-p, 1.5Gbps, NO BACK TERMINATION, 150MHz CLOCK

EYE DIAGRAM, VIN = 200mVp-p, 1.5Gbps, NO BACK TERMINATION, 1080p, 8-BIT COLOR, 60Hz

EYE DIAGRAM, VIN = 1600mVp-p, 2.25Gbps, NO BACK TERMINATION

EYE DIAGRAM, VIN = 200mVp-p, 2.25Gbps, NO BACK TERMINATION, 225MHz CLOCK, 1080p, 12-BIT COLOR, 60Hz

EYE DIAGRAM, VIN = 200mVp-p, 2.25Gbps, 400 $\Omega$  BACK TERMINATION. RSET = 3k $\Omega$ . FIGURE 1

**DIFFERENTIAL INPUT RETURN LOSS**

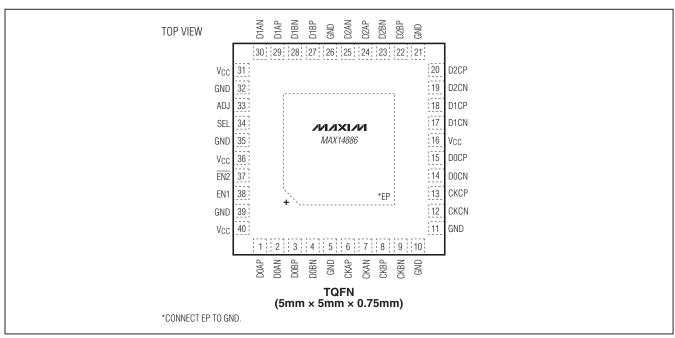

## Pin Configuration

# Pin Description

| PIN                                    | NAME | FUNCTION                                                                                                                                                            |

|----------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                      | D0AP | Noninverting Input D0 for Channel A                                                                                                                                 |

| 2                                      | D0AN | Inverting Input D0 for Channel A                                                                                                                                    |

| 3                                      | D0BP | Noninverting Input D0 for Channel B                                                                                                                                 |

| 4                                      | D0BN | Inverting Input D0 for Channel B                                                                                                                                    |

| 5, 10,<br>11, 21,<br>26, 32,<br>35, 39 | GND  | Ground                                                                                                                                                              |

| 6                                      | CKAP | Noninverting Input Clock for Channel A                                                                                                                              |

| 7                                      | CKAN | Inverting Input Clock for Channel A                                                                                                                                 |

| 8                                      | CKBP | Noninverting Input Clock for Channel B                                                                                                                              |

| 9                                      | CKBN | Inverting Input Clock for Channel B                                                                                                                                 |

| 12                                     | CKCN | Inverting Output Clock                                                                                                                                              |

| 13                                     | CKCP | Noninverting Output Clock                                                                                                                                           |

| 14                                     | D0CN | Inverting Output D0                                                                                                                                                 |

| 15                                     | D0CP | Noninverting Output D0                                                                                                                                              |

| 16, 31,<br>36, 40                      | Vcc  | Power-Supply Voltage. Bypass VCC to GND with low-ESR 10nF and 4.7µF ceramic capacitors in parallel as close as possible to the device. Recommended on each VCC pin. |

| 17                                     | D1CN | Inverting Output D1                                                                                                                                                 |

| PIN | NAME | FUNCTION                                                                                                    |

|-----|------|-------------------------------------------------------------------------------------------------------------|

| 18  | D1CP | Noninverting Output D1                                                                                      |

| 19  | D2CN | Inverting Output D2                                                                                         |

| 20  | D2CP | Noninverting Output D2                                                                                      |

| 22  | D2BP | Noninverting Input D2 for Channel B                                                                         |

| 23  | D2BN | Inverting Input D2 for Channel B                                                                            |

| 24  | D2AP | Noninverting Input D2 for Channel A                                                                         |

| 25  | D2AN | Inverting Input D2 for Channel A                                                                            |

| 27  | D1BP | Noninverting Input D1 for Channel B                                                                         |

| 28  | D1BN | Inverting Input D1 for Channel B                                                                            |

| 29  | D1AP | Noninverting Input D1 for Channel A                                                                         |

| 30  | D1AN | Inverting Input D1 for Channel A                                                                            |

| 33  | ADJ  | Output Level Adjust                                                                                         |

| 34  | SEL  | Mux Select Input. SEL is internally pulled down by a 400k $\Omega$ (typ) resistor.                          |

| 37  | EN2  | Active-Low Enable Input. $\overline{\text{EN2}}$ is internally pulled up by a 400k $\Omega$ (typ) resistor. |

| 38  | EN1  | Active-High Enable Input. EN1 is internally pulled down by a $400 \text{k}\Omega$ (typ) resistor.           |

| _   | EP   | Exposed Pad. Connect EP to GND.                                                                             |

# MIXIM MAX14886 D2AN · D2BN $\leq 50\Omega$ - D2CP D1AP -- D2CN D1AN -D1BP -- D1CP D1BN -- D1CN MULTIPLEXER/ LIMITING AMPLIFIER DOAP -- DOCP DOAN -- DOCN D0BP DOBN -- CKCN CKAP CKAN CKRP CKBN -CONTROL GND SEL

## **Functional Diagram/Truth Tables**

| EN1           | EN2           | FUNCTION |

|---------------|---------------|----------|

| 0/Unconnected | X             | Shutdown |

| X             | 1/Unconnected | Shutdown |

| 1             | 0             | Active   |

X = Don't care.

| SEL           | D_A_, CKA_ | D_B_, CKB_ |

|---------------|------------|------------|

| 0/Unconnected | On         | Off        |

| 1             | Off        | On         |

X = Don't care.

### **Detailed Description**

The MAX14886 is a high-speed, low-skew, active redriver multiplexer designed to switch and amplify TMDS-formatted signals. Input buffers have  $50\Omega$  HDMI-compliant terminations to VCC (see the Functional Diagram/Truth Tables), allowing either DC-coupling to an HDMI source or AC-coupling to a DisplayPort source. Signals from the input buffers are multiplexed and redriven by the limiting amplifier and an open-collector output buffer. The HDMI monitor sink is DC-coupled to the outputs and provides DC bias.

Both TMDS clock and data are multiplexed and redriven to full HDMI v.1.4 levels with low skew and jitter to guarantee mask compliance at an external HDMI connector. The device is VESA DisplayPort Interoperability Guideline v.1.1a-compliant and integrates seamlessly with an external HDMI connector on the motherboard. The low-frequency signals (DDC, CEC, and HPD) can be handled by external low-cost logic.

The device accommodates differential inputs as low as 200mV and drives differential TMDS outputs to 1000mV (typ). A precision resistor on the output level adjust pin (ADJ) allows differential output back-termination resistors of 400 $\Omega$  (typ) to better meet HDMI mask jitter compliance, while maintaining full TMDS swing requirements.

This device also features both active-high and active-low enable inputs. One of the enable inputs can be connected to either VCC or GND, while the other can be used to control the device (see the *Functional Diagram/Truth Tables* and *Enable Inputs (EN1, EN2)* section). This eliminates any issues with logic sense and the need for an inverter.

#### **Level Translation**

The device accepts two sets of four differential DisplayPort-level TMDS-formatted inputs, each with magnitudes as low as 200mV. The selected channel is translated to full HDMI TMDS levels that are HDMI v.1.4 port mask-compliant up to 2.25Gbps.

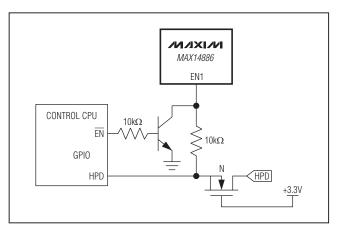

### Enable Inputs (EN1, EN2)

The device features both an active-high enable input (EN1) and an active-low enable input (EN2) that can be controlled by LVCMOS or LVTTL. EN1 has an internal 400k $\Omega$  (typ) pulldown resistor, and EN2 has an internal 400k $\Omega$  (typ) pullup resistor. When EN1 is driven low or left unconnected, or EN2 is driven high or left unconnected, the device enters low-power shutdown mode. For normal operation drive both EN1 high and EN2 low. See the Functional Diagram/Truth Tables.

Only one input is necessary to control the device. If active-high enable is desired, connect  $\overline{\text{EN2}}$  to GND and use EN1 to control the device. Similarly, for active-low enable, connect EN1 to VCC and use  $\overline{\text{EN2}}$  to control the device.

**Note:** The monitor sink termination must be present and powered before enabling the device (see the *Control Sequence* section and Figure 2).

### **Digital Control Input (SEL)**

The device provides two sets of 4 channels for all the differential signals required by HDMI connections. The SEL input controls which channel is translated to the output channel (see the *Functional Diagram/Truth Tables*). An internal 400k $\Omega$  pulldown resistor guarantees that channel A is translated to the output if the SEL pin is not externally driven.

### **Output Level Adjust (ADJ)**

The level-shifter's output current and output signal swing are set with an external  $\pm 1\%$  precision  $3.3k\Omega$  (typ) resistor. If a double output termination ( $400\Omega$  typ) is desired for signal integrity reasons, the ADJ resistor value can be decreased to maintain a desired output swing (Figure 1).

# Applications Information

#### **HDMI Driver**

The device's high-speed, low-skew, active redriver multiplexer is ideal for switching between outputs of dual-graphics systems and signal conditioning to meet HDMI v.1.4 compliance at an external HDMI connector (Figure 1). It is well suited for switching between integrated (e.g., Intel or AMD) and discrete graphics (e.g., NVIDIA or ATI GPU). The device is VESA DisplayPort Interoperability Guideline v.1.1a-compliant (requires external DDC logic) and integrates seamlessly with an external HDMI connector on the motherboard.

### **Output Termination**

Outputs are terminated in normal use by the HDMI monitor. For  $50\Omega$  test equipment purposes, terminate each output with a high-frequency bias-T that has an inductor in series with a  $50\Omega$  resistor to VCC.

#### **Control Sequence**

The monitor sink termination must be present and powered before enabling the device. A simple circuit can be added to protect the device by forcing hot-plug detection (HPD) to be present before the part is enabled (Figure 2).

Figure 1. HDMI Driver Application with Output Back Termination

Figure 2. Control Sequence Protection Circuit

### **Power-Supply Bypassing**

Adequate power-supply bypassing is necessary to maximize performance and noise immunity. Bypass each VCC pin to GND with high-frequency, low-ESR, X7R/X5R 10nF and 4.7 $\mu$ F surface-mount ceramic capacitors as close as possible to the device.

#### **Printed Circuit Board (PCB) Traces**

Input and output trace characteristics affect the performance of the device. Connect each of the inputs and outputs to a  $50\Omega$  characteristic impedance trace in to minimize reflections. Avoid discontinuities in differential impedance and maximize common-mode noise immunity by maintaining the distance between differential traces and avoiding sharp corners. Minimize the number of vias to prevent impedance discontinuities. Reduce reflections by maintaining the  $50\Omega$  characteristic impedance through connectors and across cables. Minimize skew by matching the electrical length of the traces.

#### **Exposed-Pad Package**

The exposed-pad, 40-pin TQFN package incorporates features that provide a very low thermal resistance path for heat removal from the IC. The exposed pad on the device must be soldered to the circuit board ground plane for proper electrical and thermal performance. For more information on exposed-pad packages, refer to Application Note 862: HFAN-08.1: Thermal Considerations of QFN and Other Exposed-Paddle Packages.

## **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE | LAND        |

|------------|---------|---------|-------------|

| TYPE       | CODE    | NO.     | PATTERN NO. |

| 40 TQFN-EP | T4055+2 | 21-0140 |             |

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 12/10         | Initial release | _                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.