Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **General Description**

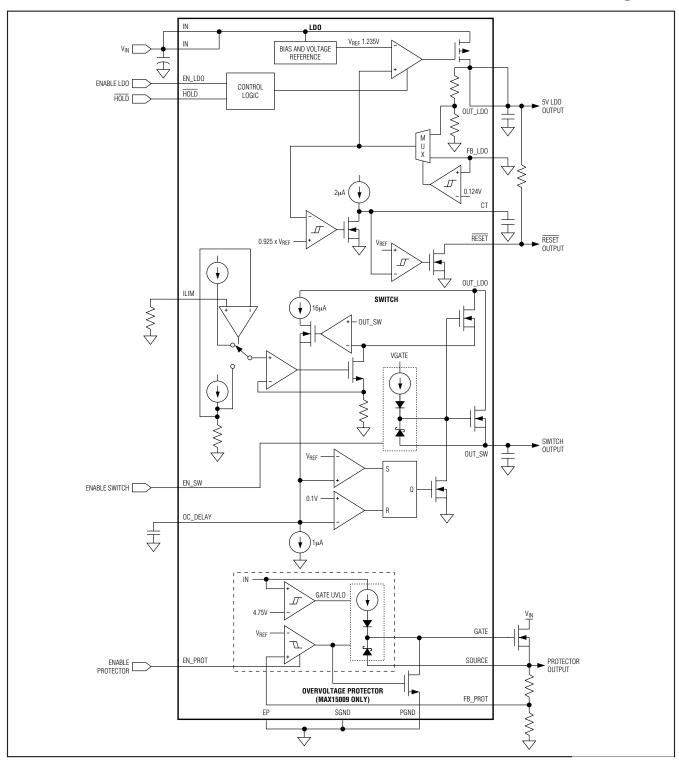

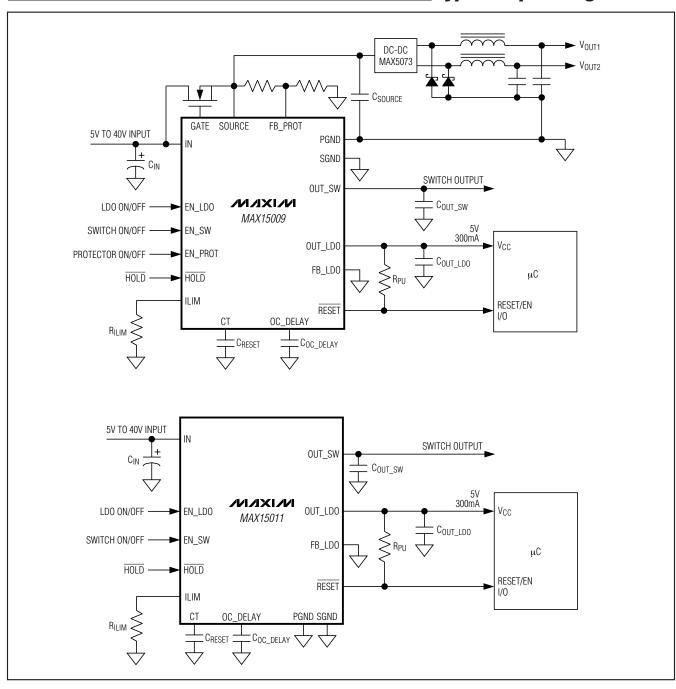

The MAX15009 includes a 300mA LDO regulator, a switched output, and an overvoltage protection (OVP) controller to protect downstream circuits from high-voltage load dump. The MAX15011 includes only the 300mA LDO regulator and switched output. Both devices operate over a wide supply voltage range from 5V to 40V and are able to withstand load-dump transients up to 45V. The MAX15009/MAX15011 feature short-circuit and thermalshutdown protection. These devices offer highly integrated power management solutions for automotive applications such as instrument clusters, climate control, and a variety of automotive power-supply circuits.

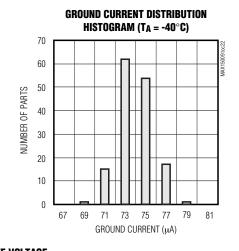

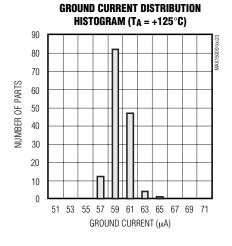

The 300mA LDO regulator consumes 67µA guiescent current at light loads and is well suited to power always-on circuits during "key off" conditions. The LDO features independent enable and hold inputs, as well as a microprocessor (µP) reset output with adjustable reset timeout period.

The switched output of the MAX15009/MAX15011 incorporates a low RDS(ON) (0.28 $\Omega$ , typ) pass transistor switch internally connected to the output of the LDO regulator. This switch features accurate current-limit sensing circuitry and is capable of controlling remote loads. The MAX15009/MAX15011 feature an adjustable current limit and a programmable delay timer to set the overcurrent detection blanking time of the switch and autoretry timeout.

The MAX15009 OVP controller operates with an external enhancement mode n-channel MOSFET. While the monitored voltage remains below the adjustable threshold, the MOSFET stays on. When the monitored voltage exceeds the OVP threshold, the OVP controller quickly turns off the external MOSFET. The OVP controller is configurable as a load-disconnect switch or a voltage limiter.

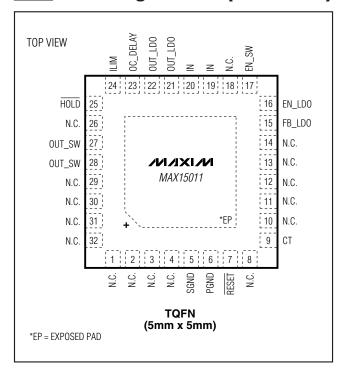

The MAX15009/MAX15011 are available in a thermally enhanced, 32-pin (5mm x 5mm), TQFN package and are fully specified over the -40°C to +125°C automotive operating temperature range.

#### **Applications**

Instrument Clusters Climate Control AM/FM Radio Power Supply Multimedia Power Supply **Telematics Power Supply**

Typical Operating Circuits and Selector Guide appear at end of data sheet.

#### **Features**

- 300mA LDO Regulator, Switched Output, and OVP Controller (MAX15009)

- ♦ 300mA LDO Regulator and Switched Output (MAX15011)

- ♦ 5V to 40V Wide Operating Supply Voltage Range

- **♦ 45V Load Dump Protection**

- ♦ 67µA Quiescent Current LDO Regulator

- **♦ OVP Controller Disconnects or Limits Output Voltage During Battery Overvoltage Conditions**

- ♦ LDO Regulator with Enable, Hold, and Reset **Features**

- ♦ Internal 0.28Ω (typ) n-Channel Switch for **Switched Output**

- **♦ 100mA Switched Output with Adjustable Current-Limit Blanking/Autoretry Delay**

# **Ordering Information**

| PART                 | TEMP RANGE      | PIN-<br>PACKAGE | PKG<br>CODE |

|----------------------|-----------------|-----------------|-------------|

| <b>MAX15009</b> ATJ+ | -40°C to +125°C | 32 TQFN-EP*     | T3255-4     |

| <b>MAX15011</b> ATJ+ | -40°C to +125°C | 32 TQFN-EP*     | T3255-4     |

+Denotes a lead-free package.

For tape and reel, add a T after "+."

\*EP = Exposed pad.

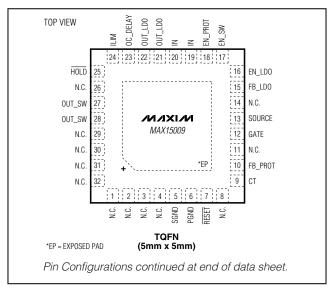

# **Pin Configurations**

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| (4)                                                                 |

|---------------------------------------------------------------------|

| (All pins referenced to SGND, unless otherwise noted.)              |

| IN, GATE0.3V to +45V                                                |

| EN_LDO, EN_SW, EN_PROT0.3V to (V <sub>IN</sub> + 0.3V)              |

| SOURCE0.3V to (V <sub>IN</sub> + 0.3V)                              |

| OUT_LDO, FB_LDO, FB_PROT, RESET,                                    |

| OC_DELAY0.3V to +12V                                                |

| GATE to SOURCE0.3V to +12V                                          |

| OUT_SW, ILIM, <del>HOLD</del> 0.3V to (V <sub>OUT_LDO</sub> + 0.3V) |

| OUT_SW to OUT_LDO12V to +0.3V                                       |

| CT to SGND0.3V to +12V                                              |

| SGND to PGND0.3V to +0.3V                                           |

| IN, OUT_LDO Current700mA                                            |

|                                                                     |

| OUT_SW Current                                        |         |

|-------------------------------------------------------|---------|

| Current Sink/Source (all remaining pins)              | 50mA    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |         |

| 32-Pin TQFN (derate 34.5mW/°C above +70°C)            | 2.7W    |

| Thermal Resistance                                    |         |

| θJA                                                   | ).0°C/W |

| θJC1                                                  | 1.7°C/W |

| Operating Temperature Range40°C to                    | +125°C  |

| Junction Temperature                                  | +150°C  |

| Storage Temperature Range60°C to                      | +150°C  |

| Lead Temperature (soldering, 10s)                     | +300°C  |

| *As per JEDEC 51 Standard, Multilayer Board (PCB).    |         |

"As per JEDEC 51 Standard, Multilayer Board (PCB).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +14V, \ V_{SGND} = V_{PGND} = 0V, \ C_{GATE} = 6000pF, \ C_{IN} = 10\mu F \ (ESR < 1.5\Omega), \ C_{OUT\_LDO} = 22\mu F \ (ceramic), \ C_{OUT\_SW} = 1\mu F, \ V_{OUT\_LDO} = 5V, \ C_{T} = open, \ T_{A} = T_{J} = -40^{\circ}C \ to \ +125^{\circ}C, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_{A} = +25^{\circ}C.) \ (Note \ 1)$

| PARAMETER                             | SYMBOL                 | CONDITIONS                                |                                                                                                                                         | MIN                                                                      | TYP  | MAX  | UNITS |    |

|---------------------------------------|------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|-------|----|

| Supply Voltage Range                  | VIN                    | V <sub>IN</sub> ≥ V <sub>OUT</sub> + 1.5V |                                                                                                                                         | 5                                                                        |      | 40   | V     |    |

| Supply Current                        |                        |                                           | EN_PRC<br>= 0µA, L                                                                                                                      | D = IN, EN_SW = DT = 0V, IOUT_LDO DO on, switch off, or off, measured ND |      | 67   | 85    |    |

|                                       |                        | MAX15009                                  | EN_LDO = EN_SW = IN,<br>EN_PROT = 0V, LDO ON,<br>IOUT_LDO = 100µA, switch<br>on, IOUT_SW = 0µA,<br>protector off, measured<br>from SGND |                                                                          |      | 290  | 360   | 4  |

|                                       | IIN                    |                                           | EN_LDO = EN_SW = EN_PROT = IN, LDO ON, IOUT_LDO = 100µA, switch on, IOUT_SW = 0µA, protector on, measured from SGND                     |                                                                          |      | 360  | 500   | μА |

|                                       |                        | MAX15011                                  | EN_LDO = EN_SW = IN,<br>LDO ON, I <sub>OUT_LDO</sub> =<br>100μA, switch on, I <sub>OUT_SW</sub><br>= 0μA, measured from<br>SGND         |                                                                          |      | 268  | 360   |    |

|                                       |                        |                                           | EN_LDO = EN_SW = TA = -40°C<br>EN_PROT = SGND, +85°C                                                                                    |                                                                          |      | 16   | 30    |    |

| Shutdown Supply Current               | ISHDN                  | measured from SGND                        |                                                                                                                                         | T <sub>A</sub> = -40°C to<br>+125°C                                      |      |      | 40    | μΑ |

| IN Undervoltage Lockout               | Vuvlo                  | V <sub>IN</sub> falling, G                | ATE disak                                                                                                                               | oled                                                                     | 4.10 | 4.27 | 4.45  | V  |

| IN Undervoltage Lockout<br>Hysteresis | V <sub>UVLO_HYST</sub> |                                           |                                                                                                                                         |                                                                          |      | 260  |       | mV |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=+14V,~V_{SGND}=V_{PGND}=0V,~C_{GATE}=6000pF,~C_{IN}=10\mu F~(ESR<1.5\Omega),~C_{OUT\_LDO}=22\mu F~(ceramic),~C_{OUT\_SW}=1\mu F,~V_{OUT\_LDO}=5V,~C_{T}=open,~T_{A}=T_{J}=-40^{\circ}C~to~+125^{\circ}C,~unless~otherwise~noted.~Typical~values~are~at~T_{A}=+25^{\circ}C.)~(Note~1)$

| PARAMETER                                                                                  | SYMBOL               | CONDITIONS                                                                                            | MIN         | TYP   | MAX   | UNITS |  |

|--------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|-------------|-------|-------|-------|--|

| Thermal-Shutdown Temperature                                                               | T <sub>SHDN</sub>    |                                                                                                       |             | +160  |       | °C    |  |

| Thermal Hysteresis                                                                         | THYST                |                                                                                                       |             | 20    |       | °C    |  |

| LDO                                                                                        |                      |                                                                                                       |             |       |       |       |  |

|                                                                                            |                      | I <sub>LOAD</sub> = 1mA, FB_LDO = SGND                                                                | 4.92        | 5.00  | 5.09  |       |  |

| Output Voltage                                                                             | Vout_ldo             | I <sub>LOAD</sub> = 300mA, V <sub>IN</sub> = 8V,<br>FB_LDO = SGND                                     | 4.88        | 5.00  | 5.11  | V     |  |

| FB_LDO Set-Point Voltage                                                                   | V <sub>FB_LDO</sub>  | With respect to SGND, I <sub>LOAD</sub> = 1mA,<br>V <sub>OUT_LDO</sub> = 5V, adjustable output option | 1.21        | 1.235 | 1.26  | V     |  |

| Dual Mode™ FB_LDO                                                                          | \/                   | FB_LDO rising                                                                                         |             | 0.125 |       | V     |  |

| Threshold                                                                                  | Vfb_ldo_th           | FB_LDO falling                                                                                        |             | 0.064 |       | V     |  |

| FB_LDO Input Current                                                                       | I <sub>FB_LDO</sub>  | V <sub>FB_LDO</sub> = 1V                                                                              | -100        |       | +100  | nA    |  |

| LDO Output Voltage                                                                         | V <sub>LDO_ADJ</sub> | Adjustable output option (Note 2)                                                                     | 1.8         |       | 11.0  | V     |  |

| LDO Dropout Voltago                                                                        | V <sub>DO</sub>      | I <sub>LOAD</sub> = 300mA (Note 3)                                                                    |             | 800   | 1500  | mV    |  |

| LDO Diopout voltage                                                                        | V DO                 | I <sub>LOAD</sub> = 200mA (Note 3)                                                                    |             | 520   | 1000  | 1117  |  |

| LDO Output Current                                                                         | lout_ldo             | (Note 4)                                                                                              | 300         |       |       | mA    |  |

| LDO Output Current Limit                                                                   | ILIM_LDO             | OUT_LDO = SGND, V <sub>IN</sub> = 6V                                                                  | 330         | 500   | 700   | mA    |  |

| LDO Output Current Limit  OUT_LDO Line Regulation                                          |                      | $6V \le V_{IN} \le 40V$ , $I_{LOAD} = 1mA$ ,<br>$V_{OUT\_LDO} = 5V$                                   |             | 0.03  | 0.2   |       |  |

|                                                                                            | ΔVουτ/               | $6V \le V_{IN} \le 40V$ , $I_{LOAD} = 1mA$ ,<br>FB_LDO = SGND, $V_{OUT\_LDO} = 3.3V$                  |             | 0.03  | 0.1   |       |  |

| OUT_EDO LINE REGUIATION                                                                    | ΔV <sub>IN</sub>     | 6V ≤ V <sub>IN</sub> ≤ 40V, I <sub>LOAD</sub> = 20mA,<br>FB_LDO = SGND, V <sub>OUT_LDO</sub> = 5V     |             | 0.27  | 1     | mV/V  |  |

| LDO Dropout Voltage  LDO Output Current  LDO Output Current Limit  OUT_LDO Line Regulation |                      | $6V \le V_{IN} \le 40V$ , $I_{LOAD} = 20$ mA,<br>$V_{OUT\_LDO} = 3.3V$                                |             | 0.27  | 0.5   |       |  |

| OUT I DO I and Doculation                                                                  | ΔVουτ/               | 1mA to 300mA, V <sub>IN</sub> = 8V,<br>FB_LDO = SGND                                                  |             | 0.054 | 0.15  | νο \  |  |

| OUT_LDO Load Regulation                                                                    | ΔΙΟυτ                | 1mA to 300mA, V <sub>IN</sub> = 6.3V,<br>V <sub>OUT_LDO</sub> = 3.3V                                  | 0.038 0.100 |       | mV/mA |       |  |

| OUT_LDO Power-Supply<br>Rejection Ratio                                                    | PSRR                 | I <sub>LOAD</sub> = 10mA, f = 100Hz, 500mV <sub>P-P</sub> ,<br>V <sub>OUT_LDO</sub> = 5V              |             | 60    |       | dB    |  |

| OUT_LDO Startup Delay<br>Time                                                              | tSTARTUP_DELAY       | IOUT_LDO = 0mA, from EN_LDO rising to 10% of VOUT_LDO (nominal), FB_LDO = SGND                        |             | 30    |       | μs    |  |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +14V, \ V_{SGND} = V_{PGND} = 0V, \ C_{GATE} = 6000pF, \ C_{IN} = 10\mu F \ (ESR < 1.5\Omega), \ C_{OUT\_LDO} = 22\mu F \ (ceramic), \ C_{OUT\_SW} = 1\mu F, \ V_{OUT\_LDO} = 5V, \ C_{T} = open, \ T_{A} = T_{J} = -40^{\circ}C \ to \ +125^{\circ}C, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_{A} = +25^{\circ}C.) \ (Note \ 1)$

| PARAMETER                                        | SYMBOL                  | CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNITS                 |

|--------------------------------------------------|-------------------------|----------------------------------------------------------------------------|-------|-------|-------|-----------------------|

| OUT_LDO Overvoltage<br>Protection Threshold      | V <sub>OV_</sub> TH     | 1mA sink from OUT_LDO                                                      |       | 105   | 110   | %Vout_LDO             |

| OUT_LDO Overvoltage<br>Protection Sink Current   | lov                     | V <sub>OUT_LDO</sub> = V <sub>OUT</sub> (nominal) x 1.15                   | 8     | 19    |       | mA                    |

| ENABLE/HOLD INPUTS                               |                         |                                                                            |       |       |       |                       |

| EN_LDO to EN_PROT Input                          | V <sub>IH</sub>         |                                                                            | 2     |       |       | V                     |

| Threshold Voltage                                | V <sub>IL</sub>         |                                                                            |       |       | 0.7   | V                     |

| EN_LDO, EN_PROT, EN_SW<br>Input Pulldown Current | I <sub>EN_PD</sub>      | EN_ is internally pulled low to SGND                                       |       | 1     |       | μА                    |

| HOLD Input Threshold                             | $V_{IH}$                |                                                                            | 1.4   |       |       | V                     |

| Voltage                                          | V <sub>IL</sub>         |                                                                            |       |       | 0.4   | V                     |

| HOLD Input Pullup                                | l <del>hold</del> _pu   | HOLD is internally pulled high to OUT_LDO                                  |       | 0.6   |       | μΑ                    |

| RESET                                            |                         |                                                                            |       |       |       |                       |

| RESET Voltage Threshold<br>HIGH                  | V <del>RESET</del> _H   | RESET goes HIGH when rising VOUT_LDO crosses this threshold, FB_LDO = SGND | 90.0  | 92.5  | 95.0  | %Vout_LDO             |

| HIGH                                             | -                       | RESET goes HIGH when rising VFB_LDO crosses this threshold                 | 90.0  | 92.5  | 95.0  | %V <sub>FB_LDO</sub>  |

| RESET Voltage Threshold                          | VRESET_L                | RESET goes LOW when falling VOUT_LDO crosses this threshold, FB_LDO = SGND | 88    | 90    | 92    | %Vout_LDO             |

| LOW                                              |                         | RESET goes LOW when falling VFB_LDO crosses this threshold                 | 88    | 90    | 92    | %V <sub>FB_LDO</sub>  |

| Vour_LDO to RESET Delay                          | <sup>t</sup> RESET_FALL | V <sub>OUT_LDO</sub> falling, 0.1V/μs                                      |       | 19    |       | μs                    |

| CT Ramp Current                                  | ICT                     | V <sub>CT</sub> = 0V                                                       | 1.50  | 2     | 2.35  | μΑ                    |

| CT Ramp Threshold                                | V <sub>CT_TH</sub>      | V <sub>CT</sub> rising                                                     | 1.190 | 1.235 | 1.270 | V                     |

| RESET Output-Voltage Low                         | V <sub>OL</sub>         | Isink = 1mA, output asserted                                               |       |       | 0.1   | V                     |

| RESET Open-Drain<br>Leakage Current              | ILEAK_RESET             | Output not asserted                                                        |       |       | 150   | nA                    |

| LOAD DUMP PROTECTOR                              | (MAX15009 only)         |                                                                            |       |       |       |                       |

| FB_PROT Threshold<br>Voltage                     | VTH_PROT                | FB_PROT rising                                                             | 1.20  | 1.235 | 1.27  | V                     |

| FB_PROT Threshold Hysteresis                     | V <sub>HYST</sub>       |                                                                            |       | 4     |       | %V <sub>TH_PROT</sub> |

| FB_PROT Input Current                            | I <sub>FB_PROT</sub>    | V <sub>FB_PROT</sub> = 1.4V                                                | -100  |       | +100  | nA                    |

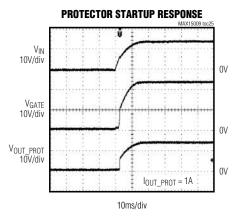

| Startup Response Time                            | tstart                  | EN_PROT rising, EN_LDO = IN, to VGATE = 0.5V                               |       | 20    |       | μs                    |

| GATE Rise Time                                   | tgate                   | GATE rising to +8V, VSOURCE = 0V                                           |       | 1     |       | ms                    |

\_\_\_\_\_\_\_*NIXI/*N

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +14V, \ V_{SGND} = V_{PGND} = 0V, \ C_{GATE} = 6000 pF, \ C_{IN} = 10 \mu F \ (ESR < 1.5 \Omega), \ C_{OUT\_LDO} = 22 \mu F \ (ceramic), \ C_{OUT\_SW} = 1 \mu F, \ V_{OUT\_LDO} = 5V, \ C_{T} = open, \ T_{A} = T_{J} = -40 ^{\circ}C \ to \ +125 ^{\circ}C, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_{A} = +25 ^{\circ}C.) \ (Note \ 1)$

| PARAMETER                                     | SYMBOL                              | CONDITIONS                                                                                                                                       | MIN                   | TYP                      | MAX                      | UNITS |

|-----------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|--------------------------|-------|

| FB_PROT to GATE Turn-Off Propagation Delay    | tov                                 | FB_PROT rising from V <sub>TH_PROT</sub> - 250mV to V <sub>TH_PROT</sub> + 250mV                                                                 |                       |                          | 0.6                      | μs    |

| GATE Output High Voltage                      | Vo. 177 VII.                        | $\begin{aligned} &V_{SOURCE} = V_{IN} = 5.5V, \\ &R_{GATE} \text{ to IN} = 1 \text{M}\Omega \end{aligned}$                                       | V <sub>IN</sub> + 3.2 | V <sub>IN</sub> +<br>3.5 | V <sub>IN</sub> +<br>3.8 | V     |

| GATE Output High Voltage                      | V <sub>GATE</sub> - V <sub>IN</sub> | $V_{SOURCE} = V_{IN}$ ; $V_{IN} \ge 14V$ , $R_{GATE}$ to $IN = 1MΩ$                                                                              | V <sub>IN</sub> + 7.0 | V <sub>IN</sub> +<br>8.1 | V <sub>IN</sub> +<br>9.5 | V     |

| GATE Output Pulldown<br>Current               | IGATEPD                             | V <sub>GATE</sub> = 5V, V <sub>EN_PROT</sub> = 0V                                                                                                |                       | 63                       | 100                      | mA    |

| GATE Charge-Pump<br>Current                   | IGATE                               | GATE = SGND                                                                                                                                      |                       | 45                       |                          | μΑ    |

| GATE-to-SOURCE Clamp<br>Voltage               | VCLMP                               |                                                                                                                                                  | 12                    | 16                       | 18                       | V     |

| SWITCH                                        |                                     |                                                                                                                                                  |                       |                          |                          |       |

| Switch Dropout                                | ΔV <sub>SW</sub>                    | ΔV <sub>SW</sub> = V <sub>OUT_LDO</sub> - V <sub>OUT_SW</sub> ,<br>I <sub>OUT_SW</sub> = 100mA, V <sub>OUT_LDO</sub> = 5V,<br>no external MOSFET |                       | 36                       | 70                       | mV    |

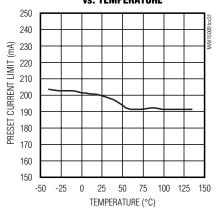

|                                               |                                     | ILIM = OUT_LDO, V <sub>IN</sub> = 8V                                                                                                             | 170                   | 200                      | 240                      |       |

| Switch Current Limit                          | I <sub>SW_LIM</sub>                 | $R_{LIM} = 100k\Omega$ to SGND,<br>$V_{OUT\_LDO} = 5V$ , $V_{IN} = 8V$                                                                           | 85                    | 100                      | 120                      | mA    |

|                                               |                                     | $R_{LIM} = 39k\Omega$ to SGND,<br>$V_{OUT\_LDO} = 5V$ , $V_{IN} = 8V$                                                                            | 30                    | 40                       | 50                       |       |

| Current-Limit Selector ILIM<br>Voltage        | VILIM                               | $R_{LIM} = 100k\Omega$                                                                                                                           |                       | 0.395                    |                          | V     |

| OC_DELAY Timeout<br>Threshold                 | VOC_DELAY                           |                                                                                                                                                  | 1.194                 | 1.235                    | 1.270                    | V     |

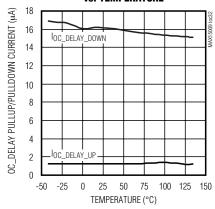

| OC_DELAY Timeout Pullup<br>Current            | IOC_DELAY_UP                        | VOC_DELAY = 0.5V rising                                                                                                                          | 12.5                  | 16.0                     | 21.3                     | μΑ    |

| OC_DELAY Timeout<br>Pulldown Current          | IOC_DELAY_DOWN                      | VOC_DELAY = 0.5V, falling                                                                                                                        | 0.75                  | 1.00                     | 1.40                     | μΑ    |

| Minimum OC_DELAY<br>Timeout                   | tOC_DELAY_MIN                       | Coc_delay is unconnected                                                                                                                         |                       | 12                       |                          | μs    |

| EN_SW to OUT_SW<br>Turn-On Time               |                                     | OUT_SW rising to +0.5V, $R_{OUT\_SW} = 1k\Omega$                                                                                                 |                       | 38                       |                          | μs    |

| EN_SW to OUT_SW<br>Turn-Off Propagation Delay | tov_sw                              | EN_SW falling, VouT_LDO - VouT_SW rising to +1V, ROUT_SW = $1k\Omega$ , VouT_LDO = $5V$                                                          |                       | 18                       |                          | μs    |

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

**Note 2:** 1.8V is the minimum limit for proper HOLD functionality.

Note 3: Dropout is defined as  $V_{IN}$  -  $V_{OUT\_LDO}$  when  $V_{OUT\_LDO}$  is 98% of the value of  $V_{OUT\_LDO}$  for  $V_{IN}$  =  $V_{OUT\_LDO}$  + 1.5V.

Note 4: Maximum output current may be limited by the power dissipation of the package.

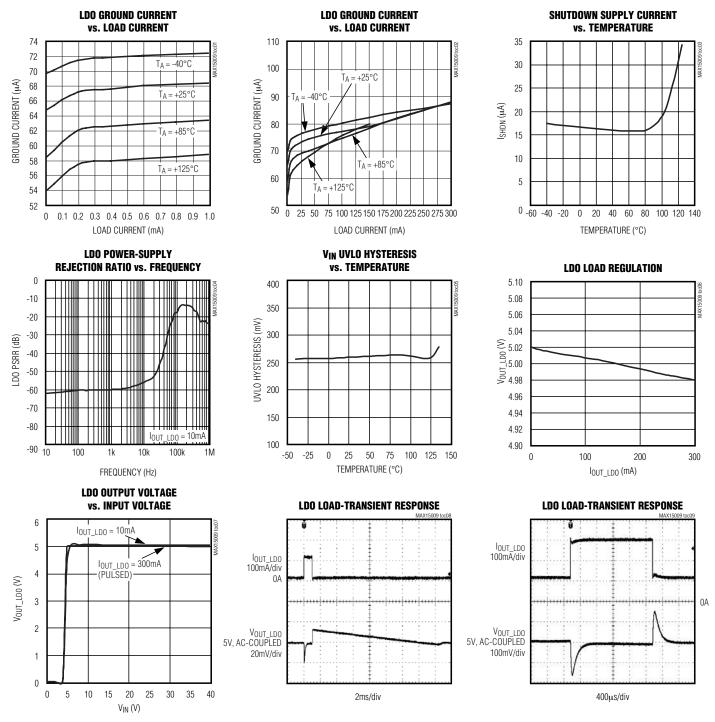

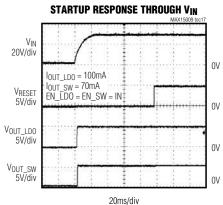

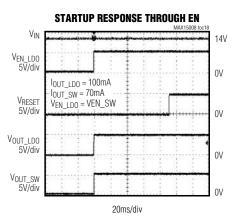

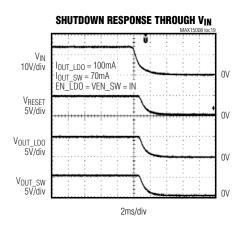

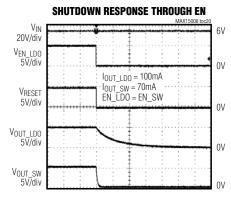

## **Typical Operating Characteristics**

$(V_{IN} = V_{EN\_LDO} = V_{EN\_PROT} = V_{EN\_SW} = +14V, C_{IN} = 10\mu\text{F}, C_{OUT\_LDO} = 22\mu\text{F}, C_{OUT\_SW} = 1\mu\text{F}, V_{OUT\_LDO} = +5V, FB\_LDO = SGND, T_A = +25^{\circ}C, unless otherwise specified.)$

# MAX15009/MAX15011

# Automotive 300mA LDO Regulators with Switched Output and Overvoltage Protector

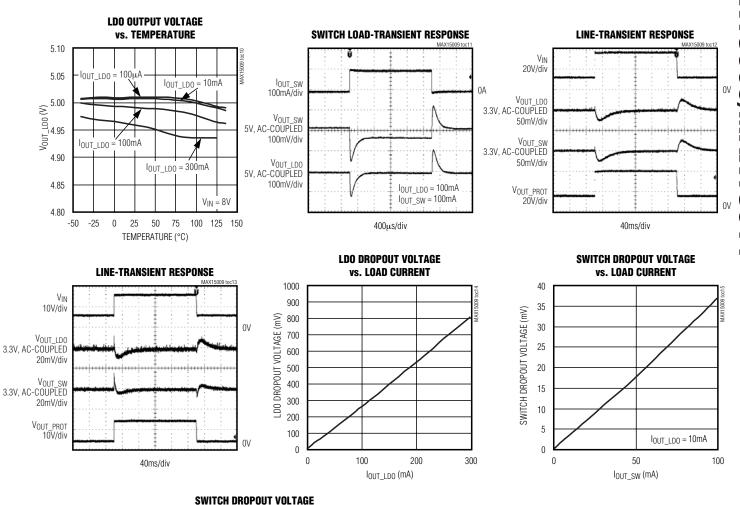

# Typical Operating Characteristics (continued)

$(V_{IN} = V_{EN\_LDO} = V_{EN\_PROT} = V_{EN\_SW} = +14V, C_{IN} = 10\mu\text{F}, C_{OUT\_LDO} = 22\mu\text{F}, C_{OUT\_SW} = 1\mu\text{F}, V_{OUT\_LDO} = +5V, FB\_LDO = SGND, T_A = +25^{\circ}C$ , unless otherwise specified.)

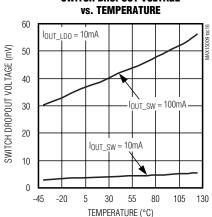

# Typical Operating Characteristics (continued)

$(V_{IN} = V_{EN\_LDO} = V_{EN\_PROT} = V_{EN\_SW} = +14V, C_{IN} = 10\mu\text{F}, C_{OUT\_LDO} = 22\mu\text{F}, C_{OUT\_SW} = 1\mu\text{F}, V_{OUT\_LDO} = +5V, FB\_LDO = SGND, T_A = +25^{\circ}C, unless otherwise specified.)$

# Typical Operating Characteristics (continued)

$(V_{IN} = V_{EN\_LDO} = V_{EN\_PROT} = V_{EN\_SW} = +14V, C_{IN} = 10\mu\text{F}, C_{OUT\_LDO} = 22\mu\text{F}, C_{OUT\_SW} = 1\mu\text{F}, V_{OUT\_LDO} = +5V, FB\_LDO = SGND, T_A = +25^{\circ}C, unless otherwise specified.)$

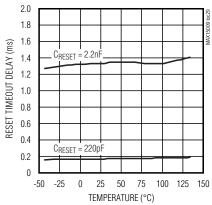

# RESET TIMEOUT DELAY vs. TEMPERATURE

# INTERNAL PRESET SWITCH CURRENT LIMIT vs. TEMPERATURE

# IOC\_DELAY\_UP AND IOC\_DELAY\_DOWN vs. TEMPERATURE

# **Pin Description**

| DIN                                | NA       | ME       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                                | MAX15009 | MAX15011 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1–4, 8, 11,<br>14, 26, 29–32       | N.C.     | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1–4, 8,<br>10–14, 18,<br>26, 29–32 | _        | N.C.     | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                         |

| 5                                  | SGND     | SGND     | Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6                                  | PGND     | PGND     | Ground. PGND is also the return path for the overvoltage protector pulldown current for the MAX15009. In this case, connect PGND to SGND at the negative terminal of the bypass capacitor connected to the source of the external MOSFET. For the MAX15011, connect PGND to SGND together to the local ground plane.                                                                                                             |

| 7                                  | RESET    | RESET    | Active-Low Open-Drain Reset Output. RESET is low while OUT_LDO is below the reset threshold. Once OUT_LDO has exceeded the reset threshold, RESET remains low for the duration of the reset timeout period then goes high.                                                                                                                                                                                                       |

| 9                                  | СТ       | СТ       | Reset Timeout Adjust Input. Connect a capacitor (CRESET) from CT to ground to adjust the reset timeout period. See the Setting the RESET Timeout Period section.                                                                                                                                                                                                                                                                 |

| 10                                 | FB_PROT  | _        | Overvoltage-Threshold Adjustment Input. Connect FB_PROT to an external resistive voltage-divider network to adjust the desired overvoltage threshold. Use FB_PROT to monitor a system input or output voltage. See the <i>Setting the Overvoltage Threshold (MAX15009 Only)</i> section.                                                                                                                                         |

| 12                                 | GATE     | _        | Protector Gate Drive Output. Connect GATE to the gate of an external n-channel MOSFET. GATE is the output of a charge pump with a 45µA pullup current to 8.1V (typ) above IN during normal operation. GATE is quickly turned off through a 63mA internal pulldown during an overvoltage condition. GATE then remains low until FB_PROT has decreased below 96% of the overvoltage threshold. GATE pulls low when EN_PROT is low. |

| 13                                 | SOURCE   | _        | Output-Voltage Sense Input. Connect SOURCE to the source of the external n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                       |

# Pin Description (continued)

| 5111   | NA       | ME       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN    | MAX15009 | MAX15011 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15     | FB_LDO   | FB_LDO   | LDO Voltage Feedback Input. Connect FB_LDO to SGND to select the preset +5V output voltage. Connect FB_LDO to an external resistive voltage-divider for adjustable output operation. See the <i>Setting the Output Voltage</i> section.                                                                                                                                                                                                                                                                                                              |

| 16     | EN_LDO   | EN_LDO   | Active-High LDO Enable Input. Connect EN_LDO to IN or to a logic-high voltage to turn on the regulator. To place the LDO in shutdown, pull EN_LDO low or leave unconnected and leave HOLD unconnected. EN_LDO is internally pulled to SGND through a 1µA current sink. See the <i>Control Logic</i> section.                                                                                                                                                                                                                                         |

| 17     | EN_SW    | EN_SW    | Active-High Switch Enable Input. Connect EN_SW to IN or to a logic-high voltage to turn on the switch. Pull EN_SW low or leave unconnected to place the switch in shutdown. EN_SW is internally pulled to SGND through a 1µA current sink.                                                                                                                                                                                                                                                                                                           |

| 18     | EN_PROT  | _        | Protector Enable Input. Drive EN_PROT low to force GATE low and turn off the external n-channel MOSFET. EN_PROT is internally pulled to SGND by a 1µA sink current. Connect EN_PROT to IN for normal operation.                                                                                                                                                                                                                                                                                                                                      |

| 19, 20 | IN       | IN       | Regulator Input. Bypass IN to SGND with a 10 $\mu$ F capacitor with an ESR < 1.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21, 22 | OUT_LDO  | OUT_LDO  | LDO Regulator Output. Bypass OUT_LDO to SGND with a ceramic capacitor with a minimum value of 22µF. OUT_LDO has a fixed 5V output or can be adjusted from1.8V to 11V. See the <i>Setting the Output Voltage</i> section.                                                                                                                                                                                                                                                                                                                             |

| 23     | OC_DELAY | OC_DELAY | Switch Overcurrent Blanking Time Programming Input. Leave OC_DELAY unconnected to select the minimum delay timeout before turning the switch off. OC_DELAY is internally pulled to SGND through a 1µA current source. See the Programming the Switch Overcurrent Blanking Time section.                                                                                                                                                                                                                                                              |

| 24     | ILIM     | ILIM     | Switch Current-Limit Set Input. Connect a $10k\Omega$ to $200k\Omega$ resistor from ILIM to SGND to select the current limit for the internal switch. Connect ILIM to OUT_LDO to select the internal 170mA (min) current-limit threshold. Do not leave ILIM unconnected. See the Setting the Switch Current Limit section.                                                                                                                                                                                                                           |

| 25     | HOLD     | HOLD     | Active-Low Hold Input. If EN_LDO is high when \$\overline{HOLD}\$ is forced low, the regulator latches the state of the EN_LDO input and allows the regulator to remain turned on when EN_LDO is subsequently pulled low. To shut down the regulator, release \$\overline{HOLD}\$ after EN_LDO is pulled low. If \$\overline{HOLD}\$ functionality is unused, connect \$\overline{HOLD}\$ to OUT_LDO or leave unconnected. \$\overline{HOLD}\$ is internally pulled up to OUT_LDO through a 0.6µA current source. See the \$Control Logic\$ section. |

| 27, 28 | OUT_SW   | OUT_SW   | Switch Output. Bypass OUT_SW to SGND with a minimum 0.1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| _      | EP       | EP       | Exposed Pad. Connect EP to SGND plane. EP also functions as a heatsink to maximize thermal dissipation. Do not use as the main ground connection.                                                                                                                                                                                                                                                                                                                                                                                                    |

## **Detailed Description**

The MAX15009/MAX15011 integrate a 300mA LDO voltage regulator, a current-limited switched output, and an OVP controller (MAX15009 only). These devices operate over a wide supply voltage range from 5V to 40V and are able to withstand load-dump transients up to 45V.

The MAX15009/MAX15011 feature a 300mA LDO regulator that consumes 70µA of current under light-load conditions and feature a fixed 5V or an adjustable output voltage (1.8V to 11V). Connect FB\_LDO to ground to select a fixed 5V output voltage or select the LDO output voltage by connecting an external resistive voltage-divider at FB\_LDO. The regulator sources at least 300mA of current and includes a current limit of 330mA (min). Enable the LDO by pulling EN\_LDO high.

The switch features accurate current-limit sensing circuitry and is capable of controlling remote loads. Once enabled, an internal charge pump generates the overdrive voltage for an internal MOSFET. The switch then starts to conduct and OUT\_SW is charged up to VOUT\_LDO. The switch is enabled when the output voltage of the LDO is above the RESET threshold voltage (92.5% of the LDO nominal output value).

An overcurrent condition exists when the current at OUT\_SW, IOUT\_SW, exceeds the 200mA (typ) internal factory-set current-limit threshold or the externally adjustable current-limit threshold. During a continuous overcurrent event, the capacitor connected at OC\_DELAY, Coc DELAY, is charged up to a voltage of 1.235V with a current, IOC DELAY UP. When this voltage is reached, an overcurrent latch is set and the gate of the internal MOSFET is discharged, reducing IOUT SW. Coc DFI AY is then discharged through a pulldown current, IOC DELAY DOWN (IOC DELAY UP / 16) and the internal MOSFET remains off until COC\_DELAY has been discharged to 0.1V. After this user-programmable turnoff delay, the switch turns back on. This charge/ discharge is repeated if the overcurrent condition persists. The switch returns to normal operation once the overcurrent condition has been removed.

The OVP controller (MAX15009 only) relies on an external MOSFET with adequate voltage rating (VDSS) to protect downstream circuitry from overvoltage transients. The OVP controller drives the gate of the external n-channel MOSFET, and is configurable to operate as an overvoltage protection switch or as a closed-loop voltage limiter.

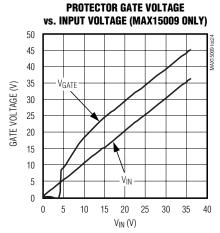

#### **GATE Voltage (MAX15009 Only)**

The MAX15009 uses a high-efficiency charge pump to generate the GATE voltage for the external n-channel MOSFET. Once the input voltage, VIN, exceeds the undervoltage lockout (UVLO) threshold, the internal charge pump fully enhances the external n-channel MOSFET. An overvoltage condition occurs when the voltage at FB\_PROT goes above the threshold voltage, VTH PROT. After VTH PROT is exceeded, GATE is quickly pulled to PGND with a 63mA pulldown current. The MAX15009 includes an internal clamp from GATE to SOURCE that ensures that the voltage at GATE never exceeds one diode drop below SOURCE during gate discharge. The voltage clamp also prevents the GATEto-SOURCE voltage from exceeding the absolute maximum rating for the VGS of the external MOSFET in case the source terminal is accidentally shorted to 0V.

#### Overvoltage Monitoring (MAX15009 Only)

The OVP controller monitors the voltage at FB\_PROT and controls an external n-channel MOSFET, isolating, or limiting the load during an overvoltage condition. Operation in OVP switch mode or limiter mode depends on the connection between FB\_PROT and the external MOSFET.

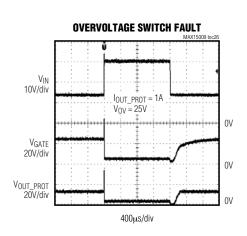

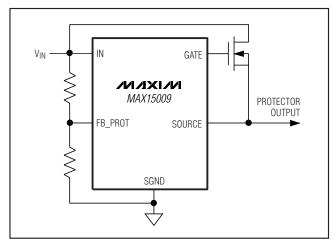

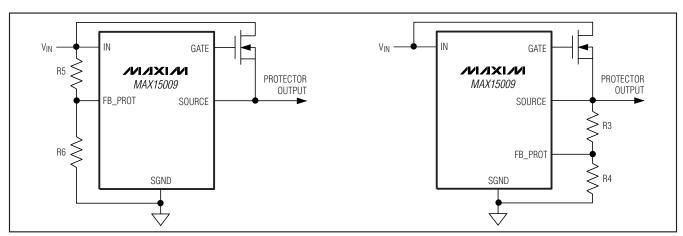

#### Overvoltage Switch Mode

When operating in OVP switch mode, the FB\_PROT divider is connected to the drain of the external MOS-FET. The feedback path consists of the voltage-divider tapped at FB\_PROT, FB\_PROT's internal comparator, the internal gate charge pump/gate pulldown, and the external n-channel MOSFET (Figure 1). When the programmed overvoltage threshold is exceeded, the internal comparator quickly pulls GATE to ground and turns

Figure 1. Overvoltage-Limiter Switch Configuration (MAX15009)

off the external MOSFET, disconnecting the power source from the load. In this configuration, the voltage at the source of the MOSFET is not monitored. When the voltage at FB\_PROT decreases below the overvoltage threshold, the MAX15009 raises the voltage at GATE, reconnecting the load to the power source.

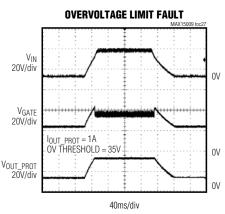

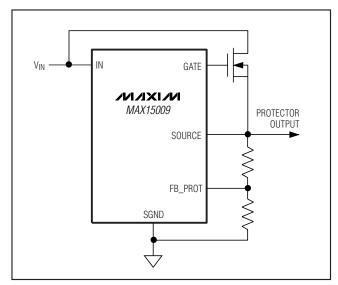

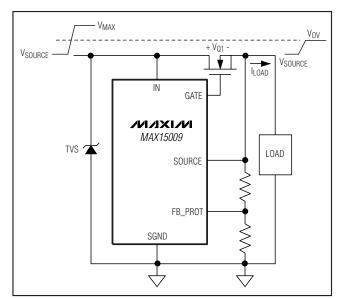

#### Overvoltage-Limiter Mode (MAX15009 Only)

When operating in overvoltage-limiter mode, the feedback path consists of SOURCE, FB\_PROT's internal comparator, the internal gate charge pump/gate pull-down, and the external n-channel MOSFET (Figure 2). This configuration results in the external MOSFET operating as a hysteretic voltage regulator.

During normal operation, GATE is enhanced 8.1V above VIN. The external MOSFET source voltage is monitored through a resistive voltage-divider between SOURCE and FB\_PROT. When VSOURCE exceeds the adjustable overvoltage threshold, an internal pulldown switch discharges the gate voltage and guickly turns the MOSFET off. Consequently, the source voltage begins to fall. The VSOURCE fall time is dependent on the MOS-FET's gate charge, the internal charge-pump current, the output load, and any load capacitance at SOURCE. When the voltage at FB\_PROT is below the overvoltage threshold by an amount equal to the hysteresis, the charge pump restarts and turns the MOSFET back on. In this way, the OVP controller attempts to regulate VSOURCE around the overvoltage threshold. SOURCE remains high during overvoltage transients and the MOSFET continues to conduct during an overvoltage event. The hysteresis of the FB\_PROT comparator and the gate turn-on delay force the external MOSFET to operate in a switched on/off sequence during an overvoltage event.

Exercise caution when operating the MAX15009 in voltage-limiting mode for long durations. Care must be taken against prolonged or repeated exposure to overvoltage events while delivering large amounts of load current as the power dissipation in the external MOSFET may be high under these conditions. To prevent damage to the MOSFET, implement proper heatsinking. The capacitor tied between SOURCE and ground may also be damaged if the ripple current rating for the capacitor is exceeded.

Figure 2. Overvoltage Limiter (MAX15009)

As the transient voltage decreases, the voltage at SOURCE falls. For fast-rising transients and very large MOSFETs, connect an additional capacitor from GATE to PGND. This capacitor acts as a voltage-divider working against the MOSFET's drain-to-gate capacitance. If using a very low gate charge MOSFET, additional capacitance from GATE to ground might be required to reduce the switching frequency.

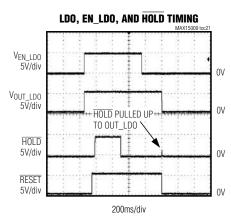

#### **Control Logic**

The MAX15009/MAX15011 LDO features two logic inputs, EN\_LDO and HOLD, making these devices suitable for automotive applications. For example, when the ignition key signal drives EN\_LDO high, the regulator turns on and remains on even if EN\_LDO goes low, as long as HOLD is forced low and stays low after initial regulator power-up. In this state, releasing HOLD turns the regulator output (OUT\_LDO) off. This feature makes it possible to implement a self-holding circuit without external components. Forcing EN\_LDO low and HOLD high (or unconnected) places the regulator into shutdown mode, reducing the supply current to less than 16μA. Table 1 shows the state of OUT\_LDO with respect to EN\_LDO and HOLD. Leave HOLD unconnected or connect directly to OUT\_LDO to allow the EN\_LDO input to act as a standard on/off logic input for the regulator.

\_ /VIXI/VI

Table 1. EN\_LDO/HOLD Truth/State Table

| OPERATION STATE  | EN_LDO | HOLD                | OUT_LDO | COMMENT                                                                                                                                       |

|------------------|--------|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Initial State    | Low    | Don't care          | OFF     | EN_LDO is pulled to SGND through an internal pulldown. HOLD is unconnected and is internally pulled up to OUT_LDO. The regulator is disabled. |

| Turn-On State    | High   | Don't care          | ON      | EN_LDO is externally driven high turning regulator on. HOLD is pulled up to OUT_LDO.                                                          |

| Hold Setup State | High   | Low                 | ON      | HOLD is externally pulled low while EN_LDO remains high (latches EN_LDO state).                                                               |

| Hold State       | Low    | Low                 | ON      | EN_LDO is driven low or left unconnected. HOLD remains externally pulled low keeping the regulator on.                                        |

| Off State        | Low    | High or unconnected | OFF     | HOLD is driven high or left unconnected while EN_LDO is low. The regulator is turned off and EN_LDO/HOLD logic returns to the initial state.  |

## **Applications Information**

#### **Load Dump**

Most automotive applications run off a multicell 12V lead-acid battery with a nominal voltage that swings between 9V and 16V, depending on load current, charging status, temperature, and battery age, etc. The battery voltage is distributed throughout the automobile and is locally regulated down to voltages required by the different system modules. Load dump occurs when the alternator is charging the battery and the battery becomes disconnected. Power in the alternator (behaving now essentially as an inductor) flows into the distributed power system and elevates the voltage seen at each module. The voltage spikes have rise times typically greater than 5ms and decay within several hundred milliseconds but can extend out to 1s or more depending on the characteristics of the charging system. These transients are capable of destroying semiconductors on the first fault event.

The MAX15009/MAX15011 feature load-dump transient protection up to +45V.

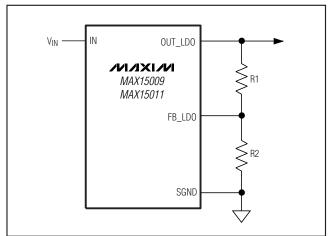

#### **Setting the Output Voltage**

The MAX15009/MAX15011 feature dual-mode operation: these devices operate in either a preset voltage mode or an adjustable mode. In preset voltage mode, internal feedback resistors set the linear regulator output voltage (Voutloo) to 5V. To select the preset 5V output voltage, connect FB\_LDO to SGND.

To select an adjustable output voltage between 1.8V and 11V, use two external resistors connected as a voltage-divider to FB\_LDO (Figure 3). Set the output voltage using the following equation:

Figure 3. Setting the LDO Output Voltage

$V_{OUT\_LDO} = V_{FB\_LDO} \times (R_1 + R_2) \, / \, R_2$  where  $V_{FB}$   $_{LDO} = 1.235 V$  and  $R_2 \le 50 k \Omega.$

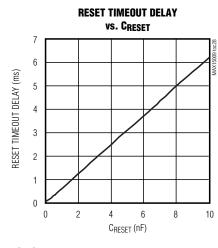

### Setting the RESET Timeout Period

The reset timeout period is adjustable to accommodate a variety of applications. Set the reset timeout period by connecting a capacitor,  $C_{RESET}$ , between CT and SGND. Use the following formula to select the reset timeout period,  $t_{RESET}$ :

treset = Creset x Vct\_th / Ict

where treset is in seconds and Creset is in  $\mu$ F. VCT\_TH is the CT ramp threshold in volts and IcT is the CT ramp current in  $\mu$ A, as described in the *Electrical Characteristics* table.

Leave CT open to select a typical reset timeout of  $19\mu s$ . To maintain reset accuracy, use a low-leakage type of capacitor.

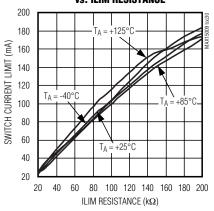

#### **Setting the Switch Current Limit**

The switch block features accurate current-limit sensing circuitry. A resistor connected from ILIM to SGND can be used to select the current-limit threshold using the following relationship:

ISW LIM (mA) = RILIM (k $\Omega$ ) x 1mA / k $\Omega$

where  $20k\Omega \le R_{ILIM} \le 200k\Omega$ .

Connect ILIM to OUT\_LDO to select the default current limit of 200mA (typ).

# **Programming the Switch Overcurrent Blanking Time**

The switch provides an adjustable overcurrent blanking time to allow the safe charge of large capacitive loads. When an overcurrent event is detected, a delay period elapses before the condition is latched and the internal MOSFET is turned off. This period is the overcurrent delay, toc\_Delay. Set the overcurrent delay using the following equation:

toc\_delay = Coc\_delay x Voc\_delay / loc\_delay\_up where toc\_delay is in seconds and Coc\_delay is in  $\mu F$ . Voc\_delay is the overcurrent delay timeout threshold voltage in volts and loc\_delay\_up is the overcurrent delay timeout pullup current in  $\mu A$  as seen in the Electrical Characteristics table.

Ensure that the switch is not disabled due to a large startup inrush current by selecting a large enough value for overcurrent blanking time. Assume that the current available for charging the total switch output capacitance, Cout\_sw, is the difference between the current-limit threshold value, Isw\_LIM, and the nominal

DC load current at OUT\_SW, IOUT\_SW\_NOM and select the COC\_DELAY using the following relationship:

$$C_{\text{OC\_DELAY}} \ge \frac{|\text{OC\_DELAY\_UP} \times \text{V}_{\text{OUT\_LDO}} \times \text{C}_{\text{OUT\_SW}}}{\text{V}_{\text{OC\_DELAY}} \times (|\text{Sw\_Lim} - |\text{OUT\_Sw\_NOM})}$$

COC\_DELAY also affects the length of time before the MAX15009/MAX15011 attempt to turn the switch back on. Set the autoretry delay using the following equation:

where toc\_RETRY is in seconds, Coc\_DELAY is in  $\mu$ F, Voc\_DELAY is in volts, and loc\_DELAY\_DOWN is in  $\mu$ A.

COC\_DELAY should be a low-leakage type of capacitor with a minimum value of 100pF.

# Setting the Overvoltage Threshold (MAX15009 Only)

The MAX15009 provides an accurate means to set the overvoltage threshold for the OVP controller using FB\_PROT. Use a resistive voltage-divider to set the desired overvoltage threshold (Figure 4). FB\_PROT has a rising 1.235V threshold with a 4% falling hysteresis.

Begin by selecting the total end-to-end resistance,  $RTOTAL = R_3 + R_4$ . Choose RTOTAL to yield a total current equivalent to a minimum of 100 x  $IFB\_PROT$  (FB\\_PROT's input maximum bias current) at the desired overvoltage threshold. See the *Electrical Characteristics* table.

#### For example:

With an overvoltage threshold (Vov) set to 20V, RTOTAL < 20V / (100 x IFB\_PROT), where IFB\_PROT is FB\_PROT's maximum 100nA bias current:

RTOTAL <  $2M\Omega$

Figure 4. Setting the Overvoltage Threshold (MAX15009)

Use the following formula to calculate R4:

R4 = VTH PROT X RTOTAL / VOV

where V<sub>TH\_PROT</sub> is the 1.235V FB\_PROT rising threshold and V<sub>OV</sub> is the desired overvoltage threshold.  $R_4 = 124k\Omega$ :

$RTOTAL = R_3 + R_4$

where  $R_3 = 1.88M\Omega$ . Use a standard  $1.87M\Omega$  resistor.

A lower value for total resistance dissipates more power, but provides better accuracy and robustness against external disturbances.

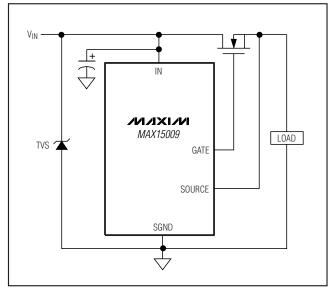

#### **Input Transients Clamping**

When the external MOSFET is turned off during an overvoltage event, stray inductance in the power path may cause additional input-voltage spikes that exceed the VDSS rating of the external MOSFET or the absolute maximum rating for the MAX15009. Minimize stray inductance in the power path using wide traces and minimize the loop area included by the power traces and the return ground path.

For further protection, add a zener diode or transient voltage suppressor (TVS) rated below the absolute maximum rating limits (Figure 5).

Figure 5. Protecting the MAX15009 Input from High-Voltage Transients

#### **External MOSFET Selection**

Select the external MOSFET with adequate voltage rating, VDSS, to withstand the maximum expected load-dump input voltage. The on-resistance of the MOSFET, RDS(ON), should be low enough to maintain a minimal voltage drop at full load, limiting the power dissipation of the MOSFET.

During regular operation, the power dissipated by the MOSFET is:

$$PNORMAL = ILOAD^2 \times RDS(ON)$$

Normally, this power loss is small and is safely handled by the MOSFET. However, when operating the MAX15009 in overvoltage limiter mode under prolonged or frequent overvoltage events, select an external MOSFET with an appropriate power rating.

During an overvoltage event, the power dissipation in the external MOSFET is proportional to both load current and to the drain-source voltage, resulting in high power dissipated in the MOSFET (Figure 6). The power dissipated across the MOSFET is:

where  $V_{Q1}$  is the voltage across the MOSFET's drain and source during overvoltage limiter operation, and  $I_{L\,OAD}$  is the load current.

Figure 6. Power Dissipated Across MOSFETs During an Overvoltage Fault (Overvoltage Limiter Mode)

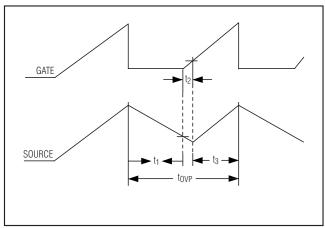

Figure 7. MAX15009 Timing Diagram

#### Overvoltage-Limiter Mode Switching Frequency

When the MAX15009 is configured in overvoltage-limiter mode, the external n-channel MOSFET is subsequently switched on and off during an overvoltage event. The output voltage at OUT\_PROT resembles a periodic sawtooth waveform. Calculate the period of the waveform, tovp, by summing three time intervals (Figure 7):

$$tOVP = t_1 + t_2 + t_3$$

where  $t_1$  is the V<sub>SOURCE</sub> output discharge time,  $t_2$  is the GATE delay time, and  $t_3$  is the V<sub>SOURCE</sub> output charge time.

During an overvoltage event, the power dissipated inside the MAX15009 is due to the gate pulldown current, IGATEPD. This amount of power dissipation is worse when ISOURCE = 0 (CSOURCE is discharged only by the internal current sink).

The worst-case internal power dissipation contribution in overvoltage limiter mode, POVP, in watts can be approximated using the following equation:

$$P_{OVP} = V_{OV} \times 0.98 \times I_{GATEPD} \times \frac{t_1}{t_{OVP}}$$

where Vov is the overvoltage threshold voltage in volts and IGATEPD is 100mA (max) GATE pulldown current.

#### Output Discharge Time (t<sub>1</sub>)

When the voltage at SOURCE exceeds the adjusted overvoltage threshold, GATE's internal pulldown is enabled until VSOURCE drops by 4%. The internal current sink, IGATEPD, and the external load current, ILOAD, discharge the external capacitance from SOURCE to ground.

Calculate the discharge time,  $t_1$ , using the following equation:

$$t_1 = C_{SOURCE} \times \frac{0.04 \times V_{OV}}{I_{LOAD} + I_{GATEPD}}$$

where  $t_1$  is in ms,  $V_{OV}$  is the adjusted overvoltage threshold in volts,  $I_{LOAD}$  is the external load current in mA, and  $I_{GATEPD}$  is the 100mA (max) internal pulldown current of GATE. CSOURCE is the value of the capacitor connected between the source of the MOSFET and PGND in  $\mu F$ .

#### GATE Delay Time (t<sub>2</sub>)

When SOURCE falls 4% below the overvoltage-threshold voltage, the internal current sink is disabled and the internal charge pump begins recharging the external GATE voltage. Due to the external load, the SOURCE voltage continues to drop until the gate of the MOSFET is recharged. The time needed to recharge GATE and reenhance the external MOSFET is approximately:

$$t_2 = C_{iss} \times \frac{V_{GS(TH)} + V_F}{I_{GATF}}$$

where t<sub>2</sub> is in µs,  $C_{iSS}$  is the input capacitance of the MOSFET in pF, and  $V_{GS(TH)}$  is the GATE-to-SOURCE threshold voltage of the MOSFET in volts. VF is the 0.7V (typ) internal clamp diode forward voltage of the MOSFET in volts, and  $I_{GATE}$  is the charge-pump current 45µA (typ). Any external capacitance between GATE and PGND adds up to  $C_{iSS}$ .

During t<sub>2</sub>, the SOURCE capacitance, C<sub>SOURCE</sub>, loses charge through the output load. The voltage across C<sub>SOURCE</sub>,  $\Delta$ V<sub>2</sub>, decreases until the MOSFET reaches its V<sub>GS(TH)</sub> threshold. Approximate  $\Delta$ V<sub>2</sub> using the following formula:

$$\Delta V_2 = \frac{I_{LOAD} \times t_2}{C_{SOURCE}}$$

#### SOURCE Output Charge Time (t<sub>3</sub>)

Once the GATE voltage exceeds the GATE-to-SOURCE threshold,  $V_{GS(TH)}$ , of the external MOSFET, the MOSFET turns on and the charge through the internal charge pump with respect to the drain potential, QG, determines the slope of the output voltage rise. The time required for the SOURCE voltage to rise again to the overvoltage threshold is:

$$t_3 = \frac{C_{rss} \times \Delta V_{SOURCE}}{I_{GATE}}$$

18 \_\_\_\_\_\_ /N/XI/M

where V<sub>SOURCE</sub> = (V<sub>OV</sub> x 0.04) + V<sub>2</sub> in volts, and  $C_{rss}$  is the MOSFET's reverse transfer capacitance in pF. Any external capacitance between GATE and PGND adds up to  $C_{rss}$ .

#### **Power Dissipation/Junction Temperature**

During normal operation, the MAX15009/MAX15011 have two main sources of internal power dissipation: the LDO and the switched output.

The internal power dissipation due to the LDO can be calculated as:

where V<sub>IN</sub> is the LDO input supply voltage in volts, V<sub>OUT\_LDO</sub> is the output voltage of the LDO in volts, I<sub>OUT\_LDO</sub> is the LDO total load current in mA, and I<sub>OUT</sub> sw is the switch load current in mA.

Calculate the power dissipation due to the switch as:

$$P_{SW} = \Delta V_{SW} \times I_{OUT}$$

SW

where  $\Delta V_{SW}$  is the switch dropout voltage in volts for the given  $I_{OUT}$  sw current in mA.

The total power dissipation PDISS in mW as:

For prolonged exposure to overvoltage events, use the V<sub>IN</sub> voltage expected during overvoltage conditions. Under these circumstances the corresponding internal power dissipation contribution, P<sub>OVP</sub>, calculated in the previous section should also be included in the total power dissipation, P<sub>DISS</sub>.

For a given ambient temperature,  $T_A$ , calculate the junction temperature,  $T_J$ , as follows:

$$T_J = T_A + P_{DISS} \times \theta_{JA}$$

where  $T_J$  and  $T_A$  are in °C and  $\theta_{JA}$  is the junction-to-ambient thermal resistance in °C/W as listed in the *Absolute Maximum Ratings* section.

The junction temperature should never exceed +150°C during normal operation.

#### **Thermal Protection**

When the junction temperature exceeds  $T_J = +160^{\circ}C$ , the MAX15009/MAX15011 shut down to allow the device to cool. When the junction temperature drops to  $+140^{\circ}C$ , the thermal sensor turns all enabled blocks on again, resulting in a cycled output during continuous thermal-overload conditions. Thermal protection protects the MAX15009/MAX15011 from excessive power dissipation. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $+150^{\circ}C$ .

# **Typical Operating Circuits**

# MAX15009/MAX15011

# Automotive 300mA LDO Regulators with Switched Output and Overvoltage Protector

# Pin Configurations (continued)

## \_Selector Guide

| PART     | LDO          | SWITCHED<br>OUTPUT | OVP<br>CONTROLLER |

|----------|--------------|--------------------|-------------------|

| MAX15009 | $\checkmark$ | $\checkmark$       | $\sqrt{}$         |

| MAX15011 | V            | V                  | _                 |

**Chip Information**

PROCESS: BICMOS

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |      |       |      |      |                 |      |      |                     |      |                     |         |                |      |      |      |

|-------------------|------|-------|------|------|-----------------|------|------|---------------------|------|---------------------|---------|----------------|------|------|------|

| PKG.              | 16   | L 5   | ×5   | 2    | 20L 5×5 28L 5×5 |      |      | 3                   | 2L 5 | 5×5                 | 40L 5×5 |                |      |      |      |

| SYMBOL            | MIN. | NDM.  | MAX. | MIN. | NDM.            | MAX. | MIN. | NDM.                | MAX. | MIN.                | NDM.    | MAX.           | MIN. | NDM. | MAX. |

| Α                 | 0.70 | 0.75  | 0.80 | 0.70 | 0.75            | 0.80 | 0.70 | 0.75                | 0.80 | 0.70                | 0.75    | 0.80           | 0.70 | 0.75 | 0.80 |

| A1                | 0    | 0.02  | 0.05 | 0    | 0.02            | 0.05 | 0    | 0.02                | 0.05 | 0                   | 0.02    | 0.05           | ٥    | 0.02 | 0.05 |

| A2                | 0.8  | 20 RE | F.   | 0.7  | 20 RE           | F.   | 0.2  | 20 RE               | F.   | 0.8                 | 20 RE   | REF. 0.20 REF. |      |      |      |

| b                 | 0.25 | 0.30  | 0.35 | 0.25 | 0.30            | 0.35 | 0.20 | 0.25                | 0.30 | 0.20                | 0.25    | 0.30           | 0.15 | 0.20 | 0.25 |

| D                 | 4.90 | 5.00  | 5.10 | 4.90 | 5.00            | 5.10 | 4.90 | 5.00                | 5.10 | 4.90                | 5.00    | 5.10           | 4.90 | 5.00 | 5.10 |

| E                 | 4.90 | 5.00  | 5.10 | 4.90 | 5.00            | 5.10 | 4.90 | 5.00                | 5.10 | 4.90                | 5.00    | 5.10           | 4.90 | 5.00 | 5.10 |

| e                 | 0.   | 80 B  | SC.  | 0.   | 65 B            | SC.  | 0.   | 0.50 BSC. 0.50 BSC. |      | 0.50 BSC. 0.40 BSC. |         |                |      |      |      |

| ĸ                 | 0.25 | -     | -    | 0.25 | 1               | -    | 0.25 | -                   | -    | 0.25                | -       | -              | 0.25 | -    | -    |

| ٦                 | 0.30 | 0.40  | 0.50 | 0.45 | 0.55            | 0.65 | 0.45 | 0.55                | 0.65 | 0.30                | 0.40    | 0.50           | 0.30 | 0.40 | 0.50 |

| N                 |      | 16    |      |      | 20              |      |      | 28                  |      | 32                  |         |                | 40   |      |      |

| ND                |      | 4     |      |      | 5               |      |      | 7                   |      | 8                   |         |                | 10   |      |      |

| NE                |      | 4     |      |      | 5               |      |      | 7                   |      | 8                   |         |                | 10   |      |      |

| JEDEC             |      |       |      |      | /HHD-           | 2    | -    |                     |      |                     |         |                |      |      |      |

| ιп | TE C. |  |

|----|-------|--|

| чu | I E S |  |

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- ⚠ DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- ⚠ COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR

- T2855-3, T2855-6, T4055-1 AND T4055-2. △OL WARPAGE SHALL NOT EXCEED 0.10 mm.

- 11. MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- ⚠ LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05.

- 14. ALL DIMENSIONS APPLY TO BOTH LEADED AND PHFREE PARTS.

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |

|------------------------|------|------|------|------|------|------|--|--|

| PKG.<br>CODES          | D2   |      |      | E2   |      |      |  |  |

|                        | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |  |  |

| T1655-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-5                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2055MN-5              | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-3                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2955-4                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-5                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2955-6                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-7                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-8                | 3.15 | 3.25 | 3.35 | 3.15 | 3,25 | 3.35 |  |  |

| T2855N-1               | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T3255-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255M-4               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-5                | 3.00 | 3.10 | 3,20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T4055-1                | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

| T4055-2                | 3,40 | 3,50 | 3.60 | 3,40 | 3.50 | 3.60 |  |  |

| T4055MN-1              | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

#

PACKAGE DUTLINE,

16,20,28,32,40L THIN QFN, 5x5x0.80mm

DOCUMENT CONTROL NO. 21-0140

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                             | PAGES<br>CHANGED |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 8/07          | Initial release                                                                                                                         | _                |

| 1                  | 1/08          | Removed future product asterisks, updated <i>Electrical Characteristics</i> table and <i>Typical Operating Characteristics</i> section. | 1, 2, 6, 8       |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.