Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **General Description**

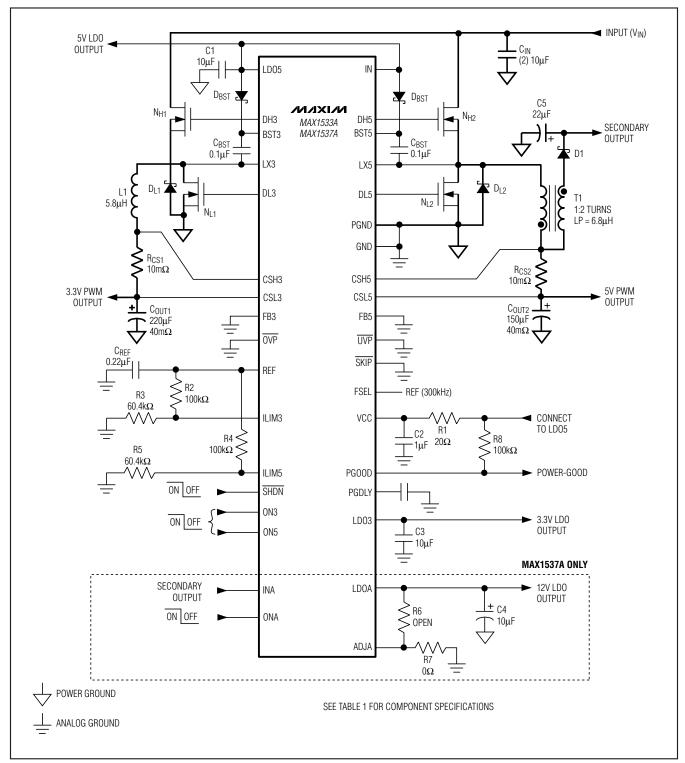

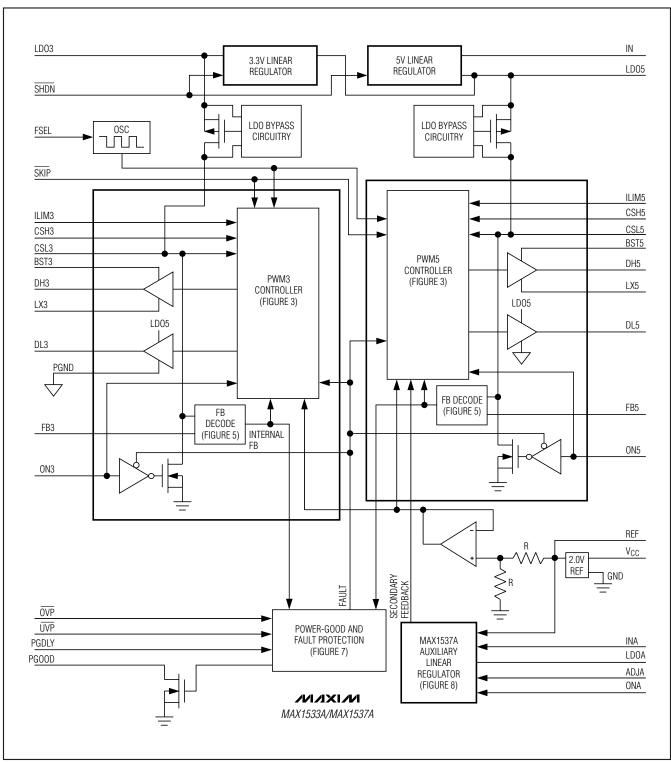

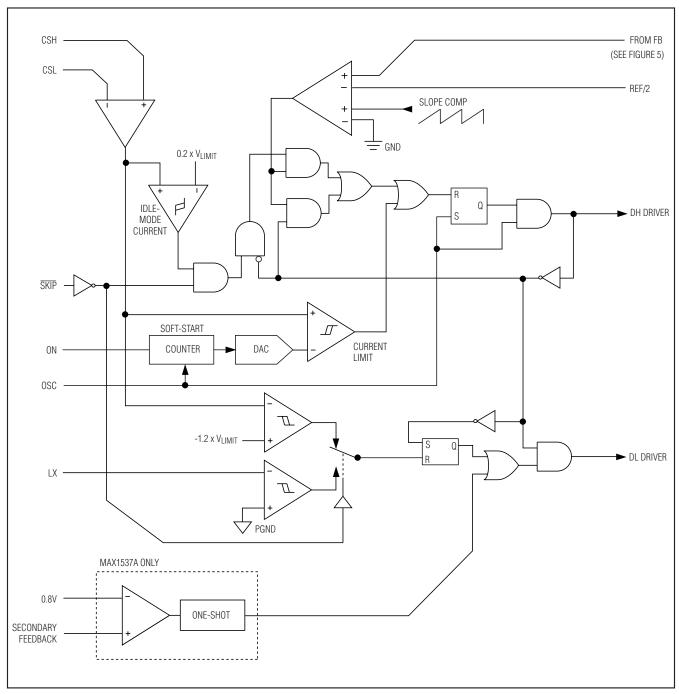

The MAX1533A/MAX1537A are dual step-down, switchmode power-supply (SMPS) controllers with synchronous rectification, intended for main 5V/3.3V power generation in battery-powered systems. Fixed-frequency operation with optimal interleaving minimizes input ripple current from the lowest input voltages up to the 26V maximum input. Optimal 40/60 interleaving allows the input voltage to go down to 8.3V before duty-cycle overlap occurs, compared to 180° out-of-phase regulators where the duty-cycle overlap occurs when the input drops below 10V. Output current sensing provides accurate current limit using a sense resistor. Alternatively, power dissipation can be reduced using lossless inductor current sensing.

Internal 5V and 3.3V linear regulators power the MAX1533A/MAX1537A and their gate drivers, as well as external keep-alive loads, up to a total of 100mA. When the main PWM regulators are in regulation, automatic bootstrap switches bypass the internal linear regulators, providing currents up to 200mA from each linear output. An additional 5V to 23V adjustable internal 150mA linear regulator is typically used with a secondary winding to provide a 12V supply.

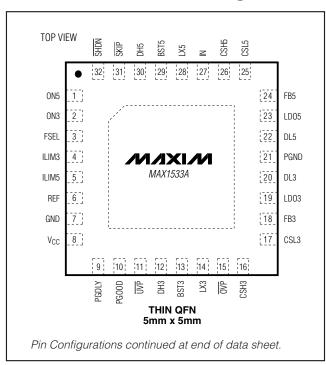

The MAX1533A/MAX1537A include on-board power-up sequencing, a power-good (PGOOD) output, digital soft-start, and internal soft-shutdown output discharge that prevents negative voltages on shutdown. The MAX1533A is available in a 32-pin 5mm x 5mm thin QFN package, and the MAX1537A is available in a 36pin 6mm x 6mm thin QFN package. The exposed backside pad improves thermal characteristics for demanding linear keep-alive applications.

## **Applications**

2 to 4 Li+ Cells Battery-Powered Devices Notebook and Subnotebook Computers PDAs and Mobile Communicators

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE           |

|--------------|----------------|-----------------------|

| MAX1533AETJ  | -40°C to +85°C | 32 Thin QFN 5mm x 5mm |

| MAX1533AETJ+ | -40°C to +85°C | 32 Thin QFN 5mm x 5mm |

| MAX1537AETX  | -40°C to +85°C | 36 Thin QFN 6mm x 6mm |

| MAX1537AETX+ | -40°C to +85°C | 36 Thin QFN 6mm x 6mm |

<sup>+</sup>Denotes lead-free package.

Dual Mode is a trademark of Maxim Integrated Products, Inc.

## **Features**

- ♦ Fixed-Frequency, Current-Mode Control

- ♦ 40/60 Optimal Interleaving

- **♦** Accurate Differential Current-Sense Inputs

- ♦ Internal 5V and 3.3V Linear Regulators with 100mA Load Capability

- ♦ Auxiliary 12V or Adjustable 150mA Linear Regulator (MAX1537A Only)

- ♦ Dual Mode™ Feedback—3.3V/5V Fixed or Adjustable Output (Dual Mode) Voltages

- ♦ 200kHz/300kHz/500kHz Switching Frequency

- ♦ Versatile Power-Up Sequencing

- ◆ Adjustable Overvoltage and Undervoltage **Protection**

- ♦ 6V to 26V Input Range

- ♦ 2V ±0.75% Reference Output

- ♦ Power-Good Output

- ♦ Soft-Shutdown

- ♦ 5µA (typ) Shutdown Current

## Pin Configurations

## **ABSOLUTE MAXIMUM RATINGS**

| IN, SHDN, INA, LDOA to GND         |                             |

|------------------------------------|-----------------------------|

| GND to PGND                        | 0.3V to +0.3V               |

| LDO5, LDO3, V <sub>CC</sub> to GND | 0.3V to +6V                 |

| ILIM3, ILIM5, PGDLY to GND         |                             |

| CSL3, CSH3, CSL5, CSH5 to GND      | 0.3V to +6V                 |

| ON3, ON5, FB3, FB5 to GND          | 0.3V to +6V                 |

| SKIP, OVP, UVP to GND              | 0.3V to +6V                 |

| PGOOD, FSEL, ADJA, ONA to GND.     | 0.3V to +6V                 |

| REF to GND                         | 0.3V to $(V_{CC} + 0.3V)$   |

| DL3, DL5 to PGND                   | 0.3V to $(V_{LDO5} + 0.3V)$ |

| BST3, BST5 to PGND                 | 0.3V to +36V                |

| LX3 to BST3                        | 6V to +0.3V                 |

| DH3 to LX3                         | 0.3V to $(V_{BST3} + 0.3V)$ |

|                                    |                             |

| LX5 to BST5                                | 6V to +0.3V                   |

|--------------------------------------------|-------------------------------|

| DH5 to LX5                                 | $0.3V$ to $(V_{BST5} + 0.3V)$ |

| LDO3, LDO5 Short Circuit to GND            | Momentary                     |

| REF Short Circuit to GND                   | Momentary                     |

| INA Shunt Current                          | +15mA                         |

| Continuous Power Dissipation ( $T_A = +70$ | O°C)                          |

| 32-Pin TQFN (derate 21.3mW/°C abo          | ve +70°C)1702mW               |

| 36-Pin TQFN (derate 26.3mW/°C abo          |                               |

| Operating Temperature Range                | 40°C to +85°C                 |

| Junction Temperature                       | +150°C                        |

| Storage Temperature Range                  | 65°C to +150°C                |

| Lead Temperature (soldering, 10s)          | +300°C                        |

|                                            |                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = 12V$ , both SMPS enabled,  $V_{CC} = 5V$ , FSEL = REF,  $\overline{SKIP} = GND$ ,  $V_{ILIM} = V_{LDO5}$ ,  $V_{INA} = 15V$ ,  $V_{LDOA} = 12V$ ,  $V_{LDO5} = V_{LDO5} = V_{L$

| PARAMETER                                | SYMBOL                | CONDITIONS                                                                                                          | MIN   | TYP   | MAX   | UNITS  |

|------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| INPUT SUPPLIES (Note 1)                  |                       |                                                                                                                     |       |       |       |        |

| V <sub>IN</sub> Input Voltage Range      | VIN                   | LDO5 in regulation                                                                                                  | 6     |       | 26    | \<br>\ |

| VIN Input voltage hange                  | VIN                   | IN = LDO5, V <sub>OUT5</sub> < 4.43V                                                                                | 4.5   |       | 5.5   | V      |

| V <sub>IN</sub> Operating Supply Current | I <sub>IN</sub>       | LDO5 switched over to CSL5                                                                                          |       | 15    | 35    | μΑ     |

| V <sub>IN</sub> Standby Supply Current   | I <sub>IN(STBY)</sub> | V <sub>IN</sub> = 6V to 26V, both SMPS off, includes ISHDN                                                          |       | 100   | 170   | μΑ     |

| V <sub>IN</sub> Shutdown Supply Current  | IN(SHDN)              | V <sub>IN</sub> = 6V to 26V, SHDN = GND                                                                             |       | 5     | 17    | μΑ     |

| Quiescent Power Consumption              | PQ                    | Both SMPS on, FB3 = FB5 = SKIP = GND, VCSL3 = 3.5V, VCSL5 = 5.3V, VINA = 15V, ILDOA = 0, PIN + PCSL3 + PCSL5 + PINA |       | 3.5   | 4.5   | mW     |

| V <sub>CC</sub> Quiescent Supply Current | Icc                   | Both SMPS on, FB3 = FB5 = GND,<br>V <sub>CSL3</sub> = 3.5V, V <sub>CSL5</sub> = 5.3V                                |       | 1.1   | 2.1   | mA     |

| MAIN SMPS CONTROLLERS                    |                       |                                                                                                                     |       |       |       |        |

| 3.3V Output Voltage in Fixed Mode        | V <sub>OUT3</sub>     | $V_{IN} = 6V$ to 26V, $\overline{SKIP} = V_{CC}$ (Note 2)                                                           | 3.280 | 3.33  | 3.380 | V      |

| 5V Output Voltage in Fixed Mode          | V <sub>OUT5</sub>     | V <sub>IN</sub> = 6V to 26V, SKIP = V <sub>CC</sub> (Note 2)                                                        | 4.975 | 5.05  | 5.125 | V      |

| Feedback Voltage in Adjustable<br>Mode   | V <sub>FB</sub> _     | V <sub>IN</sub> = 6V to 26V, FB3 or FB5,<br>duty factor = 20% to 80% (Note 2)                                       | 0.990 | 1.005 | 1.020 | V      |

| Output-Voltage Adjust Range              |                       | Either SMPS                                                                                                         | 1.0   |       | 5.5   | V      |

| FB3, FB5 Dual-Mode Threshold             |                       |                                                                                                                     | 0.1   |       | 0.2   | V      |

| Feedback Input Leakage Current           |                       | V <sub>FB3</sub> = V <sub>FB5</sub> = 1.1V                                                                          | -0.1  |       | +0.1  | μΑ     |

| DC Load Regulation                       |                       | Either SMPS, SKIP = V <sub>CC</sub> ,<br>I <sub>LOAD</sub> = 0 to full load                                         |       | -0.1  |       | %      |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1

| PARAMETER                                 | SYMBOL               | CONDITIONS                                                                    |                                                               | MIN  | TYP          | MAX       | UNITS |

|-------------------------------------------|----------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------|------|--------------|-----------|-------|

| Line-Regulation Error                     |                      | Either SMPS, duty                                                             | cycle = 10% to 90%                                            |      | 1            |           | %     |

|                                           |                      | FSEL = GND                                                                    | FSEL = GND                                                    |      | 200          | 230       |       |

| Operating Frequency (Note 1)              | fosc                 | FSEL = REF                                                                    |                                                               | 270  | 300          | 330       | kHz   |

|                                           |                      | FSEL = V <sub>CC</sub>                                                        |                                                               | 425  | 500          | 575       |       |

|                                           |                      | FSEL = GND                                                                    |                                                               | 91   | 93           |           |       |

| Maximum Duty Factor (Note 1)              | D <sub>MAX</sub>     | FSEL = REF                                                                    |                                                               | 91   | 93           |           | %     |

|                                           |                      | FSEL = V <sub>CC</sub>                                                        |                                                               | 91   | 93           |           |       |

| Minimum On-Time                           | ton(MIN)             | (Note 3)                                                                      |                                                               |      |              | 200       | ns    |

| SMPS3 to SMPS5 Phase Shift                |                      | SMPS5 starts afte                                                             | r SMPS3                                                       |      | 40           |           | %     |

| OWN GO TO GIVIN GO T FIELDE GITINE        |                      | Olvii 00 Starts arte                                                          | 1 OIVII OO                                                    |      | 144          |           | Deg   |

| CURRENT LIMIT                             |                      |                                                                               |                                                               |      |              |           |       |

| ILIM_ Adjustment Range                    |                      |                                                                               |                                                               | 0.5  |              | $V_{REF}$ | V     |

| Current-Sense Input Range                 |                      | CSH_, CSL_                                                                    |                                                               | 0    |              | 5.5       | V     |

| Current-Sense Input Leakage<br>Current    |                      | CSH_, V <sub>CSH</sub> _ = 5                                                  | .5V                                                           | -1   |              | +1        | μΑ    |

| Current-Limit Threshold (Fixed)           | V <sub>LIMIT</sub> _ | V <sub>CSH</sub> V <sub>CSL</sub> _, IL                                       | IM_ = V <sub>CC</sub>                                         | 70   | 75           | 80        | mV    |

|                                           |                      |                                                                               | V <sub>ILIM</sub> _ = 2.00V                                   | 170  | 200          | 230       |       |

| Current-Limit Threshold (Adjustable)      | V <sub>LIMIT</sub> _ | VCSH VCSL_                                                                    | V <sub>ILIM</sub> _ = 1.00V                                   | 91   | 100          | 109       | mV    |

|                                           |                      |                                                                               | $V_{ILIM} = 0.50V$                                            | 42   | 50           | 58        |       |

| Current-Limit Threshold (Negative)        | V <sub>NEG</sub>     | V <sub>CSH</sub> - V <sub>CSL</sub> , Sh<br>current limit                     | $\overline{\text{KIP}} = V_{CC}$ , percent of                 |      | -120         |           | %     |

| Current-Limit Threshold (Zero Crossing)   | V <sub>Z</sub> X     | V <sub>PGND</sub> - V <sub>LX</sub> , SK                                      | IP = GND, ILIM_ = V <sub>CC</sub>                             |      | 3            |           | mV    |

|                                           |                      |                                                                               | ILIM_ = VCC                                                   | 10   | 16           | 22        | mV    |

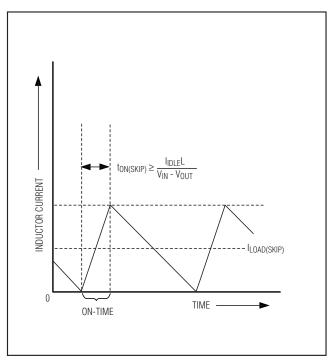

| Idle Mode™ Threshold                      | VIDLE                | VCSH VCSL_                                                                    | With respect to current-limit threshold (V <sub>LIMIT</sub> ) |      | 20           |           | %     |

| ILIM_ Leakage Current                     |                      | ILIM3 = ILIM5 = C                                                             | GND or V <sub>CC</sub>                                        | -0.1 |              | +0.1      | μΑ    |

| Soft-Start Ramp Time                      | tss                  | Measured from th                                                              | e rising edge of ON_ to                                       |      | 512/<br>fosc |           | S     |

| INTERNAL FIXED LINEAR REGUL               | ATORS                | •                                                                             |                                                               |      |              |           |       |

| LDO5 Output Voltage                       | V <sub>LDO5</sub>    | ON3 = ON5 = GND, 6V < V <sub>IN</sub> < 26V,<br>0 < I <sub>LDO5</sub> < 100mA |                                                               | 4.80 | 4.95         | 5.10      | V     |

| LDO5 Undervoltage-Lockout Fault Threshold |                      | Rising edge, hysteresis = 1%                                                  |                                                               | 3.75 | 4.0          | 4.25      | V     |

| LDO5 Bootstrap Switch Threshold           |                      | Rising edge of CS                                                             | SL5, hysteresis = 1%                                          | 4.41 |              | 4.75      | V     |

| LDO5 Bootstrap Switch<br>Resistance       |                      | LDO5 to CSL5, V <sub>0</sub><br>I <sub>LDO5</sub> = 50mA                      | CSL5 = 5V,                                                    |      | 0.75         | 3         | Ω     |

Idle Mode is a trademark of Maxim Integrated Products, Inc.

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                                                            | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| LDO3 Output Voltage                             | V <sub>LDO3</sub>       | Standby mode, 6V < V <sub>IN</sub> < 26V,<br>0 < I <sub>LOAD</sub> < 100mA                            | 3.20  | 3.35 | 3.42  | V     |

| LDO3 Bootstrap Switch Threshold                 |                         | Rising edge of CSL3, hysteresis = 1%                                                                  | 2.83  |      | 3.10  | V     |

| LDO3 Bootstrap Switch<br>Resistance             |                         | LDO3 to CSL3, V <sub>CSL3</sub> = 3.2V,<br>I <sub>LDO3</sub> = 50mA                                   |       | 1    | 3     | Ω     |

| Short-Circuit Current                           |                         | LDO3 = LDO5 = GND,<br>CSL3 = CSL5 = GND                                                               |       | 150  | 220   | mA    |

| Short-Circuit Current (Switched Over to CSL_)   |                         | LDO3 = LDO5 = GND, V <sub>CSL3</sub> > 3.1V,<br>V <sub>CSL5</sub> > 4.7V                              | 250   |      |       | mA    |

| AUXILIARY LINEAR REGULATOR                      | R (MAX1537A             | ONLY)                                                                                                 | •     |      |       |       |

| LDOA Voltage Range                              | V <sub>LDOA</sub>       |                                                                                                       | 5     |      | 23    | V     |

| INA Voltage Range                               | VINA                    |                                                                                                       | 6     |      | 24    | V     |

| LDOA Regulation Threshold,<br>Internal Feedback |                         | ADJA = GND, 0 < I <sub>LDOA</sub> < 120mA,<br>V <sub>INA</sub> > 13V                                  | 11.4  | 12.0 | 12.4  | V     |

| ADJA Regulation Threshold,<br>External Feedback | V <sub>ADJA</sub>       | 0 < I <sub>LDOA</sub> < 120mA, V <sub>LDOA</sub> > 5.0V and V <sub>INA</sub> > V <sub>LDOA</sub> + 1V | 1.94  | 2.00 | 2.06  | V     |

| ADJA Dual-Mode Threshold                        |                         |                                                                                                       | 0.1   | 0.15 | 0.2   | V     |

| ADJA Leakage Current                            |                         | V <sub>ADJA</sub> = 2.1V                                                                              | -0.1  |      | +0.1  | μΑ    |

| LDOA Current Limit                              |                         | V <sub>LDOA</sub> forced to V <sub>INA</sub> - 1V, V <sub>ADJA</sub> = 1.9V, V <sub>INA</sub> > 6V    | 150   |      |       | mA    |

| Secondary Feedback Regulation<br>Threshold      |                         | VINA - VLDOA                                                                                          | 0.65  | 0.8  | 0.95  | V     |

| DL Duty Factor                                  |                         | V <sub>INA</sub> - V <sub>LDOA</sub> < 0.7V, pulse width with respect to switching period             |       | 33   |       | %     |

| INA Quiescent Current                           | I <sub>INA</sub>        | V <sub>INA</sub> = 24V, I <sub>LDOA</sub> = no load                                                   |       | 50   | 165   | μΑ    |

| INA Shunt Sink Current                          |                         | V <sub>INA</sub> = 28V                                                                                | 10    |      |       | mA    |

| INA Leakage Current                             | INA(SHDN)               | V <sub>INA</sub> = 5V, LDOA disabled                                                                  |       |      | 30    | μΑ    |

| REFERENCE (REF)                                 |                         |                                                                                                       |       |      |       |       |

| Reference Voltage                               | V <sub>REF</sub>        | $V_{CC} = 4.5V \text{ to } 5.5V, I_{REF} = 0$                                                         | 1.985 | 2.00 | 2.015 | V     |

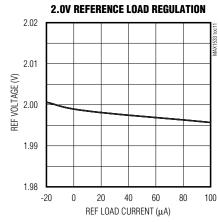

| Reference Load Regulation                       |                         | $I_{REF} = -10\mu A \text{ to } +100\mu A$                                                            | 1.980 |      | 2.020 | V     |

| REF Lockout Voltage                             | V <sub>REF</sub> (UVLO) | Rising edge, hysteresis = 350mV                                                                       |       | 1.95 |       | V     |

| FAULT DETECTION                                 |                         |                                                                                                       |       |      |       |       |

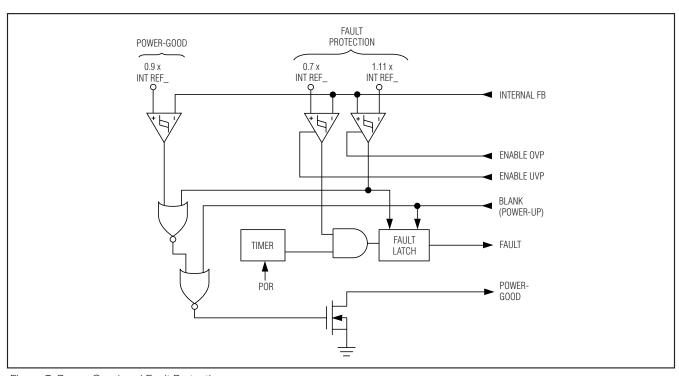

| Output Overvoltage Trip<br>Threshold            |                         | OVP = GND, with respect to error-<br>comparator threshold                                             | 8     | 11   | 15    | %     |

| Output Overvoltage Fault-<br>Propagation Delay  | tovp                    | 50mV overdrive                                                                                        |       | 10   |       | μs    |

· \_\_\_\_\_\_\_//////

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  = 1000 and  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 and  $V_{LDO5}$

| PARAMETER                                        | SYMBOL          | CONDITIONS                                                  |                | MIN                       | TYP           | MAX         | UNITS |

|--------------------------------------------------|-----------------|-------------------------------------------------------------|----------------|---------------------------|---------------|-------------|-------|

| Output Undervoltage-Protection<br>Trip Threshold |                 | With respect to error-compara                               | ator threshold | 65                        | 70            | 75          | %     |

| Output Undervoltage Fault-<br>Propagation Delay  | tuvp            | 50mV overdrive                                              |                |                           | 10            |             | μs    |

| Output Undervoltage-Protection Blanking Time     | tBLANK          | From rising edge of ON_                                     |                |                           | 6144/<br>fosc |             | S     |

| PGOOD Lower Trip Threshold                       |                 | With respect to error-compara<br>threshold, hysteresis = 1% | ator           | -14                       | -10           | -7.5        | %     |

| PGOOD Propagation Delay                          | tpgood_         | Falling edge, 50mV overdrive                                |                |                           | 10            |             | μs    |

| PGOOD Output Low Voltage                         |                 | I <sub>SINK</sub> = 4mA                                     |                |                           |               | 0.4         | V     |

| PGOOD Leakage Current                            | IPGOOD_         | High state, PGOOD forced to                                 | 5.5V           |                           |               | 1           | μΑ    |

| PGDLY Pullup Current                             |                 | PGDLY = GND                                                 |                | 4                         | 5             | 6           | μΑ    |

| PGDLY Pulldown Resistance                        |                 |                                                             |                |                           | 10            | 25          | Ω     |

| PGDLY Trip Threshold                             |                 |                                                             |                | REF-<br>0.2               | REF           | REF+<br>0.2 | V     |

| Thermal-Shutdown Threshold                       | TSHDN           | Hysteresis = 15°C                                           |                |                           | +160          |             | °C    |

| GATE DRIVERS                                     |                 |                                                             |                |                           |               |             |       |

| DH_ Gate-Driver On-Resistance                    | R <sub>DH</sub> | BST LX_ forced to 5V                                        |                |                           | 1.5           | 5           | Ω     |

|                                                  |                 | DL_, high state                                             |                | 1.7                       | 5             | 0           |       |

| DL_ Gate-Driver On-Resistance                    | R <sub>DL</sub> | DL_, low state                                              |                |                           | 0.6           | 3           | Ω     |

| DH_ Gate-Driver Source/Sink<br>Current           | lDH             | DH_ forced to 2.5V,<br>BST LX_ forced to 5V                 |                |                           | 2             |             | А     |

| DL_ Gate-Driver Source Current                   | I <sub>DL</sub> | DL_ forced to 2.5V                                          |                |                           | 1.7           |             | А     |

| DL_ Gate-Driver Sink Current                     | IDL (SINK)      | DL_ forced to 2.5V                                          |                |                           | 3.3           |             | Α     |

|                                                  |                 | DL_ rising                                                  |                |                           | 35            |             |       |

| Dead Time                                        | tDEAD           | DH_ rising                                                  |                |                           | 26            |             | ns    |

| LX_, BST_ Leakage Current                        |                 | V <sub>BST</sub> _ = V <sub>L</sub> X_ = 26V                |                |                           | <2            | 20          | μA    |

| INPUTS AND OUTPUTS                               | •               |                                                             |                | ı                         |               |             |       |

|                                                  |                 |                                                             | High           | 2.4                       |               |             |       |

| Logic Input Voltage                              |                 | SKIP, hysteresis = 600mV                                    | Low            |                           |               | 0.8         | V     |

| Fault Enable Logic Input Voltage                 |                 | OVP, UVP, ONA                                               | High           | 0.7 x<br>V <sub>C</sub> C |               |             | V     |

|                                                  |                 |                                                             | Low            |                           |               | 0.4         |       |

| Logic Input Current                              |                 | OVP, UVP, SKIP, ONA                                         |                | -1                        |               | +1          | μΑ    |

| CUDN logget Trip 11                              |                 | Rising trip level                                           |                | 1.10                      | 1.6           | 2.20        | 17    |

| SHDN Input Trip Level                            |                 | Falling trip level                                          |                | 0.96                      | 1             | 1.04        | V     |

|                                                  | 1               |                                                             | .1             |                           |               | 0.0         |       |

|                                                  |                 | Clear fault level/SMPS off leve                             | 91             |                           |               | 0.8         |       |

| ON_ Input Voltage                                |                 | Clear fault level/SMPS off level Delay start level (REF)    | 91             | 1.9                       |               | 2.1         | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDOA}$  =

| PARAMETER                                               | SYMBOL     | CONDITIONS                                 | MIN                    | TYP | MAX | UNITS |

|---------------------------------------------------------|------------|--------------------------------------------|------------------------|-----|-----|-------|

|                                                         |            | High                                       | V <sub>C</sub> C - 0.2 |     |     |       |

| FSEL Three-Level Input Logic                            |            | REF                                        | 1.7                    |     | 2.3 | V     |

|                                                         |            | GND                                        |                        |     | 0.4 | ]     |

| Janut Laglage Current                                   |            | OVP, UVP, SKIP, ONA, ON3, ON5 = GND or VCC | -1                     |     | +1  |       |

| Input Leakage Current                                   |            | SHDN, 0V or 26V                            | -1                     |     | +1  | μA    |

|                                                         |            | FSEL = GND or V <sub>CC</sub>              | -3                     |     | +3  |       |

| CSL_ Discharge-Mode<br>On-Resistance                    | RDISCHARGE |                                            |                        | 10  | 25  | Ω     |

| CSL_ Synchronous-Rectifier Discharge-Mode Turn-On Level |            |                                            | 0.2                    | 0.3 | 0.4 | V     |

## **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  =  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 1000 = 1000,  $V_{INA}$  = 15V,  $V_{LDO5}$  = 1000 = 1000,  $V_{LDO5}$  = 1

| PARAMETER                                     | SYMBOL                              | CONDITIONS                                                                                                                | MIN   | MAX   | UNITS |

|-----------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|

| INPUT SUPPLIES (Note 1)                       |                                     |                                                                                                                           |       |       |       |

| V <sub>IN</sub> Input Voltage Range           | VIN                                 | LDO5 in regulation                                                                                                        | 6     | 26    | V     |

| VIN Input voitage hange                       | VIN                                 | IN = LDO5, V <sub>OUT5</sub> < 4.4V                                                                                       | 4.5   | 5.5   | V     |

| V <sub>IN</sub> Operating Supply Current      | I <sub>IN</sub>                     | LDO5 switched over to CSL5, either SMPS on                                                                                |       | 35    | μΑ    |

| V <sub>IN</sub> Standby Supply Current        | I <sub>IN</sub> (STBY)              | V <sub>IN</sub> = 6V to 26V, both SMPS off, includes I <sub>SHDN</sub>                                                    |       | 170   | μΑ    |

| V <sub>IN</sub> Shutdown Supply Current       | IN(SHDN)                            | V <sub>IN</sub> = 6V to 26V                                                                                               |       | 17    | μΑ    |

| Quiescent Power Consumption                   | PQ                                  | Both SMPS on, FB3 = FB5 = SKIP = GND,<br>VCSL3 = 3.5V, VCSL5 = 5.3V, VINA = 15V,<br>ILDOA = 0, PIN + PCSL3 + PCSL5 + PINA |       | 4.5   | mW    |

| V <sub>CC</sub> Quiescent Supply Current      | Icc                                 | Both SMPS on, FB3 = FB5 = GND,<br>V <sub>CSL3</sub> = 3.5V, V <sub>CSL5</sub> = 5.3V                                      |       | 2.5   | mA    |

| MAIN SMPS CONTROLLERS                         |                                     |                                                                                                                           |       |       |       |

| 3.3V Output Voltage in Fixed Mode             | V <sub>О</sub> ТЗ                   | V <sub>IN</sub> = 6V to 26V, $\overline{\text{SKIP}}$ = V <sub>CC</sub> (Note 2)                                          | 3.28  | 3.38  | V     |

| 5V Output Voltage in Fixed Mode               | V <sub>OUT5</sub>                   | $V_{IN} = 6V$ to 26V, $\overline{SKIP} = V_{CC}$ (Note 2)                                                                 | 4.975 | 5.125 | V     |

| Feedback Voltage in<br>Adjustable Mode        | V <sub>FB3</sub> , V <sub>FB5</sub> | V <sub>IN</sub> = 6V to 26V, FB3 or FB5,<br>duty factor = 20% to 80% (Note 2)                                             | 0.982 | 1.018 | V     |

| Output-Voltage Adjust Range                   |                                     | Either SMPS                                                                                                               | 1.0   | 5.5   | V     |

| FB3, FB5 Adjustable-Mode<br>Threshold Voltage |                                     | Dual-mode comparator                                                                                                      | 0.1   | 0.2   | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  =  $V_{LDO5}$  =

| PARAMETER                                       | SYMBOL               | co                                                                                                       | ONDITIONS                                                                     | MIN   | MAX              | UNITS |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|------------------|-------|

|                                                 |                      | FSEL = GND                                                                                               |                                                                               | 170   | 230              |       |

| Operating Frequency (Note 1)                    | fosc                 | FSEL = REF                                                                                               | FSEL = REF                                                                    |       | 330              | kHz   |

|                                                 |                      | FSEL = V <sub>CC</sub>                                                                                   |                                                                               | 375   | 575              |       |

|                                                 |                      | FSEL = GND                                                                                               |                                                                               | 91    |                  |       |

| Maximum Duty Factor (Note 1)                    | D <sub>MAX</sub>     | FSEL = REF                                                                                               |                                                                               | 91    |                  | %     |

|                                                 |                      | FSEL = V <sub>CC</sub>                                                                                   |                                                                               | 91    |                  |       |

| Minimum On-Time                                 | ton(MIN)             |                                                                                                          |                                                                               |       | 250              | ns    |

| CURRENT LIMIT                                   |                      |                                                                                                          |                                                                               |       |                  |       |

| ILIM_ Adjustment Range                          |                      |                                                                                                          |                                                                               | 0.5   | V <sub>REF</sub> | V     |

| Current-Limit Threshold (Fixed)                 | V <sub>LIMIT</sub> _ | V <sub>CSH</sub> V <sub>CSL</sub> _, IL                                                                  | IM_ = VCC                                                                     | 67    | 83               | mV    |

|                                                 |                      |                                                                                                          | V <sub>ILIM</sub> _ = 2.00V                                                   | 170   | 230              |       |

| Current-Limit Threshold (Adjustable)            | V <sub>LIMIT</sub> _ | V <sub>CSH</sub> V <sub>CSL</sub> _                                                                      | V <sub>ILIM</sub> _ = 1.00V                                                   | 90    | 110              | mV    |

| (Adjustable)                                    |                      |                                                                                                          | V <sub>ILIM</sub> _ = 0.50V                                                   | 40    | 60               |       |

| INTERNAL FIXED LINEAR REGU                      | JLATORS              |                                                                                                          |                                                                               |       |                  |       |

| LDO5 Output Voltage                             | V <sub>LDO5</sub>    |                                                                                                          | ON3 = ON5 = GND, 6V < V <sub>IN</sub> < 26V,<br>0 < I <sub>LDO5</sub> < 100mA |       | 5.1              | V     |

| LDO5 Undervoltage-Lockout<br>Fault Threshold    |                      | Rising edge, hyste                                                                                       | eresis = 1%                                                                   | 3.75  | 4.30             | V     |

| LDO3 Output Voltage                             | V <sub>LDO3</sub>    | Standby mode, 6\<br>0 < I <sub>LOAD</sub> < 100m                                                         |                                                                               | 3.20  | 3.43             | V     |

| AUXILIARY LINEAR REGULATO                       | R (MAX1537)          | A ONLY)                                                                                                  |                                                                               |       |                  | I.    |

| LDOA Voltage Range                              | V <sub>LODA</sub>    |                                                                                                          |                                                                               | 5     | 23               | V     |

| INA Voltage Range                               | VINA                 |                                                                                                          |                                                                               | 6     | 24               | V     |

| LDOA Regulation Threshold,<br>Internal Feedback |                      | ADJA = GND, 0 <<br>V <sub>INA</sub> > 13V                                                                | I <sub>LDOA</sub> < 120mA,                                                    | 11.40 | 12.55            | V     |

| ADJA Regulation Threshold,<br>External Feedback | Vadja                | 0 < I <sub>LDOA</sub> < 120mA, V <sub>LDOA</sub> > 5.0V and<br>V <sub>INA</sub> > V <sub>LDOA</sub> + 1V |                                                                               | 1.94  | 2.08             | V     |

| ADJA Dual-Mode Threshold                        |                      | ADJA                                                                                                     | ADJA                                                                          |       | 0.25             | V     |

| Secondary Feedback<br>Regulation Threshold      |                      | VINA - VLDOA                                                                                             |                                                                               | 0.63  | 0.97             | V     |

| INA Quiescent Current                           | I <sub>INA</sub>     | V <sub>INA</sub> = 24V, I <sub>LDOA</sub> = no load                                                      |                                                                               |       | 165              | μΑ    |

| REFERENCE (REF)                                 |                      |                                                                                                          |                                                                               |       |                  |       |

| Reference Voltage                               | V <sub>REF</sub>     | $V_{CC} = 4.5V \text{ to } 5.5$                                                                          | V, I <sub>REF</sub> = 0                                                       | 1.97  | 2.03             | V     |

|                                                 |                      | 7.112                                                                                                    |                                                                               |       |                  | ·     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN}$  = 12V, both SMPS enabled,  $V_{CC}$  = 5V, FSEL = REF,  $\overline{SKIP}$  = GND,  $V_{ILIM}$  =  $V_{LDO5}$ ,  $V_{INA}$  = 15V,  $V_{LDOA}$  = 12V,  $V_{LDO5}$  =  $V_{LDO5}$  = 15V,  $V_{LDO5}$  = 12V,  $V_{LDO5}$  = 12V,

| PARAMETER                                        | SYMBOL           | CONDITIONS                                      | MIN              | MAX                   | UNITS       |          |

|--------------------------------------------------|------------------|-------------------------------------------------|------------------|-----------------------|-------------|----------|

| FAULT DETECTION                                  |                  |                                                 |                  |                       |             |          |

| Output Overvoltage Trip<br>Threshold             |                  | OVP = GND, with respect to comparator threshold | error-           | +8                    | +15         | %        |

| Output Undervoltage-Protection<br>Trip Threshold |                  | With respect to error-compa                     | rator threshold  | +65                   | +75         | %        |

| PGOOD Lower Trip Threshold                       |                  | With respect to error-compa hysteresis = 1%     | rator threshold, | -14.0                 | -7.0        | %        |

| PGOOD Output Low Voltage                         |                  | I <sub>SINK</sub> = 4mA                         |                  |                       | 0.4         | V        |

| PGDLY Pulldown Resistance                        |                  |                                                 |                  |                       | 25          | Ω        |

| PGDLY Trip Threshold                             |                  |                                                 |                  | REF-<br>0.2           | REF+<br>0.2 | V        |

| GATE DRIVERS                                     | 1.               |                                                 |                  | •                     |             | •        |

| DH_ Gate-Driver On-Resistance                    | R <sub>DH</sub>  | BST LX_ forced to 5V                            |                  |                       | 5           | Ω        |

| DL_ Gate-Driver On-Resistance                    | D <sub>D</sub> , | DL_, high state                                 |                  |                       | 5           | Ω        |

| DL_ Gate-Driver On-nesistance                    | R <sub>DL</sub>  | DL_, low state                                  |                  |                       | 3           | 52       |

| INPUTS AND OUTPUTS                               |                  |                                                 |                  |                       |             |          |

| Logic Input Voltage                              | ļ                | SKIP, hysteresis = 600mV                        | High             | 2.4                   |             | V        |

| Logic input voltage                              |                  | Orth, mysteresis = dooniv                       | Low              |                       | 8.0         | v        |

| Fault Enable Logic Input Voltage                 |                  | OVP, UVP, ONA                                   | High             | 0.7 x<br>VCC          |             | V        |

|                                                  |                  |                                                 | Low              |                       | 0.4         |          |

| SHDN Input Trip Level                            |                  | Rising trip level                               |                  | 1.1                   | 2.2         | V        |

| Show input trip Level                            |                  | Falling trip level                              |                  | 0.95                  | 1.05        | V        |

|                                                  |                  | Clear fault level                               |                  |                       | 0.8         |          |

| ON_ Input Voltage                                |                  | SMPS off level                                  |                  |                       | 1.6         | V        |

| ON_INPUT VOITage                                 |                  | Delay start level (REF)                         |                  | 1.9                   | 2.1         | <u> </u> |

|                                                  |                  | SMPS on level                                   |                  | 2.4                   |             |          |

|                                                  |                  | High                                            |                  | V <sub>CC</sub> - 0.2 |             |          |

| FSEL Three-Level Input Logic                     |                  | REF                                             |                  | 1.7                   | 2.3         | V        |

|                                                  |                  | GND                                             |                  |                       | 0.4         |          |

- Note 1: The MAX1533A/MAX1537A cannot operate over all combinations of frequency, input voltage (V<sub>IN</sub>), and output voltage. For large input-to-output differentials and high-switching frequency settings, the required on-time may be too short to maintain the regulation specifications. Under these conditions, a lower operating frequency must be selected. The minimum on-time must be greater than 150ns, regardless of the selected switching frequency. On-time and off-time specifications are measured from 50% point to 50% point at the DH\_ pin with LX\_ = GND, VBST\_ = 5V, and a 250pF capacitor connected from DH\_ to LX\_. Actual in-circuit times may differ due to MOSFET switching speeds.

- Note 2: When the inductor is in continuous conduction, the output voltage has a DC regulation level lower than the error-comparator threshold by 50% of the ripple. In discontinuous conduction (SKIP = GND, light load), the output voltage has a DC regulation level higher than the trip level by approximately 1% due to slope compensation.

- Note 3: Specifications are guaranteed by design, not production tested.

- Note 4: Specifications to -40°C are guaranteed by design, not production tested.

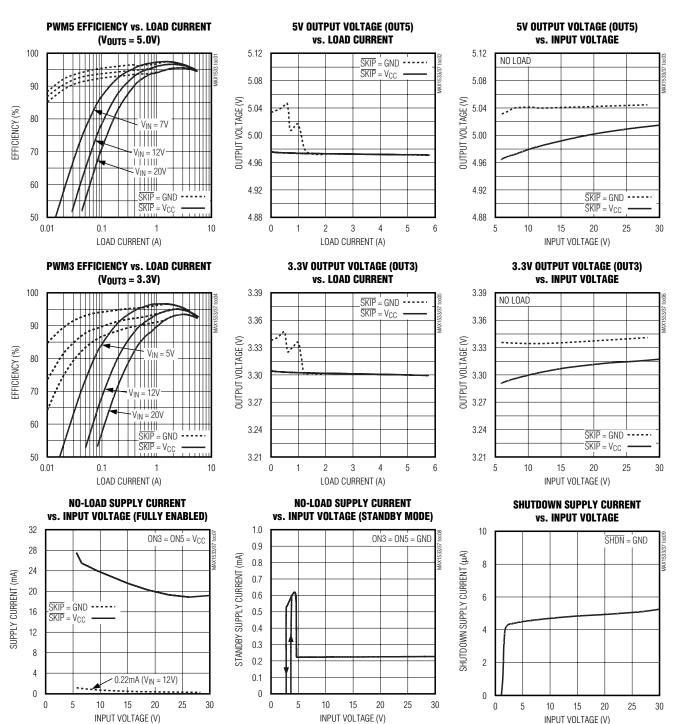

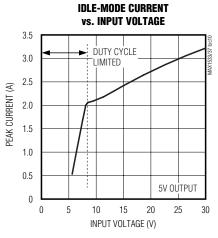

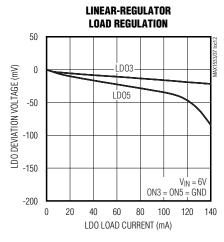

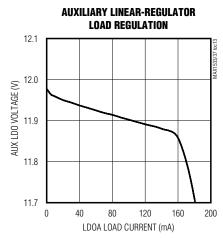

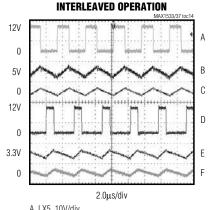

## **Typical Operating Characteristics**

(MAX1537A circuit of Figure 1, V<sub>IN</sub> = 12V, LDO5 = V<sub>CC</sub> = 5V, SKIP = GND, FSEL = REF, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(MAX1537A circuit of Figure 1, V<sub>IN</sub> = 12V, LDO5 = V<sub>CC</sub> = 5V, SKIP = GND, FSEL = REF, T<sub>A</sub> = +25°C, unless otherwise noted.)

- A. LX5, 10V/div

- B. 5V OUTPUT, 100mV/div

- C. PWM5 INDUCTOR CURRENT, 5A/div

- D. LX3, 10V/div

- E. 3.3V OUTPUT, 100mV/div

- F. PWM3 INDUCTOR CURRENT, 5A/div

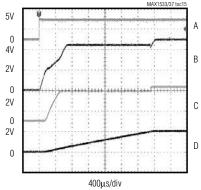

### LINEAR-REGULATOR STARTUP WAVEFORMS

- A. SHDN, 5V/div

- B. LD05, 2V/div

- C. LD03, 2V/div

- D. REF, 2V/div

- $100\Omega$  LOAD ON LD05 AND LD03

## Typical Operating Characteristics (continued)

2V

(MAX1537A circuit of Figure 1, V<sub>IN</sub> = 12V, LDO5 = V<sub>CC</sub> = 5V, SKIP = GND, FSEL = REF, T<sub>A</sub> = +25°C, unless otherwise noted.)

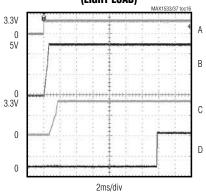

### **DELAYED STARTUP WAVEFORM** (LIGHT LOAD)

- A. ON5, 5V/div B. 5V OUTPUT, 2V/div

- C. 3.3V OUPUT, 2V/div

- D PGOOD 2V/div

- $100\Omega$  LOAD ON OUT5 AND OUT3, ON3 = REF

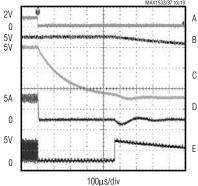

## STARTUP WAVEFORM (HEAVY LOAD)

- A. ON5. 5V/div

- B. 5V OUTPUT, 2V/div

- C. INDUCTOR CURRENT, 5A/div

- D. LD05, 1V/div

- E. DL5. 5V/div

- $1.0\Omega$  LOAD

SHUTDOWN WAVEFORM (NO LOAD)

- A. SHDN, 5V/div B. 5V OUTPUT, 5V/div C. DL5. 5V/div

- D. 3.3V OUTPUT, 5V/div E. DL3, 5V/div

- F. PGOOD, 5V/div  $\text{ON3} = \text{ON5} = \text{V}_{\text{CC}}, \, \overline{\text{OVP}} = \text{GND}$

## SHUTDOWN WAVEFORM (1 $\Omega$ LOAD)

- A. SHDN, 5V/div

- B. LD05. 2V/div

- C. 5V OUTPUT, 2V/div

- D. INDUCTOR CURRENT, 5A/div

- E. DL5, 5V/div

- $ON3 = ON5 = V_{CC}, \overline{OVP} = GND$

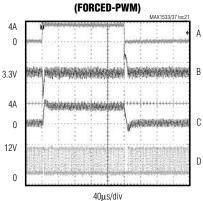

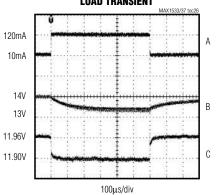

#### **5V OUTPUT LOAD TRANSIENT** (FORCED-PWM)

- A. I<sub>OUT5</sub> = 0.2A TO 4A, 5A/div

- B. V<sub>OUT5</sub> = 5.0V, 100mV/div

- C. INDUCTOR CURRENT, 5A/div

- D. LX5, 10V/div

- $\overline{SKIP} = V_{CC}$

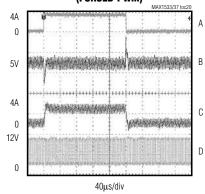

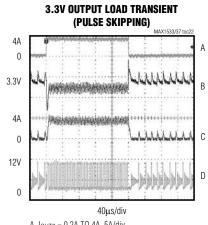

## 3.3V OUTPUT LOAD TRANSIENT

- A. I<sub>OUT3</sub> = 0.2A TO 4A, 5A/div B.  $V_{OUT3} = 3.3V$ , 100 mV/div

- C. INDUCTOR CURRENT, 5A/div

- D. LX3, 10V/div

- SKIP = Vcc

## Typical Operating Characteristics (continued)

(MAX1537A circuit of Figure 1,  $V_{IN}$  = 12V, LDO5 =  $V_{CC}$  = 5V,  $\overline{SKIP}$  = GND, FSEL = REF,  $T_A$  = +25°C, unless otherwise noted.)

A. I<sub>OUT3</sub> = 0.2A TO 4A, 5A/div B.  $V_{OUT3} = 3.3V$ , 100 mV/divC. INDUCTOR CURRENT, 5A/div D. LX3, 10V/div  $\overline{SKIP} = GND$

E. LX3, 20V/div

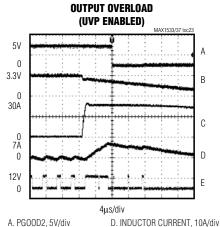

B. 3.3V OUTPUT, 3.3V/div C. LOAD (0 TO 30A), 20A/div

В

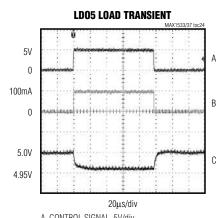

A. CONTROL SIGNAL, 5V/div B. I<sub>LD05</sub> = 1mA TO 100mA, 100mA/div C. LD05, 50m/div ON3 = ON5 = GND

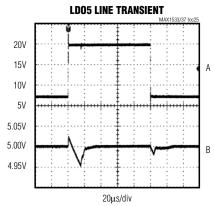

A. INPUT VOLTAGE ( $V_{IN} = 7V \text{ TO } 20V$ ), 5V/divB. LD05 OUTPUT VOLTAGE, 50mV/div  $0N3 = 0N5 = GND, I_{LD05} = 20mA$

#### **AUXILIARY LINEAR-REGULATOR LOAD TRANSIENT**

A. I<sub>LDOA</sub> = 10mA TO 100mA, 100mA/div B. INA. 1V/div C. LDOA, 50mV/div INA = VOLTAGE GENERATED BY SECONDARY TRANSFORMER WINDING

## Pin Description

| PIN      |          |       |                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1533A | MAX1537A | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                    |

| _        | 1        | ADJA  | Auxiliary Feedback Input. Connect a resistive voltage-divider from LDOA to analog ground to adjust the auxiliary linear-regulator output voltage. ADJA regulates at 2V. Connect ADJA to GND for nominal 12V output using internal feedback.                                                                                                                                                 |

| 1        | 2        | ON5   | 5V SMPS Enable Input. The 5V SMPS is enabled if ON5 is greater than the SMPS on level and disabled if ON5 is less than the SMPS off level. If ON5 is connected to REF, the 5V SMPS starts after the 3.3V SMPS reaches regulation (delay start). Drive ON5 below the clear fault level to reset the fault latches.                                                                           |

| 2        | 3        | ON3   | 3.3V SMPS Enable Input. The 3.3V SMPS is enabled if ON3 is greater than the SMPS on level and disabled if ON3 is less than the SMPS off level. If ON3 is connected to REF, the 3.3V SMPS starts after the 5V SMPS reaches regulation (delay start). Drive ON3 below the clear fault level to reset the fault latches.                                                                       |

| _        | 4        | ONA   | LDOA Enable Input. When ONA is low, LDOA is high impedance and the secondary winding control is off. When ONA is high, LDOA is on. Connect to LDO3, LDO5, CSL3, CSL5, or other output for desired automatic startup sequencing.                                                                                                                                                             |

| 3        | 5        | FSEL  | Frequency-Select Input. This three-level logic input sets the controller's switching frequency. Connect to GND, REF, or $V_{CC}$ to select the following typical switching frequencies: $V_{CC} = 500 \text{kHz}$ , REF = $300 \text{kHz}$ , GND = $200 \text{kHz}$                                                                                                                         |

| 4        | 6        | ILIM3 | 3.3V SMPS Peak Current-Limit Threshold Adjustment. The current-limit threshold defaults to 75mV if ILIM3 is connected to V <sub>CC</sub> . In adjustable mode, the current-limit threshold across CSH3 and CSL3 is precisely 1/10 the voltage seen at ILIM3 over a 500mV to 2.0V range. The logic threshold for switchover to the 75mV default value is approximately V <sub>CC</sub> - 1V. |

| 5        | 7        | ILIM5 | 5V SMPS Peak Current-Limit Threshold. The current-limit threshold defaults to 75mV if ILIM5 is connected to $V_{\rm CC}$ . In adjustable mode, the current-limit threshold across CSH5 and CSL5 is precisely 1/10th the voltage seen at ILIM5 over a 500mV to 2.0V range. The logic threshold for switchover to the 75mV default value is approximately $V_{\rm CC}$ - 1V.                  |

| 6        | 8        | REF   | 2.0V Reference Voltage Output. Bypass REF to analog ground with a 0.1µF or greater ceramic capacitor. The reference can source up to 100µA for external loads. Loading REF degrades output-voltage accuracy according to the REF load-regulation error. The reference shuts down when \$\overline{SHDN}\$ is low.                                                                           |

| 7        | 9        | GND   | Analog Ground. Connect the backside pad to GND.                                                                                                                                                                                                                                                                                                                                             |

| 8        | 10       | Vcc   | Analog Supply Input. Connect to the system supply voltage (+4.5V to +5.5V) through a series $20\Omega$ resistor. Bypass V <sub>CC</sub> to analog ground with a 1µF or greater ceramic capacitor.                                                                                                                                                                                           |

| 9        | 11       | PGDLY | Power-Good One-Shot Delay. Place a timing capacitor on PGDLY to delay PGOOD going high. PGDLY has a $5\mu\text{A}$ pullup current and a $10\Omega$ pulldown. The pulldown is activated when power is not good. When power is good, the pulldown is shut off and the $5\mu\text{A}$ pullup is activated. When PGDLY crosses REF, PGOOD is enabled.                                           |

## Pin Description (continued)

| PIN      |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|----------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX1533A | MAX1537A | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 10       | 12       | PGOOD | Open-Drain Power-Good Output. PGOOD is low if either output is more than 10% (typ) below the normal regulation point, during soft-start, and in shutdown. PGOOD is delayed on the rising edge by the PGDLY one-shot timer. PGOOD becomes high impedance when both SMPS outputs are in regulation.                                                                                                                                                                                                                                            |  |  |  |

| 11       | 13       | ŪVP   | Undervoltage Fault-Protection Control. Connect $\overline{\text{UVP}}$ to GND to select the default overvoltage threshold of 70% of nominal. Connect to V <sub>CC</sub> to disable undervoltage protection and clear the undervoltage fault latch.                                                                                                                                                                                                                                                                                           |  |  |  |

| 12       | 14       | DH3   | High-Side Gate-Driver Output for 3.3V SMPS. DH3 swings from LX3 to BST3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

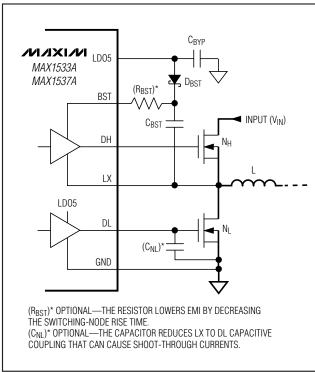

| 13       | 15       | BST3  | Boost Flying-Capacitor Connection for 3.3V SMPS. Connect to an external capacitor and diode as shown in Figure 6. An optional resistor in series with BST3 allows the DH3 pullup current to be adjusted.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 14       | 16       | LX3   | Inductor Connection for 3.3V SMPS. Connect LX3 to the switched side of the inductor. LX3 serves as the lower supply rail for the DH3 high-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 15       | 17       | OVP   | Overvoltage Fault-Protection Control. Connect $\overline{\text{OVP}}$ to GND to select the default overvoltage threshold of +11% above nominal. Connect to V <sub>CC</sub> to disable overvoltage protection and clear the overvoltage fault latch.                                                                                                                                                                                                                                                                                          |  |  |  |

| 16       | 18       | CSH3  | Positive Current-Sense Input for 3.3V SMPS. Connect to the positive terminal of the current-sense element. Figure 9 describes two different current-sensing options.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 17       | 19       | CSL3  | Negative Current-Sense Input for 3.3V SMPS. Connect to the negative terminal of the current-sense element. Figure 9 describes two different current-sensing options. CSL3 also serves as the bootstrap input for LDO3.                                                                                                                                                                                                                                                                                                                       |  |  |  |

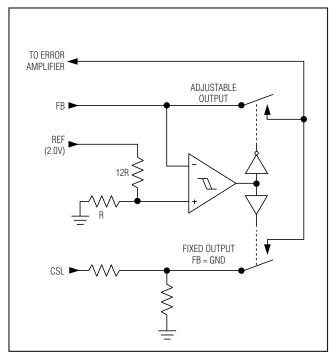

| 18       | 20       | FB3   | Feedback Input for 3.3V SMPS. Connect to GND for fixed 3.3V output. In adjustable mode, FB3 regulates to 1V.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 19       | 21       | LDO3  | 3.3V Internal Linear-Regulator Output. Bypass with 2.2 $\mu$ F (min) (1 $\mu$ F/20mA). Provides 100mA (min). Power is taken from LDO5. If CSL3 is greater than 3V, the linear regulator shuts down and LDO3 connects to CSL3 through a 1 $\Omega$ switch rated for loads up to 200mA.                                                                                                                                                                                                                                                        |  |  |  |

| 20       | 22       | DL3   | Low-Side Gate-Driver Output for 3.3V SMPS. DL3 swings from PGND to LDO5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 21       | 23       | PGND  | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 22       | 24       | DL5   | Low-Side Gate-Driver Output for 5V SMPS. DL5 swings from PGND to LDO5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 23       | 25       | LDO5  | 5V Internal Linear-Regulator Output. Bypass with 2.2 $\mu$ F (min) (1 $\mu$ F/20mA). Provides power for the DL_ low-side gate drivers, the DH_ high-side drivers through the BST diodes, the PWM controller, logic, and reference through the V <sub>CC</sub> pin, as well as the LDO3 internal 3.3V linear regulator. Provides 100mA (min) for external loads (+25mA for gate drivers). If CSL5 is greater than 4.5V, the linear regulator shuts down and LDO5 connects to CSL5 through a 0.75 $\Omega$ switch rated for loads up to 200mA. |  |  |  |

| 24       | 26       | FB5   | Feedback Input for 5V SMPS. Connect to GND for fixed 5V output. In adjustable mode, FB5 regulates to 1V.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

## Pin Description (continued)

| PIN      |          |      |                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX1533A | MAX1537A | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 25       | 27       | CSL5 | Negative Current-Sense Input for 5V SMPS. Connect to the negative terminal of the current-sense element. Figure 9 describes two different current-sensing options. CSL5 also serves as the bootstrap input for LDO5.                                                                                                                                                                              |  |  |

| 26       | 28       | CSH5 | Positive Current-Sense Input for 5V SMPS. Connect to the positive terminal of the current-sense element. Figure 9 describes two different current-sensing options.                                                                                                                                                                                                                                |  |  |

| 27       | 29       | IN   | Input of the Startup Circuitry and the LDO5 Internal 5V Linear Regulator. Bypass to PGND with 0.22µF close to the IC.                                                                                                                                                                                                                                                                             |  |  |

| 28       | 30       | LX5  | Inductor Connection for 5V SMPS. Connect LX5 to the switched side of the inductor. LX5 serves as the lower supply rail for the DH5 high-side gate driver.                                                                                                                                                                                                                                         |  |  |