Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### **General Description**

The MAX16065/MAX16066 flash-configurable system managers monitor and sequence multiple system voltages. The MAX16065/MAX16066 can also accurately monitor (±2.5%) one current channel using a dedicated high-side current-sense amplifier. The MAX16065 manages up to twelve system voltages simultaneously, and the MAX16066 manages up to eight supply voltages. These devices integrate a selectable differential or single-ended analog-to-digital converter (ADC) and configurable outputs for sequencing power supplies. Device configuration information, including overvoltage and undervoltage limits, timing settings, and the sequencing order is stored in nonvolatile flash memory. During a fault condition, fault flags and channel voltages can be automatically stored in the nonvolatile flash memory for later read-back.

The internal 1% accurate 10-bit ADC measures each input and compares the result to one overvoltage, one undervoltage, and one early warning limit that can be configured as either undervoltage or overvoltage. A fault signal asserts when a monitored voltage falls outside the set limits. Up to three independent fault output signals are configurable to assert under various fault conditions.

Because the MAX16065/MAX16066 support a power-supply voltage of up to 14V, they can be powered directly from the 12V intermediate bus in many systems.

The integrated sequencer provides precise control over the power-up and power-down order of up to twelve (MAX16065) or up to eight (MAX16066) power supplies. Eight outputs (EN\_OUT1-EN\_OUT8) are configurable with charge-pump outputs to directly drive external n-channel MOSFETs.

The MAX16065/MAX16066 include eight/six programmable general-purpose inputs/outputs (GPIO\_s). GPIO\_s are flash configurable as dedicated fault outputs, as a watchdog input or output, or as a manual reset.

The MAX16065/MAX16066 feature nonvolatile fault memory for recording information during system shutdown events. The fault logger records a failure in the internal flash and sets a lock bit protecting the stored fault data from accidental erasure. An SMBus or a JTAG serial interface configures the MAX16065/MAX16066. The MAX16065 is available in a 48-pin, 7mm x 7mm, TQFN package, and the MAX16066 is available in a 40-pin, 6mm x 6mm, TQFN package. Both devices are fully specified from -40°C to +85°C.

**Features**

- ♦ Operate from 2.8V to 14V

- ♦ ±2.5% Current-Monitoring Accuracy

- ♦ 1% Accurate 10-Bit ADC Monitors 12/8 Voltage Inputs

- ♦ Single-Ended or Differential ADC for System Voltage/Current Monitoring

- ♦ Integrated High-Side Current-Sense Amplifier

- ♦ 12/8 Monitored Inputs with Overvoltage/ Undervoltage/Early Warning Limit

- ♦ Nonvolatile Fault Event Logger

- Power-Up and Power-Down Sequencing Capability

- ♦ Independent Secondary Sequence Block

- ♦ 12/8 Outputs for Sequencing/Power-Good Indicators

- ♦ Two Programmable Fault Outputs and One Reset Output

- Eight General-Purpose Inputs/Outputs Configurable as:

Dedicated Fault Outputs Watchdog Timer Function Manual Reset Margin Enable

- ♦ SMBus (with Timeout) or JTAG Interface

- ♦ Flash Configurable Time Delays and Thresholds

- **♦** -40°C to +85°C Operating Temperature Range

### **Applications**

Networking Equipment

Telecom Equipment (Base Stations, Access)

Storage/Raid Systems

Servers

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX16065ETM+ | -40°C to +85°C | 48 TQFN-EP* |

| MAX16066ETL+ | -40°C to +85°C | 40 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Typical Operating Circuits appear at end of data sheet.

<sup>\*</sup>EP = Exposed pad.

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### **ABSOLUTE MAXIMUM RATINGS**

| Input/Output Current                      | 20mA             |

|-------------------------------------------|------------------|

| Continuous Power Dissipation ( $T_A = +7$ | 70°C)            |

| 40-Pin TQFN (derate 26.3mW/°C abo         | ove +70°C)2105mW |

| 48-Pin TQFN (derate 27.8mW/°C abo         | ove +70°C)2222mW |

| Operating Temperature Range               | 40°C to +85°C    |

| Junction Temperature                      | +150°C           |

| Storage Temperature Range                 | 65°C to +150°C   |

| Lead Temperature (soldering, 10s)         |                  |

| Soldering Temperature (reflow)            | +260°C           |

|                                           |                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(VCC = 2.8V \text{ to } 14V, TA = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise specified. Typical values are at VABP} = VDBP = VCC = 3.3V, TA = +25^{\circ}C.)$  (Note 1)

| PARAMETER                       | SYMBOL             | CONDITIONS                                                                    | MIN   | TYP  | MAX   | UNITS |

|---------------------------------|--------------------|-------------------------------------------------------------------------------|-------|------|-------|-------|

| Operating Voltage Bange         | \/oo               | Reset output asserted low                                                     | 1.2   |      |       | V     |

| Operating Voltage Range         | Vcc                | (Note 2)                                                                      | 2.8   |      | 14    | V     |

| Undervoltage Lockout (Rising)   | Vuvlo              | Minimum voltage on VCC to ensure the device is flash configurable             |       |      | 2.7   | V     |

| Undervoltage Lockout Hysteresis | Vuvlo_HYS          |                                                                               |       | 100  |       | mV    |

| Minimum Flash Operating Voltage | V <sub>flash</sub> | Minimum voltage on V <sub>CC</sub> to ensure flash erase and write operations |       | 2.7  |       | V     |

| Cumply Current                  | Icc                | No load on output pins                                                        |       | 4.5  | 7     | νος Λ |

| Supply Current                  |                    | During flash writing cycle                                                    |       | 10   | 14    | - mA  |

| ABP Regulator Voltage           | VABP               | CABP = 1µF, no load, VCC = 5V                                                 | 2.85  | 3    | 3.15  | V     |

| DBP Regulator Voltage           | VDBP               | $C_{DBP} = 1\mu F$ , no load, $V_{CC} = 5V$                                   | 2.8   | 3    | 3.1   | V     |

| Boot Time                       | tBOOT              | VCC > VUVLO                                                                   |       | 200  | 350   | μs    |

| Flash Writing Time              |                    | 8-byte word                                                                   |       | 122  |       | ms    |

| Internal Timing Accuracy        |                    | (Note 3)                                                                      | -8    |      | +8    | %     |

|                                 | VTH_EN_R           | EN voltage rising                                                             |       | 1.41 |       | V     |

| EN Input Voltage                | VTH_EN_F           | EN voltage falling                                                            | 1.365 | 1.39 | 1.415 | V     |

| EN Input Current                | IEN                |                                                                               | -0.5  |      | +0.5  | μΑ    |

| MON_ Input Voltage Range        |                    |                                                                               | 0     |      | 5.5   | V     |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VCC = 2.8V \text{ to } 14V, TA = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are at VABP = VDBP = VCC = 3.3V, TA = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                        | SYMBOL              |                                             | CONDITIONS            | MIN  | TYP  | MAX  | UNITS  |  |

|--------------------------------------------------|---------------------|---------------------------------------------|-----------------------|------|------|------|--------|--|

| ADC DC ACCURACY                                  |                     |                                             |                       |      |      |      |        |  |

| Resolution                                       |                     |                                             |                       |      |      | 10   | Bits   |  |

| Gain Error                                       | ADCGAIN             | T <sub>A</sub> = +25°C                      |                       |      |      | 0.35 | %      |  |

|                                                  |                     | $T_A = -40^{\circ}$                         | C to +85°C            |      |      | 0.70 |        |  |

| Offset Error                                     | ADCoff              |                                             |                       |      |      | 1    | LSB    |  |

| Integral Nonlinearity                            | ADCINL              |                                             |                       |      |      | 1    | LSB    |  |

| Differential Nonlinearity                        | ADC <sub>DNL</sub>  |                                             |                       |      |      | 1    | LSB    |  |

| ADC Total Monitoring Cycle Time                  | tCYCLE              |                                             | fault detected        |      | 40   | 50   | μs     |  |

|                                                  |                     | 1 LSB = 5                                   |                       |      | 5.56 |      |        |  |

| ADC IN_ Ranges                                   |                     | 1 LSB = 2                                   | .72mV                 |      | 2.78 |      | V      |  |

|                                                  |                     | 1 LSB = 1                                   | .36mV                 |      | 1.39 |      |        |  |

| CURRENT SENSE                                    |                     |                                             |                       |      |      |      |        |  |

| CSP Input-Voltage Range                          | VCSP                |                                             |                       | 3    |      | 14   | V      |  |

| Input Bias Current                               | ICSP                |                                             |                       |      | 14   | 25   |        |  |

| Imput bias Current                               | ICSM                | VCSP = VC                                   | CSM                   |      | 3    | 5    | μΑ     |  |

| CSP Total Unadjusted Error                       | CSPERR              | (Note 4)                                    |                       |      |      | 2    | %FSR   |  |

|                                                  | OVCTH               | VCSP -<br>VCSM                              | Gain = 48             | 21.5 | 25   | 30.5 | mV     |  |

| Overcurrent Differential                         |                     |                                             | Gain = 24             | 46   | 51   | 56   |        |  |

| Threshold                                        |                     |                                             | Gain = 12             | 94   | 101  | 108  |        |  |

|                                                  |                     |                                             | Gain = 6              | 190  | 202  | 210  |        |  |

| V <sub>SENSE</sub> Fault Threshold<br>Hysteresis | OVCHYS              |                                             |                       |      | 0.5  |      | %OVCTH |  |

|                                                  |                     | r73h[6:5] :                                 | = '00'                |      | 0    |      |        |  |

| Secondary Overcurrent Threshold                  |                     | r73h[6:5] :                                 |                       | 3    | 4    | 5    | 1      |  |

| Timeout                                          | OVCDEL              | r73h[6:5] :                                 |                       | 12   | 16   | 20   | ms     |  |

|                                                  |                     | r73h[6:5] :                                 |                       | 50   | 64   | 60   | -      |  |

|                                                  |                     | Gain = 6                                    |                       |      | 232  |      |        |  |

|                                                  |                     | Gain = 12                                   |                       |      | 116  |      | -      |  |

| VSENSE Ranges                                    |                     | Gain = 24                                   |                       |      | 58   |      | mV     |  |

|                                                  |                     | Gain = 48                                   |                       |      | 29   |      | -      |  |

|                                                  |                     |                                             | 150mV (gain = 6 only) | -2.5 | ±0.2 | +2.5 |        |  |

| ADC Current Measurement                          |                     |                                             | 50mV, gain = 12       | -4   | ±0.2 | +4   | †      |  |

| Accuracy                                         |                     |                                             | 25mV, gain = 24       |      | ±0.5 |      | -<br>% |  |

|                                                  |                     |                                             | 10mV, gain = 48       |      | ±1   |      |        |  |

| Gain Accuracy                                    |                     | VSENSE = 20mV to 100mV, VCSP = 5V, gain = 6 |                       | -1.5 |      | +1.5 | %      |  |

| Common-Mode Rejection Ratio                      | CMRR <sub>SNS</sub> | VCSP > 4V                                   |                       |      | 80   |      | dB     |  |

| Power-Supply Rejection Ratio                     | PSRR <sub>SNS</sub> | 1                                           |                       |      | 80   |      | dB     |  |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.8V \text{ to } 14V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are at  $V_{ABP} = V_{DBP} = V_{CC} = 3.3V, T_A = +25^{\circ}\text{C.}$  (Note 1)

| PARAMETER                                              | SYMBOL   | CONDITIONS                                           | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------|----------|------------------------------------------------------|-----|-----|-----|-------|

| OUTPUTS (EN_OUT_, RESET, G                             | PIO_)    |                                                      |     |     |     |       |

|                                                        |          | ISINK = 2mA                                          |     |     | 0.4 |       |

| Output-Voltage Low                                     | VoL      | ISINK = 10mA, GPIO_ only                             |     |     | 0.7 | V     |

|                                                        |          | VCC = 1.2V, ISINK = 100μA (RESET only)               |     |     | 0.3 |       |

| Maximum Output Sink Current                            |          | Total current into EN_OUT_, RESET, GPIO_, VCC = 3.3V |     |     | 30  | mA    |

| Output-Voltage High (Push-Pull)                        |          | ISOURCE = 100µA                                      | 2.4 |     |     | V     |

| Output Leakage (Open Drain)                            |          |                                                      |     |     | 1   | ^     |

| Output Leakage (Open Drain)                            |          | VEN_OUT1 - VEN_OUT8 = 13.2V                          |     |     | 5   | μΑ    |

| OUT_ Overdrive (Charge Pump)<br>(EN_OUT1-EN_OUT8 Only) |          | IGATE_ = 1µA                                         | 10  | 11  | 13  | V     |

| OUT_ Pullup Current (Charge Pump)                      | ICH_UP   | During power up, VGATE = 1V                          | 2.5 | 4   |     | μΑ    |

| SMBus INTERFACE                                        |          |                                                      |     |     |     |       |

| Logic-Input Low Voltage                                | VIL      | Input voltage falling                                |     |     | 0.8 | V     |

| Logic-Input High Voltage                               | VIH      | Input voltage rising                                 | 2.0 |     |     | V     |

| Input Leakage Current                                  |          | IN = GND or V <sub>CC</sub>                          | -1  |     | +1  | μΑ    |

| Output Voltage Low (SDA/SCL)                           | VoL      | ISINK = 3mA                                          |     |     | 0.4 | V     |

| Input Capacitance                                      | CIN      |                                                      |     | 5   |     | рF    |

| SMBus Timeout                                          | tTIMEOUT | SCL time low for reset                               | 25  |     | 35  | ms    |

| INPUTS (A0, GPIO_)                                     |          |                                                      |     |     |     |       |

| Input Logic-Low                                        | VIL      |                                                      |     |     | 0.8 | V     |

| Input Logic-High                                       | VIH      |                                                      | 2.0 |     |     | V     |

| WDI Pulse Width                                        | twDI     |                                                      | 100 |     |     | ns    |

| MR Pulse Width                                         | tMR      |                                                      | 1   |     |     | μs    |

| MR to RESET Delay                                      |          |                                                      |     | 0.5 |     | μs    |

| MR Glitch Rejection                                    |          |                                                      |     | 100 |     | ns    |

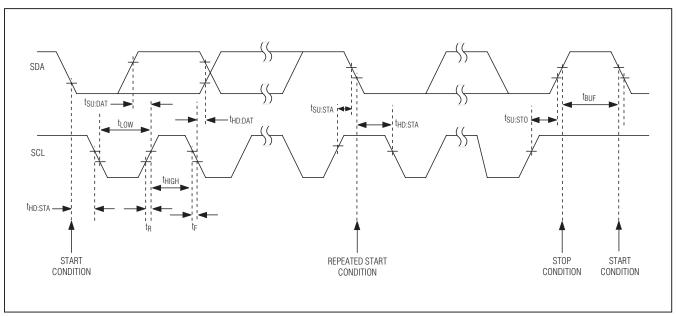

| SMBus TIMING                                           |          |                                                      |     |     |     |       |

| Serial Clock Frequency                                 | fscl     |                                                      |     |     | 400 | kHz   |

| Bus Free Time Between STOP and START Condition         | tBUF     |                                                      | 1.3 |     |     | μs    |

| START Condition Setup Time                             | tsu:sta  |                                                      | 0.6 |     |     | μs    |

| START Condition Hold Time                              | tHD:STA  |                                                      | 0.6 |     |     | μs    |

| STOP Condition Setup Time                              | tsu:sto  |                                                      | 0.6 |     |     | μs    |

| Clock Low Period                                       | tLOW     |                                                      | 1.3 |     |     | μs    |

| Clock High Period                                      | tHIGH    |                                                      | 0.6 |     |     | μs    |

| Data Setup Time                                        | tsu:dat  |                                                      | 100 |     |     | ns    |

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VCC = 2.8V \text{ to } 14V, TA = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are at VABP = VDBP = VCC = 3.3V, TA = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                 | SYMBOL           | CONDITIONS                         | MIN | TYP | MAX  | UNITS |

|-------------------------------------------|------------------|------------------------------------|-----|-----|------|-------|

| Output Fall Time                          | tor              | CBUS = 10pF to 400pF               |     |     | 250  | ns    |

| Data Hold Time                            | thd:dat          | From 50% SCL falling to SDA change | 0.3 |     | 0.9  | μs    |

| Pulse Width of Spike Suppressed           | tsp              |                                    |     | 30  |      | ns    |

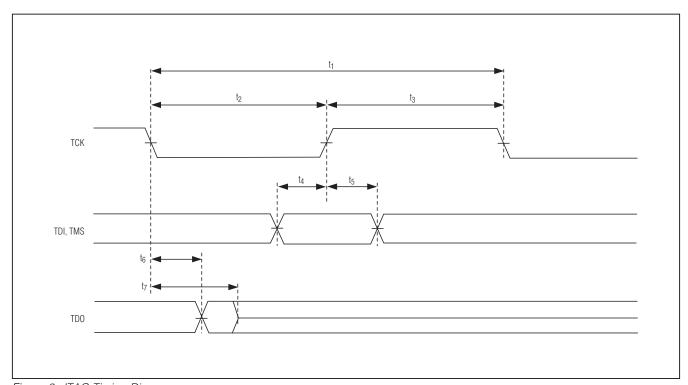

| JTAG INTERFACE                            |                  |                                    |     |     |      |       |

| TDI, TMS, TCK Logic-Low Input<br>Voltage  | VIL              | Input voltage falling              |     |     | 0.8  | V     |

| TDI, TMS, TCK Logic-High Input<br>Voltage | VIH              | Input voltage rising               | 2   |     |      | V     |

| TDO Logic-Output Low Voltage              | VoL              | ISINK = 3mA                        |     |     | 0.4  | V     |

| TDO Logic-Output High Voltage             | Voн              | ISOURCE = 200µA                    | 2.4 |     |      | V     |

| TDI, TMS Pullup Resistors                 | R <sub>PU</sub>  | Pullup to DBP                      | 40  | 50  | 60   | kΩ    |

| I/O Capacitance                           | C <sub>I/O</sub> |                                    |     | 5   |      | рF    |

| TCK Clock Period                          | t <sub>1</sub>   |                                    |     |     | 1000 | ns    |

| TCK High/Low Time                         | t2, t3           |                                    | 50  | 500 |      | ns    |

| TCK to TMS, TDI Setup Time                | t4               |                                    | 15  |     |      | ns    |

| TCK to TMS, TDI Hold Time                 | t5               |                                    | 10  |     |      | ns    |

| TCK to TDO Delay                          | t <sub>6</sub>   |                                    |     |     | 500  | ns    |

| TCK to TDO High-Z Delay                   | t7               |                                    |     |     | 500  | ns    |

**Note 1:** Specifications are guaranteed for the stated global conditions, unless otherwise noted. 100% production tested at  $T_A = +25$ °C and  $T_A = +85$ °C. Specifications at  $T_A = -40$ °C are guaranteed by design.

Note 2: For V<sub>CC</sub> of 3.6V or lower, connect V<sub>CC</sub>, DBP, and ABP together. For higher supply applications, connect only V<sub>CC</sub> to the supply rail.

Note 3: Applies to RESET, fault, autoretry, sequence delays, and watchdog timeout.

Note 4: Total unadjusted error is a combination of gain, offset, and quantization error.

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

Figure 1. SMBus Timing Diagram

Figure 2. JTAG Timing Diagram

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

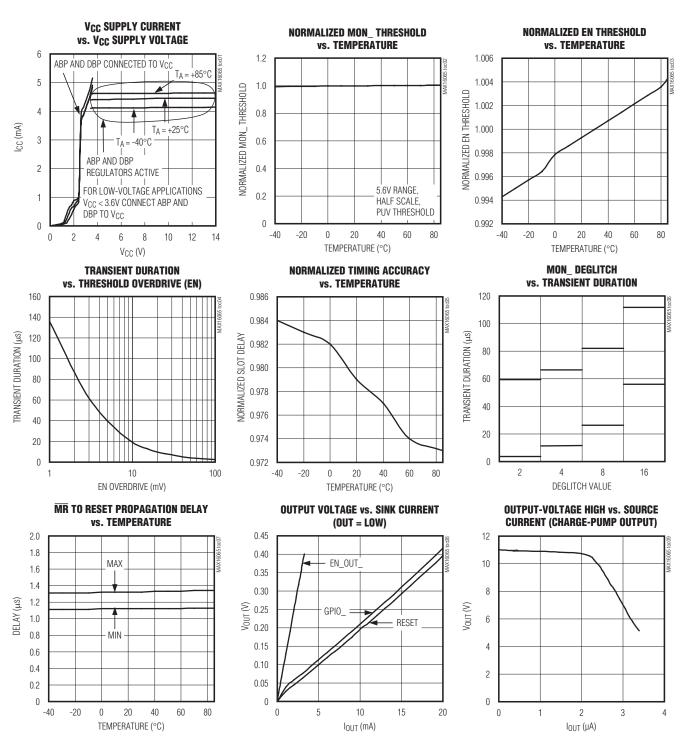

### \_Typical Operating Characteristics

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25$ °C, unless otherwise noted.)

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

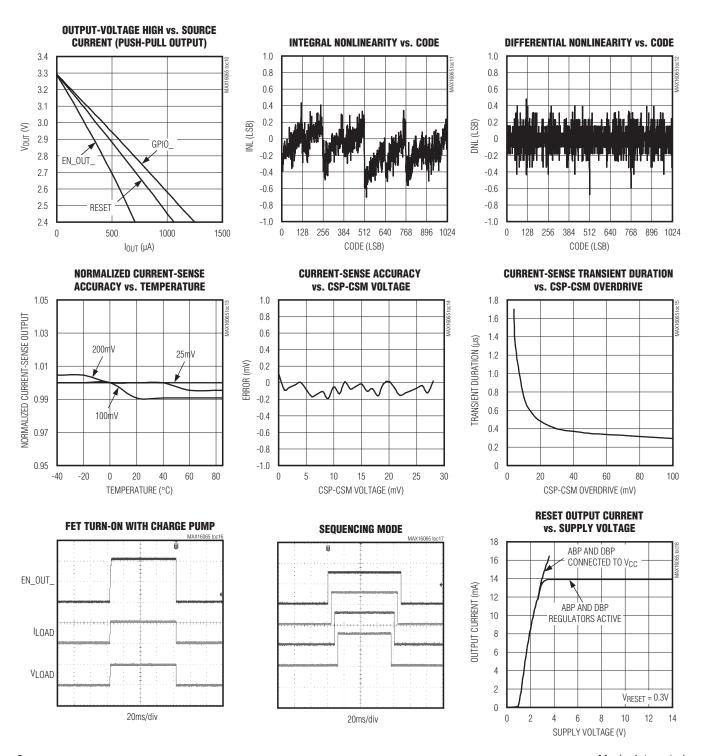

**Typical Operating Characteristics (continued)**

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

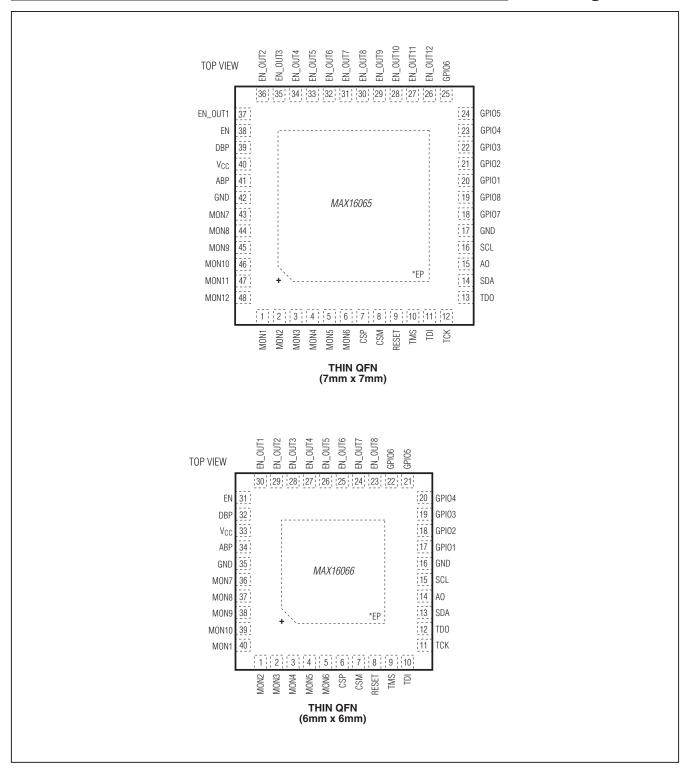

**Pin Configurations**

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### Pin Description

| PIN        |                   |                      |                                                                                                                                                                                                                                                                                                                           |

|------------|-------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16065   | MAX16066          | NAME                 | FUNCTION                                                                                                                                                                                                                                                                                                                  |

| 1–6, 43–46 | 40, 1–5,<br>36–39 | MON1-<br>MON10       | Monitor Voltage Inputs. Set monitor voltage range through configuration registers. Measured value written to ADC register can be read back through the SMBus or JTAG interface.                                                                                                                                           |

| 47, 48     | _                 | MON11,<br>MON12      | Monitor Voltage Inputs. Set monitor voltage range through configuration registers. Measured value written to ADC register can be read back through the SMBus or JTAG interface.                                                                                                                                           |

| 7          | 6                 | CSP                  | Current-Sense Amplifier Positive Input. Connect CSP to the source side of the external sense resistor.                                                                                                                                                                                                                    |

| 8          | 7                 | CSM                  | Current-Sense Amplifier Negative Input. Connect CSM to the load side of the external sense resistor.                                                                                                                                                                                                                      |

| 9          | 8                 | RESET                | Configurable Reset Output                                                                                                                                                                                                                                                                                                 |

| 10         | 9                 | TMS                  | JTAG Test Mode Select                                                                                                                                                                                                                                                                                                     |

| 11         | 10                | TDI                  | JTAG Test Data Input                                                                                                                                                                                                                                                                                                      |

| 12         | 11                | TCK                  | JTAG Test Clock                                                                                                                                                                                                                                                                                                           |

| 13         | 12                | TDO                  | JTAG Test Data Output                                                                                                                                                                                                                                                                                                     |

| 14         | 13                | SDA                  | SMBus Serial-Data Open-Drain Input/Output                                                                                                                                                                                                                                                                                 |

| 15         | 14                | A0                   | Four-State SMBus Address. Address sampled upon POR.                                                                                                                                                                                                                                                                       |

| 16         | 15                | SCL                  | SMBus Serial-Clock Input                                                                                                                                                                                                                                                                                                  |

| 17, 42     | 16, 35            | GND                  | Ground                                                                                                                                                                                                                                                                                                                    |

| 20–25      | 17–22             | GPIO1-<br>GPIO6      | General-Purpose Input/Outputs. GPIO_s can be configured to act as a TTL input, a push-pull, open-drain, or high-impedance output or a pulldown circuit during a fault event.                                                                                                                                              |

| 18, 19     | _                 | GPIO7,<br>GPIO8      | General-Purpose Input/Outputs. GPIO_s can be configured to act as a TTL input, a push-pull, open-drain, or high-impedance output or a pulldown circuit during a fault event or reverse sequencing.                                                                                                                        |

| 26–29      | _                 | EN_OUT12-<br>EN_OUT9 | Outputs. Set EN_OUT_ with active-high/active-low logic and with push-pull or open-drain configuration. EN_OUT_ can be asserted by a combination of IN_ voltages configurable through the flash.                                                                                                                           |

| 30–37      | 23–30             | EN_OUT8-<br>EN_OUT1  | Outputs. Set EN_OUT_ with active-high/active-low logic and with push-pull or open-drain configuration. EN_OUT_ can be asserted by a combination of IN_ voltages configurable through the flash. EN_OUT1-EN_OUT8 can be configured with a charge-pump output (+10V above GND) that can drive an external n-channel MOSFET. |

| 38         | 31                | EN                   | Analog Enable Input. All outputs deassert when VEN is below the enable threshold.                                                                                                                                                                                                                                         |

| 39         | 32                | DBP                  | Digital Bypass. All push-pull outputs are referenced to DBP. Bypass DBP with a 1µF capacitor to GND.                                                                                                                                                                                                                      |

| 40         | 33                | Vcc                  | Device Power Supply. Connect V <sub>CC</sub> to a voltage from 2.8V to 14V. Bypass V <sub>CC</sub> with a 10µF capacitor to GND.                                                                                                                                                                                          |

| 41         | 34                | ABP                  | Analog Bypass. Bypass ABP with a 1µF ceramic capacitor to GND.                                                                                                                                                                                                                                                            |

| _          | _                 | EP                   | Exposed Pad. Internally connected to GND. Connect to ground, but do not use as the main ground connection.                                                                                                                                                                                                                |

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

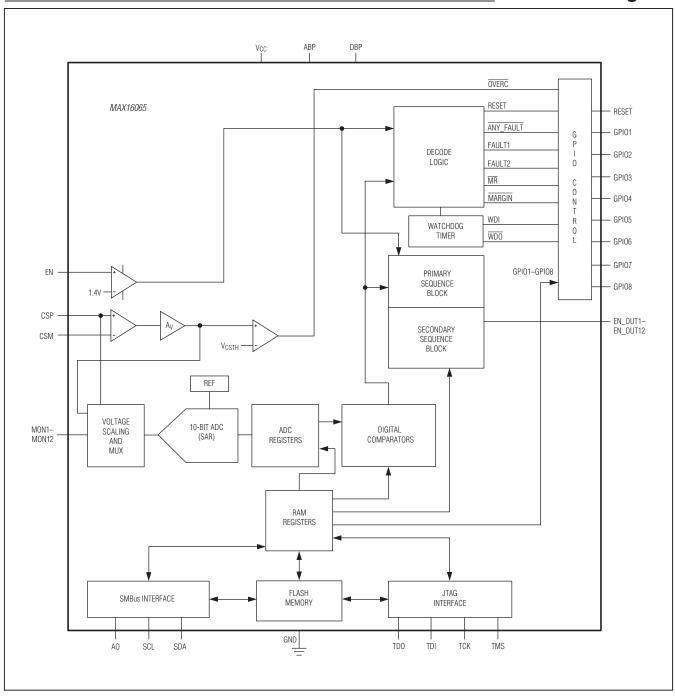

**Functional Diagram**

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

### **Detailed Description**

The MAX16065 manages up to twelve system power supplies and the MAX16066 can manage up to eight system power supplies. After boot-up, if EN is high and the software enable bit is set to '1,' a power-up sequence begins based on the configuration stored in flash and the EN\_OUT\_s are controlled accordingly. When the power-up sequence is successfully completed, the monitoring phase begins. An internal multiplexer cycles through each MON\_ input. At each multiplexer stop, the 10-bit ADC converts the monitored analog voltage to a digital result and stores the result in a register. Each time a conversion cycle (50us, max) completes, internal logic circuitry compares the conversion results to the overvoltage and undervoltage thresholds stored in memory. When a result violates a programmed threshold, the conversion can be configured to generate a fault. GPIO\_ can be programmed to assert on combinations of faults. Additionally, faults can be configured to shut off the system and trigger the nonvolatile fault logger, which writes all fault information automatically to the flash and writeprotects the data to prevent accidental erasure.

The MAX16065/MAX16066 contain both SMBus and JTAG serial interfaces for accessing registers and flash. Use only one interface at any given time. For more information on how to access the internal memory through these interfaces, see the *SMBus-Compatible Interface* and *JTAG Serial Interface* sections. The memory map is divided into three pages with access controlled by special SMBus and JTAG commands.

The factory-default values at POR (power-on reset) for all RAM registers are '0's. POR occurs when VCC reaches the undervoltage-lockout threshold (UVLO) of 2.8V (max). At POR, the device begins a boot-up sequence. During the boot-up sequence, all monitored inputs are masked from initiating faults and flash contents are copied to the respective register locations. During boot-up, the MAX16065/MAX16066 are not accessible through the serial interface. The boot-up sequence takes up to 350µs, after which the device is ready for normal operation. RESET is asserted low up to the boot-up phase and remains asserted for its programmed timeout period once sequencing is completed and all monitored channels are within their respective thresholds. Up to the boot-up phase, the GPIO\_s and EN\_OUT\_s are high impedance.

#### Power

Apply 2.8V to 14V to VCC to power the MAX16065/ MAX16066. Bypass VCC to ground with a 10 $\mu$ F capacitor. Two internal voltage regulators, ABP and DBP, supply power to the analog and digital circuitry within the device. For operation at 3.6V or lower, disable the regulators by connecting ABP and DBP to VCC.

ABP is a 3.0V (typ) voltage regulator that powers the internal analog circuitry. Bypass ABP to GND with a  $1\mu$ F ceramic capacitor installed as close to the device as possible.

DBP is an internal 3.0V (typ) voltage regulator. DBP powers flash and digital circuitry. All push-pull outputs refer to DBP. DBP supplies the input voltage to the internal charge pump when the programmable outputs are configured as charge-pump outputs. Bypass the DBP output to GND with a  $1\mu F$  ceramic capacitor installed as close as possible to the device.

Do not power external circuitry from ABP or DBP.

#### Sequencing

To sequence a system of power supplies safely, the output voltage of a power supply must be good before the next power supply may turn on. Connect EN\_OUT\_ outputs to the enable input of an external power supply and connect MON\_ inputs to the output of the power supply for voltage monitoring. More than one MON\_ can be used if the power supply has multiple outputs.

#### Seauence Order

The MAX16065/MAX16066 provide a system of ordered slots to sequence multiple power supplies. To determine the sequence order, assign each EN\_OUT\_ to a slot ranging from Slot 1 to Slot 12. EN\_OUT\_(s) assigned to Slot 1 are turned on first, followed by outputs assigned to Slot 2, and so on through Slot 12. Multiple EN\_OUT\_s assigned to the same slot turn on at the same time.

Each slot includes a built-in configurable sequence delay (registers r77h to r7Dh) ranging from 20µs to 1.6s. During a reverse sequence, slots are turned off in reverse order starting from Slot 12. The MAX16065/MAX16066 can be configured to power-down in simultaneous mode or in reverse sequence mode as set in r75h[0]. See Tables 5 and 6 for the EN\_OUT\_ slot assignment bits, and Tables 3 and 4 for the sequence delays.

During power-up or power-down sequencing, the current sequencer state can be found in r21h[4:0].

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

**Table 1. Current Sequencer Slot**

| REGISTER<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21h                 | [4:0]     | Current Sequencer State:  00000 = Slot 0  00001 = Slot 1  00010 = Slot 2  00011 = Slot 3  00100 = Slot 4  00101 = Slot 5  00110 = Slot 6  00111 = Slot 7  01000 = Slot 8  01001 = Slot 9  01010 = Slot 10  01011 = Slot 11  01100 = Slot 12  01101 = Secondary sequence monitoring mode  01110 = Primary sequence fault  01111 = Primary sequence fault  10000 = Secondary sequence fault  10001 to 11111 = Reserved |

|                     | [7:5]     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                             |

### Multiple Sequencing Groups

The MAX16065/MAX16066 sequencing slots can be split into two groups: the primary sequence and the secondary sequence. The last slot of the primary sequence is selected using register bits r7Dh[7:4]. The secondary sequence begins at the slot after the one specified in register bits r7Dh[7:4]. The primary sequence is controlled by the EN input and the software enable bit in r73h[0]. Outputs assigned to slots in the primary sequence turn on, and monitoring begins for inputs assigned to these slots. RESET deasserts after the primary sequence and timeout period completes.

To initiate secondary sequencing and monitoring, set the software enable r73h[1] bit to 1. Additionally, if GPIO\_ is configured as EN2 then both the software enable 2 and EN2 must be high. Outputs assigned to slots in the secondary sequence turn on, and monitoring begins for inputs assigned to these slots. If a GPIO\_ is configured as the RESET2 output, it deasserts after the secondary sequence and timeout period completes.

If a critical fault occurs in the primary sequence group, both sequence groups automatically shut down. If a critical fault occurs in the secondary sequence group, then just the outputs assigned to slots in the secondary sequence turn off. The failing slot in secondary sequence is stored in r1Dh.

Multiple sequencing groups can be used to conserve power by powering down secondary systems when not in use.

#### Enable and Enable2

To initiate sequencing/tracking and enable monitoring, the voltage at EN must be above 1.4V and the software enable bit in r73h[0] must be set to '1.' To power down and disable monitoring, either pull EN below 1.35V or set the Software Enable bit to '0.' See Table 2 for the software enable bit configurations. Connect EN to ABP if not used.

If a fault condition occurs during the power-up cycle, the EN\_OUT\_ outputs are powered down immediately, regardless of the state of EN. In the monitoring state, if EN falls below the threshold, the sequencing state machine begins the power-down sequence. If EN rises above the threshold during the power-down sequence, the sequence state machine continues the power-down sequence until all the channels are powered off and then the device immediately begins the power-up sequence. When in the monitoring state, a register bit, ENRESET, is set to a '1' when EN falls below the undervoltage threshold. This register bit latches and must be cleared through software. This bit indicates if RESET asserted low due to EN going under the threshold. The POR state of ENRESET is '0'. The bit is only set on a falling edge

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

of the EN comparator output or the software enable bit. If operating in latch-on fault mode, toggle EN or toggle the Software Enable bit to clear the latch condition and restart the device once the fault condition has been removed.

To initiate secondary sequencing and monitoring set the software enable r73h[1] bit to 1. Additionally, if GPIO\_ is configured as EN2 then both the software enable 2 bit and EN2 must be high. To power-down and disable monitoring, either drive EN2 low or set the Software Enable2 bit to '0.' See Table 2 for the software enable bit configurations.

When a fault condition occurs during the power-up cycle, the EN\_OUT\_ outputs are powered down immediately, independent of the state of EN2. Drive EN2 low to begin the secondary power-down sequence. When EN2 is

driven high during the power-down sequence, the sequence state machine continues the power-down sequence until the secondary channels are powered off and then the device immediately begins the power-up sequence.

#### Monitoring Inputs While Sequencing

An enabled MON\_ input can be assigned to a slot ranging from Slot 1 to Slot 12. EN\_OUT\_s are always asserted at the beginning of a slot. The supply voltages connected to the MON\_ inputs must exceed the undervoltage threshold before the programmed timeout period expires otherwise a fault condition will occur. The undervoltage threshold checking cannot be disabled during power-up and power-down. See Tables 5 and 6 for the MON\_ slot assignment bits. The programmed

**Table 2. Software Enable Configurations**

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE                                                                                         | DESCRIPTION                                                                                                                         |

|---------------------|------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                     |                  | [0]                                                                                               | Software enable 1 (primary sequence)                                                                                                |

|                     |                  | [1]                                                                                               | Software enable 2 (secondary sequence)                                                                                              |

|                     |                  | [2]                                                                                               | 1 = Margin mode enabled                                                                                                             |

| 73h                 | 273h [3]         | Early warning threshold select 0 = Early warning is undervoltage 1 = Early warning is overvoltage |                                                                                                                                     |

| [4]                 |                  | [4]                                                                                               | Independent watchdog mode enable  1 = Watchdog timer is independent of sequencer  0 = Watchdog timer boots after sequence completes |

**Table 3. Slot Delay Register**

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION                                                     |

|---------------------|------------------|-----------|-----------------------------------------------------------------|

| 77h                 | 277h             | [3:0]     | Sequence Slot 0 Delay                                           |

| 7711                | 27711            | [7:4]     | Sequence Slot 1 Delay                                           |

| 78h                 | 278h             | [3:0]     | Sequence Slot 2 Delay                                           |

| 7 011               | 2/8/1            | [7:4]     | Sequence Slot 3 Delay                                           |

| 79h                 | 270h             | [3:0]     | Sequence Slot 4 Delay                                           |

| 7911                | 279h             | [7:4]     | Sequence Slot 5 Delay                                           |

| 7Ah                 | 0741             | [3:0]     | Sequence Slot 6 Delay                                           |

| /AII                | 27Ah             | [7:4]     | Sequence Slot 7 Delay                                           |

| 7Bh                 | 27Bh             | [3:0]     | Sequence Slot 8 Delay                                           |

| / DII               | 2/011            | [7:4]     | Sequence Slot 9 Delay                                           |

| 70h                 | 070h             | [3:0]     | Sequence Slot 10 Delay                                          |

| 7Ch                 | 7Ch 27Ch         |           | Sequence Slot 11 Delay                                          |

| 7Db                 | 701 0701         | [3:0]     | Sequence Slot 12 Delay                                          |

| /Un                 | 7Dh 27Dh         |           | Grouped Sequence Split Location, Final Slot of Primary Sequence |

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

Table 4. Power-Up/Power-Down Slot Delays

| CODE | VALUE |

|------|-------|

| 0000 | 25µs  |

| 0001 | 500µs |

| 0010 | 1ms   |

| 0011 | 2ms   |

| 0100 | 3ms   |

| 0101 | 4ms   |

| 0110 | 6ms   |

| 0111 | 8ms   |

| 1000 | 10ms  |

| 1001 | 12ms  |

| 1010 | 25ms  |

| 1011 | 100ms |

| 1100 | 200ms |

| 1101 | 400ms |

| 1110 | 800ms |

| 1111 | 1.6s  |

sequence delay is then counted before moving to the next slot.

Slot 0 does not monitor any MON\_ input and does not control any EN\_OUT\_. Slot 0 waits for the Software Enable bit r73h[0] to be a logic-high and for the voltage on EN to rise above 1.4V before initiating the power-up sequence and counting its own sequence delay.

Any MON\_ input that suffers a fault that occurs during power-up sequencing causes all the EN\_OUT\_s to turn off and the sequencer to shut down regardless of the state of the critical fault enables (see the *Faults* section for more information). If a MON\_ input is less critical to system operation, it can be configured as "monitoring only" (see Table 6) for either the primary or secondary sequence. Monitoring for MON\_ inputs assigned as "monitoring only" begins after sequencing is complete for that group, and can trigger a critical fault only if specifically configured to do so using the critical fault enables.

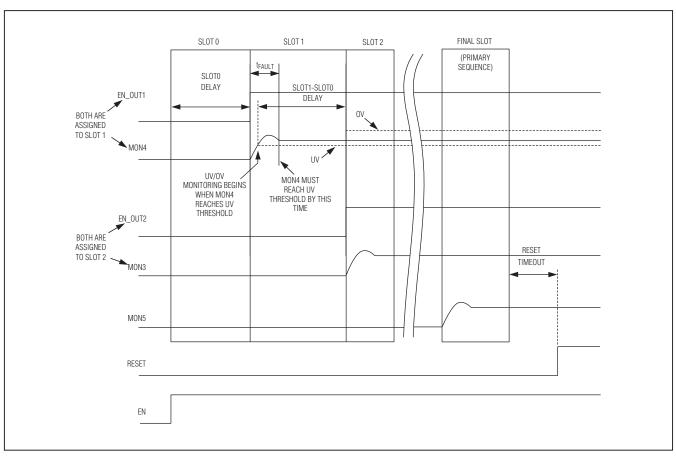

#### Power-Up

On power-up, when EN is high and the Software Enable bit is 1, the MAX16065/MAX16066 begin sequencing with Slot 0. After the sequencing delay for Slot 0 expires, the sequencer advances to Slot 1, and all EN\_OUT\_s assigned to the slot assert. All MON\_ inputs assigned to Slot 1 are monitored and when the voltage rises above the UV fault threshold, the sequence delay counter is started.

When the tFAULT counter expires before all MON\_ inputs assigned to the slot are above the fault UV threshold, a fault asserts. EN\_OUT\_ outputs are disabled and the MAX16065/MAX16066 return to the power-off state. When the sequence delay expires, the MAX16065/MAX16066 proceed to the next slot.

After the voltages on all MON\_ inputs assigned to the last slot exceed the UV fault threshold and the slot delay expires, the MAX16065/MAX16066 start the reset timeout counter. After the reset timeout, RESET deasserts. r75h[4:1] sets the tFAULT delay. See Table 7 for details.

#### Power-Down

Power-down starts when EN is pulled low or the Software Enable bit is set to '0.' Power down EN\_OUT\_s simultaneously or in reverse-sequence mode by setting the Reverse Sequence bit (r75h[0]) appropriately.

#### Reverse-Sequence Mode

When the MAX16065/MAX16066 are fully powered up (including secondary sequence group, if enabled) and EN or the Software Enable bit is set to '0', the EN\_OUT\_s assigned to Slot 12 deassert, the MAX16065/MAX16066 wait for the Slot 12 sequence delay and then proceed to the previous slot (Slot 11), and so on until the EN\_OUT\_s assigned to Slot 1 turn off. When simultaneous powerdown is selected (r75h[0] set to '0'), all EN\_OUT\_s turn off at the same time.

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

Figure 3. Delay and Reset Timing

### Table 5. MON\_ and EN\_OUT\_ Assignment Registers

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION |

|---------------------|------------------|-----------|-------------|

| 7Eh                 | 27Eh             | [3:0]     | MON1        |

| / [1]               | 2/511            | [7:4]     | MON2        |

| 7Fh                 | 27Fh             | [3:0]     | MON3        |

| / [1]               | 2/511            | [7:4]     | MON4        |

| 80h                 | 280h             | [3:0]     | MON5        |

| 0011                | 20011            | [7:4]     | MON6        |

| 81h                 | 281h             | [3:0]     | MON7        |

| 0111                | 20111            | [7:4]     | MON8        |

| 0.015               | 000h             | [3:0]     | MON9        |

| 82h                 | 282h             | [7:4]     | MON10       |

| 026                 | 0006             | [3:0]     | MON11       |

| 83h                 | 283h             | [7:4]     | MON12       |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

Table 5. MON\_ and EN\_OUT\_ Assignment Registers (continued)

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION |

|---------------------|------------------|-----------|-------------|

| 84h                 | 284h             | [3:0]     | EN_OUT1     |

| 0411                | 20411            | [7:4]     | EN_OUT2     |

| 85h                 | 285h             | [3:0]     | EN_OUT3     |

| 0311                | 20311            | [7:4]     | EN_OUT4     |

| OCh                 | 286h             | [3:0]     | EN_OUT5     |

| 86h                 | 28011            | [7:4]     | EN_OUT6     |

| 07h                 | 007h             | [3:0]     | EN_OUT7     |

| 87h                 | 287h             | [7:4]     | EN_OUT8     |

| 88h                 | 0006             | [3:0]     | EN_OUT9     |

| 0011                | 288h             | [7:4]     | EN_OUT10    |

| 89h                 | 290h             | [3:0]     | EN_OUT11    |

| 09(1                | 289h             | [7:4]     | EN_OUT12    |

Table 6. MON\_ and EN\_OUT\_ Slot Assignment Codes

|      | SLOT ASSIGNMENT                     |                                                |  |  |  |  |

|------|-------------------------------------|------------------------------------------------|--|--|--|--|

| CODE | MON_ DESCRIPTION                    | EN_OUT_ DESCRIPTION                            |  |  |  |  |

| 0000 | Not assigned                        | Not assigned                                   |  |  |  |  |

| 0001 | Slot 1                              | Slot 1                                         |  |  |  |  |

| 0010 | Slot 2                              | Slot 2                                         |  |  |  |  |

| 0011 | Slot 3                              | Slot 3                                         |  |  |  |  |

| 0100 | Slot 4                              | Slot 4                                         |  |  |  |  |

| 0101 | Slot 5                              | Slot 5                                         |  |  |  |  |

| 0110 | Slot 6                              | Slot 6                                         |  |  |  |  |

| 0111 | Slot 7                              | Slot 7                                         |  |  |  |  |

| 1000 | Slot 8                              | Slot 8                                         |  |  |  |  |

| 1001 | Slot 9                              | Slot 9                                         |  |  |  |  |

| 1010 | Slot 10                             | Slot 10                                        |  |  |  |  |

| 1011 | Slot 11                             | Slot 11                                        |  |  |  |  |

| 1100 | Slot 12                             | Slot 12                                        |  |  |  |  |

| 1101 | Monitoring only, secondary sequence | General-purpose input (EN_OUT9-EN_OUT12 only)  |  |  |  |  |

| 1110 | Monitoring only, primary sequence   | General-purpose output (EN_OUT9-EN_OUT12 only) |  |  |  |  |

| 1111 | Not assigned                        | Not assigned                                   |  |  |  |  |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

**Table 7. tFAULT Delay Settings**

| CODE | DELAY |

|------|-------|

| 0000 | 120µs |

| 0001 | 150µs |

| 0010 | 250µs |

| 0011 | 380µs |

| 0100 | 600µs |

| 0101 | 1ms   |

| 0110 | 1.5ms |

| 0111 | 2.5ms |

| 1000 | 4ms   |

| 1001 | 6ms   |

| 1010 | 10ms  |

| 1011 | 15ms  |

| 1100 | 25ms  |

| 1101 | 40ms  |

| 1110 | 60ms  |

| 1111 | 100ms |

When the secondary sequence group is already powered down and EN or the Software Enable bit is set to '0', the reverse power-down sequence is similar to above, but starts from the last slot assigned to the primary sequence r7Dh[7:4]. After the last assigned slot is powered down the previous slot will power down and so on until Slot 0 is powered down.

To power down the secondary sequence group, drive EN2 low or set r75h[1] to '0'. The secondary reverse power-down sequence will start at Slot 12 and end at the primary sequence monitoring mode state at which point only the slots assigned to the primary sequence are active.

### **Voltage/Current Monitoring**

The MAX16065/MAX16066 feature an internal 10-bit ADC that monitors the MON\_ voltage inputs. An internal multiplexer cycles through each of the enabled inputs, taking less than 40µs for a complete monitoring cycle. Each acquisition takes approximately 3.2µs. At each multiplexer stop, the 10-bit ADC converts the analog input to a digital result and stores the result in a register. ADC conversion results are stored in registers r00h to r1Ah (see Table 10). Use the SMBus or JTAG serial interface to read ADC conversion results.

The MAX16065 provides twelve inputs, MON1–MON12, for voltage monitoring. The MAX16066 provides eight inputs, MON1–MON8, for voltage monitoring. Each input

voltage range is programmable in registers r43h to r45h (see Table 9). When MON\_ configuration registers are set to '11,' MON\_ voltages are not monitored, and the multiplexer does not stop at these inputs, decreasing the total cycle time. These inputs cannot be configured to trigger fault conditions.

The three programmable thresholds for each monitored voltage include an overvoltage, an undervoltage, and a secondary warning threshold that can be set in r73h[3] to be either an undervoltage or overvoltage threshold. See the *Faults* section for more information on setting overvoltage and undervoltage thresholds. All voltage thresholds are 8 bits wide. The 8 MSBs of the 10-bit ADC conversion result are compared to these overvoltage and undervoltage thresholds.

For any undervoltage or overvoltage condition to be monitored and any faults detected, the MON\_ input must be assigned to a sequence order or set to monitoring mode as described in the *Sequencing* section.

Inputs that are not enabled are not converted by the ADC; they contain the last value acquired before that channel was disabled.

The ADC conversion result registers are reset to 00h at boot-up. These registers are not reset when a reboot command is executed.

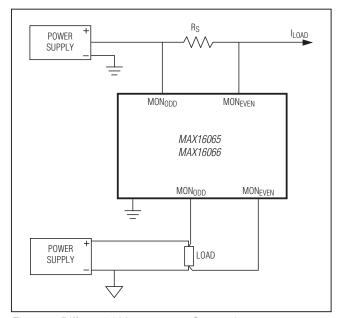

Configure the MAX16065/MAX16066 for differential mode in r46h (Table 9). The possible differential

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

pairs are MON1/MON2, MON3/MON4, MON5/MON6, MON7/MON8 with the first input always being at a higher voltage than the second. Use differential voltage sensing to eliminate voltage offsets or measure supply current. See Figure 4. In differential mode, the odd-numbered MON\_ input measures the absolute voltage with respect to GND while the result of the even input is the difference between the odd and even inputs. See Figure 4 for the typical differential measurement circuit.

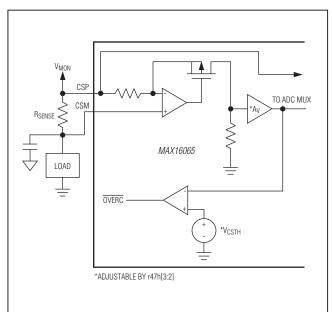

#### **Internal Current-Sense Amplifier**

The current-sense inputs, CSP/CSM, and a current-sense amplifier facilitate power monitoring (see Figure 5). The voltage on CSP relative to GND is also monitored by the ADC when the current-sense amplifier is enabled with r47h[0]. The conversion results are located in registers r19h and r1Ah (see Table 10). There are two selectable voltage ranges for CSP set by r47h[1], see Table 8. Although the voltage can be monitored over SMBus or JTAG, this voltage has no threshold comparators and cannot trigger any faults. Regarding the current-sense amplifier, there are four selectable ranges and the ADC output for a current-sense conversion is:

$$XADC = (VSENSE \times AV)/1.4V \times (28 - 1)$$

where X<sub>ADC</sub> is the 8-bit decimal ADC result in register r18h, V<sub>SENSE</sub> is V<sub>CSP</sub> - V<sub>CSM</sub>, and A<sub>V</sub> is the current-sense voltage gain set by r47h[3:2].

Figure 4. Differential Measurement Connections

In addition, there are two programmable current-sense trip thresholds: primary overcurrent and secondary overcurrent. For fast fault detection, the primary overcurrent threshold is implemented with an analog comparator connected to the internal OVERC signal. The OVERC signal can be output on one of the GPIO\_s. See the *General-Purpose Inputs/Outputs* section for configuring the GPIO\_ to output the OVERC signal. The primary threshold is set by:

#### ITH = VCSTH/RSENSE

where I<sub>TH</sub> is the current threshold to be set, V<sub>CSTH</sub> is the threshold set by r47h[3:2], and R<sub>SENSE</sub> is the value of the sense resistor. See Table 8 for a description of r47h. OVERC depends only on the primary overcurrent threshold. The secondary overcurrent threshold is implemented through ADC conversions and digital comparison set by r6Ch. The secondary overcurrent threshold includes programmable time delay options located in r73h[6:5]. Primary and secondary current-sense faults are enabled/disabled through r47h[0].

#### **General-Purpose Inputs/Outputs**

GPIO1-GPIO8 are programmable general-purpose inputs/outputs. GPIO1-GPIO8 are configurable as a manual reset input, a watchdog timer input and output, logic inputs/outputs, fault-dependent outputs. When programmed as outputs, GPIO\_s are open drain or pushpull. See Tables 12 and 13 for more detailed information on configuring GPIO1-GPIO8.

Figure 5. Current-Sense Amplifier

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

**Table 8. Overcurrent Primary Threshold and Current-Sense Control**

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT<br>RANGE | DESCRIPTION                                                                                                                                                                                                                                        |

|---------------------|------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                  | [0]          | 1 = Current sense is enabled<br>0 = Current sense is disabled                                                                                                                                                                                      |

|                     |                  | [1]          | 1 = CSP full-scale range is 14V<br>0 = CSP full-scale range is 7V                                                                                                                                                                                  |

| 47h                 | 247h             | [3:2]        | Overcurrent Primary Threshold and Current-Sense Gain Setting:  00 = 200mV threshold, A <sub>V</sub> = 6V/V  01 = 100mV threshold, A <sub>V</sub> = 12V/V  10 = 50mV threshold, A <sub>V</sub> = 24V/V  11 = 25mV threshold, A <sub>V</sub> = 48V/V |

| 73h                 | 273h             | [6:5]        | Overcurrent Secondary Threshold Deglitch:  00 = No delay  01 = 4ms  10 = 15ms  11 = 60ms                                                                                                                                                           |

**Table 9. ADC Configuration Registers**

| REGISTER ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                 |

|------------------|------------------|-----------|---------------------------------------------------------------------------------------------|

|                  | 243h             | [1:0]     | ADC1 Full-Scale Range:<br>00 = 5.6V<br>01 = 2.8V<br>10 = 1.4V<br>11 = Channel not converted |

| 401              |                  | [3:2]     | ADC2 Full-Scale Range:<br>00 = 5.6V<br>01 = 2.8V<br>10 = 1.4V<br>11 = Channel not converted |

| 43h              |                  | [5:4]     | ADC3 Full-Scale Range:  00 = 5.6V  01 = 2.8V  10 = 1.4V  11 = Channel not converted         |

|                  |                  | [7:6]     | ADC4 Full-Scale Range:<br>00 = 5.6V<br>01 = 2.8V<br>10 = 1.4V<br>11 = Channel not converted |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

**Table 9. ADC Configuration Registers (continued)**

| REGISTER ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                  |

|------------------|------------------|-----------|----------------------------------------------------------------------------------------------|

|                  | 244h             | [1:0]     | ADC5 Full-Scale Range:<br>00 = 5.6V<br>01 = 2.8V<br>10 = 1.4V<br>11 = Channel not converted  |

| 44b              |                  | [3:2]     | ADC6 Full-Scale Range:  00 = 5.6V  01 = 2.8V  10 = 1.4V  11 = Channel not converted          |

| 44h              |                  | [5:4]     | ADC7 Full-Scale Range:  00 = 5.6V  01 = 2.8V  10 = 1.4V  11 = Channel not converted          |

|                  |                  | [7:6]     | ADC8 Full-Scale Range:<br>00 = 5.6V<br>01 = 2.8V<br>10 = 1.4V<br>11 = Channel not converted  |

|                  | 245h             | [1:0]     | ADC9 Full-Scale Range 00 = 5.6V 01 = 2.8V 10 = 1.4V 11 = Channel not converted               |

| 45h              |                  | [3:2]     | ADC10 Full-Scale Range:<br>00 = 5.6V<br>01 = 2.8V<br>10 = 1.4V<br>11 = Channel not converted |

| 4511             |                  | [5:4]     | ADC11 Full-Scale Range: 00 = 5.6V 01 = 2.8V 10 = 1.4V 11 = Channel not converted             |

|                  |                  | [7:6]     | ADC12 Full-Scale Range: 00 = 5.6V 01 = 2.8V 10 = 1.4V 11 = Channel not converted             |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

**Table 9. ADC Configuration Registers (continued)**

| REGISTER ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION                                                 |

|------------------|------------------|-----------|-------------------------------------------------------------|

| 46h              | 246h             | [0]       | Differential Conversion ADC1-ADC2: 0 = Disabled 1 = Enabled |

|                  |                  | [1]       | Differential Conversion ADC3-ADC4: 0 = Disabled 1 = Enabled |

|                  |                  | [2]       | Differential Conversion ADC5-ADC6: 0 = Disabled 1 = Enabled |

|                  |                  | [3]       | Differential Conversion ADC7-ADC8: 0 = Disabled 1 = Enabled |

Table 10. ADC Conversion Results (Read Only)

| REGISTER ADDRESS | BIT RANGE | DESCRIPTION                   |

|------------------|-----------|-------------------------------|

| 00h              | [7:0]     | ADC1 result (MSB) bits 9-2    |

| 01h              | [7:6]     | ADC1 result (LSB) bits 1-0    |

| 02h              | [7:0]     | ADC2 result (MSB) bits 9-2    |

| 03h              | [7:6]     | ADC2 result (LSB) bits 1-0    |

| 04h              | [7:0]     | ADC3 result (MSB) bits 9-2    |

| 05h              | [7:6]     | ADC3 result (LSB) bits 1-0    |

| 06h              | [7:0]     | ADC4 result (MSB) bits 9-2    |

| 07h              | [7:6]     | ADC4 result (LSB) bits 1-0    |

| 08h              | [7:0]     | ADC5 result (MSB) bits 9-2    |

| 09h              | [7:6]     | ADC5 result (LSB) bits 1-0    |

| 0Ah              | [7:0]     | ADC6 result (MSB) bits 9-2    |

| 0Bh              | [7:6]     | ADC6 result (LSB) bits 1-0    |

| 0Ch              | [7:0]     | ADC7 result (MSB) bits 9-2    |

| 0Dh              | [7:6]     | ADC7 result (LSB) bits 1-0    |

| 0Eh              | [7:0]     | ADC8 result (MSB) bits 9-2    |

| 0Fh              | [7:6]     | ADC8 result (LSB) bits 1-0    |

| 10h              | [7:0]     | ADC9 result (MSB) bits 9-2    |

| 11h              | [7:6]     | ADC9 result (LSB) bits 1-0    |

| 12h              | [7:0]     | ADC10 result (MSB) bits 9-2   |

| 13h              | [7:6]     | ADC10 result (LSB) bits 1-0   |

| 14h              | [7:0]     | ADC11 result (MSB) bits 9-2   |

| 15h              | [7:6]     | ADC11 result (LSB) bits 1-0   |

| 16h              | [7:0]     | ADC12 result (MSB) bits 9-2   |

| 17h              | [7:6]     | ADC12 result (LSB) bits 1-0   |

| 18h              | [7:0]     | Current-sense ADC result      |

| 19h              | [7:0]     | CSP ADC output (MSB) bits 9-2 |

| 1Ah              | [7:6]     | CSP ADC output (LSB) bits 1-0 |

## 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

When GPIO1-GPIO8 are configured as general-purpose inputs/outputs, read values from the GPIO\_ports through r1Eh and write values to GPIO\_s through r3Eh. Note that r3Eh has a corresponding flash register, which programs the default state of a general-purpose output. See Table 11 for more information on reading and writing to the GPIO\_.

#### Fault1 and Fault2

GPIO1–GPIO8 are configurable as dedicated fault outputs, Fault1 or Fault2. Fault outputs can assert on one or more overvoltage, undervoltage, or early warning conditions for selected inputs, as well as the secondary overcurrent comparator. Fault1 and Fault2 dependencies are set using registers r36h to r3Ah. See Table 14. When a fault output depends on more than one MON\_, the fault output asserts when one or more MON\_ exceeds a programmed threshold voltage. These fault outputs act independently of the critical fault system, described in the *Critical Faults* section.

Table 11. GPIO\_ State Registers

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION        |

|---------------------|------------------|-----------|--------------------|

|                     |                  | [0]       | GPIO1 input state  |

|                     |                  | [1]       | GPIO2 input state  |

|                     |                  | [2]       | GPIO3 input state  |

| 4 F b               |                  | [3]       | GPIO4 input state  |

| 1Eh                 | _                | [4]       | GPIO5 input state  |

|                     |                  | [5]       | GPIO6 input state  |

|                     |                  | [6]       | GPIO7 input state  |

|                     |                  | [7]       | GPIO8 input state  |

|                     |                  | [0]       | GPIO1 output state |

|                     | 23Eh             | [1]       | GPIO2 output state |

|                     |                  | [2]       | GPIO3 output state |

| 3Eh                 |                  | [3]       | GPIO4 output state |

| ) SEII              |                  | [4]       | GPIO5 output state |

|                     |                  | [5]       | GPIO6 output state |

|                     |                  | [6]       | GPIO7 output state |

|                     |                  | [7]       | GPIO8 output state |

**Table 12. GPIO\_ Configuration Registers**

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION               |

|---------------------|------------------|-----------|---------------------------|

|                     |                  | [2:0]     | GPIO1 configuration       |

| 3Fh                 | 23Fh             | [5:3]     | GPIO2 configuration       |

|                     |                  | [7:6]     | GPIO3 configuration (LSB) |

|                     |                  | [0]       | GPIO3 configuration (MSB) |

| 401-                | 0.401-           | [3:1]     | GPIO4 configuration       |

| 40h                 | 240h             | [6:4]     | GPIO5 configuration       |

|                     |                  | [7]       | GPIO6 configuration (LSB) |

|                     |                  | [1:0]     | GPIO6 configuration (MSB) |

| 41h                 | 241h             | [4:2]     | GPIO7 configuration       |

|                     |                  | [7:5]     | GPIO8 configuration       |

# 12-Channel/8-Channel, Flash-Configurable System Managers with Nonvolatile Fault Registers

Table 12. GPIO\_ Configuration Registers (continued)

| REGISTER<br>ADDRESS | FLASH<br>ADDRESS | BIT RANGE | DESCRIPTION                                                    |

|---------------------|------------------|-----------|----------------------------------------------------------------|

|                     |                  | [0]       | Output Configuration for GPIO1: 0 = Push-pull 1 = Open drain   |

|                     |                  | [1]       | Output Configuration for GPIO2:  0 = Push-pull  1 = Open drain |

|                     |                  | [2]       | Output Configuration for GPIO3:  0 = Push-pull  1 = Open drain |

| 101                 | 242h             | [3]       | Output Configuration for GPIO4:  0 = Push-pull  1 = Open drain |

| 42h                 |                  | [4]       | Output Configuration for GPIO5:  0 = Push-pull  1 = Open drain |

|                     |                  | [5]       | Output Configuration for GPIO6:  0 = Push-pull  1 = Open drain |

|                     |                  | [6]       | Output Configuration for GPIO7:  0 = Push-pull  1 = Open drain |

|                     |                  | [7]       | Output Configuration for GPIO8:  0 = Push-pull  1 = Open drain |

Table 13. GPIO\_ Function Configuration Bits

|     | GPIO1            | GPIO2            | GPIO3             | GPIO4                 | GPIO5            | GPIO6            | GPIO7            | GPIO8                 |

|-----|------------------|------------------|-------------------|-----------------------|------------------|------------------|------------------|-----------------------|

| 000 | Logic input      | Logic<br>input   | Logic input       | Logic input           | Logic input      | Logic<br>input   | Logic input      | Logic input           |

| 001 | Logic output     | Logic<br>output  | Logic output      | Logic output          | Logic output     | Logic<br>output  | Logic output     | Logic<br>output       |