Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

EVALUATION KIT

## **AVAILABLE** EEPROM-Programmable, High-Voltage, 350mA LED Drivers with LED Current Foldback

### **General Description**

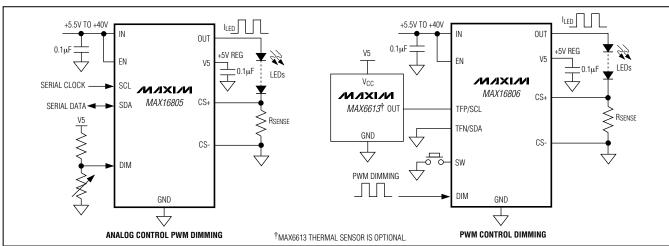

The MAX16805/MAX16806 LED drivers eliminate the need for microcontrollers or switch-mode converters for automotive interior dome, map, and courtesy light applications. An EEPROM-programmable LED currentsense reference simplifies production by using one sense resistor to set the LED current for all LED bins. A dual-mode DIM pin and an on-board 200Hz ramp generator allow for PWM dimming with an analog or PWM control signal. The analog control signal at dimming input DIM allows for the "theater dimming" effect to be implemented. Fast turn-on/-off times ensure a widerange PWM operation, while waveshaping circuitry minimizes EMI. EEPROM-programmable LED current foldback makes it possible to operate at a high input voltage, while saving the cost and space associated with having a large heatsink. The MAX16806 works with an external thermal sensor to maintain maximum LED junction temperature by folding back the LED current. The thermal foldback temperature knee and slope are EEPROM programmable. The MAX16806 SW pin supplies necessary wetting current to a momentary switch.

### **Applications**

Automotive Interior: Map, Dome, and Courtesy Lighting

Automotive Exterior:

Rear Combination Light (RCL) Daytime Running Light (DRL) Adaptive Front Light

**Emergency Vehicle Warning Lights**

Navigation and Marine Indicators

### **Features**

- **♦** EEPROM or I<sup>2</sup>C Dynamically Programmable: LED Current Foldback for High Input Voltage **LED Current Reference LED Current Thermal Foldback (MAX16806)**

- ♦ On-Board 200Hz Ramp Generator Eliminates the Need for µC PWM Signal

- ♦ Flexible Analog or PWM Control for PWM or **Theater Dimming**

- **♦** Wetting Current and Debounce for Momentary Switch (MAX16806)

- ♦ 5.5V to 40V Input with Up to 39V Output Capability

- ♦ 35mA to 350mA Adjustable LED Current

- ♦ Waveshaping Minimizes EMI During Dimming

- **Output Short-Circuit and Overtemperature** Protection

- ◆ -40°C to +125°C Operating Temperature Range

### **Ordering Information**

| PART         | TEMP RANGE      | PIN<br>PACKAGE | PKG<br>CODE |

|--------------|-----------------|----------------|-------------|

| MAX16805ATP+ | -40°C to +125°C | 20 TQFN-EP**   | T2055M-5    |

| MAX16806ATP+ | -40°C to +125°C | 20 TQFN-EP**   | T2055M-5    |

<sup>+</sup>Denotes lead-free package.

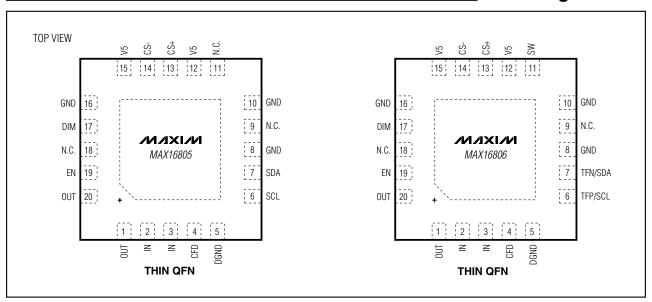

Pin Configurations appear at end of data sheet.

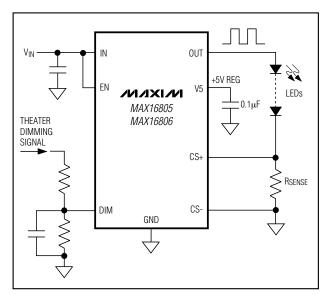

### **Typical Operating Circuits**

MIXIM

Maxim Integrated Products 1

<sup>\*\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| IN to GND                                  | 0.3V to +45V                     |

|--------------------------------------------|----------------------------------|

| DIM, OUT, EN to GND                        | 0.3V to (V <sub>IN</sub> + 0.3V) |

| IN Slew Rate (20V < V <sub>IN</sub> < 45V) | 250mV/µs                         |

| SDA, SCL (MAX16805), TFN/SDA,              | ·                                |

| TFP/SCL (MAX16806) to GND                  | 0.3V to +6V                      |

| CFD, CS+, V5 to GND                        | 0.3V to +6V                      |

| DGND and CS- to GND                        | 0.3V to +0.3V                    |

| OUT Short Circuited to GND Duration (      | V <sub>IN</sub> < +16V)1 hour    |

|                                            |                                  |

| Maximum Current into Any Pin (except in and OUT)±20mA  |

|--------------------------------------------------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )  |

| 20-Pin Thin QFN (derate 34.5mW/°C above +70°C)2758.6mW |

| Operating Temperature Range40°C to +125°C              |

| Junction Temperature+150°C                             |

| Storage Temperature Range65°C to +150°C                |

Lead Temperature (soldering, 10s).....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=V_{EN}=12V,~C_{V5}=0.1\mu F,~I_{V5}=0,~CS-=GND,~R_{SENSE}=0.56\Omega,~V_{DIM}=4V,~DGND=GND,~TFP/SCL=5V,~TFN/SDA=0V,~SW=CFD=Open,~T_A=T_J=-40^{\circ}C~to~+125^{\circ}C,~unless~otherwise~noted.~Typical~values~are~at~T_A=+25^{\circ}C.)~(Note~1)$

| PARAMETER                            | SYMBOL            | CONE                                                                          | DITIONS                                   | MIN | TYP | MAX | UNITS |  |

|--------------------------------------|-------------------|-------------------------------------------------------------------------------|-------------------------------------------|-----|-----|-----|-------|--|

| Supply Voltage Range                 | VIN               | (Note 2)                                                                      |                                           | 5.5 |     | 40  | V     |  |

| Ground Current                       | IG                | I <sub>LOAD</sub> = 350mA                                                     | I <sub>LOAD</sub> = 350mA                 |     | 2.5 | 4.5 | mA    |  |

| Shutdown Supply Current              | Ishdn             | V <sub>EN</sub> ≤ 0.3V                                                        |                                           |     | 12  | 40  | μΑ    |  |

| Guaranteed Output Current            | lout              | $R_{SENSE} = 0.55\Omega$                                                      |                                           | 350 |     |     | mA    |  |

| Output Current Accuracy              |                   | 35mA < I <sub>OUT</sub> < 350r<br>not included                                | mA, R <sub>SENSE</sub> tolerance          |     |     | 3.0 | %     |  |

| Dunnant Valtage (Nata 2)             | 4)/               | $I_{OUT} = 350 \text{mA}, 12 \text{V} < V_{IN} < 40 \text{V}$                 |                                           |     | 0.4 | 1.2 | V     |  |

| Dropout Voltage (Note 3)             | ΔV <sub>DO</sub>  | I <sub>OUT</sub> = 350mA, 6.5V                                                | OUT = 350mA, 6.5V < V <sub>IN</sub> < 12V |     | 0.5 | 1.5 | V     |  |

| Output Current Slew Rate             |                   | Current rising, DIM r                                                         | Current rising, DIM rising to 4V          |     | 17  |     | Δ.    |  |

| (External PWM Signal at DIM)         |                   | Current falling, DIM                                                          | Current falling, DIM falling to 0.6V      |     | 17  |     | mA/µs |  |

| Short-Circuit Current                |                   | V <sub>OUT</sub> = 0V                                                         | V <sub>OUT</sub> = 0V                     |     | 600 |     | mA    |  |

| ENABLE INPUT                         |                   |                                                                               |                                           | •   |     |     |       |  |

| EN Input Current                     | I <sub>EN</sub>   |                                                                               |                                           |     |     | 100 | nA    |  |

| EN Input-Voltage High                | VIH               |                                                                               |                                           | 2.8 |     |     | V     |  |

| EN Input-Voltage Low                 | VIL               |                                                                               |                                           |     |     | 0.6 | V     |  |

| Enable Turn-On Time                  | ton               | EN rising edge to 90                                                          | EN rising edge to 90% of OUT              |     | 225 |     | μs    |  |

| 5V REGULATOR                         |                   |                                                                               |                                           | •   |     |     |       |  |

| Output Voltage Regulation            |                   |                                                                               | 0 < I <sub>V5</sub> < 0.5mA,<br>SW = GND  | 4.9 | 5.1 | 5.3 |       |  |

| (MAX16806)                           | V5                | 6.5V < V <sub>IN</sub> < 40V                                                  | 0 < Iv5 < 2mA,<br>SW = open               | 4.9 | 5.1 | 5.3 | V     |  |

| Output Voltage Regulation (MAX16805) | V5                | 0 < I <sub>V5</sub> < 2mA, 6.5V < V <sub>IN</sub> < 40V                       |                                           | 4.9 | 5.1 | 5.3 | ٧     |  |

| CURRENT SENSE                        | •                 | -                                                                             |                                           |     |     |     | •     |  |

| Regulated R <sub>SENSE</sub> Voltage | V <sub>RSNS</sub> | VSENSE = [VCS+ - VCS-], Binning Adjustment register at factory default (0x0F) |                                           | 192 | 198 | 204 | mV    |  |

| Input Current (CS+)                  |                   | $V_{CS+} = 210 \text{mV}$                                                     |                                           | 12  |     |     | μΑ    |  |

| Input Current (CS-)                  |                   | V <sub>CS+</sub> = 210mV                                                      |                                           |     |     | -75 | μΑ    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=V_{EN}=12V,\ C_{V5}=0.1\mu\text{F},\ I_{V5}=0,\ CS\text{-}=GND,\ R_{SENSE}=0.56\Omega,\ V_{DIM}=4V,\ DGND=GND,\ TFP/SCL=5V,\ TFN/SDA=0V,\ SW=CFD=Open,\ T_A=T_J=-40^{\circ}C\ to+125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.$ ) (Note 1)

| PARAMETER                                                 | SYMBOL                   | CONDITIONS                                                     | MIN         | TYP   | MAX   | UNITS |  |

|-----------------------------------------------------------|--------------------------|----------------------------------------------------------------|-------------|-------|-------|-------|--|

| Minimum Regulated VSENSE Programming Range                | VSENSE(MIN)              |                                                                | 99.4        | 103   | 106.6 | mV    |  |

| Maximum Regulated VSENSE Programming Range                | VSENSE(MAX)              |                                                                | 192 198 204 |       | 204   | Tilv  |  |

| Regulated V <sub>SENSE</sub> Default Voltage              | VSENSE(DEF)              | Binning Adjustment register at factory default (0x0F)          |             | 198   |       | mV    |  |

| EXTERNAL PWM DIMMING INPU                                 | Т                        |                                                                |             |       |       |       |  |

| DIM Input Current                                         |                          |                                                                |             |       | 0.5   | μΑ    |  |

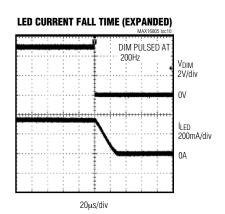

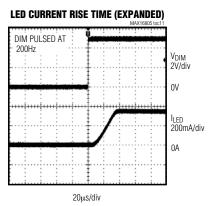

| Turn-On Time                                              | ton                      | After DIM rising to 4V (Note 4)                                |             | 28    | 52    | μs    |  |

| Turn-Off Time                                             | toff                     | After DIM falling to 0.6V (Note 4)                             |             | 19    | 38    | μs    |  |

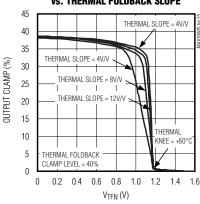

| THERMAL FOLDBACK (MAX168)                                 | 06 with MAX66            | 13)                                                            |             |       |       |       |  |

| Maximum Thermal Foldback<br>Knee Point Programming Range  | TF <sub>KNEE</sub> (MAX) |                                                                | 326         | 335   | 354   |       |  |

| Minimum Thermal Foldback Knee<br>Point Programming Range  | TF <sub>KNEE</sub> (MIN) |                                                                | 1143        | 1174  | 1213  | mV    |  |

| Minimum Thermal Foldback Temperature Programming Range    | TF <sub>(MIN)</sub>      |                                                                |             | +60   |       |       |  |

| Maximum Thermal Foldback Temperature Programming Range    | TF <sub>(MAX)</sub>      |                                                                |             | +135  |       | °C    |  |

| Thermal Foldback Default<br>Threshold Temperature         | V <sub>TH</sub>          | Thermal Foldback Knee Point register at factory default (0x00) |             | +60   |       | °C    |  |

| Thermal Foldback Default<br>Threshold Voltage             | TF <sub>VTH</sub>        |                                                                |             | 1.174 |       | V     |  |

| Minimum Thermal Foldback Slope                            | TF <sub>SL(MIN)</sub>    |                                                                | 3.88        | 4     | 4.12  | V/V   |  |

| Maximum Thermal Foldback Slope                            | TF <sub>SL(MAX)</sub>    |                                                                | 15.52       | 16    | 16.48 | V/V   |  |

| Thermal Foldback Default Slope                            |                          | Thermal Foldback Slope Gain register at factory default (0x03) |             | 4     |       | V/V   |  |

| TFP/SCL (SCL for MAX16805)                                | \/                       | I <sup>2</sup> C interface active                              | -0.3        |       | V5    | V     |  |

| Voltage Compliance Range                                  | VTFP                     | Remote thermal sensor active                                   | +0.3        |       | V5    | V     |  |

| TFN/SDA (SDA for MAX16805)<br>Voltage Compliance Range    | V <sub>TFN</sub>         |                                                                | -0.3        |       | V5    | V     |  |

| Minimum Thermal Foldback<br>Clamp Current Reduction Range | TF <sub>C(MIN)</sub>     | +25°C ≤ T <sub>A</sub> ≤ +125°C                                |             | 40    |       | %     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=V_{EN}=12V,\ C_{V5}=0.1\mu\text{F},\ I_{V5}=0,\ CS\text{-}=GND,\ R_{SENSE}=0.56\Omega,\ V_{DIM}=4V,\ DGND=GND,\ TFP/SCL=5V,\ TFN/SDA=0V,\ SW=CFD=Open,\ T_A=T_J=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.$ ) (Note 1)

| PARAMETER                                                 | SYMBOL                | CONDITIONS                                                                                       | MIN  | TYP   | MAX  | UNITS  |  |

|-----------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|------|-------|------|--------|--|

| Maximum Thermal Foldback Clamp Current Reduction Range    | TF <sub>C(MAX)</sub>  | +25°C ≤ T <sub>A</sub> ≤ +125°C                                                                  |      | 100   |      | %      |  |

| Default Thermal Foldback Clamp<br>Current Reduction Range | TF <sub>DEF</sub>     | Thermal Foldback Clamp register at factory default (0x07), +25°C ≤ T <sub>A</sub> ≤ +125°C       |      | 40    |      | %      |  |

| THERMAL PROTECTION                                        |                       |                                                                                                  |      |       |      |        |  |

| Thermal Shutdown Temperature                              | T <sub>J</sub> (SHDN) |                                                                                                  |      | +155  |      | °C     |  |

| Thermal Shutdown Hysteresis                               |                       |                                                                                                  |      | +23   |      | °C     |  |

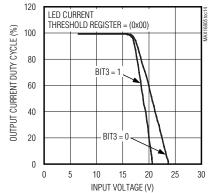

| LED CURRENT FOLDBACK                                      |                       |                                                                                                  |      |       |      |        |  |

| Minimum Input LED Current Foldback Range                  | VCFD(MIN)             |                                                                                                  |      | 11.4  |      | V      |  |

| Maximum Input LED Current Foldback Range                  | VCFD(MAX)             |                                                                                                  |      | 16.4  |      | V      |  |

| LED Current Foldback Default<br>Level                     | VCFD                  | LED Current Foldback Threshold register at factory default (0x00)                                |      | 16.4  |      | V      |  |

| LED Current Foldback Voltage                              |                       | V <sub>IN</sub> > 11V, CFD register bit 3 = 0                                                    | 0.71 |       |      | Motor  |  |

| Step Size                                                 |                       | V <sub>IN</sub> > 11V, CFD register bit 3 = 1                                                    |      | 0.355 |      | V/step |  |

| INTERNAL RAMP GENERATOR                                   |                       |                                                                                                  |      |       |      |        |  |

| Internal RAMP Frequency                                   | fRAMP                 |                                                                                                  | 176  | 200   | 224  | Hz     |  |

| External Sync Frequency Range                             | fDIM                  |                                                                                                  | 80   |       | 2000 | Hz     |  |

| External Sync Voltage Low                                 |                       |                                                                                                  |      |       | 0.4  | V      |  |

| External Sync Voltage High                                |                       |                                                                                                  | 2.8  |       |      | V      |  |

|                                                           |                       | V <sub>DIM</sub> = 0V                                                                            |      | 0     |      |        |  |

| Output Current Duty Cycle                                 | I <sub>DC</sub>       | V <sub>DIM</sub> > (V <sub>RAMP</sub> + 0.4V) (MAX16806),<br>V <sub>DIM</sub> > +3.3V (MAX16805) |      | 100   |      | %      |  |

| Minimum Ramp Peak<br>Programming Range                    | VRAMP(MIN)            |                                                                                                  | 1.49 | 1.55  | 1.60 | V      |  |

| Maximum Ramp Peak<br>Programming Range                    | VRAMP(MAX)            |                                                                                                  | 2.77 | 2.88  | 3.00 | V      |  |

| Ramp Peak Default Voltage                                 |                       | Ramp Peak register at factory default (0x07)                                                     |      | 2.88  |      | V      |  |

| Ramp Offset Voltage                                       |                       |                                                                                                  |      | 210   |      | mV     |  |

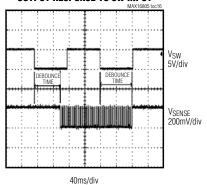

| MOMENTARY SWITCH INTERFA                                  | CE (SW) (MAX          | 16806)                                                                                           |      |       |      |        |  |

| SW Pullup Current                                         | Isw                   | V <sub>SW</sub> = 0V                                                                             | 1    |       | 3    | mA     |  |

| SW Input-Voltage High                                     | VIH                   | I <sub>SW</sub> = 100μA                                                                          | 4    |       |      | V      |  |

| SW Input-Voltage Low                                      | VIL                   |                                                                                                  |      |       | 0.4  | V      |  |

| Minimum Pulse Width                                       |                       |                                                                                                  | 120  |       |      | ms     |  |

| Minimum Debounce Time                                     |                       |                                                                                                  | 40   |       |      | ms     |  |

4 \_\_\_\_\_\_ *NIXIN*

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=V_{EN}=12V,\ C_{V5}=0.1\mu\text{F},\ I_{V5}=0,\ CS\text{-}=GND,\ R_{SENSE}=0.56\Omega,\ V_{DIM}=4V,\ DGND=GND,\ TFP/SCL=5V,\ TFN/SDA=0V,\ SW=CFD=Open,\ T_A=T_J=-40^{\circ}\text{C}\ to\ +125^{\circ}\text{C},\ unless\ otherwise\ noted.}$

| PARAMETER                                         | SYMBOL          | CONDITIONS                                                                                                                                                                                  | MIN | TYP | MAX | UNITS |

|---------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| EEPROM                                            |                 |                                                                                                                                                                                             |     |     |     |       |

| V <sub>IN</sub> Voltage for EEPROM<br>Programming |                 |                                                                                                                                                                                             | 20  | 22  | 24  | V     |

| EEPROM Data-Retention Time                        |                 |                                                                                                                                                                                             | 10  |     |     | Years |

| I <sup>2</sup> C DIGITAL INPUTS (TFP/SCL, 1       | FN/SDA) (Not    | e 5)                                                                                                                                                                                        |     |     |     |       |

| Logic Input-Voltage High                          | VIH             |                                                                                                                                                                                             | 2.8 |     |     | V     |

| Logic Input-Voltage Low                           | VIL             |                                                                                                                                                                                             |     |     | 0.8 | V     |

| Input Capacitance                                 |                 |                                                                                                                                                                                             |     | 5   |     | pF    |

| SDA Output Voltage Low                            | V <sub>OL</sub> | ISINK = 3mA                                                                                                                                                                                 |     |     | 0.4 | V     |

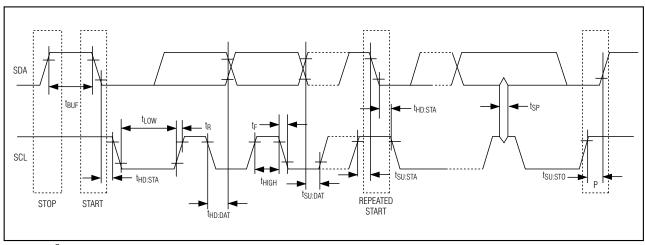

| I <sup>2</sup> C INTERFACE TIMING (Figure         | 1)              |                                                                                                                                                                                             |     |     |     |       |

| Serial Clock Frequency                            | fscL            |                                                                                                                                                                                             |     |     | 400 | kHz   |

| Bus Free Time Between STOP and START Condition    | tBUF            |                                                                                                                                                                                             | 1.3 |     |     | μs    |

| START Condition Hold Time                         | thd:Sta         |                                                                                                                                                                                             | 0.6 |     |     | μs    |

| Clock Low Period                                  | tLOW            |                                                                                                                                                                                             | 1.3 |     |     | μs    |

| Clock High Period                                 | thigh           |                                                                                                                                                                                             | 0.6 |     |     | μs    |

| Repeat START Condition Setup<br>Time              | tsu:sta         |                                                                                                                                                                                             | 0.6 |     |     | μs    |

| Data Hold Time                                    | tHD:DAT         | A master device must provide a hold time of at least 300ns for the SDA signal (referred to V <sub>IL</sub> of the SCL signal) in order to bridge the undefined region of SCL's falling edge | 0   |     | 0.9 | μs    |

| Data Setup Time                                   | tsu:dat         |                                                                                                                                                                                             | 100 |     |     | ns    |

| Receive SCL/SDA Rise Time                         | t <sub>R</sub>  |                                                                                                                                                                                             |     |     | 300 | ns    |

| Receive SCL/SDA Fall Time                         | tF              |                                                                                                                                                                                             |     |     | 250 | ns    |

| STOP Condition Setup Time                         | tsu:sto         |                                                                                                                                                                                             | 0.6 |     |     | μs    |

| Pulse Width of Spike Suppressed                   | tsp             |                                                                                                                                                                                             |     | 50  |     | ns    |

| Transmit SDA Fall Time                            |                 | ISINK ≤ 6mA, C <sub>B</sub> ≤ 400pF (Note 6)                                                                                                                                                |     |     | 250 | ns    |

- Note 1: All devices 100% production tested at  $T_J = +25$ °C. Limits over the operating temperature range are guaranteed by design.

- Note 2: Resistors were added from OUT to CS+ to aid with the power dissipation during testing.

- Note 3: Dropout is measured as follows: Connect a resistor from OUT to CS+. Connect R<sub>SENSE</sub> = 0.56Ω from CS+ to CS-. Set V<sub>IN</sub> = V<sub>OUT</sub> +3V (record V<sub>OUT</sub> as V<sub>OUT1</sub>). Reduce V<sub>IN</sub> until V<sub>OUT</sub> = 0.97 x V<sub>OUT1</sub> (record as V<sub>IN2</sub> and V<sub>OUT2</sub>). ΔV<sub>DO</sub> = V<sub>IN2</sub> V<sub>OUT2</sub>.

- Note 4:  $t_{ON}$  time includes the delay and the rise time needed for  $l_{OUT}$  to reach 90% of its final value.  $t_{OFF}$  time is the time needed for  $l_{OUT}$  to drop below 10%. See the *Typical Operating Characteristics*.  $t_{ON}$  and  $t_{OFF}$  are tested with 13 $\Omega$  from OUT to CS+.

- Note 5: TPF/SCL (SCL for MAX16805) and TPN/SDA (SDA for the MAX16805) are I<sup>2</sup>C interface compatible only when the MAX16805/MAX16806 are the only parts on the bus for production programming.

- Note 6: CB is the total bus capacitance.

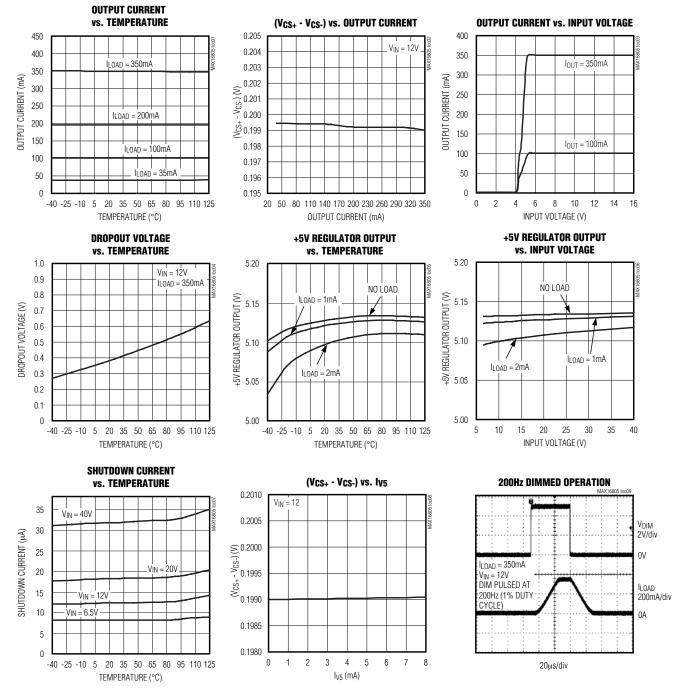

### **Typical Operating Characteristics**

$(V_{IN}=12V,V_{EN}=V_{IN},C_{V5}=0.1\mu\text{F},I_{V5}=0,CS\text{-}=GND,R_{SENSE}=0.56\Omega,connect OUT to CS+,V_{DIM}=4V,SW=V_{FD}=open,V_{TEP/SC}=5V,V_{TEN/SD}=GND,DGND=GND,T_A=+25^{\circ}C,unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{IN}=12V,V_{EN}=V_{IN},C_{V5}=0.1\mu\text{F},I_{V5}=0,C\text{S-}=\text{GND},R_{SENSE}=0.56\Omega,\text{connect OUT to CS+},V_{DIM}=4V,SW=V_{FD}=\text{open},V_{TFP/SC}=5V,V_{TFN/SD}=\text{GND},D\text{GND}=\text{GND},T_{A}=+25^{\circ}\text{C},\text{unless otherwise noted.})$

#### OUTPUT CLAMP vs. Thermal Foldback Slope

### **Pin Description**

| Р         | IN       |         |                                                                                                                                                                                       |

|-----------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16805  | MAX16806 | NAME    | FUNCTION                                                                                                                                                                              |

| 1, 20     | 1, 20    | OUT     | Current Regulated Output. Connect pins 1 and 20.                                                                                                                                      |

| 2, 3      | 2, 3     | IN      | Input Supply. Bypass IN with a $0.1 \mu F$ (min) capacitor to GND. Connect pins 2 and 3.                                                                                              |

| 4         | 4        | CFD     | LED Current Foldback Dimming Enable Input. Leave CFD unconnected to enable the current foldback dimming function. Drive CFD low to disable the LED current foldback dimming function. |

| 5         | 5        | DGND    | Digital Ground. Connect to GND.                                                                                                                                                       |

| 6         | _        | SCL     | I <sup>2</sup> C Serial Clock Input                                                                                                                                                   |

| 7         | _        | SDA     | I <sup>2</sup> C Serial-Data Input/Output                                                                                                                                             |

| 8, 10, 16 | 8, 10,16 | GND     | Ground                                                                                                                                                                                |

| 9, 11, 18 | 9, 18    | N.C.    | No Connection. Leave unconnected (internal connection).                                                                                                                               |

| 12, 15    | 12, 15   | V5      | 5V Regulated Output. Connect a 0.1µF capacitor from V5 to GND. Connect pin 12 to 15.                                                                                                  |

| 13        | 13       | CS+     | Positive Input of the Internal Differential Amplifier. Connect the current-sense resistor between CS+ and CS- to program the output current level.                                    |

| 14        | 14       | CS-     | Negative Input of the Internal Differential Amplifier. Connect the current-sense resistor between CS- and CS+ to program the output current level.                                    |

| 17        | 17       | DIM     | Dimming Input. See the Dimming Input (DIM) section.                                                                                                                                   |

| 19        | 19       | EN      | Enable Input. Drive EN high to enable the output and the 5V regulator.                                                                                                                |

| _         | 11       | SW      | Momentary Switch Interface. See the <i>Momentary Switch Interface (SW)</i> section.                                                                                                   |

|           | 6        | TFP/SCL | Thermal Foldback Positive Input/I <sup>2</sup> C Serial Clock Input. See the <i>Thermal Sensor Inputs/I<sup>2</sup>C Interface (TFP/SCL and TFN/SDA)</i> section.                     |

| _         | 7        | TFN/SDA | Thermal Foldback Negative Input/I <sup>2</sup> C Serial-Data Input/Output. See the <i>Thermal Sensor Inputs/I<sup>2</sup>C Interface (TFP/SCL and TFN/SDA)</i> section.               |

| EP        | EP       | EP      | Exposed Pad. Connect to the ground plane for improved power dissipation. Do not use as a ground connection for the part.                                                              |

8 \_\_\_\_\_\_ NIXI/N

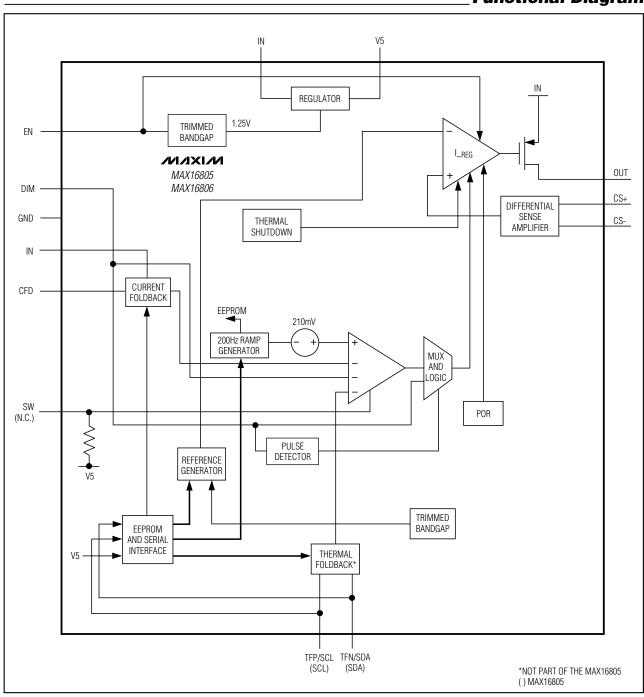

### **Functional Diagram**

Figure 1. I<sup>2</sup>C Serial Interface Timing Diagram

### Detailed Description

The MAX16805/MAX16806 are constant-current regulators that provide up to 350mA of current to one or more strings of high-brightness LEDs. A wide operating input voltage range of 5.5V to 40V makes the devices ideal for automotive applications. The MAX16805/MAX16806 feature the I<sup>2</sup>C interface that allows communication with the internal dynamic registers and EEPROM.

Dynamic registers control the MAX16805/MAX16806 functions and can be updated in real time through the I<sup>2</sup>C interface. See Table 2 for register addresses. Turning off the input voltage clears the dynamic register contents. To save settings, store them into the EEPROM. The MAX16805/MAX16806 load the stored settings into the dynamic registers at power-up. In addition, during normal operation a write command to the EEPROM Content Transfer register loads the stored settings into the dynamic registers. Information stored can be transferred into dynamic registers after issuing a "write" command to the EEPROM Content Transfer register.

The MAX16805/MAX16806's 5V regulator (V5) provides up to 2mA of current to external circuitry. However, the MAX16806's 5V regulator can deliver 2mA of output current only when the momentary switch is not used. When the momentary switch is active, the MAX16806 achieves up to 0.5mA of current. In addition, the MAX16805/MAX16806 feature thermal and output short-circuit protection. The wide operating voltage range helps protect the device against large transients up to 45V such as those found in load dump situations.

The MAX16805/MAX16806 use a feedback loop to control the output current. The differential voltage across the sense resistor is compared to a fixed reference voltage and the error is amplified to serve as the drive to the internal pass device, see the *Functional Diagram*. The MAX16805/MAX16806 offer a programmable LED current reference using the Binning Adjustment register.

These devices are current controllers internally optimized for driving the impedance range expected from 1 to 10 (or more) high-brightness LEDs.

### **Dimming Input (DIM)**

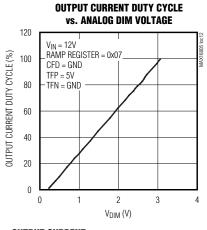

The MAX16805/MAX16806's dimming input operates with either an analog or PWM control signal. If the pulse detector detects three edges of a PWM signal with a frequency range between 80Hz to 2kHz, the MAX16805/MAX16806 synchronize to external PWM input signal and pulse-width-modulate the LED current. If an analog control signal is applied to DIM, the MAX16805/MAX16806 compare the DC input to an internally generated 200Hz ramp to pulse-width-modulate the LED current. The maximum peak value of the 200Hz ramp can be programmed using the Ramp Peak register. This allows the LED current to be adjusted through the I<sup>2</sup>C interface from 50% (typ) to 100% in real time when V<sub>DIM</sub> is 1.54V.

The output current duty cycle is adjustable from 0% to 100% (0.21V < VDIM < 3.1V).

Use the following formula to calculate the output current duty cycle:

Duty cycle = (VDIM - 0.21V) / VRAMP

The dimming feature can be used for LED brightness adjustment (see the *Typical Operating Circuits*) and theater dimming. If the external PWM signal is used, theater dimming can be achieved by varying the PWM duty cycle. Figure 2 shows a simple circuit that implements theater dimming with a DC input signal.

## Thermal Sensor Inputs/I<sup>2</sup>C Interface (TFP/SCL and TFN/SDA)

The MAX16806 features dual-function inputs, TFP/SCL and TFN/SDA. In programming mode, TFP/SCL and TFN/SDA serve as the I<sup>2</sup>C serial communication interface. TFP/SCL and TFN/SDA also serve as inputs for analog signals generated by an external temperature sensor such as the MAX6613. When the thermal sensor is not used, connect TFP/SCL and TFN/SDA through  $50k\Omega$  resistors to V5 and GND, respectively.

The MAX16805 does not offer dual-function inputs. SCL and SDA are used only to communicate with the MAX16805 through the I<sup>2</sup>C interface.

### Momentary Switch Interface (SW)

The MAX16806 offers a momentary switch (SW) that overrides the analog dimming signal by latching the output current to 100% duty cycle. The MAX16806 does not override external PWM signal at DIM or dimming caused by thermal or LED current foldback. To latch the output current into a 100% duty cycle, press SW once. To restore the initial duty cycle determined by the DC level at DIM, press SW again. The MAX16806 provides a minimum of 1mA of wetting current to the momentary switch.

#### **Overtemperature Protection**

The MAX16805/MAX16806 enter a thermal shutdown in the event of overheating. This typically occurs in overload or output short-circuit conditions. When the junction temperature exceeds  $T_J = +155^{\circ}C$  (typ), the internal thermal protection circuitry turns off the pass device. The MAX16805/MAX16806 recover from thermal shutdown once the junction temperature drops by +23°C (typ). This feature allows self-protection by thermally cycling in the event of a short-circuit or overload condition.

### **Digital Interface**

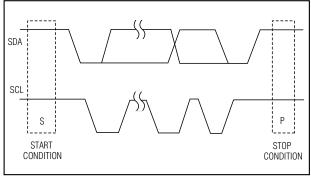

The MAX16805/MAX16806 feature an I<sup>2</sup>C, 2-wire serial interface consisting of a bidirectional serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX16805/MAX16806 and the master device at rates

Figure 2. Theater Dimming Light

Figure 3. I<sup>2</sup>C Communication Start and Stop Conditions

up to 400kHz. The master (typically a microcontroller) initiates data transfer on the bus and generates SCL.

### **Start and Stop Conditions**

Both SCL and SDA remain high when the interface is not busy. A master controller signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL is high. The master controller issues a STOP condition by transitioning the SDA from low to high while SCL is high, when it finishes communicating with the slave. The bus is then free for another transmission (Figure 3).

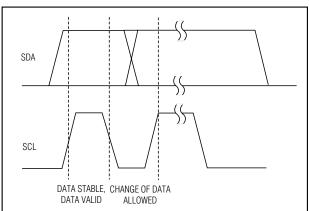

#### **Bit Transfer**

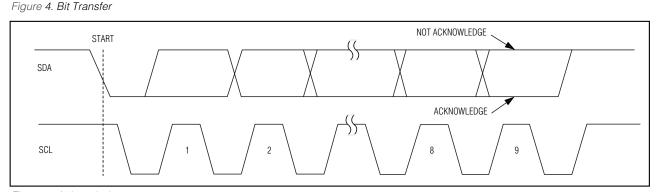

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable while SCL is high (Figure 4).

### Acknowledge

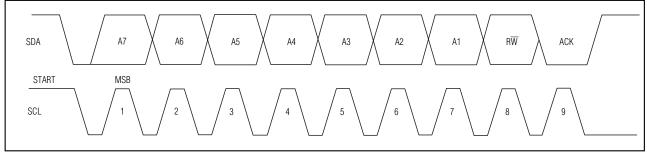

The acknowledge bit is a clocked 9th bit that the recipient uses to handshake receipt each byte of data (Figure 5). Therefore, each byte effectively transferred requires 9 bits. The master controller generates the 9th

Cianna 4 Dit Transfer

clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, so the SDA line remains stable low during the high period of the clock pulse.

#### **Slave Address**

The MAX16805/MAX16806 have a 7-bit-long slave address (Figure 6, Table 1). The 8th bit following the 7-bit slave address is the R/W bit. Set the R/W bit low for a write command and high for a read command.

**Table 1. Slave Address**

| WRITE ADDRESS (HEX) | READ ADDRESS (HEX) |

|---------------------|--------------------|

| 0xEE                | 0xEF               |

Figure 5. Acknowledge

Figure 6. Slave Address

#### **Message Format**

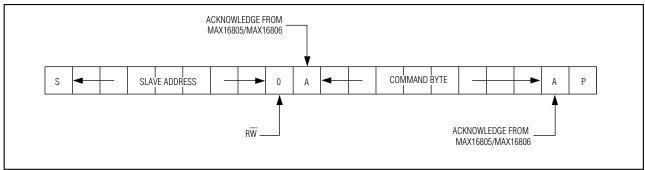

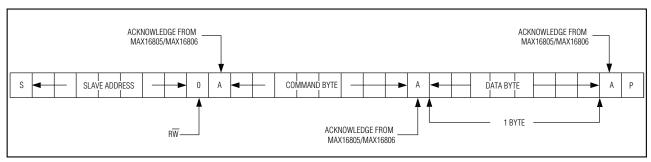

Write to the MAX16805/MAX16806 by transmitting the device's slave address with R/W, 8th bit set to zero followed by at least 1 byte of information (Figure 7). The first byte of information is the command byte. The bytes received after the command byte are the data bytes. The first data byte goes into the internal register as selected by the command byte (Figure 8). If there is more than one data byte, the MAX16805/MAX16806 auto-increment to the next register address locations to write the subsequent data bytes. The MAX16805/MAX16806 auto-increment up to the register address 0x05, EEPROM Content Transfer register.

#### A read operation is performed as follows:

After the START condition (S), a 7-bit slave ID is sent followed by an 8th bit (R/W) set to zero. A register address is then sent to specify the address location from which the read has to take place. To complete a read operation, the master needs to generate a repeated START (Sr) followed by the 7-bit slave ID but with the 8th bit (R/W) set to "1" this time indicating a read operation. On the other hand, a read operation can be performed by sending in the 7-bit slave ID followed by

**Table 2. Registers Address**

| REGISTER NAME                               | REGISTER<br>ADDRESS | NO. OF BITS |

|---------------------------------------------|---------------------|-------------|

| Binning Adjustment                          | 0x00                | 4           |

| Ramp Peak                                   | 0x01                | 3           |

| LED Current Foldback<br>Threshold (LED_CFT) | 0x02                | 4           |

| Thermal Foldback Knee Point                 | 0x03                | 4           |

| Thermal Foldback Slope<br>Gain              | 0x04                | 2           |

| Thermal Foldback Clamp<br>Level             | 0x05                | 3           |

| EEPROM Content Transfer                     | 0x06                | _           |

| EEPROM Program Enable                       | 0x08                | _           |

| Password Register                           | 0xFF                | _           |

|                                             |                     | •           |

an 8th bit  $(R\overline{W})$  set to "1" if the current address location happens to be the address location from which data needs to be read.

Figure 7. Command Byte Received

Figure 8. Command and a Single Data Byte Received

#### **Binning Adjustment Register (0x00)**

The Binning Adjustment register is a 4-bit register that sets the differential regulation voltage reference between CS+ and CS-. Only the first 4 bits of the data byte update the Binning Adjustment register. The remaining 4 bits are ignored. See Table 3. The factory-default register value is 198mV.

### Ramp Peak Register (0x01), MAX16806

The Ramp Peak register is a 3-bit register that sets the maximum peak value of an internally 200Hz generated ramp. The ramp signal can be programmed for a peak value of 1.55V to 2.88V. Only the first 3 bits of the data byte update the Ramp Peak register. The remaining 5 bits are ignored (see Table 4). The factory-default register value is 2.88V.

**Table 3. Binning Adjustment**

| REGULATION<br>VOLTAGE (mV) | BIT 3 | BIT 2 | BIT 1 | BIT 0 | HEX    |

|----------------------------|-------|-------|-------|-------|--------|

| 103.0                      | 0     | 0     | 0     | 0     | (0x00) |

| 109.0                      | 0     | 0     | 0     | 1     | (0x01) |

| 115.4                      | 0     | 0     | 1     | 0     | (0x02) |

| 121.8                      | 0     | 0     | 1     | 1     | (0x03) |

| 128.2                      | 0     | 1     | 0     | 0     | (0x04) |

| 134.6                      | 0     | 1     | 0     | 1     | (0x05) |

| 141.0                      | 0     | 1     | 1     | 0     | (0x06) |

| 147.4                      | 0     | 1     | 1     | 1     | (0x07) |

| 153.7                      | 1     | 0     | 0     | 0     | (80x0) |

| 160.1                      | 1     | 0     | 0     | 1     | (0x09) |

| 166.5                      | 1     | 0     | 1     | 0     | (0x0A) |

| 173.0                      | 1     | 0     | 1     | 1     | (0x0B) |

| 179.3                      | 1     | 1     | 0     | 0     | (0x0C) |

| 185.7                      | 1     | 1     | 0     | 1     | (0x0D) |

| 192.1                      | 1     | 1     | 1     | 0     | (0x0E) |

| 198.0                      | 1     | 1     | 1     | 1     | (0x0F) |

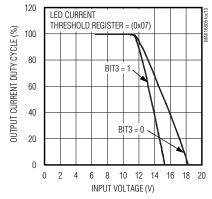

## LED Current Foldback Threshold (LED\_CFT) Register (0x02)

LED\_CFT is a 4-bit register that sets the threshold for the onset of the LED current foldback operation. Only the first 3 bits of the data byte program the LED\_CFT register. Bit 3, not shown in Table 5, sets the LED current foldback range.

The MAX16805/MAX16806 start dimming the LED current when the input voltage exceeds the LED current foldback threshold. For bit 3 = 0, the dimming range is 1.2 times the programmed ramp peak voltage. For bit 3 = 1, the dimming range is 2.4 times the programmed ramp peak. To disable the LED current foldback feature of the MAX16805/MAX16806 connect CFT to GND. The factory-default register value is 16V.

**Table 4. Ramp Peak Value**

| RAMP END<br>POINT (V) | BIT 2 | BIT 1 | BIT 0 | HEX    |

|-----------------------|-------|-------|-------|--------|

| 1.55                  | 0     | 0     | 0     | (0x00) |

| 1.74                  | 0     | 0     | 1     | (0x01) |

| 1.93                  | 0     | 1     | 0     | (0x02) |

| 2.12                  | 0     | 1     | 1     | (0x03) |

| 2.32                  | 1     | 0     | 0     | (0x04) |

| 2.51                  | 1     | 0     | 1     | (0x05) |

| 2.70                  | 1     | 1     | 0     | (0x06) |

| 2.88                  | 1     | 1     | 1     | (0x07) |

**Table 5. LED Current Foldback Threshold**

| CURRENT<br>FOLDBACK<br>THRESHOLD (V) | BIT 2 | BIT 1 | BIT 0 | HEX    |

|--------------------------------------|-------|-------|-------|--------|

| 16.4                                 | 0     | 0     | 0     | (0x00) |

| 15.7                                 | 0     | 0     | 1     | (0x01) |

| 15.0                                 | 0     | 1     | 0     | (0x02) |

| 14.3                                 | 0     | 1     | 1     | (0x03) |

| 13.5                                 | 1     | 0     | 0     | (0x04) |

| 12.8                                 | 1     | 0     | 1     | (0x05) |

| 12.1                                 | 1     | 1     | 0     | (0x06) |

| 11.4                                 | 1     | 1     | 1     | (0x07) |

### Thermal Foldback Knee Point (TFK) Register (0x03), MAX16806

The TFK register is a 4-bit register that sets the thermal knee. Only the first 4 bits of the data byte program the TFK register. The remaining 4 bits are ignored (see Table 6). The MAX16806 initiates dimming once the differential voltage between TFP/SCL and TFN/SDA drops below the programmed thermal foldback knee. The factory-default register value is 1.174V, which corresponds to the MAX6613 thermal sensor output to +60°C.

## Thermal Foldback Slope Gain Register (0x04), MAX16806

Thermal Foldback Slope Gain register is a 2-bit register that sets the gain after the thermal foldback knee. Only the first 2 bits of the data byte program the Thermal Foldback Slope Gain register. The remaining 6 bits are ignored (see Table 7). The factory-default register value is 4V/V.

**Table 6. Thermal Foldback Knee**

| THERMAL FOLDBACK<br>KNEE POINT (°C)<br>(MAX6613) | THERMAL FOLDBACK<br>KNEE POINT (mV) | BIT 3 | BIT 2 | BIT 1 | BIT 0 | HEX    |

|--------------------------------------------------|-------------------------------------|-------|-------|-------|-------|--------|

| 60                                               | 1174                                | 0     | 0     | 0     | 0     | (0x00) |

| 65                                               | 1118                                | 0     | 0     | 0     | 1     | (0x01) |

| 70                                               | 1062                                | 0     | 0     | 1     | 0     | (0x02) |

| 75                                               | 1006                                | 0     | 0     | 1     | 1     | (0x03) |

| 80                                               | 950                                 | 0     | 1     | 0     | 0     | (0x04) |

| 85                                               | 894                                 | 0     | 1     | 0     | 1     | (0x05) |

| 90                                               | 838                                 | 0     | 1     | 1     | 0     | (0x06) |

| 96                                               | 782                                 | 0     | 1     | 1     | 1     | (0x07) |

| 101                                              | 726                                 | 1     | 0     | 0     | 0     | (80x0) |

| 106                                              | 670                                 | 1     | 0     | 0     | 1     | (0x09) |

| 111                                              | 615                                 | 1     | 0     | 1     | 0     | (0x0A) |

| 116                                              | 559                                 | 1     | 0     | 1     | 1     | (0x0B) |

| 121                                              | 503                                 | 1     | 1     | 0     | 0     | (0x0C) |

| 126                                              | 447                                 | 1     | 1     | 0     | 1     | (0x0D) |

| 131                                              | 391                                 | 1     | 1     | 1     | 0     | (0x0E) |

| 136                                              | 335                                 | 1     | 1     | 1     | 1     | (0x0F) |

**Table 7. Thermal Foldback Slope Gain**

| THERMAL FOLDBACK<br>SLOPE GAIN (V/V) | BIT 1 | BIT 0 | HEX    |

|--------------------------------------|-------|-------|--------|

| 16                                   | 0     | 0     | (0x00) |

| 12                                   | 0     | 1     | (0x01) |

| 8                                    | 1     | 0     | (0x02) |

| 4                                    | 1     | 1     | (0x03) |

## Thermal Foldback Clamp Level Register (0x05), MAX16806

Thermal Foldback Clamp Level is a 3-bit register that sets the minimum percentage of the LED current. Only the first 3 bits of the data byte program the Thermal Foldback Clamp Level register. The remaining 5 bits are ignored. See Table 8. The factory-default register value is 40%.

### **EEPROM Content Transfer Register (0x06)**

The MAX16805/MAX16806 use the EEPROM Content Transfer register to transfer data from the EEPROM to the dynamic registers. A write command issued to this register transfers data from the EEPROM to the dynamic registers. Data bytes written to the EEPROM Content Transfer register do not have any significance. At power-up, the EEPROM content is automatically loaded into the dynamic registers.

### **EEPROM Program Enable Register (0x08)**

The EEPROM Program Enable register enables the EEPROM for programming. Write to the EEPROM Programming Enable register to initiate the EEPROM programming cycle. Data written to the register does not have any significance, however, it must be issued following a write command [(0xFF), (0xCA)] to the Password register.

Table 8. Thermal Foldback Clamp Level

| THERMAL FOLDBACK<br>CLAMP LEVEL (%) | BIT 2 | BIT 1 | BIT 0 | HEX    |

|-------------------------------------|-------|-------|-------|--------|

| 100                                 | 0     | 0     | 0     | (0x00) |

| 91                                  | 0     | 0     | 1     | (0x01) |

| 83                                  | 0     | 1     | 0     | (0x02) |

| 74                                  | 0     | 1     | 1     | (0x03) |

| 66                                  | 1     | 0     | 0     | (0x04) |

| 57                                  | 1     | 0     | 1     | (0x05) |

| 49                                  | 1     | 1     | 0     | (0x06) |

| 40                                  | 1     | 1     | 1     | (0x07) |

### **Applications Information**

### Programming the LED Current

The MAX16805/MAX16806 use a sense resistor across CS+ and CS- to set the LED current. The differential sense amplifier connected across RSENSE provides ground-loop immunity and low-frequency noise rejection. The LED current is given by the equation below:

ILED = VSENSE / RSENSE

VSENSE is programmable from 103mV to 198mV using  $I^2C$ .

#### Programming EEPROM

Set V<sub>IN</sub> to 22V before initiating the EEPROM programming. The MAX16805/MAX16806 use dynamic registers to program the EEPROM. Once the desired dynamic registers have been updated with a setting, write the data byte (0xCA) to the Password register (0xFF). The data byte (0xCA) enables the EEPROM programming mode. Any other data byte except the (0xCA) disables the EEPROM programming mode. To transfer data from dynamic registers to the EEPROM, write to EEPROM Program Enable register (0x08).

#### Input Voltage Considerations

For proper operation, the minimum input voltage must always be:

$\label{eq:VIN(MIN)} V_{SENSE} + V_{FT(MAX)} + \Delta V_{DO(MAX)}$  where V\_{FT(MAX)} is the total forward voltage of all series connected LEDs and  $\Delta V_{DO(MAX)}$  is the maximum drop output voltage.

### **Pin Configurations**

**Chip Information**

PROCESS: BICMOS-DMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |                 |       |      |         |        |         |           |           |           |           |           |      |           |      |      |

|-------------------|-----------------|-------|------|---------|--------|---------|-----------|-----------|-----------|-----------|-----------|------|-----------|------|------|

| PKG.              | 16L 5x5 20L 5x5 |       | _ a  | 28L 5×5 |        | 32L 5×5 |           |           | 40L 5x5   |           |           |      |           |      |      |

| SYMBOL            | MIN.            | NDM.  | MAX. | MIN.    | NOM.   | MAX.    | MIN.      | NOM.      | MAX.      | MIN.      | NDM.      | MAX. | MIN.      | NDM. | MAX. |

| Α                 | 0.70            | 0.75  | 0.80 | 0.70    | 0.75   | 0.80    | 0.70      | 0.75      | 0.80      | 0.70      | 0.75      | 0.80 | 0.70      | 0.75 | 0.80 |

| A1                | 0               | 9.02  | 0.05 | 0       | 0.02   | 0.05    | 0         | 0.02      | 0.05      | 0         | 0.02      | 0.05 | 0         | 0.02 | 0.05 |

| A2                | 0.2             | 20 RE | F.   | 0.8     | 20 RE  | F.      | 0.2       | 0.20 REF. |           | 0.20 REF. |           |      | 0.20 REF. |      |      |

| b                 | 0.25            | 0.30  | 0.35 | 0.25    | 0.30   | 0.35    | 0.20      | 0.25      | 0.30      | 0.20      | 0.25      | 0.30 | 0.15      | 0.20 | 0.25 |

| D                 | 4.90            | 5.00  | 5.10 | 4.90    | 5.00   | 5.10    | 4.90      | 5.00      | 5.10      | 4.90      | 5.00      | 5.10 | 4.90      | 5.00 | 5.10 |

| E                 | 4.90            | 5.00  | 5.10 | 4.90    | 5.00   | 5.10    | 4.90      | 5.00      | 5.10      | 4.90      | 5,00      | 5.10 | 4.90      | 5,00 | 5.10 |

| e                 | 0.              | 80 B  | SC.  | 0.      | 65 B   | SC.     | 0.50 BSC. |           | 0.50 BSC. |           | 0.40 BSC. |      |           |      |      |

| k                 | 0.25            | -     | -    | 0.25    | -      | _       | 0.25      | -         | -         | 0.25      | -         | -    | 0.25      | -    | -    |

| L                 | 0.30            | 0.40  | 0.50 | 0.45    | 0.55   | 0.65    | 0.45      | 0.55      | 0.65      | 0.30      | 0.40      | 0.50 | 0.30      | 0.40 | 0.50 |

| N                 |                 | 16    |      |         | 20     |         | 28        |           |           | 32        |           | 40   |           |      |      |

| ND                |                 | 4     |      | 5       |        | 7       |           | 8         |           | 10        |           |      |           |      |      |

| ΝE                |                 | 4     |      |         | 5      |         | 7         |           | 8         |           |           | 10   |           |      |      |

| JEDEC             | 1               | WHHB  | WHIC |         | WHHD-1 |         | VHHD-2    |           |           |           |           |      |           |      |      |

| ΝП | TEC.  |

|----|-------|

| ИΠ | IE SI |

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR T2855-3, T2855-6, T4055-1 AND T4055-2.

- VARPAGE SHALL NOT EXCEED 0.10 mm.

- MARKING IS FOR PACKAGE DRIENTATION REFERENCE ONLY.

- NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 12. NUMBER OF LEADS SHOWN ARE FOR REFERENCE UNLT.

ASS. LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05.

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |

|------------------------|------|------|------|------|------|------|--|--|

| PKG.                   |      | D2   |      |      | E2   |      |  |  |

| CODES                  | MIN. | NDM. | MAX. | MIN. | NDM. | MAX. |  |  |

| T1655-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-5                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2055M-5               | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-3                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-4                | 2.60 | 2.70 | 2.80 | 2.60 | 2,70 | 2.80 |  |  |

| T2855-5                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2955-6                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-7                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-8                | 3.15 | 3.25 | 3.35 | 3.15 | 3,25 | 3.35 |  |  |

| T2855N-1               | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T3255-3                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-4                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255M-4               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-5                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255N-1               | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T4055-1                | 3.40 | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

| T4055-2                | 3,40 | 3,50 | 3,60 | 3,40 | 3.50 | 3.60 |  |  |

21-0140

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.