# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

19-0814; Rev 0; 5/07

EVALUATION KIT AVAILABLE

AMD Mobile Serial VID Dual-Phase Fixed-Frequency Controller

## **General Description**

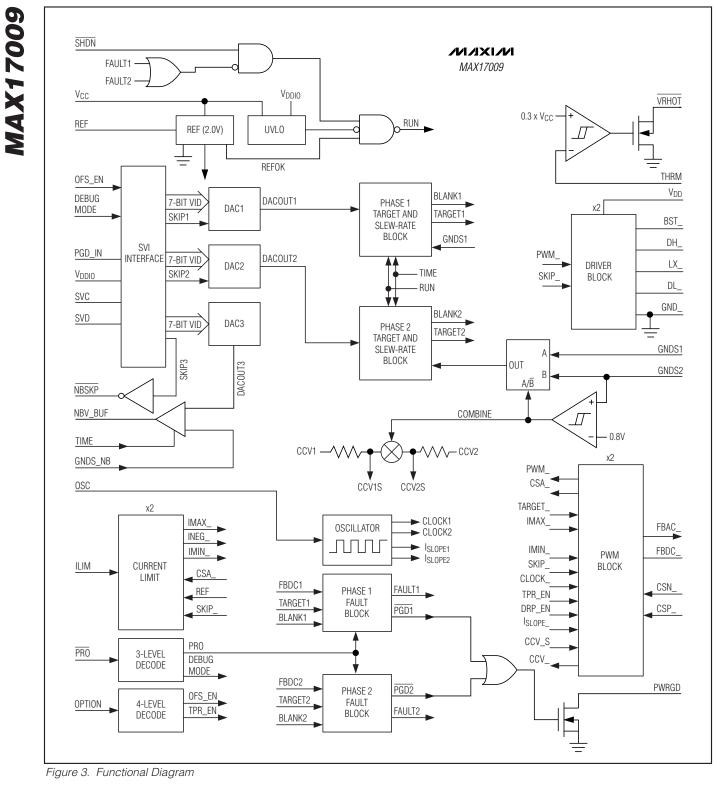

The MAX17009 is a 2-phase, step-down interleaved, fixed-frequency controller for AMD's<sup>®</sup> serial VID interface (SVI) CPU core supplies. Power-on detection of the CPU configures the MAX17009 as two independent single-phase regulators for a dual CPU core application, or one high-current, dual-phase, combined-output regulator for a unified core application. A reference buffer output (NBV\_BUF) sets the voltage-regulation level for a North Bridge (NB) regulator, completing the total CPU cores and NB power requirements.

The MAX17009 is fully AMD SVI compliant. Output voltages are dynamically changed through a 2-wire serial interface, allowing the switching regulator and the reference buffer to be individually programmed to different voltages. A programmable slew-rate controller enables controlled transitions between VID codes, soft-start limits the inrush current, and soft-shutdown brings the output voltage back down to zero without any negative ring.

Transient phase repeat improves the response of the fixed-frequency architecture. Independently programmable AC and DC droop and selectable offset improve stability and reduce the total output-capacitance requirement. A thermistor-based temperature sensor allows for a programmable thermal-fault output (VRHOT). The MAX17009 includes thermal-fault protection, undervoltage protection (UVP), and selectable output overvoltage protection (OVP). When any of these protection features detect a fault, the controller shuts down. True differential current sensing improves current limit, load-line accuracy, and current balance when operating in combined mode. The MAX17009 has an adjustable switching frequency, allowing 100kHz to 1.2MHz per-phase operation.

## **Applications**

Mobile AMD SVI Core Supply Multiphase CPU Core Supply Voltage-Positioned, Step-Down Converters Notebook/Desktop Computers

## \_Features

Dual-Output, Fixed-Frequency, Core Supply Controller

- Separate or Combinable Outputs Detected at Power-Up

- ♦ Reference Buffer Output for NB Controller

- ♦ ±0.4% V<sub>OUT</sub> Accuracy Over Line, Load, and Temperature

- ♦ AMD SVI-Compliant Serial Interface

- ♦ 7-Bit On-Board DAC: 0 to +1.550V Output Adjust Range

- Dynamic Phase Selection Optimizes Active/Sleep Efficiency

- Transient Phase Repeat Reduces Output Capacitance

- True Out-of-Phase Operation Reduces Input Capacitance

- Integrated Boost Switches

- Programmable AC and DC Droop

- Programmable 100kHz to 1.2MHz Switching Frequency

- Accurate Current Balance and Current Limit

- Adjustable Slew-Rate Control

- Power-Good (PWRGD) and Thermal-Fault (VRHOT) Outputs

- System Power-OK (PGD\_IN) Input

- Drives Large Synchronous-Rectifier MOSFETs

- ♦ 4V to 26V Battery Input-Voltage Range

- Overvoltage, Undervoltage, and Thermal-Fault Protection

- Power Sequencing and Timing

- Soft-Startup and Soft-Shutdown

- ♦ < 1µA Typical Shutdown Current</p>

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-<br>PACKAGE           | PKG<br>CODE |

|--------------|-----------------|---------------------------|-------------|

| MAX17009GTL+ | -40°C to +105°C | 40 TQFN-EP*,<br>5mm x 5mm | T4055-1     |

+Denotes a lead-free package.

\*EP = Exposed pad.

Pin Configuration appears at end of data sheet.

AMD is a registered trademark of Advanced Micro Devices, Inc.

## M \X | M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| VDD1, VDD2, VCC, VDDIO to GND |                                  |

|-------------------------------|----------------------------------|

| PWRGD to GND                  | 0.3V to +6V                      |

| FBDC_, FBAC_, PRO to GND      | 0.3V to (V <sub>CC</sub> + 0.3V) |

| GNDS2, THRM, VRHOT to GND     | 0.3V to +6V                      |

| CSP_, CSN_, ILIM to GND       | 0.3V to +6V                      |

| SVC, SVD, PGD_IN to GND       | 0.3V to +6V                      |

| NBV_BUF, NBSKP to GND         |                                  |

| REF, OSC, TIME, OPTION to GND | 0.3V to (V <sub>CC</sub> + 0.3V) |

| BST1, BST2 to GND             |                                  |

| BST1 to V <sub>DD1</sub>      | 0.3V to +30V                     |

| BST2 to V <sub>DD2</sub>      | 0.3V to +30V                     |

| LX1 to BST1                   | 6V to +0.3V                      |

| LX2 to BST2                   | 6V to +0.3V                      |

| DH1 to LX10.3V to (V <sub>BST1</sub> + 0.3V)<br>DH2 to LX20.3V to (V <sub>BST2</sub> + 0.3V)<br>DL1 to GND0.3V to (V <sub>DD1</sub> + 0.3V)<br>DL2 to GND0.3V to (V <sub>DD2</sub> + 0.3V) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDS1, GNDS_NB to GND0.3V to +0.3V<br>Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                                                                |

| Multilayer PCB (derate 35.7mW/°C above +70°C)2857mW<br>Single-Layer PCB (derate 22.2mW/°C above +70°C)1778mW                                                                               |

| Operating Temperature Range40°C to +105°C<br>Junction Temperature+150°C                                                                                                                    |

| Storage Temperature Range65°C to +150°C<br>Lead Temperature (soldering, 10s)+300°C                                                                                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

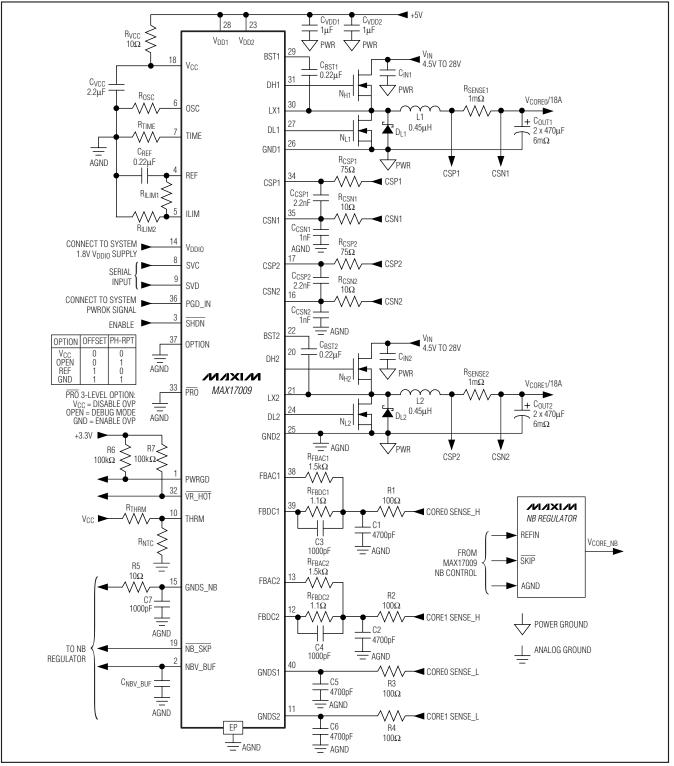

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ , FBDC\_ = FBAC\_ = CSP\_ = CSN\_ = 1.2V, all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                          | SYMBOL                              | MBOL CONDITIONS                                                                                                               |       | ТҮР   | MAX   | UNITS |

|--------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| INPUT SUPPLIES                                                     |                                     |                                                                                                                               |       |       |       |       |

|                                                                    | V <sub>IN</sub>                     | Drain of external high-side MOSFET                                                                                            | 4     |       | 26    |       |

| Input Voltage Range                                                | VBIAS                               | V <sub>CC</sub> , V <sub>DD1</sub> , V <sub>DD2</sub>                                                                         | 4.5   |       | 5.5   | V     |

|                                                                    | V <sub>DDIO</sub>                   |                                                                                                                               | 1.0   |       | 2.7   |       |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold                  | Vuvlo                               | V <sub>CC</sub> rising 50mV typical hysteresis                                                                                | 4.10  | 4.25  | 4.45  | V     |

| V <sub>CC</sub> Power-On Reset<br>Threshold                        | V <sub>CC</sub>                     | Falling edge, typical hysteresis = 1.1V,<br>faults cleared and DL_ forced high when<br>V <sub>CC</sub> falls below this level |       | 1.8   |       | V     |

| V <sub>DDIO</sub> Undervoltage-Lockout<br>Threshold                |                                     | VDDIO rising 100mV typical hysteresis                                                                                         | 0.7   | 0.8   | 0.9   | V     |

| Quiescent Supply Current (V <sub>CC</sub> )                        | Icc                                 | Skip mode, FBDC_ forced above their regulation points                                                                         |       | 5     | 10    | mA    |

| Quiescent Supply Currents<br>(VDD1, VDD2)                          | I <sub>DD1</sub> , I <sub>DD2</sub> | Skip mode, FBDC_ forced above their regulation points                                                                         |       | 0.01  | 1     | μA    |

| Quiescent Supply Current (VDDIO)                                   | IDDIO                               |                                                                                                                               |       | 10    | 25    | μΑ    |

| Shutdown Supply Current (V <sub>CC</sub> )                         |                                     | <u>SHDN</u> = GND                                                                                                             |       | 0.01  | 1     | μA    |

| Shutdown Supply Currents<br>(V <sub>DD1</sub> , V <sub>DD2</sub> ) |                                     | SHDN = GND                                                                                                                    |       | 0.01  | 1     | μA    |

| Shutdown Supply Current (VDDIO)                                    |                                     | SHDN = GND                                                                                                                    |       | 0.01  | 1     | μA    |

| Reference Voltage                                                  | V <sub>REF</sub>                    | $V_{CC}$ = 4.5V to 5.5V, no REF load                                                                                          | 1.986 | 2.000 | 2.014 | V     |

| Potoropoo Lood Pogulation                                          |                                     | Sourcing: $I_{REF} = 0$ to 500µA                                                                                              | -2    | -0.2  |       | mV    |

| Reference Load Regulation                                          |                                     | Sinking: $I_{REF} = 0$ to -100µA                                                                                              |       | 0.21  | 6.2   | IIIV  |

| REF Fault Lockout Voltage                                          |                                     | Typical hysteresis = 85mV                                                                                                     |       | 1.84  |       | V     |

MIXIM

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ , FBDC\_ = FBAC\_ = CSP\_ = CSN\_ = 1.2V, all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                            | SYMBOL             | CONDITIONS                                                                                                                                                                    |                                                                                                   | MIN  | ТҮР        | MAX                     | UNITS   |

|--------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|------------|-------------------------|---------|

| MAIN SMPS CONTROLLERS                |                    |                                                                                                                                                                               |                                                                                                   |      |            |                         |         |

|                                      |                    | DAC code                                                                                                                                                                      | es from 0.8375V to 1.5500V                                                                        | -0.4 |            | +0.4                    | %       |

| DC Output-Voltage Accuracy (Note 1)  | Vout               | DAC code                                                                                                                                                                      | DAC codes from 0.5000V to 0.8250V                                                                 |      |            | +4                      |         |

|                                      |                    | DAC code                                                                                                                                                                      | es below 0.4875V                                                                                  | -10  |            | +10                     | mV      |

| DC Load Regulation                   |                    | Either SMI<br>zero to ful                                                                                                                                                     | PS, PWM mode, droop disabled,<br>I load                                                           |      | -0.1       |                         | %       |

| Line-Regulation Error                |                    | Either SM                                                                                                                                                                     | PS, 4V < V <sub>IN</sub> < 26V                                                                    |      | 0.03       |                         | %/V     |

| GNDS_ Input Range                    | VGNDS_             | Separate                                                                                                                                                                      | mode                                                                                              | -200 |            | +200                    | mV      |

| GNDS_ Gain                           | Agnds_             | Separate: $\Delta V_{OUT}/\Delta V_{GNDS}$ ,<br>-200mV $\leq V_{GNDS} \leq +200$ mV;<br>combined: $\Delta V_{OUT}/\Delta V_{GNDS1}$ ,<br>-200mV $\leq V_{GNDS1} \leq +200$ mV |                                                                                                   | 0.95 | 1.00       | 1.05                    | V/V     |

| GNDS_ Input Bias Current             | IGNDS_             |                                                                                                                                                                               |                                                                                                   | -2   |            | +2                      | μA      |

| Combined-Mode Detection<br>Threshold |                    |                                                                                                                                                                               | etection after REFOK, latched,<br>y cycling SHDN                                                  | 0.7  | 0.8        | 0.9                     | V       |

| FBDC_ Input Bias Current             | IFBDC0_            | CSP_ = C                                                                                                                                                                      | SN_                                                                                               | -3   |            | +3                      | μA      |

|                                      |                    | Rosc = 14                                                                                                                                                                     | $43k\Omega$ (f <sub>OSC</sub> = 300kHz nominal)                                                   | -5   |            | +5                      |         |

| Switching-Frequency Accuracy         | fosc               |                                                                                                                                                                               | 5.7k $\Omega$ (f <sub>OSC</sub> = 1.2MHz nominal) to<br><sub>SC</sub> = 99kHz nominal)            | -7.5 |            | +7.5                    | %       |

| Maximum Duty Factor                  | DMAX               |                                                                                                                                                                               |                                                                                                   | 90   | 92         |                         | %       |

| Minimum On-Time                      | tonmin             |                                                                                                                                                                               |                                                                                                   |      |            | 175                     | ns      |

| SMPS1-to-SMPS2 Phase Shift           |                    | CMDC0 at                                                                                                                                                                      | orto oftor CMDC1                                                                                  |      | 50         |                         | %       |

| SMPST-10-SMPSZ Phase Shill           |                    | SIVIP52 Sta                                                                                                                                                                   | arts after SMPS1                                                                                  |      | 180        |                         | Degrees |

|                                      |                    |                                                                                                                                                                               | $R_{TIME} = 143 k\Omega$ , $SR = 6.25 mV/\mu s$                                                   | -10  |            | +10                     |         |

| TIME Slew-Rate Accuracy              |                    | During<br>transition                                                                                                                                                          | $R_{TIME} = 35.7 k\Omega$ to $357 k\Omega$ ,<br>SR = 25mV/µs to 2.5mV/µs                          | -15  |            | +15                     | %       |

|                                      |                    | Startup ar                                                                                                                                                                    | nd shutdown                                                                                       |      | 1          |                         | mV/µS   |

| CURRENT LIMIT                        |                    |                                                                                                                                                                               |                                                                                                   |      |            |                         |         |

| Current-Limit Threshold Tolerance    | V <sub>LIMIT</sub> |                                                                                                                                                                               | <sub>CSN</sub> = 0.05 × (V <sub>REF</sub> - V <sub>ILIM</sub> ),<br><sub>M</sub> ) = 0.2V to 1.0V | -3   |            | +3                      | mV      |

| Zero-Crossing Threshold              | V <sub>ZX</sub>    | V <sub>GND</sub> - V <sub>LX</sub> , SKIP mode                                                                                                                                |                                                                                                   |      | 3          |                         | mV      |

| Idle Mode™ Threshold Tolerance       | VIDLE              | V <sub>CSP</sub> - V <sub>CSN</sub> , SKIP mode, 0.15 x V <sub>LIMIT</sub>                                                                                                    |                                                                                                   | -1.5 |            | +1.5                    | mV      |

| CS_ Input-Leakage Current            |                    | CSP_ and                                                                                                                                                                      |                                                                                                   | -0.2 |            | +0.2                    | μA      |

| CS_ Common-Mode Input Range          |                    | CSP_ and                                                                                                                                                                      | CSN_                                                                                              | 0    |            | 2                       | V       |

| Phase-Disable Threshold              |                    | CSP2                                                                                                                                                                          |                                                                                                   | 3    | Vcc<br>- 1 | V <sub>CC</sub><br>-0.4 | V       |

Idle Mode is a trademark of Maxim Integrated Products, Inc.

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ , FBDC\_ = FBAC\_ = CSP\_ = CSN\_ = 1.2V, all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                               | SYMBOL                | CONDITIONS                                                                            |                                                                                                                                                                                     | MIN  | ТҮР  | МАХ  | UNITS |

|-------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| DROOP AND CURRENT BALAN                                                 | CE                    |                                                                                       |                                                                                                                                                                                     |      |      |      |       |

| DC Droop Amplifier<br>Transconductance                                  | G <sub>m(FBDC_)</sub> | $\Delta I_{FBDC}/(\Delta V_{CS}),$<br>$V_{FBDC} = V_{CSN} = V_{CSP} - V_{CSN} = -$    |                                                                                                                                                                                     | 0.97 | 1.00 | 1.03 | mS    |

| DC Droop and Current-Balance<br>Amplifier Offset                        |                       | IFBDC_/Gm(FBDC_                                                                       | )                                                                                                                                                                                   | -1.5 |      | +1.5 | mV    |

| AC Droop and Current-Balance<br>Amplifier Transconductance              | G <sub>m(FBAC_)</sub> | $\Delta I_{FBAC}/(\Delta V_{CS}),$<br>$V_{FBAC} = V_{CSN} =$<br>$V_{CSP} - V_{CSN} =$ |                                                                                                                                                                                     | 0.97 | 1.00 | 1.03 | mS    |

| AC Droop and Current-Balance<br>Amplifier Offset                        |                       | IFBAC_/Gm(FBAC_)                                                                      | )                                                                                                                                                                                   | -1.5 |      | +1.5 | mV    |

| No-Load Positive Offset with<br>Offset Enabled                          |                       | Offset enabled, O                                                                     | PTION = REF or GND                                                                                                                                                                  |      | 12.5 |      | mV    |

| Transient Detection Threshold                                           |                       | Measured at FBD<br>state FBDC_ regu<br>hysteresis (typ), tr<br>enabled, OPTION        | -32                                                                                                                                                                                 |      | -18  | mV   |       |

| NB BUFFER                                                               |                       |                                                                                       |                                                                                                                                                                                     |      |      |      |       |

|                                                                         |                       | DAC codes from 0.8375V to 1.5500V                                                     |                                                                                                                                                                                     | -0.4 |      | +0.4 | %     |

| NBV_BUF Output Voltage<br>Accuracy                                      | V <sub>NBV_BUF</sub>  | DAC codes from (                                                                      | 0.5000V to 0.8250V                                                                                                                                                                  | -4   |      | +4   | mV    |

| , local acy                                                             |                       | DAC codes below                                                                       | 0.4875V to 0.0125V                                                                                                                                                                  | -10  |      | +10  | 111V  |

| NBV_BUF Short-Circuit Current                                           |                       | DAC code set to                                                                       | $R_{TIME} = 143 k\Omega$ ,<br>$I_{NBV_BUF} = 7.0 \mu A$                                                                                                                             | -10  |      | +10  | %     |

| (Sets Slew Rate Together with External Capacitor C <sub>NBV_BUF</sub> ) |                       | 1.2V, V <sub>NBV_BUF</sub><br>= 0.4V and 2V                                           | $\label{eq:RTIME} \begin{array}{l} R_{TIME} = 35.7 \mathrm{k}\Omega \text{ to } 357 \mathrm{k}\Omega, \\ I_{NBV\_BUF} = 28 \mathrm{\mu}A \text{ to } 2.8 \mathrm{\mu}A \end{array}$ | -15  |      | +15  | /0    |

| GNDS_NB Input Range                                                     | Vgnds_nb              |                                                                                       |                                                                                                                                                                                     | -200 |      | +200 | mV    |

| GNDS_NB Gain                                                            | AGNDS_NB              | $\Delta V_{NBV}BUF/\Delta V_{GN}$<br>-200mV $\leq V_{GNDS}$                           |                                                                                                                                                                                     | 0.95 | 1.00 | 1.05 | V/V   |

| GNDS_NB Input Bias Current                                              | IGNDS_NB              |                                                                                       |                                                                                                                                                                                     | -2   |      | +2   | μΑ    |

| FAULT DETECTION                                                         |                       |                                                                                       |                                                                                                                                                                                     |      |      |      |       |

|                                                                         |                       |                                                                                       | Normal operation                                                                                                                                                                    | 250  | 300  | 350  | mV    |

| Output Overvoltage Trip<br>Threshold                                    | VOVP_                 | Measured at<br>FBDC_,<br>rising edge                                                  | Output not in regulation<br>after a downward VID<br>transition                                                                                                                      | 1.80 | 1.85 | 1.90 | V     |

|                                                                         |                       |                                                                                       | Minimum OVP threshold                                                                                                                                                               |      | 0.8  |      |       |

| Output Overvoltage Fault-<br>Propagation Delay                          | tovp                  | FBDC_ forced 25mV above trip threshold                                                |                                                                                                                                                                                     |      | 10   |      | μs    |

| Output Undervoltage-Protection<br>Trip Threshold                        | VUVP                  | Measured at FBD<br>unloaded output v                                                  |                                                                                                                                                                                     | -450 | -400 | -350 | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ , FBDC\_ = FBAC\_ = CSP\_ = CSN\_ = 1.2V, all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                           | SYMBOL                      | СО                                                                                                     | NDITIONS                                        | MIN  | ТҮР  | МАХ  | UNITS |

|-----------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|------|------|-------|

| Output Undervoltage Fault-<br>Propagation Delay     | tuvp                        | FBDC_ forced 25n                                                                                       | nV below trip threshold                         |      | 10   |      | μs    |

| PWRGD Threshold                                     |                             | Measured at<br>FBDC_ with<br>respect to<br>unloaded output<br>voltage                                  | Lower threshold, falling<br>edge (undervoltage) | -350 | -300 | -250 | V     |

|                                                     |                             | 15mV hysteresis<br>(typ)                                                                               | Upper threshold, rising edge (overvoltage)      | +150 | +200 | +250 |       |

| PWRGD Propagation Delay                             | <sup>t</sup> PWRGD_         | FBDC_ forced 25n trip thresholds                                                                       | nV outside the PWRGD                            |      | 10   |      | μs    |

| PWRGD Output Low Voltage                            |                             | $I_{SINK} = 4mA$                                                                                       |                                                 |      |      | 0.4  | V     |

| PWRGD Leakage Current                               | IPWRGD_                     | High state, PWRGI                                                                                      | D forced to 5.5V                                |      |      | 1    | μA    |

| PWRGD Startup Delay and<br>Transition Blanking Time | <sup>t</sup> BLANK          | Measured from the time when FBDC_<br>reaches the target voltage based on the<br>slew rate set by RTIME |                                                 |      | 20   |      | μs    |

| VRHOT Trip Threshold                                |                             | Measured at THRM, with respect to V <sub>CC</sub> , falling edge, 115mV hysteresis (typ)               |                                                 | 29.5 | 30   | 30.5 | %     |

| VRHOT Delay                                         | t <u>vrhot</u>              | THRM forced 25mV below the VRHOT trip threshold, falling edge                                          |                                                 |      | 10   |      | μs    |

| VRHOT Output Low Voltage                            |                             | I <sub>SINK</sub> = 4mA                                                                                |                                                 |      |      | 0.4  | V     |

| VRHOT Leakage Current                               |                             | High state, VRHOT                                                                                      | forced to 5V                                    |      |      | 1    | μA    |

| THRM Input Leakage                                  |                             |                                                                                                        |                                                 | -100 |      | +100 | nA    |

| Thermal-Shutdown Threshold                          | TSHDN                       | Hysteresis = 15°C                                                                                      |                                                 |      | 160  |      | °C    |

| GATE DRIVERS                                        |                             |                                                                                                        |                                                 |      |      |      |       |

| DH Cata Driver On Pasiatanaa                        | Power                       | BST LX_ forced                                                                                         | High state (pullup)                             |      | 0.9  | 2.0  | Ω     |

| DH_ Gate-Driver On-Resistance                       | RON(DH_)                    | to 5V                                                                                                  | Low state (pulldown)                            |      | 0.7  | 2.0  | 52    |

| DL_ Gate-Driver On-Resistance                       | PONIDU                      | DL_, high state                                                                                        |                                                 |      | 0.7  | 2.0  | Ω     |

| DL_Gale-Driver On-Resistance                        | R <sub>ON(DL_)</sub>        | DL_, low state                                                                                         |                                                 |      | 0.25 | 0.6  | 52    |

| DH_ Gate-Driver Source/Sink<br>Current              | IDH_                        | DH_ forced to 2.5V, BST LX_ forced to 5V                                                               |                                                 |      | 2.2  |      | A     |

| DL_ Gate-Driver Source Current                      | I <sub>DL</sub><br>(SOURCE) | DL_ forced to 2.5V                                                                                     |                                                 |      | 2.7  |      | A     |

| DL_ Gate-Driver Sink Current                        | IDL_(SINK)                  | DL_ forced to 2.5V                                                                                     |                                                 |      | 8    |      | А     |

| Dead Time                                           | t <sub>DH_DL</sub>          | DH_ low to DL_ hig                                                                                     | gh                                              | 15   | 25   | 40   |       |

| Dead Time                                           | tDL_DH                      | DL_ low to DH_ hig                                                                                     | gh                                              | 9    | 20   | 35   | ns    |

| Internal Boost Diode Switch R <sub>ON</sub>         |                             | BST1 to V <sub>DD1</sub> , BST<br>10mA of current                                                      | $\Gamma^2$ to $V_{DD2}$ ; measure with          |      | 10   | 20   | Ω     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ , FBDC\_ = FBAC\_ = CSP\_ = CSN\_ = 1.2V, all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                              | SYMBOL                          | CONDITIONS                                                                                                                                                                             |                                      | MIN                        | ТҮР | МАХ                        | UNITS |

|----------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------|-----|----------------------------|-------|

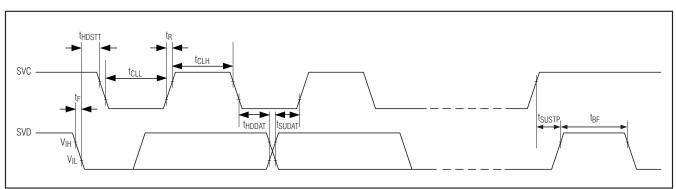

| 2-WIRE SVI BUS LOGIC INTERFA           | CE                              |                                                                                                                                                                                        |                                      | •                          |     |                            |       |

| SVI Logic Input Current                |                                 | SVC, SVD                                                                                                                                                                               |                                      | -1                         |     | +1                         | μA    |

| SVI Logic Input Threshold              |                                 | SVC, SVD, rising<br>hysteresis = 0.1                                                                                                                                                   |                                      | 0.3 x<br>V <sub>DDIO</sub> |     | 0.7 x<br>V <sub>DDIO</sub> | V     |

| SVC Clock Frequency                    | fsvc                            |                                                                                                                                                                                        |                                      |                            |     | 3.4                        | MHz   |

| START Condition Hold Time              | thd,sta                         |                                                                                                                                                                                        |                                      | 160                        |     |                            | ns    |

| Repeated START Condition<br>Setup Time | tsu,sta                         |                                                                                                                                                                                        |                                      | 160                        |     |                            | ns    |

| STOP Condition Setup Time              | tsu,sto                         |                                                                                                                                                                                        |                                      | 160                        |     |                            | ns    |

| Data Hold                              | thd,dat                         | A master device must internally provide a hold time of at least 300ns for the SDA signal (referred to the $V_{IL}$ of SCK signal) to bridge the undefined region of SCL's falling edge |                                      |                            |     | 70                         | ns    |

| Data Setup Time                        | tsu,dat                         |                                                                                                                                                                                        |                                      | 10                         |     |                            | ns    |

| SVC Low Period                         | tLOW                            |                                                                                                                                                                                        |                                      | 160                        |     |                            | ns    |

| SVC High Period                        | thigh                           |                                                                                                                                                                                        |                                      | 60                         |     |                            | ns    |

| SVC/SVD Rise and Fall Time             | t <sub>R</sub> , t <sub>F</sub> | Measured from                                                                                                                                                                          | 10% to 90% of V <sub>DDIO</sub>      |                            |     | 40                         | ns    |

| Pulse Width of Spike Suppression       |                                 | Input filters on S<br>noise spikes les                                                                                                                                                 | SVD and SVC suppress<br>as than 50ns |                            | 20  |                            | ns    |

| INPUTS AND OUTPUTS                     |                                 |                                                                                                                                                                                        |                                      |                            |     |                            |       |

| Logic Input Current                    |                                 | SHDN, PGD_IN                                                                                                                                                                           |                                      | -1                         |     | +1                         | μA    |

| Logic input current                    |                                 | PRO, OPTION                                                                                                                                                                            |                                      | -3                         |     | +3                         | μΑ    |

| Logic Input Threshold                  |                                 | SHDN, rising ec                                                                                                                                                                        | lge, hysteresis = 225mV              | 0.8                        |     | 2.0                        | V     |

|                                        |                                 |                                                                                                                                                                                        | High                                 | V <sub>CC</sub> -<br>0.4   |     |                            |       |

| Four-Level Input-Logic Levels          |                                 | OPTION                                                                                                                                                                                 | Open                                 | 3.15                       |     | 3.85                       | V     |

|                                        |                                 |                                                                                                                                                                                        | REF                                  | 1.65                       |     | 2.35                       |       |

|                                        |                                 |                                                                                                                                                                                        | Low                                  |                            |     | 0.4                        |       |

|                                        |                                 |                                                                                                                                                                                        | High                                 | V <sub>CC</sub> -<br>0.4   |     |                            |       |

| Tri-Level Input-Logic Levels           |                                 | PRO                                                                                                                                                                                    | Open                                 | 3.15                       |     | 3.85                       | V     |

|                                        |                                 |                                                                                                                                                                                        | Low                                  |                            |     | 0.4                        |       |

| PGD_IN Logic Input Threshold           |                                 | PGD_IN                                                                                                                                                                                 |                                      | 0.3 x<br>V <sub>DDIO</sub> |     | 0.7 x<br>V <sub>DDIO</sub> | V     |

|                                        |                                 | Low state, ISINK                                                                                                                                                                       | : = 3mA                              |                            |     | 0.4                        | 1     |

| NBSKP Logic Output Voltage             |                                 | High state, ISOL                                                                                                                                                                       | JRCE = 3mA                           | V <sub>CC</sub> - 0.4      |     |                            | V     |

## **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ ,  $FBDC_ = FBAC_ = CSP_ = CSN_ = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                           | SYMBOL                              | CONDITIONS                                                               |                                                                            | MIN  | MAX  | UNITS |

|-----------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|-------|

| INPUT SUPPLIES                                      |                                     |                                                                          |                                                                            |      |      |       |

|                                                     | VIN                                 | Drain of ex                                                              | ternal high-side MOSFET                                                    | 4    | 26   |       |

| Input Voltage Range                                 | VBIAS                               |                                                                          | V <sub>CC</sub> , V <sub>DD1</sub> , V <sub>DD2</sub>                      |      | 5.5  | V     |

|                                                     | V <sub>DDIO</sub>                   |                                                                          |                                                                            | 1.0  | 2.7  |       |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold   | Vuvlo                               | V <sub>CC</sub> rising                                                   | 50mV typical hysteresis                                                    | 4.10 | 4.45 | V     |

| V <sub>DDIO</sub> Undervoltage-Lockout<br>Threshold |                                     | V <sub>DDIO</sub> risir                                                  | ng 100mV typical hysteresis                                                | 0.8  | 0.9  | V     |

| Quiescent Supply Current (V <sub>CC</sub> )         | Icc                                 | Skip mode<br>regulation                                                  | e, FBDC_ forced above their points                                         |      | 10   | mA    |

| Quiescent Supply Currents<br>(VDD1, VDD2)           | I <sub>DD1</sub> , I <sub>DD2</sub> |                                                                          | e, FBDC_ forced above their points, $T_A = -40^{\circ}C$ to +85°C          |      | 1    | μA    |

| Quiescent Supply Current (V <sub>DDIO</sub> )       | IDDIO                               |                                                                          |                                                                            |      | 25   | μA    |

| Shutdown Supply Current (V <sub>CC</sub> )          |                                     | $\overline{\text{SHDN}} = G$                                             | ND, $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                 |      | 1    | μA    |

| Shutdown Supply Currents<br>(VDD1, VDD2)            |                                     | $\overline{\text{SHDN}} = G$                                             | ND, $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                 |      | 1    | μΑ    |

| Shutdown Supply Current (V <sub>DDIO</sub> )        |                                     | $T_A = -40^{\circ}C$                                                     | C to +85°C                                                                 |      | 1    | μA    |

| Reference Voltage                                   | V <sub>REF</sub>                    | $V_{CC} = 4.5^{\circ}$                                                   | V to 5.5V, no REF load                                                     | 1.98 | 2.02 | V     |

| Reference Load Regulation                           |                                     | Sourcing:                                                                | I <sub>REF</sub> = 0 to 500μA                                              | -2   |      | mV    |

| Reference Load Regulation                           |                                     | Sinking: $I_{REF} = 0$ to $-100\mu A$                                    |                                                                            |      | 6.2  |       |

| MAIN SMPS CONTROLLERS                               |                                     |                                                                          |                                                                            |      |      |       |

| DC Output Voltage Accuracy                          |                                     | DAC code                                                                 | s from 0.8375V to 1.5500V                                                  | -0.6 | +0.6 | %     |

| DC Output-Voltage Accuracy<br>(Note 1)              | Vout                                | DAC codes from 0.5000V to 0.8250V                                        |                                                                            | -6   | +6   | mV    |

| (                                                   |                                     | DAC code                                                                 | s from 0.4875V to 0.0125V                                                  | -15  | +15  |       |

| GNDS_ Input Range                                   | VGNDS_                              | Separate r                                                               |                                                                            | -200 | +200 | mV    |

| GNDS_Gain                                           | A <sub>GNDS</sub> _                 | -200mV ≤<br>Combined                                                     | ΔVOUT_/ΔVGNDS_,<br>VGNDS_ ≤ +200mV,<br>: ΔVOUT/ΔVGNDS1,<br>VGNDS1 ≤ +200mV | 0.95 | 1.05 | V/V   |

| Combined-Mode Detection<br>Threshold                |                                     |                                                                          | etection after REFOK, latched,<br>v cycling SHDN                           | 0.7  | 0.9  | V     |

|                                                     |                                     | $R_{OSC} = 14$                                                           | $43k\Omega$ (fOSC = 300kHz nominal)                                        | -7.5 | +7.5 |       |

| Switching-Frequency Accuracy                        | fosc                                | Rosc = 35.7kΩ (fosc = 1.2MHz nominal) to<br>432kΩ (fosc = 99kHz nominal) |                                                                            | -10  | +10  | %     |

| Maximum Duty Factor                                 | DMAX                                |                                                                          |                                                                            | 90   |      | %     |

| Minimum On-Time                                     | tonmin                              |                                                                          |                                                                            |      | 185  | ns    |

|                                                     |                                     | During                                                                   | $R_{TIME} = 143 k\Omega$ , $SR = 6.25 mV/\mu s$                            | -10  | +10  |       |

| TIME Slew-Rate Accuracy                             |                                     | During<br>transition                                                     | $R_{TIME} = 35.7$ kΩ to $357$ kΩ,<br>SR = 25mV/μs to 2.5mV/μs              | -15  | +15  | %     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ ,  $FBDC_ = FBAC_ = CSP_ = CSN_ = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                      | SYMBOL                 | CONDITIONS                                                                                                                                                         |                                                               | MIN  | MAX                   | UNITS |

|----------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|-----------------------|-------|

| CURRENT LIMIT                                                  |                        | ·                                                                                                                                                                  |                                                               |      |                       |       |

| Current-Limit Threshold Tolerance                              | VLIMIT                 | $V_{CSP}$ - $V_{CSN}$ = $(V_{REF} - V_{ILM}) = 0.$                                                                                                                 | 0.05 x (V <sub>REF</sub> - V <sub>ILIM</sub> ),<br>2V to 1.0V | -3   | +3                    | mV    |

| Idle Mode Threshold Tolerance                                  | VIDLE                  | V <sub>CSP</sub> V <sub>CSN</sub> _, S                                                                                                                             | KIP mode, 0.15 x V <sub>LIMIT</sub>                           | -1.5 | +1.5                  | mV    |

| CS_Common-Mode Input Range                                     |                        | CSP_ and CSN_                                                                                                                                                      |                                                               | 0    | 2                     | V     |

| Phase Disable Threshold                                        |                        | CSP2                                                                                                                                                               |                                                               | 3    | V <sub>CC</sub> - 0.4 | V     |

| DROOP AND CURRENT BALANC                                       | E                      |                                                                                                                                                                    |                                                               | •    |                       |       |

| DC Droop Amplifier<br>Transconductance                         | Gm(FBDC_)              | $\Delta I_{FBDC} / (\Delta V_{CS});$<br>$V_{FBDC} = V_{CSN}$<br>$V_{CSP} - V_{CSN} =$                                                                              | = 1.2V,                                                       | 0.97 | 1.03                  | mS    |

| DC Droop Amplifier Offset                                      |                        | IFBDC_/Gm(FBDC_                                                                                                                                                    | _)                                                            | -1.5 | +1.5                  | mV    |

| AC Droop and Current-Balance<br>Amplifier Transconductance     | G <sub>m(FBAC_</sub> ) | $\Delta I_{FBAC\_}/(\Delta V_{CS\_}),$ $V_{FBAC\_} = V_{CSN\_} = 1.2V,$ $V_{CSP\_} - V_{CSN\_} = -60mV \text{ to } +60mV$                                          |                                                               | 0.97 | 1.03                  | mS    |

| AC Droop and Current-Balance<br>Amplifier Offset               |                        | IFBAC_/Gm(FBAC_                                                                                                                                                    | )                                                             | -1.5 | +1.5                  | mV    |

| Transient-Detection Threshold                                  |                        | Measured at FBDC_ with respect to<br>steady-state<br>FBDC_ regulation voltage,<br>5mV hysteresis (typ),<br>transient phase repeat enabled,<br>OPTION = OPEN or GND |                                                               | -32  | -18                   | mV    |

| NB BUFFER                                                      | •                      |                                                                                                                                                                    |                                                               | •    |                       |       |

|                                                                |                        | DAC codes from                                                                                                                                                     | 0.8375V to 1.5500V                                            | -0.6 | +0.6                  | %     |

| NBV_BUF Output-Voltage<br>Accuracy                             | V <sub>NBV_BUF</sub>   | DAC codes from                                                                                                                                                     | 0.5000V to 0.8250V                                            | -6   | +6                    | mV    |

|                                                                |                        | DAC codes from                                                                                                                                                     | 0.4875V to 0.0125V                                            | -15  | +15                   |       |

| NBV_BUF Short-Circuit Current<br>(Sets Slew Rate Together with |                        | DAC code set to<br>1.2V, V <sub>NBV_BUF</sub>                                                                                                                      | R <sub>TIME</sub> = 143kΩ,<br>I <sub>NBV_BUF</sub> = 7.0μA    | -10  | +10                   | %     |

| External Capacitor C <sub>NBV_BUF</sub> )                      |                        | = 0.4V and 2V                                                                                                                                                      | $R_{TIME} = 35.7$ kΩ to $357$ kΩ,<br>INBV_BUF = 28μA to 2.8μA | -15  | +15                   | 70    |

| GNDS_NB Input Range                                            | VGNDS_NB               |                                                                                                                                                                    |                                                               | -200 | +200                  | mV    |

| GNDS_NB Gain                                                   | Agnds_nb               | $\Delta V_{NBV_BUF}/\Delta V_{GN}$<br>-200mV $\leq V_{GNDS_1}$                                                                                                     |                                                               | 0.95 | 1.05                  | V/V   |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD1} = V_{DD2} = \overline{SHDN} = PGD_IN = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $\overline{PRO} = OPTION = GNDS_NB = GNDS_ = GND_$ , FBDC\_ = FBAC\_ = CSP\_ = CSN\_ = 1.2V, all DAC codes set to the 1.2V code,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                        | SYMBOL                          | CONDITIONS                                                                                                                                                                             |                                                    | MIN                        | MAX            | UNITS |

|--------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------|----------------|-------|

| FAULT DETECTION                                  | •                               |                                                                                                                                                                                        |                                                    |                            |                |       |

| Output Overvoltage Trip<br>Threshold             | Vovp_                           | Measured at FBDC_, rising edge                                                                                                                                                         | Normal operation                                   | 250                        | 350            | mV    |

| Output Undervoltage-Protection<br>Trip Threshold | Vuvp                            | Measured at FBDC_v<br>unloaded output volta                                                                                                                                            |                                                    | -450                       | -350           | mV    |

| PWRGD Threshold                                  |                                 | Measured at FBDC_<br>with respect to<br>unloaded output<br>voltage                                                                                                                     | Lower threshold,<br>falling edge<br>(undervoltage) | -350                       | -250           | V     |

|                                                  |                                 | 15mV hysteresis<br>(typ)                                                                                                                                                               | Upper threshold,<br>rising edge<br>(overvoltage)   | +150                       | +250           |       |

| PWRGD Output Low Voltage                         |                                 | $I_{SINK} = 4mA$                                                                                                                                                                       |                                                    |                            | 0.4            | V     |

| VRHOT Trip Threshold                             |                                 | Measured at THRM, v<br>falling edge, 115mV h                                                                                                                                           |                                                    | 29.5                       | 30.5           | %     |

| VRHOT Output Low Voltage                         |                                 | I <sub>SINK</sub> = 4mA                                                                                                                                                                |                                                    |                            | 0.4            | V     |

| GATE DRIVERS                                     |                                 |                                                                                                                                                                                        |                                                    |                            |                |       |

| DH_ Gate-Driver On-Resistance                    | R <sub>ON(DH_)</sub>            | BST LX_ forced<br>to 5V                                                                                                                                                                | High state (pullup)<br>Low state (pulldown)        |                            | 2.0<br>2.0     | Ω     |

|                                                  | 5                               | DL_, high state                                                                                                                                                                        |                                                    |                            | 2.0            | 0     |

| DL_ Gate-Driver On-Resistance                    | Ron(dl_)                        | DL_, low state                                                                                                                                                                         |                                                    |                            | 0.6            | Ω     |

| Dead Time                                        | tDH_DL                          | DH_ low to DL_ high                                                                                                                                                                    |                                                    | 15                         | 40             |       |

| Dead Time                                        | tDL_DH                          | DL_ low to DH_ high                                                                                                                                                                    |                                                    | 9                          | 40             | ns    |

| Internal Boost Diode Switch RON                  |                                 | BST1 to V <sub>DD1</sub> , BST2 t<br>with 10mA of current                                                                                                                              | to $V_{DD2}$ , measured                            |                            | 20             | Ω     |

| 2-WIRE SVI BUS LOGIC INTERF                      | ACE                             | •                                                                                                                                                                                      |                                                    |                            |                |       |

| SVI Logic Input Threshold                        |                                 | SVC, SVD, rising edge<br>hysteresis = 0.15 x V[                                                                                                                                        |                                                    | 0.3 x<br>V <sub>DDIO</sub> | 0.7 x<br>Vddio | V     |

| SVC Clock Frequency                              | fsvc                            |                                                                                                                                                                                        |                                                    |                            | 3.4            | MHz   |

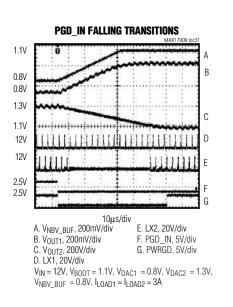

| START Condition Hold Time                        | thd,sta                         |                                                                                                                                                                                        |                                                    | 160                        |                | ns    |