Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **General Description**

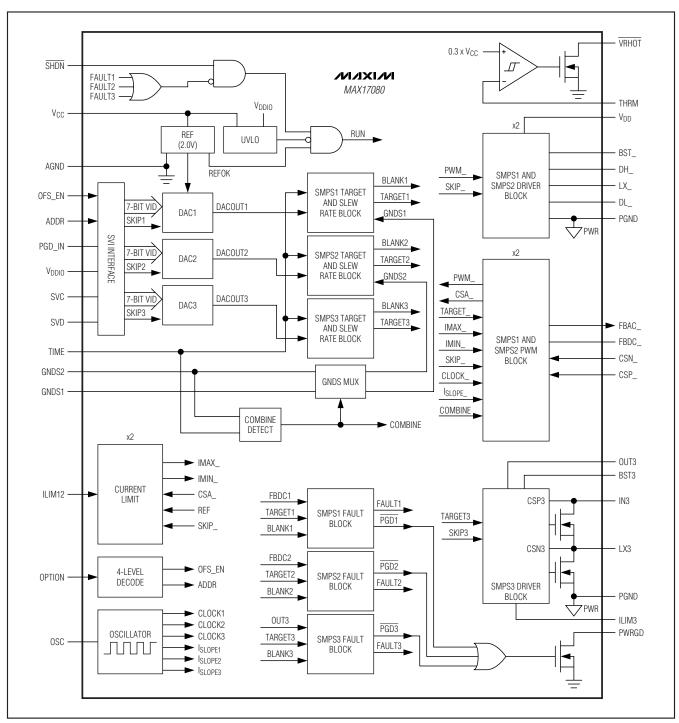

The MAX17080 is a triple-output, step-down, fixedfrequency controller for AMD's serial VID interface (SVI) CPU and northbridge (NB) core supplies. The MAX17080 consists of two high-current SMPSs for the CPU cores and one 3A internal switch SMPS for the NB core. The two CPU core SMPSs run 180° out-of-phase for true interleaved operation, minimizing input capacitance. The 3A internal switch SMPS runs at twice the switching frequency of the core SMPS, reducing the size of the external components.

The MAX17080 is fully AMD SVI compliant. Output voltages are dynamically changed through a 2-wire SVI, allowing the SMPSs to be individually programmed to different voltages. A slew-rate controller allows controlled transitions between VID codes and controlled soft-start. SVI also allows each SMPS to be individually set into a low-power pulse-skipping state.

Transient phase repeat improves the response of the fixed-frequency architecture, reducing the total output capacitance for the CPU core. A thermistor-based temperature sensor provides a programmable thermal-fault output (VRHOT).

The MAX17080 includes output overvoltage protection (OVP), undervoltage protection (UVP), and thermal protection. When any of these protection features detect a fault, the controller shuts down. True differential current sensing improves current limit and load-line accuracy. The MAX17080 has an adjustable switching frequency, allowing 100kHz to 600kHz operation per core SMPS. and twice that for the NB SMPS.

## **Applications**

Mobile AMD SVI Core Supplies Multiphase CPU Core Supplies Voltage-Positioned, Step-Down Converters Notebook/Desktop Computers

**Features**

◆ Dual-Output Fixed-Frequency Core Supply Controller

> Split or Combinable Outputs Detected at Power-Up

**Dynamic Phase Selection Optimizes Active/Sleep Efficiency**

**Transient Phase Repeat Reduces Output** Capacitance

**True Out-of-Phase Operation Reduces Input** Capacitance

Programmable AC and DC Droop

**Accurate Current Balance and Current Limit Integrated Drivers for Large Synchronous-Rectifier MOSFETs**

Programmable 100kHz to 600kHz Switching Frequency

4V to 26V Battery Input Voltage Range

- **♦** 3A Internal Switch Northbridge SMPS 2.7V to 5.5V Input Voltage Range 2x Programmable Switching Frequency 100m $\Omega$ /50m $\Omega$  Power Switches

- ♦ ±0.5% Vout Accuracy over Line, Load, and **Temperature**

- ♦ AMD SVI-Compliant Serial Interface with Switchable Address

- ♦ 7-Bit On-Board DAC: 0 to +1.550V Output Adjust Range

- **♦ Integrated Boost Switches**

- **♦** Adjustable Slew-Rate Control

- ♦ Power-Good (PWRGD) and Thermal-Fault (VRHOT) Outputs

- ♦ System Power-OK (PGD\_IN) Input

- ♦ Overvoltage, Undervoltage, and Thermal-Fault Protection

- ♦ Voltage Soft-Startup and Passive Shutdown

- ♦ < 1µA Typical Shutdown Current

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX17080GTL+ | -40°C to +105°C | 40 TQFN     |

+Denotes a lead(Pb)-free and RoHS-compliant package.

Pin Configuration appears at end of data sheet.

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| V <sub>DD</sub> , V <sub>IN3</sub> , V <sub>CC</sub> , V <sub>DDIO</sub> to AGND0.3V to | o +6V |

|-----------------------------------------------------------------------------------------|-------|

| PWRGD to AGND0.3V to                                                                    | o +6V |

| SHDN to AGND0.3V to                                                                     | o +6V |

| GNDS1, GNDS2, THRM, VRHOT to AGND0.3V to                                                | o +6V |

| CSP_, CSN_, ILIM12 to AGND0.3V to                                                       | o +6V |

| SVC, SVD, PGD_IN to AGND0.3V to                                                         | o +6V |

| FBDC_, FBAC_, OUT3 to AGND0.3V to                                                       | o +6V |

| OSC, TIME, OPTION, ILIM3 to AGND0.3V to (VCC +                                          | 0.3V) |

| BST1, BST2 to AGND0.3V to                                                               | +36V  |

| BST1, BST2 to V <sub>DD</sub> 0.3V to                                                   | +30V  |

| BST3 to AGND(V <sub>DD</sub> - 0.3V) to (V <sub>LX3</sub>                               |       |

| LX1 to BST16V to                                                                        |       |

| LX3 RMS Current (Note 2)                                                                | ±3A   |

| LX2 to BST2LX3 to PGND (Note 2)                |                                    |

|------------------------------------------------|------------------------------------|

| DH1 to LX1                                     | 0.3V to (V <sub>BST1</sub> + 0.3V) |

| DH2 to LX2                                     | 0.3V to (V <sub>BST2</sub> + 0.3V) |

| DL1 to PGND                                    | 0.3V to $(V_{DD} + 0.3V)$          |

| DL2 to PGND                                    | 0.3V to $(V_{DD} + 0.3V)$          |

| Continuous Power Dissipation (T <sub>A</sub> = | +70°C)                             |

| 40-Pin TQFN (derate 22.2mW/°C                  | above +70°C)1778mW                 |

| Operating Temperature Range                    | 40°C to +105°C                     |

| Junction Temperature                           | +150°C                             |

| Storage Temperature Range                      |                                    |

| Lead Temperature (soldering, 10s).             | +300°C                             |

|                                                |                                    |

Note 1: Absolute Maximum Ratings measured with 20MHz scope bandwidth.

Note 2: LX3 has clamp diodes to PGND and IN3. If continuous current is applied through these diodes, thermal limits must be observed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD} = V_{IN3} = V_{\overline{S}H\overline{DN}} = V_{PGD\_IN} = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $V_{OPTION} = V_{GNDS} = V_{AGND} = V_{PGND}$ ,  $V_{PBDC} = V_{PBAC} = V_{OUT3} = V_{CSP} = V_{CSN} = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                           | SYMBOL            | CONDITIONS                                                                                                  | MIN TYP |      | MAX  | UNITS |

|-----------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|---------|------|------|-------|

| INPUT SUPPLIES                                      |                   |                                                                                                             |         |      |      |       |

|                                                     | V <sub>IN</sub>   | Drain of external high-side MOSFET                                                                          | 4       |      | 26   |       |

| Input Voltage Range                                 | V <sub>BIAS</sub> | Vcc, VDD                                                                                                    | 4.5     |      | 5.5  | V     |

| input voltage hange                                 | VIN3              |                                                                                                             | 2.7     |      | 5.5  | \ \ \ |

|                                                     | V <sub>DDIO</sub> |                                                                                                             | 1.0     |      | 2.7  |       |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold   | Vuvlo             | V <sub>CC</sub> rising, 50mV typical hysteresis, latched, UV fault                                          | 4.10    | 4.25 | 4.45 | V     |

| V <sub>CC</sub> Power-On Reset Threshold            |                   | Falling edge, typical hysteresis = 1.1V, faults cleared and DL_ forced high when VCC falls below this level |         | 1.8  |      | V     |

| V <sub>DDIO</sub> Undervoltage-Lockout<br>Threshold |                   | V <sub>DDIO</sub> rising, 100mV typical hysteresis, latched, UV fault                                       | 0.7     | 0.8  | 0.9  | V     |

| V <sub>IN3</sub> Undervoltage-Lockout<br>Threshold  |                   | V <sub>IN3</sub> rising, 100mV typical hysteresis                                                           | 2.5     | 2.6  | 2.7  | V     |

| Quiescent Supply Current (VCC)                      | Icc               | Skip mode, FBDC_ and OUT3 forced above their regulation points                                              |         | 5    | 10   | mA    |

| Quiescent Supply Currents (VDD)                     | I <sub>DD</sub>   | Skip mode, FBDC_ and OUT3 forced above their regulation points, T <sub>A</sub> = +25°C                      |         | 0.01 | 1    | μA    |

| Quiescent Supply Current (V <sub>DDIO</sub> )       | I <sub>DDIO</sub> |                                                                                                             |         | 10   | 25   | μΑ    |

| Quiescent Supply Current (IN3)                      | I <sub>IN3</sub>  | Skip mode, OUT3 forced above its regulation point                                                           |         | 80   | 200  | μΑ    |

| Shutdown Supply Current (VCC)                       |                   | SHDN = GND, TA = +25°C                                                                                      |         | 0.01 | 1    | μΑ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN}$  = 12V,  $V_{CC}$  =  $V_{DD}$  =  $V_{IN3}$  =  $V_{\overline{SHDN}}$  =  $V_{PGD\_IN}$  = 5V,  $V_{DDIO}$  = 1.8V,  $V_{OPTION}$  =  $V_{GNDS\_}$  =  $V_{AGND}$  =  $V_{PGND}$ ,  $V_{PBDC\_}$  =  $V_{PBAC\_}$  =  $V_{CSP\_}$  =  $V_{CSP\_}$  = 1.2V, all DAC codes set to the 1.2V code,  $V_{AB}$  =  $V_{CB}$  =  $V_{CSP\_}$  =  $V_{CSP\_}$  = 1.2V, all DAC codes set to the 1.2V code,  $V_{AB}$  =  $V_{CSP\_}$  =  $V_{CSP\_}$  =  $V_{CSP\_}$  =  $V_{CSP\_}$  = 1.2V, all DAC codes set to the 1.2V code,  $V_{AB}$  =  $V_{CSP\_}$  =  $V_$

| PARAMETER                               | SYMBOL              | COND                                                                                                                                                                               | ITIONS                                                                | MIN  | TYP  | MAX  | UNITS   |

|-----------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|---------|

| Shutdown Supply Currents (VDD)          |                     | SHDN = GND, T <sub>A</sub> = +25°C                                                                                                                                                 |                                                                       |      | 0.01 | 1    | μΑ      |

| Shutdown Supply Current (VDDIO)         |                     | $\overline{SHDN} = GND, T_A = +$                                                                                                                                                   | -25°C                                                                 |      | 0.01 | 1    | μΑ      |

| Shutdown Supply Current (IN3)           |                     | SHDN = GND, TA = +                                                                                                                                                                 | -25°C                                                                 |      | 0.01 | 1    | μΑ      |

| INTERNAL DACs, SLEW RATE, F             | PHASE SHIF          | т                                                                                                                                                                                  |                                                                       |      |      |      | _       |

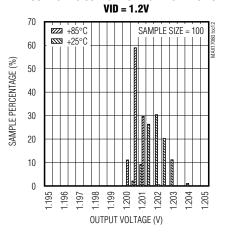

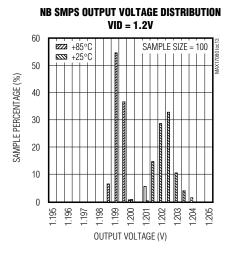

|                                         |                     | Measured at FBDC_<br>for the core SMPSs;<br>measured at OUT3                                                                                                                       | DAC codes from 0.8375V to 1.5500V                                     | -0.5 |      | +0.5 | %       |

| DC Output Voltage Accuracy<br>(Note 1)  | Vout                | for the NB SMPS;<br>30% duty cycle, no                                                                                                                                             | DAC codes from 0.5000V to 0.8250V                                     | -5   |      | +5   | mV      |

|                                         |                     | load, V <sub>ILIM3</sub> = V <sub>CC</sub> ,<br>V <sub>OUT3</sub> = V <sub>DAC3</sub> +<br>12.5mV (Note 3)                                                                         | DAC codes from<br>12.5mV to 0.4875V                                   | -10  |      | +10  | IIIV    |

| OUT3 Offset                             |                     | $V_{ILIM3} = V_{CC}$ or 3.3V                                                                                                                                                       |                                                                       |      | 12.5 |      | mV      |

| OUTS Offset                             |                     | V <sub>ILIM3</sub> = 2V or GND                                                                                                                                                     |                                                                       |      | 6.25 |      | IIIV    |

| SMPS1 to SMPS2 Phase Shift              |                     | SMPS2 starts after SN                                                                                                                                                              | MPS1                                                                  |      | 50   |      | %       |

| OWN O'T TO OWN OZ I HASE ONNE           |                     | OWN 02 Starts arter on                                                                                                                                                             | VII 0 1                                                               |      | 180  |      | Degrees |

| SMPS3 to SMPS1 and SMPS2<br>Phase Shift |                     | SMPS3 starts after SMPS1 or SMPS2                                                                                                                                                  |                                                                       |      | 25   |      | %       |

|                                         |                     | R <sub>TIME</sub> = 1                                                                                                                                                              | $43$ k $\Omega$ , SR = $6.25$ mV/ $\mu$ s                             | -10  |      | +10  |         |

| Slew-Rate Accuracy                      |                     | THANSILION I THE                                                                                                                                                                   | $5.7$ k $\Omega$ to $357$ k $\Omega$ , $V/\mu$ s to $2.5$ m $V/\mu$ s | -15  |      | +15  | %       |

|                                         |                     | Startup                                                                                                                                                                            |                                                                       |      | 1    |      | mV/µs   |

| FBAC_Input Bias Current                 | IFBAC_              | CSP_ = CSN_, TA = -                                                                                                                                                                | +25°C                                                                 | -3   |      | +3   | μΑ      |

| FBDC_ Input Bias Current                | I <sub>FBDC</sub> _ | $T_A = +25^{\circ}C$                                                                                                                                                               |                                                                       | -250 |      | +250 | nA      |

|                                         | fosc1,              | Rosc = 143kΩ (fosc nominal, fosc3 = 600                                                                                                                                            |                                                                       | -5   |      | +5   |         |

| Switching Frequency Accuracy            | fosc2,<br>fosc3     | $\begin{aligned} R_{OSC} &= 71.4 k\Omega \text{ (fosc)} \\ \text{nominal, fosc3} &= 1.2 \\ 432 k\Omega \text{ (fosc1 = fosc)} \\ \text{fosc3} &= 199 \text{kHz nom} \end{aligned}$ | MHz nominal) to<br><sub>2</sub> = 99kHz nominal,                      | -7.5 |      | +7.5 | %       |

| SMPS1 AND SMPS2 CONTROLL                | ERS                 |                                                                                                                                                                                    |                                                                       |      |      |      |         |

| DC Load Regulation                      |                     | Either SMPS, PWM mo                                                                                                                                                                | ode, droop disabled;                                                  |      | -0.1 |      | %       |

| Line Regulation Error                   |                     | Either SMPS, 4V < V <sub>IN</sub> < 26V                                                                                                                                            |                                                                       |      | 0.03 |      | %/V     |

| GNDS_Input Range                        | V <sub>GNDS</sub> _ | Separate mode                                                                                                                                                                      |                                                                       | -200 |      | +200 | mV      |

| GNDS_Gain                               | AGNDS_              | Separate: $\Delta V_{OUT}/\Delta V_{GN}$<br>$\leq +200 \text{mV}$ ; combined:<br>$-200 \text{mV} \leq V_{GNDS} \leq +200 \text{mV}$                                                |                                                                       | 0.95 | 1.00 | 1.05 | V/V     |

| GNDS_Input Bias Current                 | IGNDS_              | T <sub>A</sub> = +25°C                                                                                                                                                             |                                                                       | -2   |      | +2   | μΑ      |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN}$  = 12V,  $V_{CC}$  =  $V_{DD}$  =  $V_{IN3}$  =  $V_{\overline{SHDN}}$  =  $V_{PGD}$  = 5V,  $V_{DDIO}$  = 1.8V,  $V_{OPTION}$  =  $V_{GNDS}$  =  $V_{AGND}$  =  $V_{PGND}$ ,  $V_{PBDC}$  =  $V_{PBAC}$  =  $V_{PBAC}$

| PARAMETER                                                  | SYMBOL                | CONDITIONS                                                                                                                                      | MIN      | TYP   | MAX  | UNITS |

|------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|------|-------|

| Combined-Mode Detection<br>Threshold                       |                       | GNDS1, GNDS2, detection after REFOK, latched, cleared by cycling SHDN                                                                           | 0.7      | 0.8   | 0.9  | V     |

| Maximum Duty Factor                                        | DMAX                  |                                                                                                                                                 | 90       | 92    |      | %     |

| Minimum On-Time                                            | tonmin                |                                                                                                                                                 |          |       | 150  | ns    |

| SMPS1 AND SMPS2 CURRENT                                    | LIMIT                 |                                                                                                                                                 |          |       |      |       |

| Current-Limit Threshold<br>Tolerance                       | VLIMIT                | V <sub>CSP</sub> - V <sub>CSN</sub> = 0.052 x (V <sub>REF</sub> - V <sub>ILIM</sub> ),<br>(V <sub>REF</sub> - V <sub>ILM</sub> ) = 0.2V to 1.0V | -3       |       | +3   | mV    |

| Zero-Crossing Threshold                                    | V <sub>ZX</sub>       | V <sub>GND</sub> V <sub>LX</sub> _, skip mode                                                                                                   |          | 1     |      | mV    |

| Idle Mode™ Threshold                                       | V <sub>IMIN</sub>     | V <sub>CSP</sub> - V <sub>CSN</sub> , skip mode, 0.15 x V <sub>LIMIT</sub>                                                                      | -2       |       | +2   | mV    |

| CS_ Input Leakage Current                                  |                       | CSP_ and CSN_, T <sub>A</sub> = +25°C                                                                                                           | -0.2     |       | +0.2 | μΑ    |

| CS_ Common-Mode Input Range                                |                       | CSP_ and CSN_                                                                                                                                   | 0        |       | 2    | V     |

| SMPS1 AND SMPS2 DROOP, CL                                  | JRRENT BAL            | ANCE, AND TRANSIENT RESPONSE                                                                                                                    |          |       |      |       |

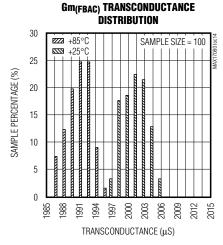

| AC Droop and Current Balance<br>Amplifier Transconductance | G <sub>m(FBAC_)</sub> | $\Delta$ IFBAC_/( $\Delta$ VCS_), VFBAC_ = VCSN_ = 1.2V, VCSP VCSN_ = 0mV to +40mV                                                              | 1.94     | 2.00  | 2.06 | mS    |

| AC Droop and Current Balance<br>Amplifier Offset           |                       | IFBAC_/Gm(FBAC_)                                                                                                                                | -1.5     |       | +1.5 | mV    |

| No-Load Positive Offset                                    |                       | OPTION = 2V or GND                                                                                                                              |          | +12.5 |      | mV    |

| Transient Detection Threshold                              |                       | Measured at FBDC_ with respect to steady-state FBDC_ regulation voltage, 5mV hysteresis (typ)                                                   | -47      |       | -28  | mV    |

| SMPS3 INTERNAL 3A STEP-DO                                  | WN CONVER             | RTER                                                                                                                                            |          |       |      |       |

| OUT3 Load Regulation                                       | R <sub>DROOP3</sub>   | $T_A = +25^{\circ}C$                                                                                                                            | 4.5      | 6.5   | 8.5  | mV/A  |

| OUT3 Line Regulation                                       |                       | 0% to 100% duty cycle                                                                                                                           |          | 5     |      | mV    |

| OUT3 Input Current                                         | I <sub>OUT3</sub>     |                                                                                                                                                 | -100     | -5    | +100 | nA    |

| LX3 Leakage Current                                        | I <sub>LX3</sub>      | $\overline{\text{SHDN}} = \text{GND}$ , $V_{\text{LX3}} = \text{GND}$ or 5.5V, $V_{\text{IN3}} = 5.5$ V, $T_{\text{A}} = +25$ °C                | -20      |       | +20  | μΑ    |

| Laterra - I MOOFFT On Desistance                           | Ron(NH3)              | High-side n-channel                                                                                                                             |          | 100   | 200  | 0     |

| Internal MOSFET On-Resistance                              | RON(NL3)              | Low-side n-channel                                                                                                                              |          | 50    | 100  | mΩ    |

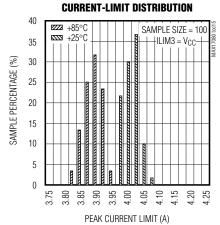

|                                                            |                       | VILIM3 = VCC                                                                                                                                    | 3.5      | 4.0   | 4.5  |       |

| LLV2 Dook Oversont Limit                                   |                       | V <sub>ILIM3</sub> = 3.3V                                                                                                                       |          | 3.4   |      | 1     |

| LX3 Peak Current Limit                                     | I <sub>LX3PK</sub>    | V <sub>ILIM3</sub> = 2V                                                                                                                         |          | 2.8   |      | A     |

|                                                            |                       | V <sub>ILIM3</sub> = GND                                                                                                                        |          | 2.2   |      | ]     |

| LX3 Idle-Mode Trip Level                                   | I <sub>LX3MIN</sub>   | Percentage of I <sub>LX3PK</sub>                                                                                                                |          | 25    |      | %     |

| LX3 Zero-Crossing Trip Level                               | I <sub>ZX3</sub>      | Skip mode                                                                                                                                       |          | 20    |      | mA    |

|                                                            |                       |                                                                                                                                                 | <u> </u> | 07    |      | 0/    |

| Maximum Duty Factor                                        | DMAX                  |                                                                                                                                                 | 84       | 87    |      | %     |

Idle Mode is a trademark of Maxim Integrated Products, Inc.

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD} = V_{IN3} = V_{\overline{SHDN}} = V_{PGD} = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $V_{OPTION} = V_{GNDS} = V_{AGND} = V_{PGND}$ ,  $V_{FBDC} = V_{FBAC} = V_{OUT3} = V_{CSP} = V_{CSN} = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                               | SYMBOL             | COI                                       | NDITIONS                                                    | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------------------------|--------------------|-------------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| FAULT DETECTION                                                         | •                  |                                           |                                                             |      |      |      | •     |

|                                                                         |                    |                                           | PWM mode                                                    | 250  | 300  | 350  | mV    |

| Output Overvoltage Trip<br>Threshold<br>(SMPS1 and SMPS2 Only)          | V <sub>OVP</sub> _ | Measured at FBDC_, rising edge            | Skip mode and output has not reached the regulation voltage | 1.80 | 1.85 | 1.90 | V     |

| (Olvii O'i alid Olvii Oz Olliy)                                         |                    | euge                                      | Minimum OVP threshold                                       |      | 0.8  |      |       |

| Output Overvoltage Fault<br>Propagation Delay (SMPS1 and<br>SMPS2 only) | tovp               | FBDC_ forced 25m                          | V above trip threshold                                      |      | 10   |      | μs    |

| Output Undervoltage Protection<br>Trip Threshold                        | VUVP               | Measured at FBDC to unloaded output       | _ or OUT3 with respect voltage                              | -450 | -400 | -350 | mV    |

| Output Undervoltage Fault<br>Propagation Delay                          | tuvp               | FBDC_ forced 25m                          | V below trip threshold                                      |      | 10   |      | μs    |

| PWRGD Threshold                                                         |                    | Measured at FBDC_ or OUT3 with respect to | Lower threshold,<br>falling edge<br>(undervoltage)          | -350 | -300 | -250 | mV    |

| rwnad iiilesiidia                                                       |                    | voltage,15mV                              | Upper threshold,<br>rising edge<br>(overvoltage)            | +150 | +200 | +250 | IIIV  |

| PWRGD Propagation Delay                                                 | tpwrgd             | FBDC_ or OUT3 for PWRGD trip thresh       | rced 25mV outside the olds                                  |      | 10   |      | μs    |

| PWRGD, Output Low Voltage                                               |                    | I <sub>SINK</sub> = 4mA                   |                                                             |      |      | 0.4  | V     |

| PWRGD Leakage Current                                                   | Ipwrgd             | High state, PWRGE +25°C                   | ) forced to 5.5V, T <sub>A</sub> =                          |      |      | 1    | μА    |

| PWRGD Startup Delay and Transition Blanking Time                        | tBLANK             | Measured from the OUT3 reach the tar      | time when FBDC_ and get voltage                             |      | 20   |      | μs    |

| VRHOT Trip Threshold                                                    |                    | Measured at THRM falling edge, 115m       | 1, with respect to V <sub>CC</sub> ,<br>V hysteresis (typ)  | 29.5 | 30   | 30.5 | %     |

| VRHOT Delay                                                             | tVRHOT             | THRM forced 25m\<br>threshold, falling e  | / below the VRHOT trip<br>dge                               |      | 10   |      | μs    |

| VRHOT, Output Low Voltage                                               |                    | Isink = 4mA                               |                                                             |      |      | 0.4  | V     |

| VRHOT Leakage Current                                                   |                    | High state, VRHOT                         | forced to 5V, T <sub>A</sub> = +25°C                        |      |      | 1    | μΑ    |

| THRM Input Leakage                                                      |                    | T <sub>A</sub> = +25°C                    |                                                             | -100 |      | +100 | nA    |

| Thermal-Shutdown Threshold                                              | TSHDN              | Hysteresis = 15°C                         |                                                             |      | +160 |      | °C    |

| GATE DRIVERS                                                            |                    |                                           |                                                             |      |      |      |       |

| DH_ Gate-Driver On-Resistance                                           | BONIDIA            | BST LX_ forced                            | High state (pullup)                                         |      | 0.9  | 2.5  | Ω     |

|                                                                         | RON(DH_)           | to 5V (Note 4)                            | Low state (pulldown)                                        |      | 0.7  | 2.5  | 32    |

| DL_ Gate-Driver On-Resistance                                           | Ron(DL_)           | DL_, high state                           |                                                             |      | 0.7  | 2.0  |       |

| DL_ Gate Driver Off-Heatatalle                                          | I TON(DL_)         | DL_, low state                            |                                                             |      | 0.25 | 0.6  | Ω     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD} = V_{IN3} = V_{\overline{SHDN}} = V_{PGD\_IN} = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $V_{OPTION} = V_{GNDS\_} = V_{AGND} = V_{PGND}$ ,  $V_{FBDC\_} = V_{FBAC\_} = V_{OUT3} = V_{CSP\_} = V_{CSN\_} = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                              | SYMBOL                          | CONDI                                                                                                  | ITIONS                                                 | MIN                        | TYP | MAX                        | UNITS |

|----------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| DH_ Gate-Driver Source/Sink<br>Current | I <sub>DH</sub> _               | DH_ forced to 2.5V, BS                                                                                 | ST LX_ forced to 5V                                    |                            | 2.2 |                            | А     |

| DL_ Gate-Driver Source Current         | I <sub>DL</sub> _               | DL_ forced to 2.5V                                                                                     |                                                        |                            | 2.7 |                            | А     |

| DL_ Gate-Driver Sink Current           | I <sub>DL</sub> (SINK)          | DL_ forced to 2.5V                                                                                     |                                                        |                            | 8   |                            | А     |

| Dood Time                              | tDH_DL                          | DH_ low to DL_ high                                                                                    |                                                        | 9                          | 20  | 35                         |       |

| Dead Time                              | t <sub>DL_DH</sub>              | DL_ low to DH_ high                                                                                    |                                                        | 9                          | 20  | 35                         | ns    |

| Internal BST1, BST2 Switch RON         |                                 | BST1, BST2 to V <sub>DD</sub> , I <sub>B</sub>                                                         | 3ST1 = IBST2 = 10mA                                    |                            | 10  | 20                         | Ω     |

| Internal BST3 Switch R <sub>ON</sub>   |                                 | BST3 to V <sub>DD</sub> , I <sub>BST3</sub> =                                                          | 10mA                                                   |                            | 10  | 20                         | Ω     |

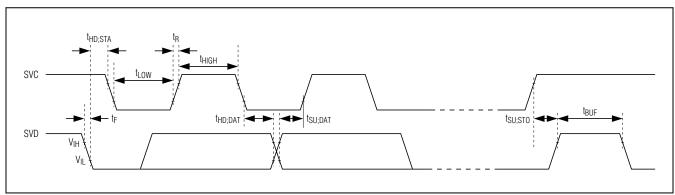

| 2-WIRE I2C BUS LOGIC INTERFA           | CE                              |                                                                                                        | · · · · · · · · · · · · · · · · · · ·                  |                            |     |                            |       |

| SVI Logic Input Current                |                                 | SVC, SVD, T <sub>A</sub> = +25°C                                                                       | C                                                      | -1                         |     | +1                         | μΑ    |

| SVI Logic Input Threshold              |                                 | SVC, SVD, rising edge                                                                                  |                                                        | 0.3 x<br>V <sub>DDIO</sub> |     | 0.7 x<br>V <sub>DDIO</sub> | V     |

| SVC Clock Frequency                    | fsvc                            |                                                                                                        |                                                        |                            |     | 3.4                        | MHz   |

| START Condition Hold Time              | thd;sta                         |                                                                                                        |                                                        | 160                        |     |                            | ns    |

| Repeated START Condition<br>Setup Time | tsu;sta                         |                                                                                                        |                                                        | 160                        |     |                            | ns    |

| STOP Condition Setup Time              | tsu;sto                         |                                                                                                        |                                                        | 160                        |     |                            | ns    |

| Data Hold                              | tHD;DAT                         | A master device mushold time of at least 3 signal (referred to the to bridge the undefine falling edge | 800ns for the SVD<br>V <sub>IHMIN</sub> of SVC signal) |                            |     | 70                         | ns    |

| Data Setup Time                        | tsu;dat                         |                                                                                                        |                                                        | 10                         |     |                            | ns    |

| SVC Low Period                         | tLOW                            |                                                                                                        |                                                        | 160                        |     |                            | ns    |

| SVC High Period                        | thigh                           | Measured from 10% to                                                                                   | o 90% of V <sub>DDIO</sub>                             | 60                         |     |                            | ns    |

| SVC/SVD Rise and Fall Time             | t <sub>R</sub> , t <sub>F</sub> | Input filters on SVD ar<br>noise spike less than                                                       |                                                        |                            |     | 40                         | ns    |

| Pulse Width of Spike Suppression       |                                 |                                                                                                        |                                                        |                            | 20  |                            | ns    |

| INPUTS AND OUTPUTS                     |                                 |                                                                                                        |                                                        |                            |     |                            |       |

| Logic Input Current                    |                                 | SHDN, PGD_IN, TA =                                                                                     | +25°C                                                  | -1                         |     | +1                         | μΑ    |

| Logic Input Current                    |                                 | ILIM3, OPTION, TA = -                                                                                  | +25°C                                                  | -200                       |     | +200                       | nA    |

| Logic Input Levels                     |                                 | SHDN, rising edge, hy                                                                                  | SHDN, rising edge, hysteresis = 225mV                  |                            |     | 2.0                        | V     |

|                                        |                                 |                                                                                                        | High                                                   | V <sub>CC</sub> - 0.4      |     |                            |       |

| Four-Level Input Logic Levels          |                                 | OPTION, ILIM3                                                                                          | 3.3V                                                   | 2.75                       |     | 3.85                       | V     |

|                                        |                                 |                                                                                                        | 2V                                                     | 1.65                       |     | 2.35                       |       |

|                                        |                                 |                                                                                                        | Low                                                    |                            |     | 0.4                        |       |

| PGD_IN Logic Input Threshold           |                                 | PGD_IN, rising edge,                                                                                   | hysteresis = 65mV                                      | 0.3 x<br>V <sub>DDIO</sub> |     | 0.7 x<br>V <sub>DDIO</sub> | V     |

6 \_\_\_\_\_\_ /N/XI/M

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 2,  $V_{IN}$  = 12V,  $V_{CC}$  =  $V_{DD}$  =  $V_{IN3}$  =  $V_{\overline{SHDN}}$  =  $V_{PGD\_IN}$  = 5V,  $V_{DDIO}$  = 1.8V,  $V_{OPTION}$  =  $V_{GNDS\_}$  =  $V_{AGND}$  =  $V_{PGND}$ ,  $V_{PBDC\_}$  =  $V_{PBAC\_}$  =  $V_{CSN\_}$  = 1.2V, all DAC codes set to the 1.2V code,  $\mathbf{T_A}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $T_{A}$  = +25°C.) (Note 5)

| PARAMETER                                           | SYMBOL                    | COND                                                                                                     | DITIONS                                                                                                | MIN  | TYP | MAX  | UNITS          |

|-----------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------|----------------|

| INPUT SUPPLIES                                      |                           | •                                                                                                        |                                                                                                        |      |     |      |                |

|                                                     | VIN                       | Drain of external high                                                                                   | n-side MOSFET                                                                                          | 4    |     | 26   |                |

| Input Voltage Range                                 | VBIAS                     | V <sub>CC</sub> , V <sub>DD</sub>                                                                        |                                                                                                        | 4.5  |     | 5.5  | ] <sub>V</sub> |

| input voitage hange                                 | V <sub>IN3</sub>          |                                                                                                          |                                                                                                        | 2.7  |     | 5.5  | ]              |

|                                                     | V <sub>DDIO</sub>         |                                                                                                          |                                                                                                        | 1.0  |     | 2.7  |                |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold   | V <sub>U</sub> VLO        | V <sub>CC</sub> rising, 50mV typ<br>latched, UV fault                                                    | ical hysteresis,                                                                                       | 4.10 |     | 4.45 | V              |

| V <sub>DDIO</sub> Undervoltage-Lockout<br>Threshold |                           | V <sub>DDIO</sub> rising, 100mV latched, UV fault                                                        | typical hysteresis,                                                                                    | 0.7  |     | 0.9  | V              |

| V <sub>IN3</sub> Undervoltage-Lockout<br>Threshold  |                           | V <sub>IN3</sub> rising, 100mV ty                                                                        | pical hysteresis                                                                                       | 2.5  |     | 2.7  | V              |

| Quiescent Supply Current (V <sub>CC</sub> )         | Icc                       | Skip mode, FBDC_ a above their regulation                                                                |                                                                                                        |      |     | 10   | mA             |

| Quiescent Supply Current                            | IDDIO                     |                                                                                                          |                                                                                                        |      |     | 25   | μΑ             |

| Quiescent Supply Current (IN3)                      | I <sub>IN3</sub>          | Skip mode, OUT3 forced above its regulation point                                                        |                                                                                                        |      |     | 200  | μА             |

| INTERNAL DACs, SLEW RATE,                           | PHASE SHIF                | T                                                                                                        |                                                                                                        |      |     |      |                |

|                                                     |                           | Measured at FBDC_<br>for the core SMPSs;                                                                 | DAC codes from 0.8375V to 1.5500V                                                                      | -0.7 |     | +0.7 | %              |

| DC Output Voltage Accuracy                          | Vоит                      | measured at OUT3<br>for the NB SMPS;<br>30% duty cycle,<br>no load, ILIM3 =                              | DAC codes from<br>0.5000V to 0.8250V                                                                   | -7.5 |     | +7.5 | mV             |

|                                                     |                           | VCC, VOUT3 = VDAC3<br>+ 12.5mV (Note 3)                                                                  | DAC codes from<br>12.5mV to 0.4875V                                                                    | -15  |     | +15  | IIIV           |

|                                                     |                           |                                                                                                          | $R_{TIME} = 143k\Omega$ ,<br>$SR = 6.25mV/\mu s$                                                       | -10  |     | +10  |                |

| Slew-Rate Accuracy                                  |                           |                                                                                                          | R <sub>TIME</sub> = $35.7$ k $\Omega$ to $357$ k $\Omega$ , SR = $25$ mV/ $\mu$ s to $2.5$ mV/ $\mu$ s | -15  |     | +15  | %              |

|                                                     |                           | $R_{OSC} = 143kΩ$ (fosc nominal, fosc3 = 600                                                             |                                                                                                        | -7.5 |     | +7.5 |                |

| Switching Frequency Accuracy                        | fosc1,<br>fosc2,<br>fosc3 | Rosc = 71.4k $\Omega$ (fosc<br>nominal, fosc3 = 1.2<br>432k $\Omega$ (fosc1 = fosc<br>fosc3 = 199kHz nom | 2 = 99kHz nominal,                                                                                     | -10  |     | +10  | %              |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD} = V_{IN3} = V_{\overline{SHDN}} = V_{PGD\_IN} = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $V_{OPTION} = V_{GNDS\_} = V_{AGND} = V_{PGND}$ ,  $V_{FBDC\_} = V_{FBAC\_} = V_{OUT3} = V_{CSP\_} = V_{CSN\_} = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 5)

| PARAMETER                                                  | SYMBOL                    | CONDITIONS                                                                                                                                                                                                                                                                    | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

|                                                            | t.                        | $R_{OSC} = 143 k\Omega$ ( $f_{OSC1} = f_{OSC2} = 300 kHz$ nominal, $f_{OSC3} = 600 kHz$ nominal)                                                                                                                                                                              | -7.5 |     | +7.5 |       |

| Switching Frequency Accuracy                               | fosc1,<br>fosc2,<br>fosc3 | $\begin{aligned} &R_{OSC} = 71.4 k\Omega \; (f_{OSC1} = f_{OSC2} = 600 \text{kHz} \\ &\text{nominal, } f_{OSC3} = 1.2 \text{MHz nominal)} \; \text{to} \\ &432 k\Omega \; (f_{OSC1} = f_{OSC2} = 99 \text{kHz nominal,} \\ &f_{OSC3} = 199 \text{kHz nominal)} \end{aligned}$ | -10  |     | +10  | %     |

| SMPS1 AND SMPS2 CONTROLL                                   | ERS                       |                                                                                                                                                                                                                                                                               |      |     |      |       |

| GNDS_ Input Range                                          | V <sub>GNDS</sub> _       | Separate mode                                                                                                                                                                                                                                                                 | -200 |     | +200 | mV    |

| GNDS_ Gain                                                 | AGNDS_                    | Separate: $\Delta V_{OUT}/\Delta V_{GNDS}$ , -200mV $\leq$ $V_{GNDS} \leq$ +200mV; combined; $\Delta V_{OUT}/\Delta V_{GNDS}$ , -200mV $\leq$ $V_{GNDS} \leq$ +200mV                                                                                                          | 0.95 |     | 1.05 | V/V   |

| Combined-Mode Detection<br>Threshold                       |                           | GNDS1, GNDS2, detection after REFOK, latched, cleared by cycling SHDN                                                                                                                                                                                                         | 0.7  |     | 0.9  | V     |

| Maximum Duty Factor                                        | DMAX                      |                                                                                                                                                                                                                                                                               | 90   |     |      | %     |

| Minimum On-Time                                            | tonmin                    |                                                                                                                                                                                                                                                                               |      |     | 150  | ns    |

| SMPS1 AND SMPS2 CURRENT I                                  | _IMIT                     |                                                                                                                                                                                                                                                                               |      |     |      |       |

| Current-Limit Threshold Tolerance                          | VLIMIT                    | V <sub>CSP</sub> - V <sub>CSN</sub> = 0.052 x (V <sub>REF</sub> - V <sub>ILIM</sub> ),<br>(V <sub>REF</sub> - V <sub>ILM</sub> ) = 0.2V to 1.0V                                                                                                                               | -3   |     | +3   | mV    |

| Idle-Mode Threshold Tolerance                              | VIMIN                     | V <sub>CSP</sub> - V <sub>CSN</sub> , skip mode, 0.15 x V <sub>LIMIT</sub>                                                                                                                                                                                                    | -2   |     | +2   | mV    |

| CS_Common-Mode Input Range                                 |                           | CSP_ and CSN_                                                                                                                                                                                                                                                                 | 0    |     | 2    | V     |

| SMPS1 AND SMPS2 DROOP, CU                                  | IRRENT BAL                | ANCE, AND TRANSIENT RESPONSE                                                                                                                                                                                                                                                  |      |     |      |       |

| AC Droop and Current Balance<br>Amplifier Transconductance | G <sub>m(FBAC_)</sub>     | $\Delta$ IFBAC_/( $\Delta$ VCS_), VFBAC_ = VCSN_ = 1.2V, VCSP VCSN_ = 0mV to +40mV                                                                                                                                                                                            | 1.94 |     | 2.06 | mS    |

| AC Droop and Current Balance<br>Amplifier Offset           |                           | IFBAC_/Gm(FBAC_)                                                                                                                                                                                                                                                              | -1.5 |     | +2.0 | mV    |

| Transient Detection Threshold                              |                           | Measured at FBDC_ with respect to steady-state FBDC_ regulation voltage, 5mV hysteresis (typ)                                                                                                                                                                                 | -47  |     | -28  | mV    |

| SMPS3 INTERNAL 3A STEP-DO\                                 | NN CONVER                 | TER                                                                                                                                                                                                                                                                           |      |     |      |       |

| OUT3 Load Regulation                                       | R <sub>DROOP3</sub>       |                                                                                                                                                                                                                                                                               | 4.5  |     | 8.5  | mV/A  |

| Internal MOSFET On-Resistance                              | RON(NH3)                  | High-side n-channel                                                                                                                                                                                                                                                           |      |     | 200  | mΩ    |

| internal MOOI ET OFFITESISTATICE                           | Ron(NL3)                  | Low-side n-channel                                                                                                                                                                                                                                                            |      |     | 100  | 11122 |

| LX3 Peak Current Limit                                     | I <sub>LX3PK</sub>        | ILIM3 = V <sub>CC</sub> , skip mode                                                                                                                                                                                                                                           | 3.5  |     | 4.5  | Α     |

| Maximum Duty Factor                                        | DMAX                      |                                                                                                                                                                                                                                                                               | 84   |     |      | %     |

| Minimum On-Time                                            | tonmin                    |                                                                                                                                                                                                                                                                               |      |     | 150  | ns    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD} = V_{IN3} = V_{\overline{SHDN}} = V_{PGD\_IN} = 5V$ ,  $V_{DDIO} = 1.8V$ ,  $V_{OPTION} = V_{GNDS\_} = V_{AGND} = V_{PGND}$ ,  $V_{FBDC\_} = V_{FBAC\_} = V_{CSN\_} = 1.2V$ , all DAC codes set to the 1.2V code,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 5)

| PARAMETER                                                      | SYMBOL               | COND                                                                                                                 | ITIONS                                                                                   | MIN                        | TYP | MAX                        | UNITS |

|----------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| FAULT DETECTION                                                | '                    |                                                                                                                      |                                                                                          |                            |     |                            |       |

|                                                                |                      |                                                                                                                      | PWM mode                                                                                 | 250                        |     | 350                        | mV    |

| Output Overvoltage Trip<br>Threshold<br>(SMPS1 and SMPS2 Only) | V <sub>OVP</sub> _   | Measured at FBDC_, rising edge                                                                                       | Skip mode and output have not reached the regulation voltage                             | 1.80                       |     | 1.90                       | V     |

| Output Undervoltage Protection<br>Trip Threshold               | V <sub>U</sub> VP    | Measured at FBDC_ to unloaded output vo                                                                              |                                                                                          | -450                       |     | -350                       | mV    |

| PWRGD Threshold                                                |                      | Measured at FBDC_<br>or OUT3 with respect<br>to unloaded output                                                      | Lower threshold,<br>falling edge<br>(undervoltage)                                       | -350                       |     | -250                       | mV    |

| T WHOS THROSHOLD                                               |                      | voltage, 15mV<br>hysteresis (typ)                                                                                    | Upper threshold,<br>rising edge<br>(overvoltage)                                         | +150                       |     | +250                       |       |

| PWRGD, Output Low Voltage                                      |                      | I <sub>SINK</sub> = 4mA                                                                                              |                                                                                          |                            |     | 0.4                        | V     |

| VRHOT Trip Threshold                                           |                      |                                                                                                                      | Measured at THRM, with respect to V <sub>CC</sub> , falling edge, 115mV hysteresis (typ) |                            |     | 30.5                       | %     |

| VRHOT, Output Low Voltage                                      |                      | I <sub>SINK</sub> = 4mA                                                                                              |                                                                                          |                            |     | 0.4                        | V     |

| GATE DRIVERS                                                   |                      |                                                                                                                      |                                                                                          |                            |     |                            |       |

| DH_ Gate-Driver On-Resistance                                  | R <sub>ON(DH_)</sub> | BST LX_ forced to 5V (Note 4)                                                                                        | High state (pullup)  Low state (pulldown)                                                |                            |     | 2.5<br>2.5                 | Ω     |

|                                                                | _                    | DL_, high state                                                                                                      | ,                                                                                        |                            |     | 2.0                        | _     |

| DL_ Gate-Driver On-Resistance                                  | RON(DL_)             | DL_, low state                                                                                                       |                                                                                          |                            |     | 0.6                        | Ω     |

| D 17:                                                          | t <sub>DH_DL</sub>   | DH_ low to DL_ high                                                                                                  |                                                                                          | 9                          |     | 35                         |       |

| Dead Time                                                      | t <sub>DL_DH</sub>   | DL_ low to DH_ high                                                                                                  |                                                                                          | 9                          |     | 35                         | ns    |

| Internal BST1, BST2 Switch RON                                 |                      | BST1, BST2 to V <sub>DD</sub> , I <sub>E</sub>                                                                       | BST1 = IBST2 = 10mA                                                                      |                            |     | 20                         | Ω     |

| Internal BST3 Switch RON                                       |                      | BST3 to V <sub>DD</sub> , I <sub>BST3</sub> =                                                                        | 10mA                                                                                     |                            |     | 20                         | Ω     |

| 2-WIRE I2C BUS LOGIC INTERFA                                   | CE                   |                                                                                                                      |                                                                                          |                            |     |                            |       |

| SVI Logic Input Threshold                                      |                      | SVC, SVD, rising edge VDDIO(V)                                                                                       | e, hysteresis = 0.14 x                                                                   | 0.3 x<br>V <sub>DDIO</sub> |     | 0.7 x<br>V <sub>DDIO</sub> | V     |

| SVC Clock Frequency                                            | fsvc                 |                                                                                                                      |                                                                                          |                            |     | 3.4                        | MHz   |

| START Condition Hold Time                                      | tsu;sta              |                                                                                                                      |                                                                                          | 160                        |     |                            | ns    |

| Repeated START Condition<br>Setup Time                         | tsu;sta              |                                                                                                                      |                                                                                          | 160                        |     |                            | ns    |

| STOP Condition Setup Time                                      | tsu;sto              |                                                                                                                      |                                                                                          | 160                        |     |                            | ns    |

| Data Hold                                                      | <sup>t</sup> HD;DAT  | A master device must<br>hold time of at least 30<br>(referred to the V <sub>IHMIN</sub> of<br>the undefined region o | 00ns for the SVD signal of SVC signal) to bridge                                         |                            |     | 70                         | ns    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2,  $V_{IN}$  = 12V,  $V_{CC}$  =  $V_{DD}$  =  $V_{IN3}$  =  $V_{\overline{SHDN}}$  =  $V_{PGD\_IN}$  = 5V,  $V_{DDIO}$  = 1.8V,  $V_{OPTION}$  =  $V_{GNDS\_}$  =  $V_{AGND}$  =  $V_{PGND}$ ,  $V_{PBDC\_}$  =  $V_{PGND}$  = 1.2V, all DAC codes set to the 1.2V code,  $V_{AB}$  = -40°C to +105°C, unless otherwise noted. Typical values are at  $V_{AB}$  = +25°C.) (Note 5)

| PARAMETER                     | SYMBOL                          | COI                | NDITIONS                                                         | MIN                        | TYP | MAX                        | UNITS |

|-------------------------------|---------------------------------|--------------------|------------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| Data Setup Time               | tsu;dat                         |                    |                                                                  | 10                         |     |                            | ns    |

| SVC Low Period                | tLOW                            |                    |                                                                  |                            |     |                            | ns    |

| SVC High Period               | tHIGH                           | Measured from 10°  | Measured from 10% to 90% of V <sub>DDIO</sub>                    |                            |     |                            | ns    |

| SVC/SVD Rise and Fall Time    | t <sub>R</sub> , t <sub>F</sub> |                    | Input filters on SVD and SVC suppress noise spike less than 50ns |                            |     | 40                         | ns    |

| INPUTS AND OUTPUTS            |                                 |                    |                                                                  |                            |     |                            |       |

| Logic Input Levels            |                                 | SHDN, rising edge  | , hysteresis = 225mV                                             | 0.8                        |     | 2.0                        | V     |

|                               |                                 |                    | High                                                             | V <sub>CC</sub> - 0.4      |     |                            |       |

| Four-Level Input Logic Levels |                                 | OPTION, ILIM3      | 3.3V                                                             | 2.75                       |     | 3.85                       | V     |

|                               |                                 |                    | 2V                                                               | 1.65                       |     | 2.35                       |       |

|                               |                                 |                    | Low                                                              |                            |     | 0.4                        |       |

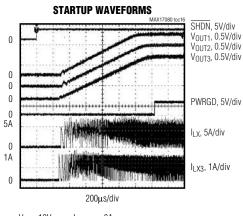

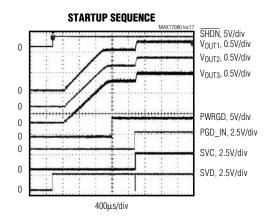

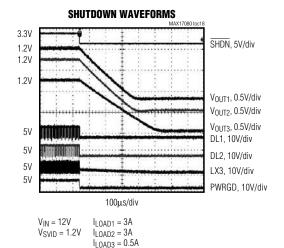

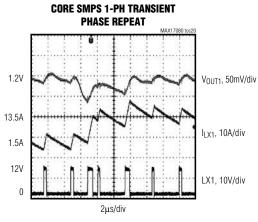

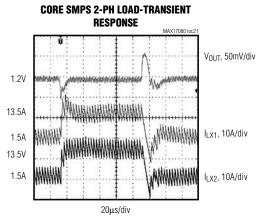

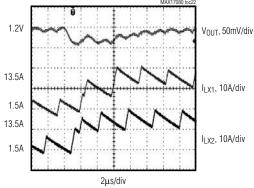

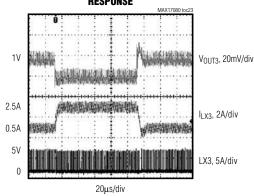

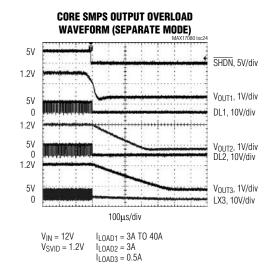

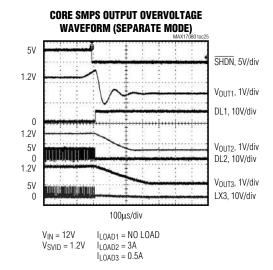

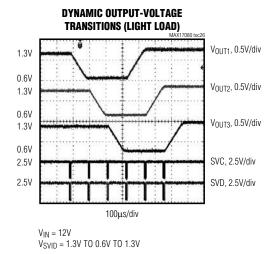

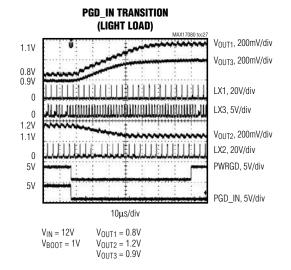

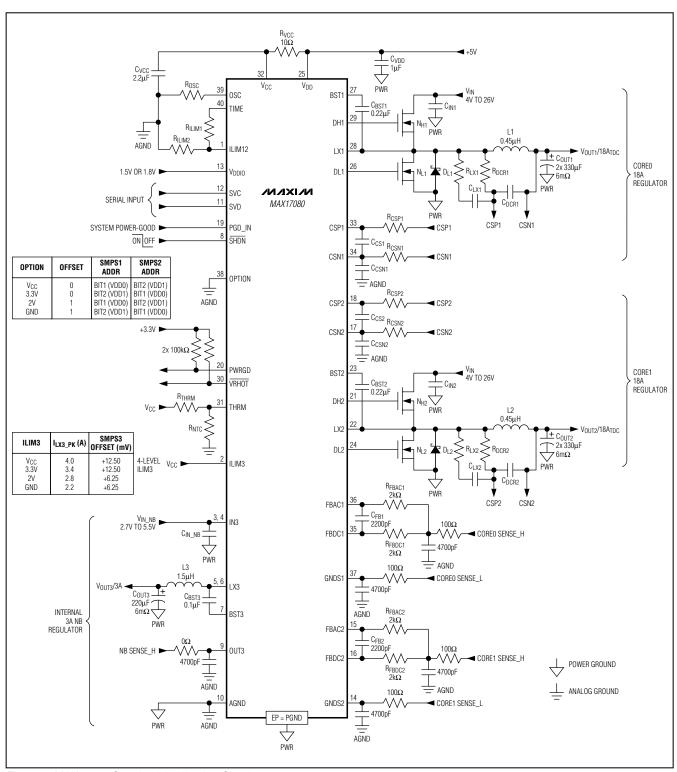

| PGD_IN Logic Input Threshold  |                                 | PGD_IN, rising edg | ge, hysteresis = 65mV                                            | 0.3 x<br>V <sub>DDIO</sub> |     | 0.7 x<br>V <sub>DDIO</sub> | V     |