## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

EVALUATION KIT AVAILABLE

keep-alive linear regulators:

### Integrated Charger, Dual Main Step-Down Controllers, and Dual LDO Regulators

#### **General Description**

\_Features

- All-in-One Charger Plus Dual Main Step-Down Controllers

- ♦ 5V/100mA and 3.3V/50mA LDO Regulators

- Main

Dual Quick-PWM with Fast Transient Response and Extended On-Time 300kHz to 800kHz Switching Frequency Fixed 5V and 3.3V SMPS Outputs Low-Noise Ultrasonic Mode Autoretry Fault Protection

SFETs. hd cell High Sw

High Switching Frequency (1.4MHz) Selectable 2-, 3-, and 4-Cell Battery Voltage Automatic Selection of System Power Source Internal Charge-Pump for Adapter n-Channel MOSFETs Drive ±0.4% Accurate Charge Voltage

±2.5% Accurate Input Current Limiting ±3% Accurate Charge Current

- Monitor Outputs for AC Adapter Current (±2% Accuracy) Battery Discharge Current (±2% Accuracy) AC Adapter OK

- Analog/PWM (100Hz to 500kHz) Adjustable Charge Current Setting

- AC Adapter Overvoltage and Overcurrent Protection

**Applications**

Notebook Computers PDAs and Mobile Communicators 5V and 3.3V Supplies 2-to-4, Li+-Cell, Battery-Powered Devices

#### **Ordering Information**

| PART                | TEMP RANGE          | PIN-PACKAGE |

|---------------------|---------------------|-------------|

| MAX17085BETL+       | -40°C to +85°C      | 40 TQFN-EP* |

| +Denotes a lead(Pb) | -free/RoHS-compliar | nt package  |

+Denotes a lead(Pb)-tree/RoH5-compliant package \*EP = Exposed pad.

#### Pin Configuration appears at end of data sheet.

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

Maxim Integrated Products 1

MAX17085B

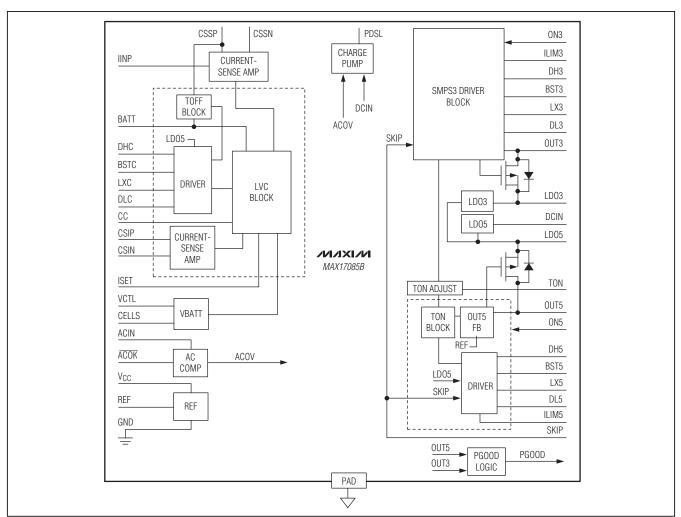

The charger uses n-channel switching MOSFETs. Adjustable charge current, charge voltage, and cell selection allow for flexible use with different battery packs. Charge current is set by an analog control input, or a PWM input. High-accuracy current-sense amplifiers provide fast cycle-by-cycle current-mode control to protect against short circuits to the battery and respond quickly to system load transients. Additionally, the charger provides a high-accuracy analog output that is proportional to the adapter current.

The MAX17085B is an all-in-one notebook power solution

integrating a multichemistry battery charger, dual fixed-

output Quick-PWM<sup>™</sup> step-down controllers, and dual

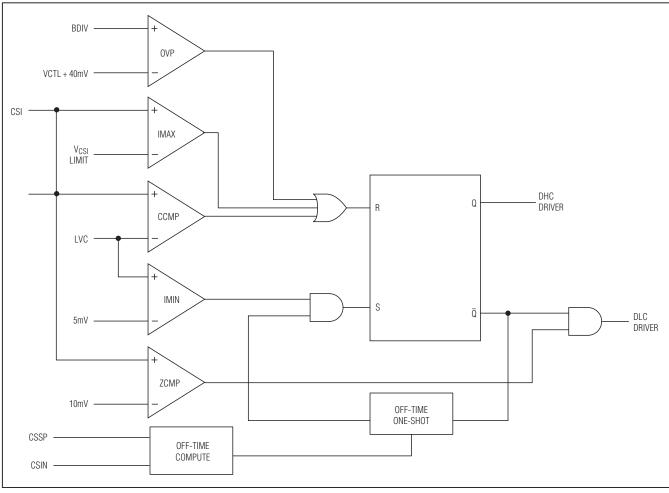

Charger: The high-frequency (~1.4MHz) multichem-

istry battery charger uses a current-mode, fixed

inductor current ripple architecture that significantly

reduces component size and cost. Low-offset sense

amplifiers allow the use of low-value sense resistors

for charging and input current limit.

An integrated charge pump controls an n-channel adapter selector switch. The charge pump remains active even when the charger is off. When the adapter is absent, a p-channel MOSFET selects the battery.

**Main SMPS:** The dual Quick-PWM step-down controllers with synchronous rectification generate the 5V and 3.3V main power in a notebook. Lowside MOSFET sensing provides a simple low-cost, highly efficient valley current-limit protection. The MAX17085B also includes output undervoltage, output overvoltage, and thermal-fault protection.

Separate enable inputs for each SMPS and a combined open-drain power-good output allow flexible power sequencing. Voltage soft-start reduces inrush current, while passive shutdown discharges the output through an internal switch. Fast transient response, with an extended on-time feature reduces output capacitance requirements. Selectable pulseskipping mode and ultrasonic mode improve lightload efficiency. Ultrasonic mode operation maintains a minimum switching frequency at light loads, minimizing audible noise effects.

**Dual LDO Regulators:** An internal 5V/100mA LDO5 with switchover can be used to either generate the 5V bias needed for power-up or other lower power "always-on" suspend supplies. Another 3.3V/50mA LDO3 provides "always-on" power to a system microcontroller.

####

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

TON, DCIN, CSSP, BATT, CSIP to GND,

MAX17085B

|                                 | LD,                                |

|---------------------------------|------------------------------------|

| LX_ to GND                      | 0.3V to +28V                       |

| CSIP to CSIN, CSSP to CSSN      | -0.3V to +0.3V                     |

| LDO3, LDO5, VCC to GND (Note 2) | -0.3V to +6V                       |

| ISET, VCTL, ACIN, ACOK to GND   | -0.3V to +6V                       |

| OUT3, OUT5 to GND (Note 2)      | -0.3V to +6V                       |

| ON3, ON5, PGOOD to GND          | -0.3V to +6V                       |

| ILIM3, ILIM5, SKIP, REF to GND  | 0.3V to (VCC + 0.3V)               |

| GND to EP                       | -0.3V to +0.3V                     |

| DL_ to EP                       | 0.3V to (V <sub>LDO5</sub> + 0.3V) |

| BST_ to GND                     | 0.3V to +34V                       |

| BST_ to LDO5                    |                                    |

| DH3 to LX3                      | 0.3V to (V <sub>BST3</sub> + 0.3V) |

| BST3 to LX3                     |                                    |

| DH5 to LX5                      | 0.3V to (V <sub>BST5</sub> + 0.3V) |

| BST5 to LX5                     | 0.3V to +6V                        |

|                                 |                                    |

| DHC to LXC0.3V to (V <sub>BSTC</sub> + 0.3V)          |

|-------------------------------------------------------|

| PDSL to GND0.3V to + 36V                              |

| BSTC to LXC0.3V to +6V                                |

| CELLS, CC, IINP to GND0.3V to ( $V_{LDO5} + 0.3V$ )   |

| LDO_ Short Circuit to GND Momentary                   |

| LDO5 Current (Internal Regulator) Continuous+100mA    |

| LDO3 Current (Internal Regulator) Continuous+50mA     |

| LDO_ Current (Switched Over) Continuous+200mA         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| 40-Pin Thin QFN (derate 34.5mW/°C above +70°C) 2857mW |

| Operating Temperature Range40°C to +85°C              |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

| Soldering Temperature (reflow)+260°C                  |

|                                                       |

Note 1: Absolute Maximum Ratings valid using 20MHz bandwidth limit.

**Note 2:** LDO5 has a weak leakage to V<sub>CC</sub> when LDO5 is more than 0.5V above V<sub>CC</sub>. OUT5 has a weak leakage to V<sub>CC</sub> when OUT5 is more than 0.5V above V<sub>CC</sub>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

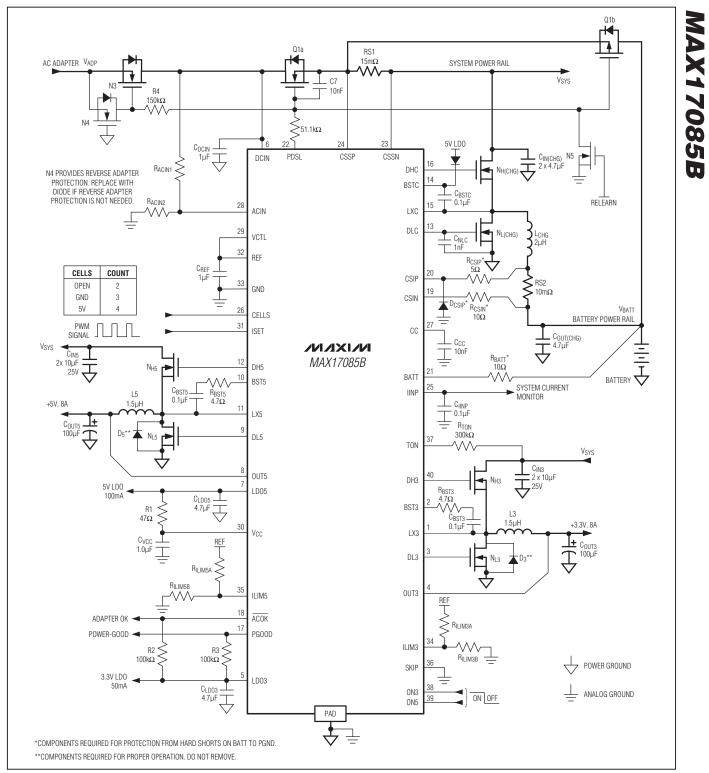

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ ,  $ON3 = ON5 = V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                           | SYMBOL | CONDITIONS                                                                 |                            | MIN | ТҮР | MAX | UNITS |

|-------------------------------------|--------|----------------------------------------------------------------------------|----------------------------|-----|-----|-----|-------|

| INPUT SUPPLIES                      |        | •                                                                          |                            |     |     |     |       |

| Adapter Present Quiescent           |        | $I_{DCIN} + I_{CSSP} + I_{CSSN},$<br>ON3 = ON5 = SKIP = VCC.               | Charging<br>enabled        |     | 3   | 6   | mA    |

| Current                             |        | $V_{OUT3} = 3.5V, V_{OUT5} = 5.3V$                                         | Charging<br>disabled       |     | 1.5 | 2.5 |       |

| Adapter Absent Quiescent<br>Current |        | $I_{DCIN} + I_{CSSP} + I_{CSSN},$<br>ON3 = ON5 = SKIP = V <sub>CC</sub> ,  | VISET = 2.4V,<br>IINP ON   |     | 1.5 | 2.5 | mA    |

|                                     |        | VOUT3 = 3.5V, VOUT5 = 5.3V                                                 | ISET = GND                 |     | 1.2 | 2.2 |       |

| CSSN Input Current                  |        | $V_{CSSP} = V_{CSSN} = 24V, T_A = -$                                       | +25°C                      |     | 0.1 | 2   | μA    |

| BATT + CSIP + CSIN + LXC            |        | VBATT = 16.8V, adapter abse                                                | nt, T <sub>A</sub> = +25°C |     |     | 4   |       |

| Input Current                       |        | VBATT = 2V to 19V, adapter p                                               | oresent                    |     | 200 | 650 | μA    |

| DCIN Input Current                  | IDCIN  | $ON3 = ON5 = SKIP = V_{CC}$ , cl<br>disabled; $V_{OUT3} = 3.5V$ , $V_{OU}$ | •                          |     | 0.1 | 0.2 | mA    |

| DCIN Standby Supply Current         |        | $V_{DCIN} = 5V$ to 24V, ON3 = OI                                           | N5 = GND                   |     | 130 | 270 | μA    |

| VCC Supply Current                  | Icc    | $ON3 = ON5 = SKIP = V_{CC}$ , cl<br>disabled; $V_{OUT3} = 3.5V$ , $V_{OU}$ | -                          |     | 1.0 | 1.5 | mA    |

| DCIN Input Voltage Range            |        | <b>Note:</b> LDO5 is NOT guarante regulation until DCIN is above           |                            | 4.5 |     | 24  | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ ,  $ON3 = ON5 = V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                         | SYMBOL      | CONDI                                                           | TIONS                                      | MIN   | TYP   | MAX   | UNITS |

|---------------------------------------------------|-------------|-----------------------------------------------------------------|--------------------------------------------|-------|-------|-------|-------|

| DCIN Undervoltage-Lockout                         |             | VDCIN falling                                                   |                                            | 7.0   | 7.2   |       | V     |

| Trip Point for Charger                            | VDCIN(UVLO) | V <sub>DCIN</sub> rising                                        |                                            |       | 7.7   | 7.9   |       |

| DCIN POR Threshold                                | VDCIN(POR)  | Falling edge of VDCIN                                           |                                            |       | 2.0   |       | V     |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold | VCC(UVLO)   | Falling edge of V <sub>CC</sub> , P<br>this threshold           | WM disabled below                          | 3.8   | 4.0   | 4.3   | V     |

| meshola                                           |             | Rising edge of V <sub>CC</sub>                                  |                                            |       | 4.2   |       | 1     |

| V <sub>CC</sub> POR Threshold                     |             | Falling edge of V <sub>CC</sub>                                 |                                            |       | 1.5   |       | V     |

| LINEAR REGULATORS                                 |             |                                                                 |                                            |       |       |       |       |

|                                                   | VLDO5       | $V_{DCIN} = 6V \text{ to } 24V, ON$<br>$0mA < I_{LDO5} < 100mA$ |                                            | 4.90  | 5.00  | 5.10  | V     |

| LDO_ Output-Voltage Accuracy                      | VLDO3       | VLDO5 = 5V, ILDO5 = 0<br>0mA < ILDO3 < 50mA,                    |                                            | 3.23  | 3.30  | 3.37  |       |

| Internal LDO Voltage After                        | VLDO5       | Not production tested                                           |                                            | 4.4   | 4.5   | 4.6   | V     |

| Switchover                                        | Vldo3       | Not production tested                                           |                                            | 2.7   | 2.8   | 2.9   |       |

| LDO3 Short-Circuit Current                        |             | LDO3 = GND                                                      |                                            | 50    |       | 130   | mA    |

| LDO5 Short-Circuit Current                        |             | LDO5 = GND                                                      |                                            | 100   |       | 260   | mA    |

| LDO5 Bootstrap Switch<br>Resistance               |             | LDO5 to OUT5, VOUT5 = 5V, ILDO5 = 50mA                          |                                            |       | 1.0   | 2.5   | Ω     |

| LDO3 Bootstrap Switch<br>Resistance               |             | LDO3 to OUT3, V <sub>OUT3</sub><br>I <sub>LDO3</sub> = 50mA     | = 3.3V,                                    |       | 1.5   | 3     | Ω     |

| Thermal-Shutdown Threshold                        | tSHDN       | Hysteresis = 50°C                                               |                                            |       | +160  |       | °C    |

| REFERENCE                                         |             |                                                                 |                                            | 1     |       |       |       |

| REF Output Voltage                                | VREF        | IREF = 50µA                                                     |                                            | 2.09  | 2.10  | 2.11  | V     |

| REF Undervoltage-Lockout<br>Threshold             | VREF_UVLO   | V <sub>REF</sub> falling                                        |                                            |       | 2.0   |       | V     |

| MAIN SMPS                                         |             |                                                                 |                                            | 1     |       |       | 1     |

| OUT5 Output Voltage Accuracy                      | Vout5       | $V_{IN} = 6V$ to 28V, SKIP                                      | = REF                                      | 5.033 | 5.083 | 5.135 | V     |

| OUT3 Output Voltage Accuracy                      | Vout3       | $V_{IN} = 6V$ to 28V, SKIP                                      |                                            | 3.267 | 3.300 | 3.333 | V     |

|                                                   |             | Either SMPS, VSKIP = 2                                          | 2V, ILOAD = 0 to 5A                        |       | -0.1  |       |       |

| Load Regulation Error                             |             | Either SMPS, SKIP = G                                           |                                            |       | -1.7  |       | %     |

| -                                                 |             | Either SMPS, SKIP = V                                           |                                            |       | -1.5  |       |       |

| Line Regulation Error                             |             | Either SMPS, VIN = 6V                                           |                                            |       | 0.005 |       | %/V   |

|                                                   | to          | V <sub>IN</sub> = 12V,                                          | R <sub>TON</sub> = 549kΩ<br>(300kHz + 10%) | 1073  | 1263  | 1452  |       |

| DH5 On-Time                                       | ton5        | V <sub>OUT5</sub> = 5.0V (Note 3)                               | R <sub>TON</sub> = 202kΩ<br>(800kHz + 10%) | 402   | 473   | 545   | ns    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                                 | SYMBOL      | CONI                                                   | CONDITIONS                                               |           | ТҮР        | MAX        | UNITS |

|---------------------------------------------------------------------------|-------------|--------------------------------------------------------|----------------------------------------------------------|-----------|------------|------------|-------|

| DH2 On Time                                                               | tous        | V <sub>IN</sub> = 12V,                                 | R <sub>TON</sub> = 549kΩ<br>(300kHz - 10%)               | 866       | 1019       | 1171       |       |

| DH3 On-Time                                                               | ton3        | VOUT3 = 3.3V (Note 5                                   | <sup>3)</sup> R <sub>TON</sub> = 202kΩ<br>(800kHz - 10%) | 325       | 382        | 439        | ns    |

| Minimum Off-Time                                                          | toff(MIN)   | (Note 3)                                               |                                                          | 210       | 270        | 330        | ns    |

| Extended On-Time Blanking                                                 |             | Duty cycle > 50%; no                                   | ot for production test                                   |           | 300        | 360        | ns    |

| Soft-Start Time                                                           | tss         | Rising edge on ON_                                     |                                                          |           | 2          |            | ms    |

| Ultrasonic Operating Frequency                                            | fsw(usonic) | SKIP = GND                                             |                                                          | 15        | 22         |            | kHz   |

| MAIN SMPS FAULT DETECTIO                                                  | <b>N</b>    |                                                        |                                                          |           |            |            |       |

| OUT_ Overvoltage Trip<br>Threshold (PGOOD Pulled Low<br>Above This Level) |             | With respect to error                                  | comparator threshold                                     | 13        | 16         | 19         | %     |

| OUT_Overvoltage Fault<br>Propagation Delay                                | tovp        | V <sub>FB</sub> forced 50mV at                         | V <sub>FB</sub> forced 50mV above trip threshold         |           |            |            | μs    |

| OUT_ Undervoltage Protection<br>Trip Threshold                            |             | With respect to error comparator threshold             |                                                          | 65        | 70         | 75         | %     |

| OUT_ Output Undervoltage<br>Fault Propagation Delay                       | tuvp        |                                                        |                                                          |           | 10         |            | μs    |

| PGOOD Lower Trip Threshold                                                |             | With respect to error falling edge, hystere            | comparator threshold,<br>sis = 15mV                      | -350      | -250       | -150       | mV    |

| PGOOD Propagation Delay                                                   | tpgood      | OUT5 or OUT3 force<br>PGOOD trip threshol              |                                                          |           | 10         |            | μs    |

| PGOOD Output Low Voltage                                                  |             | PGOOD low impeda<br>GND, I <sub>SINK</sub> = 4mA       | nce, ON5 = ON3 =                                         |           |            | 0.3        | V     |

| PGOOD Leakage Current                                                     | IPGOOD      | PGOOD high impeda<br>regulation, PGOOD f<br>TA = +25°C |                                                          |           |            | 1          | μA    |

| Fault Reset Timer                                                         |             |                                                        |                                                          | 7         | 10         |            | ms    |

| MAIN SMPS CURRENT LIMIT                                                   |             |                                                        |                                                          |           |            |            |       |

| ILIM_ Adjustment Range                                                    |             |                                                        |                                                          | 0.2       |            | 2.1        | V     |

| ILIM_ Leakage Current                                                     |             | $T_A = +25^{\circ}C$                                   |                                                          | -0.1      |            | +0.1       | μΑ    |

| Valley Current-Limit Threshold                                            |             |                                                        | /ILIM_ = 0.5V                                            | 40        | 50         | 60         |       |

| (Adjustable)                                                              | VLIM_ (VAL) |                                                        | /ILIM_ = 1.00V<br>/ILIM_ = 2.10V                         | 87<br>184 | 100<br>210 | 113<br>236 | mV    |

| Ultrasonic Negative<br>Current-Limit Threshold                            | INEG(US)    | VILIVI 2.10V                                           |                                                          |           | 72         |            | mV    |

| Current-Limit Threshold<br>(Zero Crossing)                                | Vzx         | VAGND - VLX_, SKIP<br>VILIM = 1V                       | = V <sub>CC</sub> or GND,                                |           | 1.5        |            | mV    |

#### ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ , ON3 = ON5 =  $V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open, **TA = 0°C to +85°C**, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                                         | SYMBOL           | CONDITIONS                                                                | MIN | TYP | MAX     | UNITS |

|-------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|-----|-----|---------|-------|

| MAIN SMPS INPUTS AND OUT                                          | PUTS             | ·                                                                         |     |     |         |       |

|                                                                   |                  | High = SKIP                                                               | 2.3 |     | Vcc     |       |

| SKIP Threshold Voltage                                            | Vskip            | Mid = PWM                                                                 | 1.5 |     | 1.9     | V     |

|                                                                   |                  | Low = ultrasonic                                                          | 0   |     | 0.8     |       |

| SKIP Leakage Current                                              |                  | VSKIP = 0 or 5V, $T_A = +25^{\circ}C$                                     | -2  |     | +2      | μA    |

| ON_ Input Logic Levels                                            |                  | High (SMPS on)                                                            | 2.4 |     |         | v     |

| ON_ INPUT LOGIC Levels                                            |                  | Low (SMPS off)                                                            |     |     | 0.8     | v     |

| ON_ Leakage Current                                               |                  | $V_{ON3} = V_{ON5} = 0 \text{ or } 5V, T_A = +25^{\circ}C$                | -2  |     | +2      | μA    |

| OUT_ Discharge-Mode<br>On-Resistance                              | Rdschg           | ON_ = GND                                                                 | 7.5 | 20  | 50      | Ω     |

| SMPS GATE DRIVERS                                                 | <u> </u>         | · · · · · · · · · · · · · · · · · · ·                                     |     |     |         | 1     |

| DH3, DH5 Gate Driver                                              |                  | BST3 - LX3 and BST5 - LX5 forced to 5V;<br>high state                     |     | 1.6 | 3.8     |       |

| On-Resistance                                                     | Rdh3, Rdh5       | BST3 - LX3 and BST5 - LX5 forced to 5V; low state                         |     | 1.6 | 3.8     | Ω     |

| DL3, DL5 Gate Driver                                              |                  | DL3, DL5; high state                                                      |     | 1.5 | 1.5 3.5 |       |

| On-Resistance                                                     | Rdl3, Rdl5       | DL3, DL5; low state                                                       |     | 0.6 | 1.5     | Ω     |

| DH3, DH5 Gate Driver Source/<br>Sink Current                      | IDH              | DH3, DH5 forced to 2.5V,<br>BST3 - LX3 and BST5 - LX5 forced to 5V        |     | 2   |         | А     |

| DL3, DL5 Gate Driver<br>Source Current                            | IDL(SOURCE)      | DL3, DL5 forced to 2.5V                                                   |     | 1.7 |         | А     |

| DL3, DL5 Gate Driver<br>Sink Current                              | IDL(SINK)        | DL3, DL5 forced to 2.5V                                                   |     | 3.3 |         | А     |

| DHC Gate Driver On-                                               | Devie            | High state, IDHC = 10mA                                                   |     | 1.5 | 3       |       |

| Resistance                                                        | RDHC             | Low state, I <sub>DHC</sub> = -10mA                                       |     | 0.8 | 2.1     | Ω     |

| DLC Gate Driver                                                   | 5                | High state, IDLC = 10mA                                                   |     | 3   | 6       | 0     |

| On-Resistance                                                     | RDLC             | Low state, I <sub>DLC</sub> = -10mA                                       |     | 3   | 6       | Ω     |

| Internal BST_ Switch<br>On-Resistance                             | R <sub>BST</sub> | I <sub>BST_</sub> = 10mA, V <sub>DD</sub> = 5V                            |     | 5   |         | Ω     |

| BST_ Leakage Current                                              | IBST             | $V_{BST_}$ = 24V, OUT3 and OUT5 above<br>regulation threshold, TA = +25°C |     | 2   | 20      | μA    |

| CHARGER SMPS                                                      |                  | ·                                                                         |     |     |         |       |

| DHC Off-Time K Factor                                             |                  | V <sub>DCIN</sub> = 19V, V <sub>BATT</sub> = 10V                          | 30  | 35  | 40      | ns/V  |

| Sense Voltage for Minimum<br>Discontinuous Mode Ripple<br>Current |                  | VCSIP - VCSIN                                                             |     | 5   |         | mV    |

| Zero Crossing Comparator<br>Threshold                             |                  | VCSIP - VCSIN                                                             |     | 10  |         | mV    |

| Cycle-by-Cycle Current- Limit<br>Sense Voltage                    |                  | VCSIP - VCSIN                                                             | 120 | 125 | 130     | mV    |

MAX17085B

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                             | SYMBOL     | 00                                                    | NDITIONS                                                                           | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------|------------|-------------------------------------------------------|------------------------------------------------------------------------------------|-------|------|-------|-------|

| CHARGE-VOLTAGE REGULA                 |            |                                                       |                                                                                    |       |      | MIAA  | UNITS |

|                                       |            | CELLS = open, VC                                      | CTL = REF. 2 cells                                                                 | -0.5  |      | +0.5  |       |

| Battery-Regulation Voltage            | VBATT      | CELLS = GND, VC                                       |                                                                                    | -0.5  |      | +0.5  | %     |

| Accuracy                              |            |                                                       | CTL = REF, 4 cells                                                                 | -0.5  |      | +0.5  | -     |

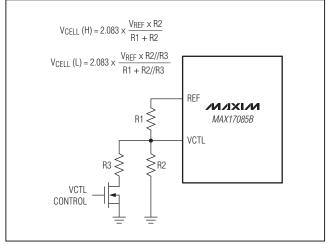

| VCTL Range                            |            | CELLS = open, 2 of                                    | CELLS = open, 2 cells                                                              |       |      | 3.5   | V     |

| VCTL Input Bias Current               |            | VCTL = GND or V                                       | $CTL = REF, T_A = +25^{\circ}C$                                                    | -1    |      | +1    | μA    |

| CELLS 3-Cell Threshold                |            |                                                       |                                                                                    |       |      | 0.8   | V     |

| CELLS 2-Cell Level                    |            | CELLS = open                                          |                                                                                    | 1.9   | 2.1  | 2.3   | V     |

| CELLS 4-Cell Threshold                |            |                                                       |                                                                                    | 2.8   |      |       | V     |

| CELLS Input Bias Current              |            | CELLS = GND or V<br>+25°C                             | VCELLS = 3.6V, T <sub>A</sub> =                                                    | -2    |      | +2    | μA    |

| CHARGE-CURRENT REGULA                 | TION       |                                                       |                                                                                    | •     |      |       |       |

| ISET Range                            |            | Charging current,                                     | analog setting                                                                     | 0     |      | REF   | V     |

| Full-Charge-Current Accuracy          |            | VBATT = 4V to                                         | $V_{\text{ISET}} = V_{\text{REF}}$ , or<br>$V_{\text{PATT}} = 4V$ to $PWM = 100\%$ |       | 100  | 103   |       |

| (CSIP to CSIN)                        | VCSI       | 16.8V VISET = 0.6 x VREF, or<br>PWM = 60%             |                                                                                    | 57.6  | 60.0 | 62.4  | mV    |

| Trickle Charge-Current<br>Accuracy    | VCSI       | VBATT = 4V to 16.8V, VISET = VREF/36 or<br>PWM = 2.7% |                                                                                    | 1.25  | 2.70 | 4.30  | mV    |

| Charge-Current Gain Error             |            |                                                       |                                                                                    | -1.5  |      | +1.5  | %     |

| Charge-Current Offset Error           |            | Based on VISET =<br>VREF                              | $V_{REF}$ and $V_{ISET} = 0.6 x$                                                   | -1.4  |      | +1.4  | mV    |

| CSIP/CSIN/BATT<br>Input-Voltage Range |            |                                                       |                                                                                    | 0     |      | 24    | V     |

| CSIP Leakage Current                  |            | VCSIP = VCSIN = 2                                     | 24V, T <sub>A</sub> = +25°C                                                        | -0.2  |      | +0.2  | μA    |

| CSIN Leakage Current                  |            | VCSIP = VCSIN = 2                                     | $24V, T_A = +25^{\circ}C$                                                          | 1     |      | 4     | μA    |

| ISET Power-Down Mode                  | VISET-SDN  | ISET falling                                          |                                                                                    | 20    | 26   | 32    | mV    |

| Threshold                             | VISET-SDIN | ISET rising                                           |                                                                                    | 32    | 38   | 46    |       |

| ISET Input Bias Current               |            | $V_{ISET} = V_{REF}/2$ an<br>T <sub>A</sub> = +25°C   | d VISET = VREF,                                                                    | -0.15 |      | +0.15 | μA    |

| ISET PWM Threshold                    |            | ISET rising<br>ISET falling                           |                                                                                    | 0.8   |      | 2.4   | V     |

| ISET Frequency                        | fISET      |                                                       |                                                                                    | 0.128 |      | 500   | kHz   |

| ISET Effective Resolution             |            | fISET = 100kHz                                        |                                                                                    |       | 8    |       | Bit   |

| INPUT SOURCE-CURRENT RE               | GULATION   |                                                       |                                                                                    |       |      |       |       |

| Input Source Current-Limit            | VCSS       | VCSSP - VCSSN                                         |                                                                                    | 58.5  | 60.0 | 61.5  | mV    |

| Threshold                             |            |                                                       |                                                                                    | -2.5  |      | +2.5  | %     |

| CSSP/CSSN<br>Input-Voltage Range      |            |                                                       |                                                                                    | 5     |      | 26    | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF,  $V_{CC} = 5V$ ,  $ON3 = ON5 = V_{CC}$ ,  $V_{DCIN} = V_{LXC} = V_{CSSP} = V_{CSSN} = 19V$ ,  $V_{BSTC} - V_{LXC} = 5V$ ,  $V_{BATT} = V_{CSIP} = V_{CSIN} = 12.6V$ ,  $V_{VCTL} = V_{ISET} = 1.8V$ , CELLS = open,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                    | SYMBOL            | CONDITIONS                                                              | MIN                        | TYP          | MAX           | UNITS  |

|----------------------------------------------|-------------------|-------------------------------------------------------------------------|----------------------------|--------------|---------------|--------|

| IINP Current-Sense Amplifier<br>Voltage Gain | GIINP             |                                                                         | 59.1                       | 60.0         | 60.9          | V/V    |

| IINP Output-Voltage Range                    |                   |                                                                         | 0                          |              | 4             | V      |

|                                              |                   | VCSSP - VCSSN = 60mV                                                    | -2                         |              | +2            |        |

| IINP Accuracy                                |                   | VCSSP - VCSSN = 40mV                                                    | -3                         |              | +3            | %      |

|                                              |                   | VCSSP - VCSSN = 20mV                                                    | -4                         |              | +4            |        |

| IINP Gain Error                              |                   | Measured at VCSSP - VCSSN = 60mV and<br>VCSSP - VCSSN = 20mV            | -1.25                      |              | +1.25         | %      |

| IINP Offset Error                            |                   | Measured at VCSSP - VCSSN = 60mV and VCSSP - VCSSN = 20mV               | -0.6                       |              | +0.6          | mV     |

| ADAPTER OVERCURRENT (A                       | COC) DETECT       | ION                                                                     |                            |              |               |        |

| ACOCP Threshold                              | VCSIN-OCP         | With respect to V <sub>CSSP</sub> _V <sub>CSSN</sub>                    |                            | 78           |               | mV     |

|                                              | *0000-00F         |                                                                         |                            | 130          |               | %      |

| ACOCP Blanking Time                          |                   |                                                                         |                            | 16           |               | ms     |

| ACOCP Waiting Time                           |                   | When ACOCP comparator is high and at the time the blanking time expires |                            | 0.6          |               | S      |

| ACIN, ACOK, AND ACOV                         |                   |                                                                         |                            |              |               |        |

| ACIN Rising Debounce                         |                   |                                                                         |                            | 44           |               | ms     |

| ACIN Falling Delay                           |                   |                                                                         |                            | 10           |               | μs     |

| ACIN Input Bias Current                      |                   | $T_{A} = +25^{\circ}C$                                                  | -1                         |              | +1            | μA     |

| ACOK Detect Threshold                        | Vacinok           | Measured at ACIN rising, hysteresis = 40mV                              | 1.47                       | 1.50         | 1.53          | V      |

| ACON Delect mieshold                         | VACINOR           | (typ)                                                                   | -2                         |              | +2            | %      |

| ACOV Detect Threshold                        | VACINOV           | Measured at ACIN rising, hysteresis = 40mV<br>(typ)                     | 2.05<br>-2.38              | 2.10         | 2.15<br>+2.38 | V<br>% |

| ACOK Sink Current                            |                   | $V\overline{ACOK} = 0.4V, VACIN = 1.7V$                                 | 1                          |              |               | mA     |

| ACOK Leakage Current                         |                   | VACOK = 5.5V, VACIN = 1.3V, TA = +25°C                                  |                            |              | 1             | μA     |

| ADAPTER PRESENT DETECT                       | ION               | ·                                                                       |                            |              |               | ·      |

| Adapter Absence<br>Detect Threshold          |                   | VDCIN - VBATT, VDCIN falling                                            | 0                          | 100          | 200           | mV     |

| Adapter Detect Threshold                     |                   | VDCIN - VBATT, VDCIN rising                                             | 300                        | 440          | 600           | mV     |

| CHARGE-PUMP MOSFET DRI                       | VER               |                                                                         |                            |              |               |        |

| PDSL Gate-Driver Source                      |                   | VPDSL - VDCIN = 3V, VDCIN = 19V                                         |                            | 60           |               |        |

| Current                                      | IPDSL-SRC         | VPDSL - VDCIN = 3V, VDCIN = 19V                                         |                            | 60           |               | μA     |

| PDSL Gate-Driver Output<br>Voltage High      | VPDSL-H           | V <sub>DCIN</sub> = 19V                                                 | V <sub>DCIN</sub><br>+ 5.3 | VDCIN<br>+ 8 |               | V      |

| PDSL SWITCH CONTROL                          |                   |                                                                         |                            |              |               |        |

| PDSL Turn-Off Resistance                     | R <sub>PDSL</sub> | Measured from PDSL to GND                                               |                            | 2.5          |               | kΩ     |

| BATTERY OVERVOLTAGE                          | 1                 |                                                                         |                            |              |               |        |

| DATIENT OVENVOLIAGE                          |                   |                                                                         |                            |              |               |        |

#### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                                        | SYMBOL      | CONDI                                                                                                                         | TIONS                                     | MIN   | TYP | MAX   | UNITS |

|--------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------|-----|-------|-------|

| INPUT SUPPLIES                                   | OTHEODE     | 001101                                                                                                                        |                                           |       |     |       |       |

| Adapter Present Quiescent                        |             | I <sub>DCIN</sub> + I <sub>CSSP</sub> +<br>I <sub>CSSN</sub> , ON3 = ON5 =                                                    | Charging enabled                          |       |     | 6     | - mA  |

| Current                                          |             | SKIP = VCC, VOUT3 = $3.5V$ , VOUT5 = $5.3V$                                                                                   | Charging disabled                         |       |     | 2.5   |       |

| Adapter Absent Quiescent                         |             | IDCIN + ICSSP +<br>ICSSN, ON3 = ON5 =                                                                                         | V <sub>ISET</sub> = 2.4V,<br>IINP ON      |       |     | 2.5   | - mA  |

| Current                                          |             | SKIP = V <sub>CC</sub> , V <sub>OUT3</sub> = 3.5V, V <sub>OUT5</sub> = 5.3V                                                   | ISET = GND                                |       |     | 2.2   |       |

| CSSN Input Current                               |             | VCSSP = VCSSN = 24V                                                                                                           | 1                                         |       |     | 2     | μΑ    |

| BATT + CSIP + CSIN + LXC Input                   |             | VBATT = 16.8V, adapte                                                                                                         | er absent                                 |       |     | 4     |       |

| Current                                          |             | VBATT = 2V to 19V, ac                                                                                                         | lapter present                            |       |     | 650   | - μΑ  |

| DCIN Input Current                               | IDCIN       | ON3 = ON5 = SKIP =<br>disabled; V <sub>OUT3</sub> = 3.5                                                                       | • •                                       |       |     | 0.2   | mA    |

| DCIN Standby Supply Current                      |             | V <sub>DCIN</sub> = 5V to 24V, Of                                                                                             | N3 = ON5 = GND                            |       |     | 300   | μA    |

| VCC Supply Current                               | ICC         | $ON3 = ON5 = SKIP = V_{CC}$ , charger<br>disabled; $V_{OUT3} = 3.5V$ , $V_{OUT5} = 5.3V$                                      |                                           |       |     | 1.5   | mA    |

| DCIN Input-Voltage Range                         |             | <b>Note:</b> LDO5 is NOT guaranteed to be regulation until DCIN is above 6V                                                   |                                           | 4.5   |     | 24    | V     |

| DCIN Undervoltage-Lockout                        |             | VDCIN falling                                                                                                                 |                                           | 6.9   |     |       | V     |

| Trip Point for Charger                           | VDCIN(UVLO) | V <sub>DCIN</sub> rising                                                                                                      |                                           |       |     | 7.9   | 7 V   |

| V <sub>CC</sub> UndervoltageLockout<br>Threshold | VCC(UVLO)   | Falling edge of V <sub>CC</sub> , F<br>this threshold                                                                         | WM disabled below                         | 3.8   |     | 4.3   | V     |

| LINEAR REGULATORS                                |             |                                                                                                                               |                                           |       |     |       |       |

|                                                  | VLDO5       | $V_{DCIN} = 6V \text{ to } 24V, Of OmA < I_{LDO5} < 100 \text{ m}$                                                            |                                           | 4.85  |     | 5.15  | - V   |

| LDO_ Output-Voltage Accuracy                     | VLDO3       | VLDO5 = 5V, ILDO5 = 0<br>50mA, ON3 = GND                                                                                      | 0A, 0mA < ILD03 <                         | 3.20  |     | 3.40  |       |

| LDO3 Short-Circuit Current                       |             | LDO3 = GND                                                                                                                    |                                           |       |     | 130   | mA    |

| LDO5 Short-Circuit Current                       |             | LDO5 = GND                                                                                                                    |                                           |       |     | 260   | mA    |

| REFERENCE                                        |             |                                                                                                                               |                                           |       |     |       |       |

| REF Output Voltage                               | Vref        | $I_{REF} = 50 \mu A$                                                                                                          |                                           | 2.08  |     | 2.12  | V     |

| MAIN SMPS                                        |             |                                                                                                                               |                                           |       |     |       |       |

| OUT5 Output-Voltage Accuracy                     | Vout5       | VIN = 6V to 28V, SKIP = REF                                                                                                   |                                           | 5.008 |     | 5.160 | V     |

| OUT3 Output-Voltage Accuracy                     | Vouts       | $V_{IN} = 6V$ to 28V, SKIP                                                                                                    |                                           | 3.25  |     | 3.35  | V     |

| DH5 On-Time                                      | ton5        | 1/ 101/                                                                                                                       | $R_{TON} = 549 k\Omega$<br>(300kHz + 10%) | 1073  |     | 1452  | - ns  |

|                                                  | UNU         | $\begin{array}{c} \text{(Note 3)} \\ \text{(Note 3)} \\ \text{(Note 3)} \\ \text{(800kHz + 10\%)} \\ \end{array} \right  402$ |                                           |       | 545 |       |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF, V<sub>CC</sub> = 5V, ON3 = ON5 = V<sub>CC</sub>, V<sub>DCIN</sub> = V<sub>LXC</sub> = V<sub>CSSP</sub> = V<sub>CSSN</sub> = 19V, V<sub>BSTC</sub> - V<sub>LXC</sub> = 5V, V<sub>BATT</sub> = V<sub>CSIP</sub> = V<sub>CSIN</sub> = 12.6V, V<sub>VCTL</sub> = V<sub>ISET</sub> = 1.8V, CELLS = open, **T<sub>A</sub>** = -40°C to +85°C, unless otherwise noted.) (Note 4)

| PARAMETER                                                                 | SYMBOL                              | CON                                                              | DITIONS                                    | MIN  | ТҮР | MAX  | UNITS |

|---------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------|--------------------------------------------|------|-----|------|-------|

| DH3 On-Time                                                               | tone                                | V <sub>IN</sub> = 12V,<br>V <sub>OUT3</sub> = 3.3V               | R <sub>TON</sub> = 549kΩ<br>(300kHz - 10%) | 866  |     | 1171 | ns    |

|                                                                           | ton3                                | (Note 3)                                                         | R <sub>TON</sub> = 202kΩ<br>(800kHz - 10%) | 325  |     | 439  |       |

| Minimum Off-Time                                                          | toff(MIN)                           | (Note 3)                                                         |                                            |      |     | 330  | ns    |

| Extended On-Time Blanking                                                 |                                     | Duty cycle > 50%; r                                              | not for production test                    |      |     | 360  | ns    |

| Ultrasonic Operating Frequency                                            | fsw(usonic)                         | SKIP = GND                                                       |                                            | 13   |     |      | kHz   |

| MAIN SMPS FAULT DETECTION                                                 |                                     |                                                                  |                                            |      |     |      |       |

| OUT_ Overvoltage Trip Threshold<br>(PGOOD Pulled Low Above this<br>Level) |                                     | With respect to erro                                             | r comparator threshold                     | 12   |     | 20   | %     |

| OUT_ Undervoltage Protection<br>Trip Threshold                            |                                     | With respect to erro                                             | r comparator threshold                     | 63   |     | 77   | %     |

| PGOOD Lower Trip Threshold                                                |                                     | With respect to erro falling edge, hystere                       | r comparator threshold,<br>esis = 15mV     | -350 |     | -150 | mV    |

| PGOOD Output Low Voltage                                                  |                                     | PGOOD low impedance, ON5 = ON3 =<br>GND, I <sub>SINK</sub> = 4mA |                                            |      |     | 0.4  | V     |

| Fault Reset Timer                                                         |                                     | Not for production t                                             | est                                        | 7    |     |      | ms    |

| MAIN SMPS CURRENT LIMIT                                                   |                                     |                                                                  |                                            |      |     |      |       |

| ILIM_ Adjustment Range                                                    |                                     |                                                                  |                                            | 0.2  |     | 2.1  | V     |

|                                                                           |                                     |                                                                  | $V_{ILIM} = 0.5V$                          | 40   |     | 60   |       |

| Valley Current-Limit Threshold (Adjustable)                               | VLIM_(VAL)                          | Vagnd - Vlx_                                                     | $V_{ILIM} = 1.00V$                         | 85   |     | 115  | mV    |

|                                                                           |                                     |                                                                  | $V_{ILIM} = 2.10V$                         | 174  |     | 246  |       |

| MAIN SMPS INPUTS AND OUTP                                                 | UTS                                 |                                                                  |                                            |      |     |      |       |

|                                                                           |                                     | High = SKIP                                                      |                                            | 2.3  |     | VCC  |       |

| SKIP Threshold Voltage                                                    | VSKIP                               | Mid = PWM                                                        |                                            | 1.5  |     | 1.9  | V     |

|                                                                           |                                     | Low = ultrasonic                                                 |                                            | 0    |     | 0.8  |       |

| SKIP Leakage Current                                                      |                                     | VSKIP = 0 or 5V, TA                                              | = +25°C                                    | -2   |     | +2   | μA    |

| ON_ Input Logic Levels                                                    |                                     | High (SMPS on)                                                   |                                            | 2.4  |     |      | - v   |

| ON_ INPUT LOGIC Levels                                                    |                                     | Low (SMPS off)                                                   |                                            |      |     | 0.8  | V     |

| SMPS GATE DRIVERS                                                         |                                     |                                                                  |                                            |      |     |      |       |

| DH3, DH5 Gate Driver On-                                                  | Rdh3,                               | BST3 - LX3 and BS <sup>-</sup><br>high state                     | T5 - LX5 forced to 5V;                     |      |     | 3.8  |       |

| Resistance                                                                | R <sub>DH5</sub>                    | BST3 - LX3 and BS <sup>-</sup><br>low state                      | BST3 - LX3 and BST5 - LX5 forced to 5V;    |      |     | 3.8  | Ω     |

| DL3, DL5 Gate-Driver On-                                                  |                                     | DL3, DL5; high state                                             | e                                          |      |     | 3.5  |       |

| Resistance                                                                | R <sub>DL3</sub> , R <sub>DL5</sub> | DL3, DL5; low state                                              |                                            |      |     | 1.5  | - Ω   |

|                                                                           | <b>D</b>                            | High state, IDHC =                                               |                                            |      |     | 3    |       |

| DHC Gate-Driver On-Resistance                                             | RDHC                                | Low state, IDHC = -                                              |                                            |      |     | 2.1  | Ω     |

#### $\mathbf{m}$ **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                     | SYMBOL    | CONDIT                                      | TIONS                                            | MIN   | ТҮР | MAX  | UNITS |  |

|-----------------------------------------------|-----------|---------------------------------------------|--------------------------------------------------|-------|-----|------|-------|--|

|                                               | _         | High state, I <sub>DLC</sub> = 10m          | ıΑ                                               |       |     | 6    |       |  |

| DLC Gate-Driver On-Resistance                 | RDLC      | Low state, IDLC = -10m                      | ıA                                               |       |     | 6    | Ω     |  |

| CHARGER SMPS                                  | 1         |                                             |                                                  |       |     |      | 1     |  |

| DHC Off-Time K Factor                         |           | VDCIN = 19V, VBATT =                        | 10V                                              | 30    |     | 40   | ns/V  |  |

| Cycle-by-Cycle Current-Limit<br>Sense Voltage |           | VCSIP - VCSIN                               |                                                  | 120   |     | 130  | mV    |  |

| CHARGE-VOLTAGE REGULATIO                      | )<br>N    | I                                           |                                                  |       |     |      | 1     |  |

|                                               |           | CELLS = open, VCTL =                        | = REF, 2 cells                                   | -0.5  |     | +0.5 |       |  |

| Battery-Regulation Voltage<br>Accuracy        | VBATT     | CELLS = GND, VCTL =                         | = REF, 3 cells                                   | -0.5  |     | +0.5 | %     |  |

|                                               |           | CELLS = LDO3, VCTL                          | = REF, 4 cells                                   | -0.5  |     | +0.5 | 1     |  |

| VCTL Range                                    |           |                                             |                                                  | 0     |     | 2.4  | V     |  |

| CELLS 3-Cell Threshold                        |           |                                             |                                                  |       |     | 0.8  | V     |  |

| CELLS 2-Cell Level                            |           | CELLS = open                                |                                                  | 1.9   |     | 2.3  | V     |  |

| CELLS 4-Cell Threshold                        |           |                                             |                                                  | 2.8   |     |      | V     |  |

| CHARGE-CURRENT REGULATION                     | N         | ·                                           | ······································           |       |     |      |       |  |

| ISET Range                                    |           | Charging current, anal                      | og setting                                       | 0.0   |     | REF  | V     |  |

| Full-Charge-Current Accuracy                  | Magi      | VBATT = 4V to 16.8V                         | $V_{ISET} = V_{REF}$ , or<br>PWM = 100%          | 97    |     | 103  | - mV  |  |

| (CSIP to CSIN)                                | VCSI      | VISET =                                     | $V_{ISET} = 0.6 \times V_{REF},$<br>or PWM = 60% | 57.6  |     | 62.4 | IIIV  |  |

| Trickle Charge-Current Accuracy               | Vcsi      | VBATT = 4V to 16.8V, V<br>PWM = 2.7%        | $V_{\rm ISET} = V_{\rm REF}/36$ or               | 1.2   |     | 4.3  | mV    |  |

| Charge-Current Gain Error                     |           |                                             |                                                  | -1.5  |     | +1.5 | %     |  |

| Charge-Current Offset Error                   |           | Based on VISET = VREF<br>VISET = 0.6 × VREF | = and                                            | -1.4  |     | +1.4 | mV    |  |

| CSIP/CSIN/BATT Input<br>Voltage Range         |           |                                             |                                                  | 0     |     | 24   | V     |  |

| ISET Power-Down Mode                          |           | ISET falling                                |                                                  | 20    |     | 32   |       |  |

| Threshold                                     | VISET-SDN | ISET rising                                 |                                                  | 32    |     | 46   | - mV  |  |

| ISET PWM Threshold                            |           | ISET rising                                 |                                                  |       |     | 2.4  | V     |  |

|                                               |           | ISET falling                                |                                                  | 0.8   |     |      | V     |  |

| ISET Frequency                                | fISET     |                                             |                                                  | 0.128 |     | 500  | kHz   |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, no load on LDO5, LDO3, OUT5, OUT3, and REF, V<sub>CC</sub> = 5V, ON3 = ON5 = V<sub>CC</sub>, V<sub>DCIN</sub> = V<sub>LXC</sub> = V<sub>CSSP</sub> = V<sub>CSSN</sub> = 19V, V<sub>BSTC</sub> - V<sub>LXC</sub> = 5V, V<sub>BATT</sub> = V<sub>CSIP</sub> = V<sub>CSIN</sub> = 12.6V, V<sub>VCTL</sub> = V<sub>ISET</sub> = 1.8V, CELLS = open, **T<sub>A</sub>** = -40°C to +85°C, unless otherwise noted.) (Note 4)

| PARAMETER                                    | SYMBOL  | CONDITIONS                                                                                                   | MIN            | TYP | MAX   | UNITS |  |

|----------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------|----------------|-----|-------|-------|--|

| INPUT SOURCE-CURRENT REG                     | ULATION | •                                                                                                            |                |     |       |       |  |

| Input Source-Current Limit                   |         |                                                                                                              | 58.5           |     | 61.5  | mV    |  |

| Threshold                                    | Vcss    | VCSSP - VCSSN                                                                                                | -2.5           |     | +2.5  | %     |  |

| CSSP/CSSN Input-Voltage Range                |         |                                                                                                              | 5              |     | 26    | V     |  |

| IINP Current-Sense Amplifier<br>Voltage Gain | GIINP   |                                                                                                              | 59.9           |     | 60.1  | V/V   |  |

| IINP Output-Voltage Range                    |         |                                                                                                              | 0              |     | 4     | V     |  |

|                                              |         | VCSSP - VCSSN = 60mV                                                                                         | -2             |     | +2    |       |  |

| IINP Accuracy                                |         | VCSSP - VCSSN = 40mV                                                                                         | -3             |     | +3    | %     |  |

|                                              |         | VCSSP - VCSSN = 20mV                                                                                         | -4             |     | +4    |       |  |

| IINP Gain Error                              |         | Measured at V <sub>CSSP</sub> - V <sub>CSSN</sub> = 60mV and<br>V <sub>CSSP</sub> - V <sub>CSSN</sub> = 20mV |                |     | +1.5  | %     |  |

| IINP Offset Error                            |         | Measured at V <sub>CSSP</sub> - V <sub>CSSN</sub> = 60mV and<br>V <sub>CSSP</sub> - V <sub>CSSN</sub> = 20mV | -0.65          |     | +0.65 | mV    |  |

| ACIN, ACOK, AND ACOV                         |         | · · · · · · · · · · · · · · · · · · ·                                                                        |                |     |       |       |  |

| ACOK Detect Threshold                        | Vacinok | Measured at ACIN rising, hysteresis = 40mV                                                                   | 1.47           |     | 1.53  | V     |  |

| ACOR Delect mileshold                        | VACINOR | (typ)                                                                                                        | -2             |     | +2    | %     |  |

| ACOV Detect Threshold                        | Vacinov | Measured at ACIN rising, hysteresis = 40mV                                                                   | 2.05           |     | 2.15  | V     |  |

|                                              | VACINOV | (typ)                                                                                                        | -2.38          |     | +2.38 | %     |  |

| ACOK Sink Current                            |         | $V\overline{ACOK} = 0.4V, VACIN = 1.7V$                                                                      | 1              |     |       | mA    |  |

| ADAPTER PRESENT DETECTIO                     | N       |                                                                                                              |                |     |       |       |  |

| Adapter Absence Detect<br>Threshold          |         | V <sub>DCIN</sub> - V <sub>BATT</sub> , V <sub>DCIN</sub> falling                                            | 0              |     | 200   | mV    |  |

| Adapter Detect Threshold                     |         | VDCIN - VBATT, VDCIN rising                                                                                  | 300            |     | 600   | mV    |  |

| CHARGE-PUMP MOSFET DRIVE                     | R       |                                                                                                              |                |     |       |       |  |

| PDSL Gate-Driver Output<br>Voltage High      | VPDSL_H | V <sub>DCIN</sub> = 19V                                                                                      | VDCIN +<br>5.3 |     |       | V     |  |

**Note 3:** On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with LX = PGND, V<sub>BST</sub> = 5V, and a 500pF capacitor from DH to LX to simulate external MOSFET gate capacitance. Actual in-circuit times may be different due to MOSFET switching speeds.

**Note 4:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and not production tested.

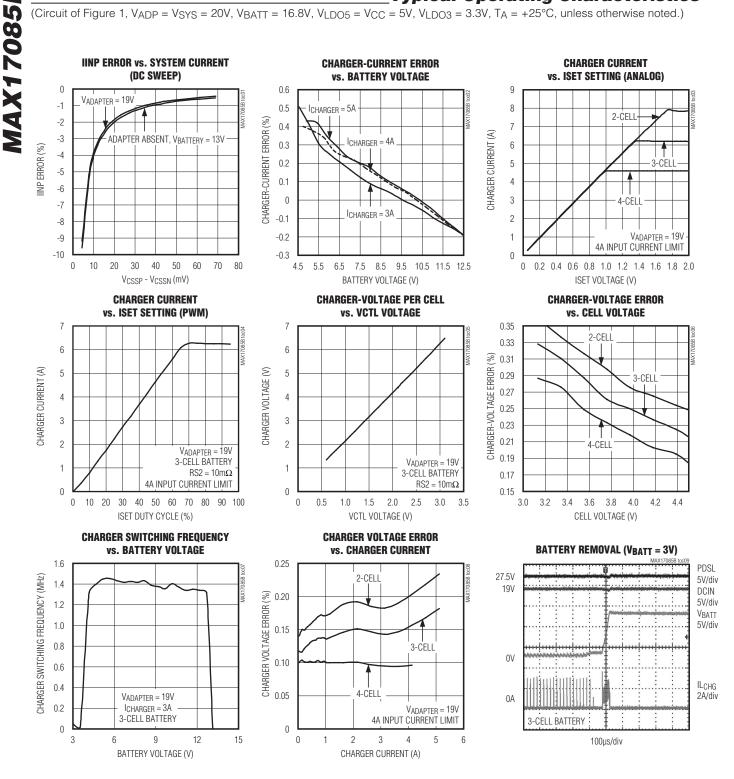

#### **Typical Operating Characteristics**

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

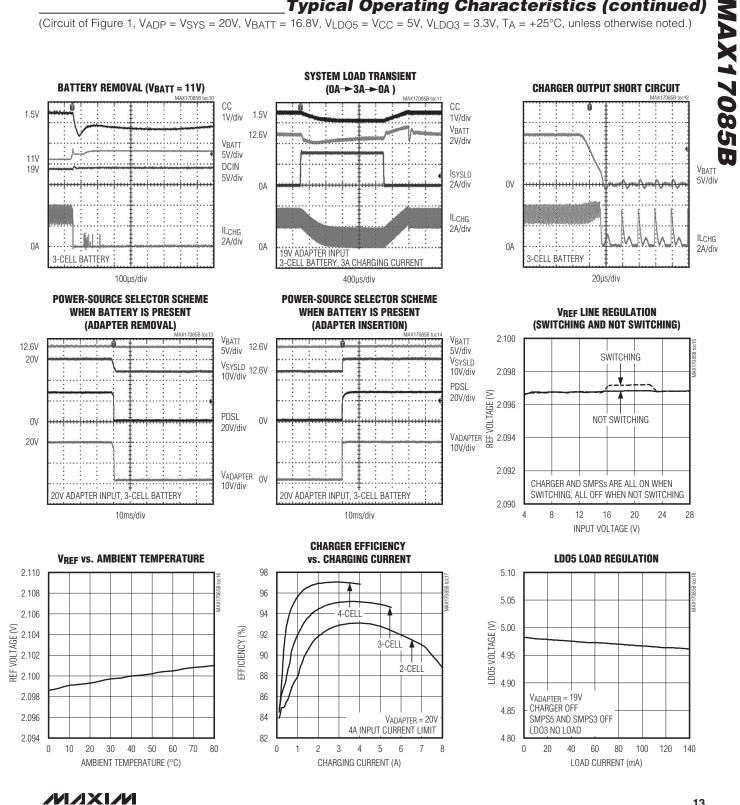

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

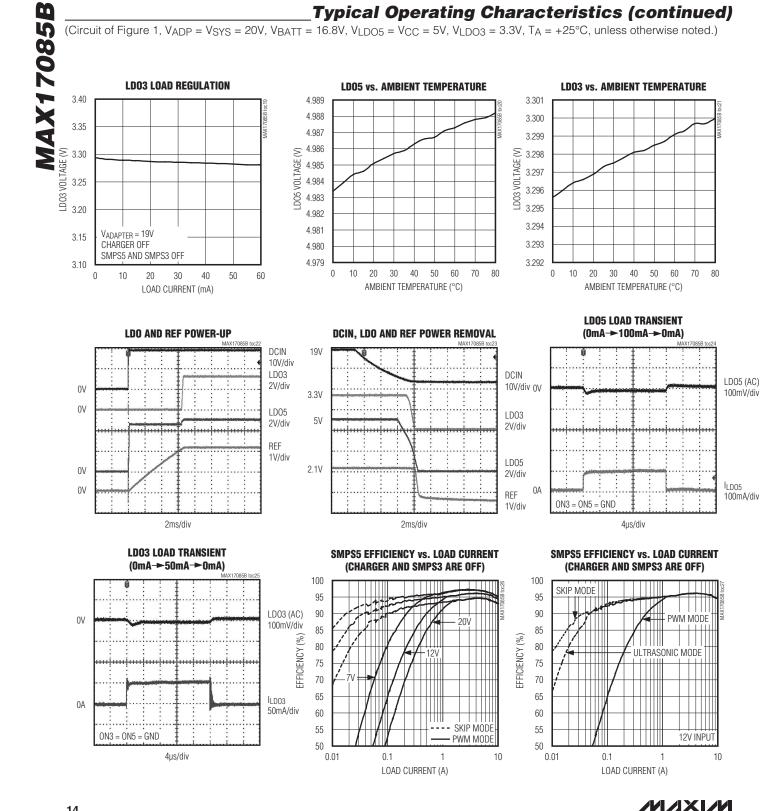

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

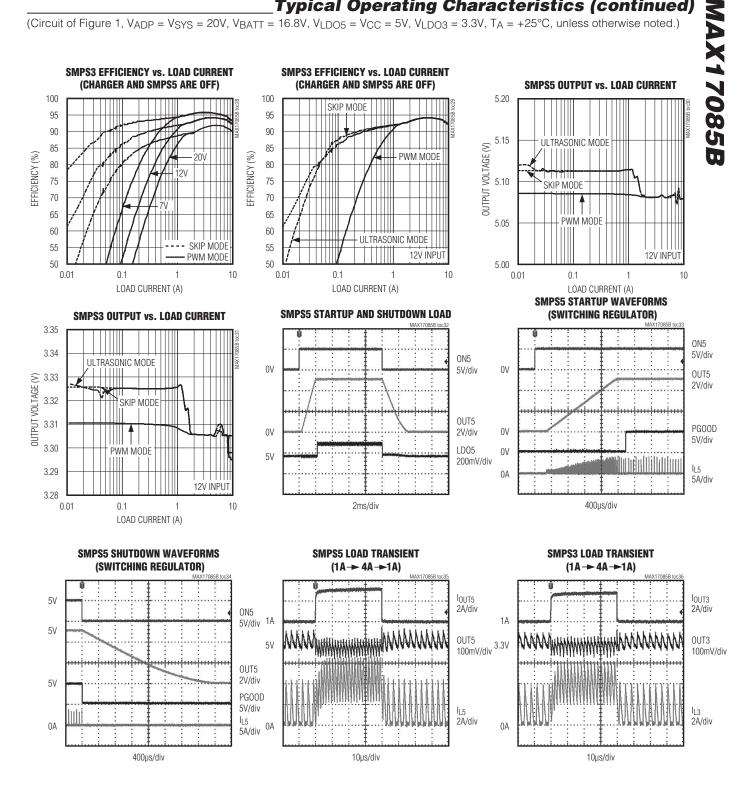

(Circuit of Figure 1, VADP = VSYS = 20V, VBATT = 16.8V, VLDO5 = VCC = 5V, VLDO3 = 3.3V, TA = +25°C, unless otherwise noted.)

#### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LX3   | Inductor Connection for SMPS3. Connect LX3 to the switched side of the inductor. LX3 is the lower supply rail for the DH3 high-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2   | BST3  | Boost Flying Capacitor Connection for SMPS3. Connect to an external capacitor as shown in Figure 1. An optional resistor in series with BST3 allows the DH3 turn-on current to be adjusted. A $4.7\Omega$ resistor is recommended to improve crosstalk between SMPSs.                                                                                                                                                                                                                                                                                                                                                             |

| 3   | DL3   | Low-Side Gate-Driver Output for SMPS3. DL3 swings from PGND to LDO5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |