Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

#### **General Description**

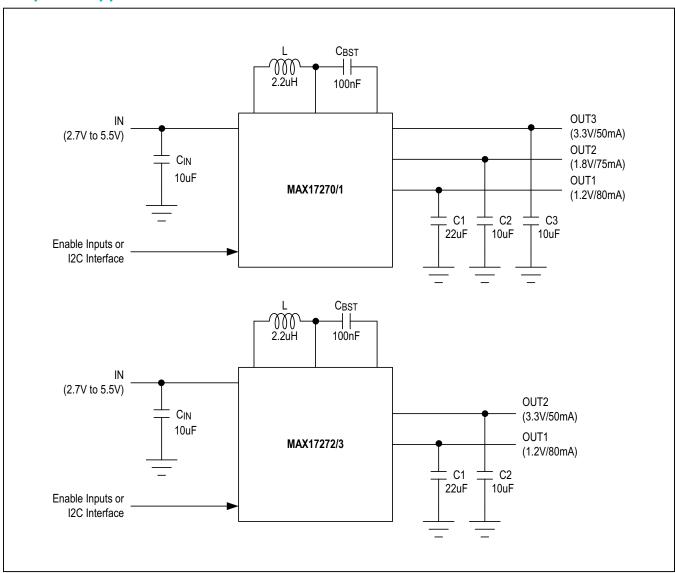

The MAX17270/MAX17271 are 3-output switching regulators designed for applications requiring efficient regulation of multiple supplies in a very small space, such as wearable electronic devices.

The parts use a buck-boost architecture that regulates three outputs using a single, small 2.2µH inductor at efficiencies up to 85%. This results in smaller board space while delivering better total system efficiency than equivalent power solutions using one buck and linear regulators.

The supply current is  $0.85\mu A$  when only one output is enabled, plus  $0.2\mu A$  for each additional output enabled.

This SIMO (Single-Input Multiple Output) regulator utilizes the entire battery voltage range due to its ability to create output voltages that are above, below, or equal to the input voltage. Peak inductor current for each output is programmable to optimize the balance between efficiency, output ripple, EMI, PCB design, and load capability.

Two versions are available. The MAX17270 has 3 enable inputs and 3 output voltage programming inputs. The MAX17271 includes an I<sup>2</sup>C interface with interrupt, a push-button turn on/off, and a power-good indication. The MAX17272/MAX17273 are 2-output versions of MAX17270/MAX17271, respectively.

All versions are offered in either a 4 x 4, 0.4mm wafer-level package (WLP) or a 16-pin TQFN package.

#### **Applications**

- Bluetooth Headsets

- Fitness Bands

- Watches

#### **Benefits and Features**

- 3-Output/2-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

- 2.7V to 5.5V Input Voltage Range

- Low-Power and Long Battery Life

- 1.3µA Operating Current (3 SIMO Channels)

- 330nA Shutdown Current

- · 85% Efficiency at 3.3V Output

- Flexible and Configurable

- I<sup>2</sup>C Compatible Interface (MAX17271/MAX17273)

- Programmable Output Voltage: 0.8V to 5.175V

- · Programmable Peak Current Limit

- Robust

- Soft-Start

- · Overload Protection

- Thermal Protection

- Small Size

- 1.77mm x 1.77mm x 0.50mm 0.4mm-Pitch WLP Package

- 3mm x 3mm x 0.75mm TQFN Package

- Small Total Solution Size

Ordering Information appears at end of data sheet.

## **Simplified Application Circuit**

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

### **Absolute Maximum Ratings**

| V <sub>PWR</sub> , OUT1, OUT2, OUT3, V <sub>IO</sub> to GND              | 0.3V to +6V    |

|--------------------------------------------------------------------------|----------------|

| Continuous Power Dissipation (WLP)                                       |                |

| $(T_A = 70^{\circ}C, derate 17.2 \text{mW/}^{\circ}C above 70^{\circ}C)$ | C.)1376mW      |

| Continuous Power Dissipation (TQFN)                                      |                |

| (T <sub>A</sub> = 70°C, derate 20.8mW/°C above 70°C                      | C.)1666.7mW    |

| Operating Temperature Range                                              | 40°C to +85°C  |

| Junction Temperature                                                     | +150°C         |

| Storage Temperature Range                                                | 60°C to +150°C |

| Soldering Temperature (reflow)                                           | +260°C         |

|                                                                          |                |

| EN1, EN2, EN3, IRQB, ON, RSTB, RSEL1,    | RSEL2,                            |

|------------------------------------------|-----------------------------------|

| RSEL3 to GND0                            | $0.3V \text{ to } V_{SUP} + 0.3V$ |

| SCL, SDA to GND                          | 0.3V to V <sub>VIO</sub> + 0.3V   |

| V <sub>SUP</sub> to V <sub>PWR</sub>     | 0.3V to +0.3V                     |

| PGND to GND                              |                                   |

| OUT1, OUT2, OUT3 Short-Circuit Duration. | Continuous                        |

| LXA Continuous Current (Note 1)          | 1.2A <sub>RMS</sub>               |

| LXB Continuous Current (Note 2)          | 1.2A <sub>RMS</sub>               |

| BST to LXB                               |                                   |

| BST to V <sub>PWR</sub>                  | 0.3V to 6V                        |

| Lead Temperature (soldering, 10 seconds) | 300°C                             |

- **Note 1:** LXA has internal clamping diodes to PGND and V<sub>PWR</sub>. It is normal for these diodes to briefly conduct during switching events. Avoid steady-state conduction of these diodes.

- Note 2: Do not externally bias LXB. LXB has an internal low-side clamping diode to PGND, and an internal high-side clamping diode that dynamically shifts to the selected SIMO output. It is normal for these internal clamping diodes to briefly conduct during switching events. When the SIMO regulator is disabled, the LXB to PGND absolute maximum voltage is -0.3V to OUT1 + 0.3V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **TOFN**

| · <del></del>                          |         |  |  |  |  |

|----------------------------------------|---------|--|--|--|--|

| PACKAGE CODE                           | T1633+5 |  |  |  |  |

| Outline Number                         | 21-0136 |  |  |  |  |

| Land Pattern Number                    | 90-0032 |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD:  |         |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 48°C/W  |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 10°C/W  |  |  |  |  |

#### **WLP**

| PACKAGE CODE                           | N161A1+1                       |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Outline Number                         | <u>21-100190</u>               |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD:  |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 57.93                          |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

#### **Electrical Characteristics**

$(V_{SUP} = V_{PWR} = 3.7V, T_J = -40^{\circ}C \text{ to } 85^{\circ}C, \underline{Typical Application Circuits}, \text{ typical values are at } T_J = 25^{\circ}C \text{ unless otherwise specified. Limits over the specified operating temperature and supply voltage range are guaranteed by design and characterization, and production tested at room temperature only.)}$

| PARAMETER                                      | SYMBOL                 | CONDI                                               | CONDITIONS                                                          |      | TYP  | MAX   | UNITS     |  |

|------------------------------------------------|------------------------|-----------------------------------------------------|---------------------------------------------------------------------|------|------|-------|-----------|--|

| Input Voltage Range                            | V <sub>IN</sub>        |                                                     |                                                                     | 2.7  |      | 5.5   | V         |  |

| V Threshold                                    | V                      | Outputs are                                         | Rising                                                              |      | 2.55 | 2.7   | V         |  |

| V <sub>IN UVLO</sub> Threshold                 | V <sub>IN_UVLO</sub>   | functional                                          | Falling                                                             | 2.2  | 2.45 |       | v         |  |

| V <sub>IN OVLO</sub> Threshold                 | V <sub>IN_OVLO</sub>   | Rising                                              |                                                                     | 5.70 | 5.85 | 6.00  | V         |  |

| OUT Voltage Range (MAX17270/<br>MAX17272 Only) | V <sub>OUT_RANGE</sub> | OUT1, OUT2, OUT                                     | 3                                                                   | 0.8  |      | 4.6   | V         |  |

| OUT Voltage Range (MAX17271/<br>MAX17273 Only) | V <sub>OUT_RANGE</sub> | OUT1, OUT2, OUT                                     | 3                                                                   | 0.8  |      | 5.175 | V         |  |

|                                                |                        | All outputs disabled (MAX17271/MAX17                |                                                                     |      | 0.33 |       |           |  |

| land Orania Orania                             | la a                   | 1 output enabled, F<br>SDA, IRQB pins op            |                                                                     |      | 0.85 | 1.8   |           |  |

| Input Supply Current                           | Icc                    | 2 outputs enabled,<br>SDA, IRQB pins op             |                                                                     |      | 1.05 | 2.4   | μΑ        |  |

|                                                |                        |                                                     | 3 outputs enabled, RSTB, V <sub>IO</sub> , SCL, SDA, IRQB pins open |      | 1.3  | 3.0   |           |  |

| OLIT Supply Compant                            |                        | Outputs disabled, T                                 | A = 25°C                                                            |      | 0.01 | 1.0   | μA        |  |

| OUT Supply Current                             | lout                   | Outputs enabled, no switching                       |                                                                     |      | 0.1  |       | μA        |  |

| OUT Overregulation Threshold                   | V <sub>OV</sub>        | T <sub>A</sub> = 25 °C                              |                                                                     |      | 2.5  | 5     | %         |  |

| OUT Voltage Accuracy                           |                        | Falling switch thres 2.7V < V <sub>SUP</sub> < 5.5\ | Falling switch threshold,<br>2.7V < V <sub>SUP</sub> < 5.5V         |      |      | +2    | %         |  |

| OUT Load Regulation                            |                        | $V_{OUT}$ = 3.3V, $I_{OUT}$                         | = 0.1mA to 100mA                                                    |      | 0.5  |       | %         |  |

| OUT Line Regulation                            |                        | V <sub>IN</sub> from 2.7V to 5.                     | 5V                                                                  |      | 0.1  |       | %         |  |

| Maximum On Time                                | t <sub>ON</sub>        | LXA switched high                                   |                                                                     | 2.2  | 4.4  | 8.8   | μs        |  |

| Maximum Off Time                               | t <sub>OFF</sub>       | LXB switched high                                   |                                                                     | 2.2  | 4.4  | 8.8   | μs        |  |

|                                                | Б                      | l ligh aida                                         | V <sub>IN</sub> = 3.7V                                              |      | 70   | 140   |           |  |

| LXA On Resistance                              | R <sub>AH</sub>        | High-side                                           | V <sub>IN</sub> = 2.7V                                              |      | 90   | 180   |           |  |

| LXA On Resistance                              | В                      | Low-side                                            | V <sub>IN</sub> = 3.7V                                              |      | 50   | 100   | - mΩ<br>- |  |

|                                                | R <sub>AL</sub>        | Low-side                                            | V <sub>IN</sub> = 2.7V                                              |      | 65   | 130   |           |  |

|                                                | D.                     | High-side, any                                      | V <sub>IN</sub> = 3.7V                                              |      | 55   | 110   |           |  |

| LXB On Resistance                              | R <sub>BH</sub>        | output                                              | V <sub>IN</sub> = 2.7V                                              |      | 75   | 150   | - mΩ      |  |

|                                                | D- :                   | Low side                                            | V <sub>IN</sub> = 3.7V                                              |      | 55   | 110   |           |  |

|                                                | R <sub>BL</sub>        | Low-side                                            | V <sub>IN</sub> = 2.7V                                              |      | 90   | 180   |           |  |

| LX Peak Current Limit                          | l                      | At LXB, T <sub>A</sub> = 25°C                       | RSELx ≤ 56.2kΩ                                                      | -5%  | +1.1 | +5%   |           |  |

| (MAX17270/MAX17272 only)                       | I <sub>LIM</sub>       | At LXB, T <sub>A</sub> = 25°C                       | RSELx ≥ 66.5 kΩ                                                     | -15% | +0.6 | +15%  | A         |  |

| LX Peak Current Limit                          | 1, 154                 | At LXB, T <sub>A</sub> = 25°C                       | ILIM[1:0] = 0b00                                                    | -5%  | +1.1 | +5%   | Α         |  |

| (MAX17271/MAX17273 Only)                       | I <sub>LIM</sub>       | / (L/L), 1A - 20 C                                  | ILIM[1:0] = 0b01                                                    | -15% | +0.8 | +15%  |           |  |

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

### **Electrical Characteristics (continued)**

$(V_{SUP} = V_{PWR} = 3.7V, T_J = -40^{\circ}C \text{ to } 85^{\circ}C, Typical Application Circuits}, typical values are at <math>T_J = 25^{\circ}C$  unless otherwise specified. Limits over the specified operating temperature and supply voltage range are guaranteed by design and characterization, and production tested at room temperature only.)

| PARAMETER                                                        | SYMBOL                              | CONDI                                                                                                                                                           | TIONS                                | MIN                       | TYP   | MAX                       | UNITS |  |

|------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|-------|---------------------------|-------|--|

| LX Peak Current Limit                                            |                                     | ALLYD T OF                                                                                                                                                      | ILIM[1:0] = 0b10                     | -15%                      | +0.6  | +15%                      |       |  |

| (MAX17271/MAX17273 only)                                         | ILIM                                | At LXB, $T_A = 25^{\circ}C$                                                                                                                                     | ILIM[1:0] = 0b11                     | -15%                      | +0.4  | +15%                      | Α     |  |

| LX Current Limit Delay                                           |                                     | Design Estimate                                                                                                                                                 |                                      |                           | 10    |                           | ns    |  |

| BST On Resistance                                                | R <sub>BST</sub>                    | BST to V <sub>PWR</sub>                                                                                                                                         |                                      |                           | 36    | 77                        | Ω     |  |

| BST Leakage Current                                              |                                     | BST = 11V, LXB = 5                                                                                                                                              | 5.5V                                 |                           | 0.01  | 1.0                       | μA    |  |

| Required Select Resistor<br>Accuracy (MAX17270/MAX17272<br>Only) | R <sub>SEL_TOL</sub>                | Use the nearest ±1'                                                                                                                                             |                                      | -1                        |       | +1                        | %     |  |

| Select Resistor Detection Time<br>(MAX17270/MAX17272 Only)       | <sup>t</sup> RSEL                   | V <sub>SUP</sub> = 2.7V, C <sub>RSE</sub>                                                                                                                       | :L < 2pF                             |                           | 600   |                           | μs    |  |

| Soft-Start Enable Delay<br>(MAX17270/MAX17272 Only)              | t <sub>DLY_</sub> ss                | EN rising edge to rising edge of 1st LXA pulse, provided that RSEL values have been determined (t <sub>RSEL</sub> has elapsed after applying V <sub>SUP</sub> ) |                                      |                           | 100   |                           | μs    |  |

| Soft-Start Ramp Rate                                             | dV <sub>OUT</sub> /dt <sub>SS</sub> | Measured from 20% ramp                                                                                                                                          | Measured from 20% to 80% of OUT ramp |                           | 1.2   |                           | mV/μs |  |

| Overtemperature Threehold                                        |                                     | T <sub>J</sub> Rising T <sub>J</sub> Falling                                                                                                                    |                                      |                           | 165   |                           | °C    |  |

| Overtemperature Threshold                                        |                                     |                                                                                                                                                                 |                                      |                           | 150   |                           |       |  |

| LOGIC INPUTS (EN1, EN2, EN3,                                     | ON)                                 |                                                                                                                                                                 |                                      |                           |       |                           |       |  |

| Input Current                                                    | h                                   | Input voltage 0V                                                                                                                                                | T <sub>A</sub> = 25°C                |                           | 0.001 | 1                         |       |  |

| input Current                                                    | I <sub>LGC_IN</sub>                 | to 5.5V $T_A = 85^{\circ}C$                                                                                                                                     |                                      | 0.01                      |       | μA                        |       |  |

| EN Input Threshold, High                                         | V <sub>IH</sub>                     | Voltage threshold, r                                                                                                                                            | rising                               | 0.7 x<br>V <sub>SUP</sub> |       |                           | V     |  |

| EN Input Threshold, Low                                          | V <sub>IL</sub>                     | Voltage threshold, f                                                                                                                                            | alling                               |                           |       | 0.3 x<br>V <sub>SUP</sub> | V     |  |

| ON Input Threshold, High                                         | V <sub>IH</sub>                     | Voltage threshold, r                                                                                                                                            | ising                                | 1.4                       |       |                           | V     |  |

| ON Input Threshold, Low                                          | V <sub>IL</sub>                     | Voltage threshold, f                                                                                                                                            | alling                               |                           |       | 0.4                       | V     |  |

| ON Debounce Time                                                 | t <sub>ON_DB</sub>                  | From ON high to sequencer on                                                                                                                                    |                                      |                           | 10    |                           | ms    |  |

| ON Reset Time                                                    | ton_rst                             | From ON high to sequencer off                                                                                                                                   |                                      |                           | 13    |                           | s     |  |

| ON Auto Power Enable                                             |                                     | SWR bit set to 1, following reset                                                                                                                               |                                      |                           | 102   |                           | ms    |  |

| LOGIC OUTPUTS (IRQB, RSTB)                                       |                                     |                                                                                                                                                                 |                                      |                           |       |                           |       |  |

| Output Voltage Low                                               | V <sub>OL</sub>                     | Asserted and sinking                                                                                                                                            | ng 1mA                               |                           |       | 0.1                       | V     |  |

| Lookaga Current                                                  | l                                   | T <sub>A</sub> = 25°C                                                                                                                                           |                                      |                           | 0.001 |                           |       |  |

| Leakage Current                                                  | I <sub>LKG</sub>                    | De-asserted, 5.5V                                                                                                                                               | T <sub>A</sub> = 85°C                |                           | 0.01  | 1                         | μA    |  |

**Note 1:** Typical values align with bench observations using the stated conditions. See the <u>Typical Operating Characteristics</u>. Minimum and maximum values are tested in production with DC currents.

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

## **Electrical Characteristics - I<sup>2</sup>C**

$(V_{VPWR} = V_{VSUP} = 3.7V, V_{IO} = 1.8V, limits are 100\% production tested at T_J = +25°C, limits over the operating temperature range <math>(T_J = -40°C \text{ to } +85°C)$  are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                      | SYMBOL              | CONDITIONS                                                                | MIN                      | TYP                       | MAX                      | UNITS |

|------------------------------------------------|---------------------|---------------------------------------------------------------------------|--------------------------|---------------------------|--------------------------|-------|

| POWER SUPPLY                                   |                     |                                                                           |                          |                           |                          |       |

| V <sub>IO</sub> Voltage Range                  | V <sub>IO</sub>     | V <sub>IO</sub> ≤ V <sub>SUP</sub>                                        | 1.7                      | 1.8                       | 3.6                      | V     |

| V <sub>IO</sub> Bias Current                   |                     | $V_{IO} = 3.6V$ , $V_{SDA} = V_{SCL} = 0V$ or 3.6V, $T_A = +25$ °C        | -1                       | 0                         | +1                       | μA    |

|                                                |                     | V <sub>IO</sub> = 1.7V, V <sub>SDA</sub> = V <sub>SCL</sub> = 0V or 1.7V  |                          | 0                         | +1                       |       |

| SDA AND SCL I/O STAGE                          |                     |                                                                           |                          |                           |                          |       |

| SCL, SDA Input High Voltage                    | V <sub>IH</sub>     | V <sub>IO</sub> = 1.7V to 3.6V                                            | 0.7 x<br>V <sub>IO</sub> |                           |                          | V     |

| SCL, SDA Input Low Voltage                     | $V_{IL}$            | V <sub>IO</sub> = 1.7V to 3.6V                                            |                          |                           | 0.3 x<br>V <sub>IO</sub> | V     |

| SCL, SDA Input Hysteresis                      | V <sub>HYS</sub>    |                                                                           |                          | 0.05 x<br>V <sub>IO</sub> |                          | V     |

| SCL, SDA Input Leakage<br>Current              | l <sub>l</sub>      | $V_{IO}$ = 3.6V, $V_{SCL}$ = $V_{SDA}$ = 0V and 3.6V                      | -10                      |                           | +10                      | μА    |

| SDA Output Low Voltage                         | $V_{OL}$            | Sinking 20mA                                                              |                          |                           | 0.4                      | V     |

| SCL, SDA Pin Capacitance                       | C <sub>I</sub>      |                                                                           |                          | 10                        |                          | pF    |

| I <sup>2</sup> C COMPATIBLE INTERFAC           | E TIMING (ST        | ANDARD, FAST AND FAST MODE PLUS) (                                        | Note 2)                  |                           |                          |       |

| Clock Frequency                                | f <sub>SCL</sub>    |                                                                           | 0                        |                           | 1000                     | kHz   |

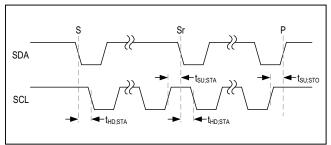

| Hold Time (REPEATED)<br>START Condition        | thd_sta             |                                                                           | 0.26                     |                           |                          | μs    |

| SCL Low Period                                 | $t_{LOW}$           |                                                                           | 0.5                      |                           |                          | μs    |

| SCL High Period                                | t <sub>HIGH</sub>   |                                                                           | 0.26                     |                           |                          | μs    |

| Setup Time (REPEATED)<br>START Condition       | tsu_sta             |                                                                           | 0.26                     |                           |                          | μs    |

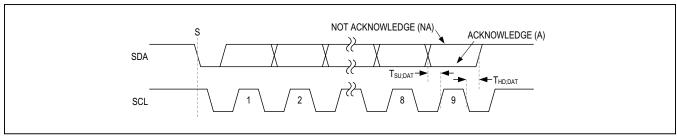

| Data Hold Time                                 | t <sub>HD_DAT</sub> |                                                                           | 0                        |                           |                          | μs    |

| Data Setup Time                                | t <sub>SU_DAT</sub> |                                                                           | 50                       |                           |                          | ns    |

| Setup Time for STOP<br>Condition               | tsu_sto             |                                                                           | 0.26                     |                           |                          | μs    |

| Bus Free Time between STOP and START Condition | t <sub>BUF</sub>    |                                                                           | 0.5                      |                           |                          | μs    |

| Pulse Width of Suppressed Spikes               | t <sub>SP</sub>     | Maximum pulse width of spikes that must be suppressed by the input filter |                          | 50                        |                          | ns    |

Note 1: Limits are 100% production tested at  $T_A$  = +25°C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control methods.

Note 2: Design guidance only. Not production tested.

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

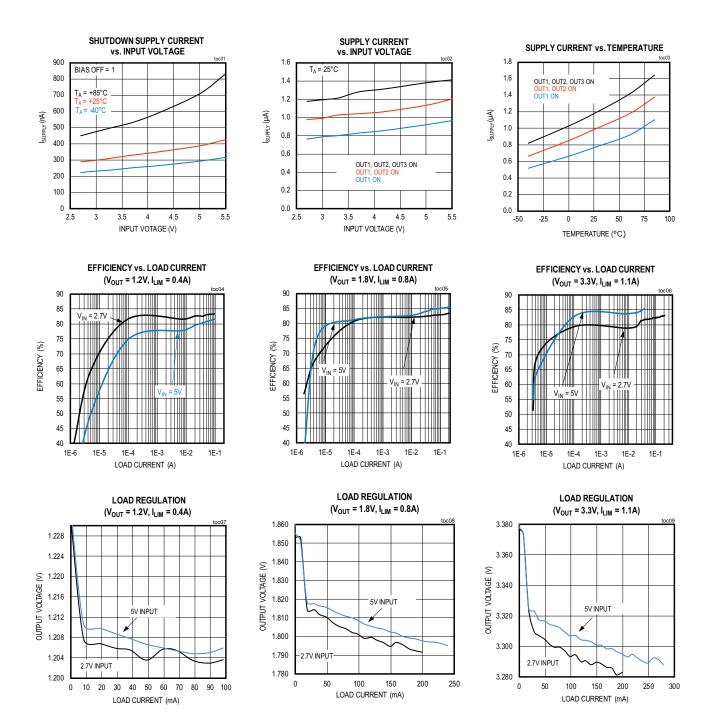

### **Typical Operating Characteristics**

$V_{IN} = 2.7 \text{V}, \text{OUT1} = 1.2 \text{V}, \\ I_{LIM} 1 = 0.4 \text{A}, \text{OUT2} = 1.8 \text{V}, \\ I_{LIM} 2 = 0.8 \text{A}, \text{OUT3} = 3.3 \text{V}, \\ I_{LIM} 3 = 1.1 \text{A}, \\ L1 = 2.2 \mu \text{H} \text{ (Coilcraft XFL4020-222ME)}, \\ \text{COUT1} = \text{COUT2} = \text{COUT3} = 22 \mu \text{F} \text{ (TDK C1608X5R1A226M080AC)}$

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

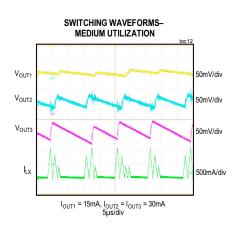

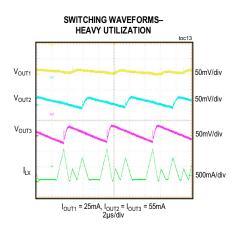

### **Typical Operating Characteristics (continued)**

$V_{IN} = 2.7 \text{V} \text{ , OUT1} = 1.2 \text{V} \text{ , I}_{LIM} \\ 1 = 0.4 \text{A} \text{ , OUT2} = 1.8 \text{V} \text{ , I}_{LIM} \\ 2 = 0.8 \text{A} \text{ , OUT3} = 3.3 \text{V} \text{ , I}_{LIM} \\ 3 = 1.1 \text{A} \text{ , L1} = 2.2 \mu \text{H} \text{ (Coilcraft XFL4020-222ME)} \text{ , COUT1} = \text{COUT2} = \text{COUT3} = 22 \mu \text{F} \text{ (TDK C1608X5R1A226M080AC)}$

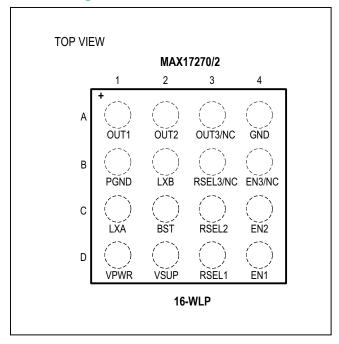

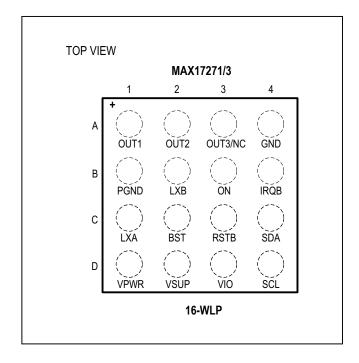

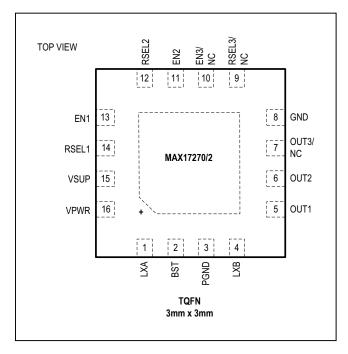

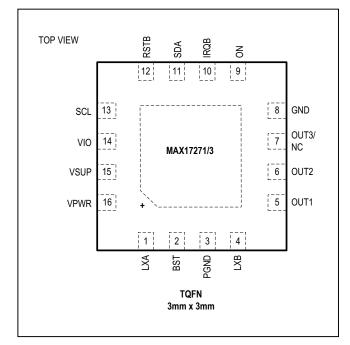

## **Pin Configurations**

# nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

## **Pin Description**

| PIN               |                   |                    |                    |                                              |                                                                                                                                                                                         |

|-------------------|-------------------|--------------------|--------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX17270/2<br>WLP | MAX17271/3<br>WLP | MAX17270/2<br>TQFN | MAX17271/3<br>TQFN | NAME                                         | FUNCTION                                                                                                                                                                                |

| A1                | A1                | 5                  | 5                  | OUT1                                         | Regulator Output 1. Connect a 10μF (min) capacitor from this pin to ground.                                                                                                             |

| B1                | B1                | 3                  | 3                  | PGND                                         | Buck-Boost Power Ground. Connect to the ground plane through a low impedance.                                                                                                           |

| C1                | C1                | 1                  | 1                  | LXA                                          | Buck-Boost Input-Side Inductor Connection. Connect a 2.2µH inductor between LXA and LXB.                                                                                                |

| D1                | D1                | 16                 | 16                 | VPWR                                         | Buck-Boost Input Power Supply Pin. Connect a 10μF(min) capacitor from this pin to ground.                                                                                               |

| A2                | A2                | 6                  | 6                  | OUT2                                         | Regulator Output 2. Connect a $10\mu F(min)$ capacitor from this pin to ground.                                                                                                         |

| B2                | B2                | 4                  | 4                  | LXB                                          | Buck-Boost Output-Side Inductor Connection. Connect a 2.2µH inductor between LXA and LXB.                                                                                               |

| C2                | C2                | 2                  | 2                  | BST                                          | Bootstrap pin for high-side output FET drivers. Connect a 3.3nF capacitor between BST and LXB.                                                                                          |

| D2                | D2                | 15                 | 15                 | VSUP                                         | Analog Input Supply. Connect to VPWR.                                                                                                                                                   |

| A3                | A3                | 7                  | 7                  | OUT3 (NC for<br>MAX17272<br>and<br>MAX17273) | Regulator Output 3. Connect a 10µF (min) capacitor from this pin to ground. Unused pin for MAX17272 and MAX17273.                                                                       |

| В3                | _                 | 9                  | _                  | RSEL3<br>(NC for<br>MAX17272)                | Select Resistor Pin 3. Connect a resistor from this pin to GND, using the value to configure OUT3. Unused pin for the MAX17272.                                                         |

| _                 | В3                | _                  | 9                  | ON                                           | Push-Button Controller Input. Connect a $100k\Omega$ resistor from ON to GND and momentary switch between ON and TTL Level Supply. Used to initiate power-up and power-down sequencing. |

| C3                | ı                 | 12                 | _                  | RSEL2                                        | Select Resistor Pin 2. Connect a resistor from this pin to GND, using the value to configure OUT2.                                                                                      |

| _                 | C3                | _                  | 12                 | RSTB                                         | Open-Drain Output to Indicate All Outputs are Active. Connect a pullup resistor between this pin and an external supply. Goes to logic-high only when all outputs are active.           |

| D3                | _                 | 14                 | _                  | RSEL1                                        | Select Resistor Pin 1. Connect a resistor from this pin to GND, using the value to configure OUT1.                                                                                      |

| _                 | D3                | _                  | 14                 | VIO                                          | Supply Voltage for the $I^2C$ Inputs. Determines the SDA and SCL thresholds. Connect to $I^2C$ supply rail.                                                                             |

| A4                | A4                | 8                  | 8                  | GND                                          | Analog Ground.                                                                                                                                                                          |

| B4                | _                 | 10                 | _                  | EN3 (NC for<br>MAX17272)                     | Enable Input for OUT3. Hold high to enable output regulation. Hold low to disable the output. Unused pin for the MAX17272.                                                              |

| _                 | B4                | _                  | 10                 | IRQB                                         | I <sup>2</sup> C Interrupt Output. Connect a pullup resistor between this pin and an external supply.                                                                                   |

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

## **Pin Description (continued)**

|                   | P                 | IN                 |                    |      |                                                                                                         |

|-------------------|-------------------|--------------------|--------------------|------|---------------------------------------------------------------------------------------------------------|

| MAX17270/2<br>WLP | MAX17271/3<br>WLP | MAX17270/2<br>TQFN | MAX17271/3<br>TQFN | NAME | FUNCTION                                                                                                |

| C4                | _                 | 11                 | _                  | EN2  | Enable Input for OUT2. Hold high to enable output regulation. Hold low to disable the output.           |

| _                 | C4                | _                  | 11                 | SDA  | I <sup>2</sup> C Data Input. Used to communicate with the part through the I <sup>2</sup> C interface.  |

| D4                | _                 | 13                 | _                  | EN1  | Enable Input for OUT1. Hold high to enable output regulation. Hold low to disable the output.           |

| _                 | D4                | _                  | 13                 | SCL  | I <sup>2</sup> C Clock Input. Used to communicate with the part through the I <sup>2</sup> C interface. |

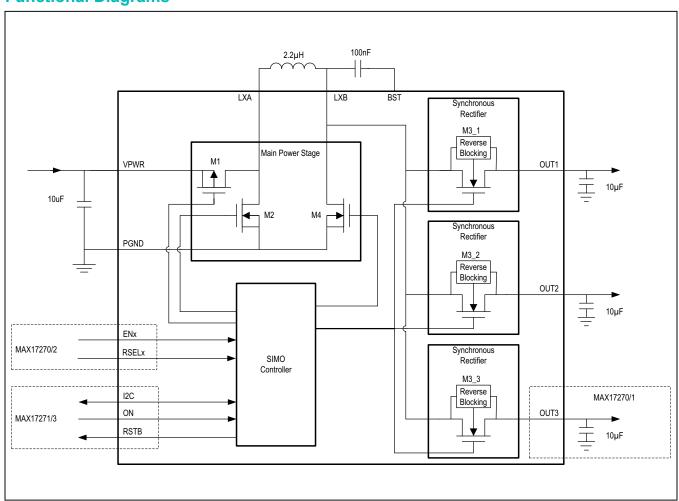

## **Functional Diagrams**

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

#### **Detailed Description**

The MAX17270/MAX17271/MAX17272/MAX17273 are nanopower, single-inductor, multiple-output (SIMO) buckboost, DC-to-DC converters designed for applications that require ultra-low supply current and small solution size. A single inductor is used to regulate three separate outputs, saving board space while delivering higher total system efficiency than equivalent power solutions using multiple buck and/or linear regulators.

The SIMO configuration utilizes the entire battery voltage range due to its ability to create output voltages that are above, below, or equal to the input voltage. Peak inductor current for each output is programmable to optimize the balance between efficiency, output ripple, EMI, PCB design, and load capability.

#### **Output Voltage Configuration**

Each of the outputs are independently configurable. In the MAX17270/MAX17272, to set the output voltages at OUT1/2/3 and the inductor peak current limits ( $I_{LIM}$ ), connect the appropriate resistors from RSEL1/2/3, respectively, to GND, as shown in Table 1. RSEL1/2/3 resistors should have 1% (or better) tolerance. In the MAX17271/MAX17273, to set the output voltages, use the I<sup>2</sup>C interface to load the configuration registers TVSIMOx[7:0]. TVSIMOx[7] is used to enable (TVSIMOx[7] = 1) or disable (TVSIMOx[7] = 0) a 1.2V offset. TVSIMOx[6:0] bits are used to set the output voltage as

$OUT = 0.8V + 25mV \times TVSIMO[6:0](decimal)$

This has been shown in Table 2.

Table 1. MAX17270/MAX17272 Output Voltage and Current Limit Setting

| OUTPUT<br>VOLTAGE (V) | CURRENT<br>LIMIT(A)                                                                                                  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| 0.800                 | 0.6                                                                                                                  |

| 0.900                 | 0.6                                                                                                                  |

| 1.000                 | 0.6                                                                                                                  |

| 1.100                 | 0.6                                                                                                                  |

| 1.200                 | 0.6                                                                                                                  |

| 1.350                 | 0.6                                                                                                                  |

| 1.500                 | 0.6                                                                                                                  |

| 1.800                 | 0.6                                                                                                                  |

| 2.200                 | 0.6                                                                                                                  |

| 2.500                 | 0.6                                                                                                                  |

| 2.800                 | 0.6                                                                                                                  |

| 3.000                 | 0.6                                                                                                                  |

| 3.300                 | 0.6                                                                                                                  |

| 3.600                 | 0.6                                                                                                                  |

| 4.100                 | 0.6                                                                                                                  |

| 4.600                 | 0.6                                                                                                                  |

|                       | VOLTAGE (V)  0.800  0.900  1.000  1.100  1.200  1.350  1.500  1.800  2.200  2.500  2.800  3.000  3.300  3.600  4.100 |

| RSEL (KΩ) | OUTPUT<br>VOLTAGE (V) | CURRENT<br>LIMIT(A) |

|-----------|-----------------------|---------------------|

| 56.2      | 0.800                 | 1.1                 |

| 47.5      | 0.900                 | 1.1                 |

| 40.2      | 1.000                 | 1.1                 |

| 34        | 1.100                 | 1.1                 |

| 28        | 1.200                 | 1.1                 |

| 23.7      | 1.350                 | 1.1                 |

| 20        | 1.500                 | 1.1                 |

| 16.9      | 1.800                 | 1.1                 |

| 14        | 2.200                 | 1.1                 |

| 11.8      | 2.500                 | 1.1                 |

| 10        | 3.000                 | 1.1                 |

| 8.45      | 3.300                 | 1.1                 |

| 7.15      | 3.600                 | 1.1                 |

| 4.99      | 4.100                 | 1.1                 |

| SHORT     | 4.600                 | 1.1                 |

Table 2. MAX17271/MAX17273 Output Voltage Setting

| TVSIMOX[6:0]<br>(DECIMAL) | OUTPUT VOLTAGE (V)<br>WITH TVSIMO[7] = 0 | OUTPUT VOLTAGE (V)<br>WITH TVSIMO[7] = 1 |

|---------------------------|------------------------------------------|------------------------------------------|

| 0                         | 0.8                                      | 2                                        |

| 1                         | 0.825                                    | 2.025                                    |

| 2                         | 0.85                                     | 2.05                                     |

| 3                         | 0.875                                    | 2.075                                    |

| 4                         | 0.9                                      | 2.1                                      |

| 5                         | 0.925                                    | 2.125                                    |

| TVSIMOX[6:0]<br>(DECIMAL) | OUTPUT VOLTAGE (V)<br>WITH TVSIMO[7] = 0 | OUTPUT VOLTAGE (V)<br>WITH TVSIMO[7] = 1 |

|---------------------------|------------------------------------------|------------------------------------------|

| 6 to 122                  | 0.95 to 3.85                             | 2.15 to 5.05                             |

| 123                       | 3.875                                    | 5.075                                    |

| 124                       | 3.9                                      | 5.1                                      |

| 125                       | 3.925                                    | 5.125                                    |

| 126                       | 3.95                                     | 5.15                                     |

| 127                       | 3.975                                    | 5.175                                    |

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

#### SIMO Control Scheme

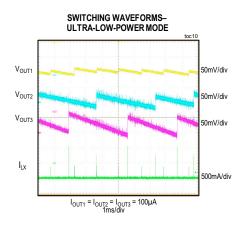

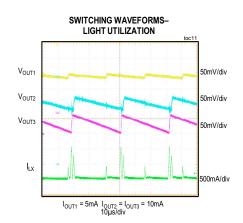

The SIMO buck-boost is designed to service multiple outputs simultaneously. A proprietary controller ensures that all outputs get serviced in a timely manner, even while multiple outputs are contending for the energy stored in the inductor. When no regulator needs service, the state machine rests in a low-power rest state.

When the controller determines that a regulator requires service, it charges the inductor (M1 + M4) until the peak current limit is reached. The inductor energy then discharges (M2 + M3\_x) into the output until the current reaches zero (Izx). In the event that multiple output channels need servicing at the same time, the controller ensures that no output utilizes all of the switching cycles. Instead, cycles interleave between all the outputs that are demanding service, while outputs that do not need service are skipped.

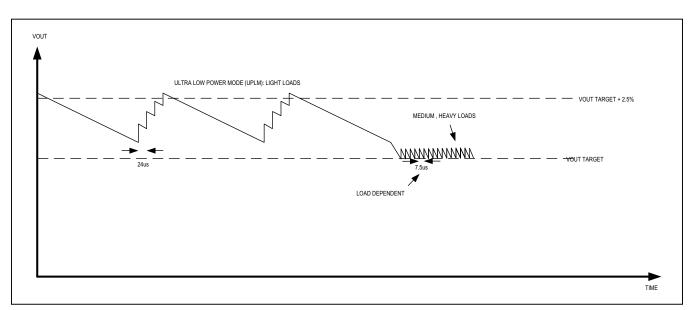

When the load current for any output is very light, that output automatically switches to an ultra-low-power mode (ULPM) to reduce the quiescent current consumption. Figure 1 shows typical waveforms during the ULPM and normal modes. While operating in ULPM, the output voltage is biased 2.5% higher than normal mode by design so that future large load transients can be handled without excessive undershoot.

#### SIMO Soft-Start

The soft-start feature of the SIMO limits inrush current during startup. The soft-start feature is achieved by

limiting the slew rate of the output voltage during startup ( $dV_{OUT}/dt_{SS}$ ).

More output capacitance results in higher input current surges during startup. The following set of equations and example describes the input current surge phenomenon during startup.

The current into the output capacitor ( $I_{COUT}$ ) during soft-start is:

$$I_{COUT} = C_{OUT} \times \frac{dV_{OUT}}{dt_{SS}}$$

(Equation 1)

where:

- C<sub>OUT</sub> is the capacitance on the output of the regulator

- dV<sub>OUT</sub>/dt<sub>SS</sub> is the rate of change of the output voltage The input current (I<sub>IN</sub>) during soft-start is:

$$I_{IN} = \frac{(I_{COUT} + I_{LOAD}) \times \frac{V_{OUT}}{V_{IN}}}{\eta}$$

(Equation 2)

where:

- I<sub>COUT</sub> is calculated from Equation 1

- I<sub>LOAD</sub> is current consumed from the external load

- V<sub>OUT</sub> is the output voltage

- V<sub>IN</sub> is the input voltage

- η is the efficiency of the regulator

Figure 1. ULPM and Normal Mode Waveforms

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

For example, given the following conditions, the peak input current ( $I_{IN}$ ) during soft-start is ~71mA:

#### Given:

- V<sub>IN</sub> is 3.5V

- V<sub>OUT2</sub> is 3.3V

- C<sub>OUT2</sub> = 10μF

- dV<sub>OUT</sub>/dt<sub>SS</sub> = 1mV/µs

- $R_{I,OAD2} = 330\Omega (I_{I,OAD2} = 3.3V/330\Omega = 10mA)$

- η is 80%

#### Calculation:

- $I_{COUT} = 10\mu F \times 1mV/\mu s$  (from Equation 1)

- I<sub>COUT</sub> = 10mA

$$I_{IN} = \frac{(10\text{mA} + 10\text{mA}) \times \frac{3.3\text{V}}{3.5\text{V}}}{0.8} \quad \text{(from Equation 2)}$$

I<sub>IN</sub> = 23.57mA

#### SIMO Registers (MAX17271/MAX17273)

In MAX17271/MAX17273, each SIMO buck-boost channel has a dedicated register to program its target output voltage (TVSIMOx[7:0]) and its peak current limit (ILIM[1:0]). Additional controls are available for enabling/disabling the active discharge resistors (ADE), as well as configuring the power up and power down sequence of the SIMO buck-boost channels (ENCTL[4:0]). For a full description of bits, registers, default values, and reset conditions, refer to the *Register Map*.

## SIMO Active Discharge Resistance (MAX17271/MAX17273)

In MAX17271/MAX17273, each SIMO buck-boost channel has an internal 100 $\Omega$  active-discharge resistor (R<sub>AD\_SBBx</sub>) that is automatically enabled/disabled based on an ADE bit and the status of the SIMO regulator. The active discharge feature may be enabled (ADE = 1) or disabled

(ADE = 0) independently for each SIMO channel. Enabling the active discharge feature helps ensure a complete and timely power-down of all system peripherals. If the active-discharge resistor is enabled by default, then the active-discharge resistor is on whenever  $V_{IN}$  is below  $V_{UVLO}$  and above the power-on reset threshold which is typically 1.35V .

These resistors discharge the output when ADE = 1, and their respective SIMO channel is off.

Note that when  $V_{\text{IN}}$  is less than 1.35V, the NMOS transistors that control the active discharge resistors lose their gate drive and become open.

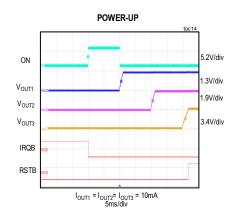

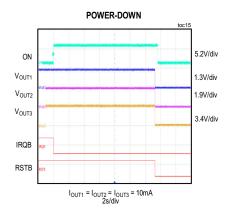

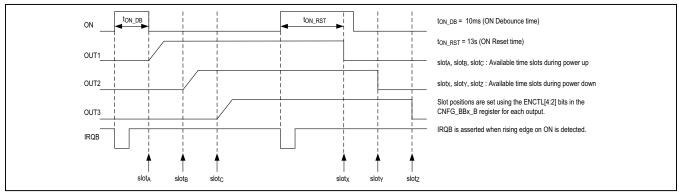

## On Pin Control and Power Sequencer (MAX17271/MAX17273)

The ON pin available on the MAX17271/MAX17273 is a TTL level input used to start and stop a power-up sequence defined through each SIMO configuration register ENCTL[4:0] . A 10ms debounce delay is applied to each edge of the ON signal for those applications using a push-button switch to control the pin. When the ON pin is toggled high for greater than 1µs and less than 13 seconds, the start sequence will be latched to commence following the 10ms debounce delay. Once a start sequence has been initiated, the ON pin can be taken low through a pulldown resistor connected to GND. Any following toggles on the ON pin less than 13 seconds will be ignored. A power-down will initiate after a start sequence if the ON pin is held high longer than 13 seconds. If, for some reason, the ON pin is stuck high, the start sequencer will remain off until a falling edge on the ON pin can be detected. The customer is also provided a software configuration bit (SWR) which will enable the SIMO to auto-restart following a power down and after the 100ms delay. This can be used for diagnostic purposes.

Figure 2 shows an example of a power-up and power-down controlled by the ON pin.

Figure 2. ON Pin Control and Power Sequencer for MAX17271/MAX17273.

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

The timing slots, with which the MAX17271/MAX17273 outputs power-up and power-down, can be set using the ENCTL[4:1] bits in the CNFG\_BBx\_B I<sup>2</sup>C registers.

For a given output, bits ENCTL[4:3] are used to set up the delay between the detection of the ON rising edge (after the debounce delay) and the start of the output voltage ramp up.

The four possible values for the power-up delay are given in the Table 3.

The ENCTL[2] bit can be used to set the power-down delay, as shown in <u>Table 4</u>. The power-down delay is the delay between detection of the ON pin being high for 10s and the start of the outputs being disabled.

To enable the power sequencer, bit ENCTL[1] should be set to 1.

**Table 3. Power-Up Delay Settings**

| ENCTL[4:3] (BINARY) | POWER-UP DELAY (MS) |

|---------------------|---------------------|

| 00                  | 0                   |

| 01                  | 10                  |

| 10                  | 20                  |

| 11                  | 30                  |

If ENCTL[1] = 0, the outputs will not ramp up or ramp down based on the ON pin signal regardless of the ENCTL[4:2] bit settings.

## Fault Response and Reporting (MAX17271/MAX17273)

$\underline{\text{Table 5}}$  describes how the MAX17271/MAX17273 responds to different types of fault events.

When the I2C Interrupt Register (GLBL\_INT) is read back following a fault event, it gets cleared (all bits reset to zero) even if the fault condition persists.

Bits in the GLBL\_INT register can be set again only if the fault condition goes away and then comes back (edge-triggered event).

**Table 4. Power-Down Delay Settings**

| ENCTL[2] (BINARY) | POWER-DOWN DELAY (MS) |

|-------------------|-----------------------|

| 0                 | 0                     |

| 1                 | 30 - (Power-Up Delay) |

Table 5. Fault Response and Reporting (MAX17271/MAX17273)

| EVENT                                   | SIMO SWITCHING<br>STATE   | I <sup>2</sup> C INTERRUPT BIT<br>(GLBL_INT REGISTER) | IRQB PIN      | RSTB PIN                                                          | LATCHING<br>BEHAVIOR                                     |

|-----------------------------------------|---------------------------|-------------------------------------------------------|---------------|-------------------------------------------------------------------|----------------------------------------------------------|

| Temperature > Overtemperature Threshold | All outputs turned off    | THI = 0 to 1                                          | IRQB = 1 to 0 | RSTB = 1 to 0                                                     | ON pin needs to go<br>high again to restart<br>switching |

| V <sub>IN</sub> > OVLO                  | Enabled outputs remain on | OVLO = 0 to 1                                         | IRQB = 1 to 0 | RSTB goes from 1 to<br>0 only if OUT < Target<br>for 14µs or more | No latching<br>behavior                                  |

| V <sub>IN</sub> < UVLO                  | All outputs turned off    | VOKB = 0 to 1                                         | IRQB = 1 to 0 | RSTB = 1 to 0                                                     | ON pin needs to go<br>high again to restart<br>switching |

| OUT < Target for<br>14µs or more        | Enabled outputs remain on | POKB = 0 to 1                                         | IRQB = 1 to 0 | RSTB = 1 to 0                                                     | No latching behavior                                     |

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

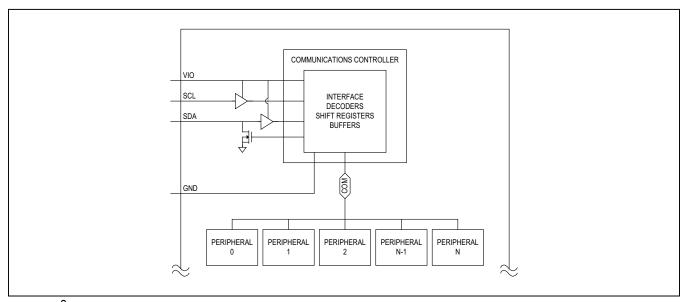

## **Detailed Description – I<sup>2</sup>C**

#### **General Description**

The MAX17271/MAX17273 feature a revision 3.0 I<sup>2</sup>C-compatible, 2-wire serial interface consisting of a bidirectional serial data line (SDA) and a serial clock line (SCL). The MAX17271/MAX17273 act as slave-only devices where they rely on the master to generate a clock signal. SCL clock rates from 0Hz to 3.4MHz are supported.I<sup>2</sup>C is an open-drain bus and therefore SDA and SCL require pullups. Optional resistors (24 $\Omega$ ) in series with SDA and SCL protect the device inputs from high-voltage spikes on the bus lines. Series resistors also minimize crosstalk and undershoot on bus signals. Figure 3 below shows the functional diagram for the I<sup>2</sup>C based communications controller. For additional information on I<sup>2</sup>C, refer the I<sup>2</sup>C bus specification and user manual that is available from NXP (document title: UM10204)

#### **Features**

I<sup>2</sup>C Revision 3 Compatible Serial Communications Channel

- 0Hz to 100kHz (Standard Mode)

- 0Hz to 400kHz (Fast Mode)

- 0Hz to 1MHz (Fast Mode Plus)

- 0Hz to 3.4MHz (High-Speed Mode)

- Does not utilize I<sup>2</sup>C Clock Stretching

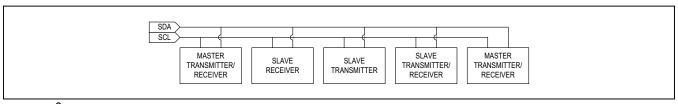

#### I<sup>2</sup>C System Configuration

The I<sup>2</sup>C bus is a multimaster bus. The maximum number of devices that can attach to the bus is only limited by bus capacitance.

A device on the I<sup>2</sup>C bus that sends data to the bus in called a transmitter. A device that receives data from the bus is called a receiver. The device that initiates a data transfer and generates the SCL clock signals to control the data transfer is a master. Any device that is being addressed by the master is considered a slave. The MAX17271/MAX17273 I<sup>2</sup>C compatible interface operates as a slave on the I<sup>2</sup>C bus with transmit and receive capabilities.

Figure 3. I<sup>2</sup>C Simplified Block Diagram

Figure 4. I<sup>2</sup>C System Configuration

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

#### I<sup>2</sup>C Interface Power

The MAX17231/MAX17273's I<sup>2</sup>C interface derives its power from  $V_{IO}$ . Typically a power input such as  $V_{IO}$  would require a local 0.1µF ceramic bypass capacitor to ground. However, in highly integrated power distribution systems, a dedicated capacitor might not be necessary. If the impedance between  $V_{IO}$  and the next closest capacitor ( $\geq$  0.1µF) is less than  $100 \text{m}\Omega$  in series with 10nH, then a local capacitor is not needed. Otherwise, bypass  $V_{IO}$  to GND with a 0.1µF ceramic capacitor.

$V_{IO}$  accepts voltages from 1.7V to 3.6V ( $V_{IO}$ ). Cycling  $V_{IO}$  does not reset the I²C registers. When  $V_{IN}$  is less than  $V_{UVLO},\,SDA$  and SCL are high impedance.

#### I<sup>2</sup>C Data Transfer

One data bit is transferred during each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are control signals. See the <u>I2C Start and Stop Conditions</u> section. Each transmit sequence is framed by a START (S) condition and a STOP (P) condition. Each data packet is nine bits long: eight bits of data followed by the acknowledge bit. Data is transferred with the MSB first.

#### I<sup>2</sup>C Start and Stop Conditions

When the serial interface is inactive, SDA and SCL idle high. A master device initiates communication by issuing a START condition. A START condition is a high-to-low

Figure 5. I<sup>2</sup>C Start and Stop Conditions

transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA, while SCL is high. See Figure 5.

A START condition from the master signals the beginning of a transmission to the MAX17271/MAX17273. The master terminates transmission by issuing a not-acknowledge followed by a STOP condition (see <a href="IZC Acknowledge">IZC Acknowledge</a> Bit for information on not-acknowledge). The STOP condition frees the bus. To issue a series of commands to the slave, the master can issue repeated start (Sr) commands instead of a STOP command to maintain control of the bus. In general a repeated start command is functionally equivalent to a regular start command.

When a STOP condition or incorrect address is detected, the MAX17271/MAX17273 internally disconnect SCL from the serial interface until the next START condition, minimizing digital noise and feedthrough.

#### I<sup>2</sup>C Acknowledge Bit

Both the I<sup>2</sup>C bus master and the MAX17271/MAX17273 (slave) generate acknowledge bits when receiving data. The acknowledge bit is the last bit of each nine bit data packet. To generate an acknowledge (A), the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse. See Figure 6. To generate a not-acknowledge (nA), the receiving device allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse and leaves it high during the high period of the clock pulse.

Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication at a later time.

The MAX17271/MAX17273 issues an ACK for all register addresses in the possible address space even if the particular register does not exist.

Figure 6. Acknowledge Bit

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

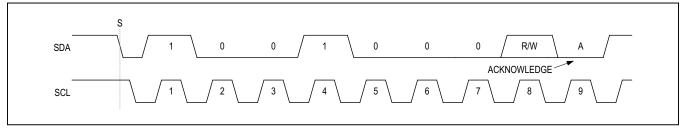

### I<sup>2</sup>C Slave Address

The I<sup>2</sup>C controller implements 7-bit slave addressing. An I<sup>2</sup>C bus master initiates communication with the slave by issuing a START condition followed by the slave address. See <u>Figure 7</u>. See <u>Table 6</u>. All slave addresses not mentioned in the Table 6 are not acknowledged.

#### I<sup>2</sup>C Clock Stretching

In general, the clock signal generation for the I<sup>2</sup>C bus is the responsibility of the master device. The I<sup>2</sup>C specification allows slow slave devices to alter the clock signal by holding down the clock line. The process in which a slave device holds down the clock line is typically called clock stretching. The MAX17271/MAX17273 does not use any form of clock stretching to hold down the clock line.

#### I<sup>2</sup>C General Call Address

The MAX17271/MAX17273 does not implement the I<sup>2</sup>C specifications general call address. If the MAX17271/MAX17273 sees the general call address (0b0000\_0000), it does not issue an acknowledge.

#### I<sup>2</sup>C Device ID

The MAX17271/MAX17273 does not support the I<sup>2</sup>C Device ID feature.

#### I<sup>2</sup>C Communication Speed

The MAX17271/MAX17273 is compatible with all 4 communication speed ranges as defined by the Revision  $3\ I^2C$  specification:

- 0Hz to 100kHz (Standard Mode)

- 0Hz to 400kHz (Fast Mode)

- 0Hz to 1MHz (Fast Mode)

- 0Hz to 3.4MHz (High-Speed Mode)

Operating in standard mode, fast mode, and fast mode plus does not require any special protocols. The main consideration when changing the bus speed through this range is the combination of the bus capacitance and pullup resistors. Higher time constants created by the bus capacitance and pullup resistance (C x R) slow the bus operation. Therefore, when increasing bus speeds, the pullup resistance must be decreased to maintain a reasonable time constant. Refer to the Pullup Resistor Sizing section of the I2C revision 3.0 specification (UM10204) for detailed guidance on the pullup resistor selection. In general for bus capacitances of 200pF, a 100kHz bus needs 5.6kΩ pullup resistors, a 400kHz bus needs about a  $1.5k\Omega$  pullup resistors, and a 1MHz bus needs  $680\Omega$  pullup resistors. Note that when the opendrain bus is low, the pullup resistor is dissipating power, lower value pullup resistors dissipate more power (V<sup>2</sup>/R).

Operating in high-speed mode requires some special considerations. For a full list of considerations, see the **I<sup>2</sup>C Specification** section. The major considerations with respect to the MAX17271/MAX17273:

- The I<sup>2</sup>C bus master use current source pullups to shorten the signal rise

- The I<sup>2</sup>C slave must use a different set of input filters on its SDA and SCL lines to accommodate for the higher bus

- The communication protocols need to utilize the highspeed master code.

At power-up and after each stop condition, the MAX17271/ MAX17273 inputs filters are set for standard mode, fast mode, or fast mode plus (i.e., 0Hz to 1MHz). To switch the input filters for high-speed mode, use the high-speed master code protocols that are described in the <a href="#center-of-22">[2]Communication Protocols</a> section.

Figure 7. Slave Address Example

#### Table 6.: I<sup>2</sup>C Slave Address Options

| ADDRESS                    | 7-BIT SLAVE ADDRESS | 8-BIT WRITE ADDRESS | 8-BIT READ ADDRESS |

|----------------------------|---------------------|---------------------|--------------------|

| Main Address<br>(ADDR = 1) | 0x48, 0b 100 1000   | 0x90, 0b 1001 0000  | 0x91, 0b 1001 0001 |

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

#### I<sup>2</sup>C Communication Protocols

The MAX17271/MAX17273 supports both writing and reading from its registers.

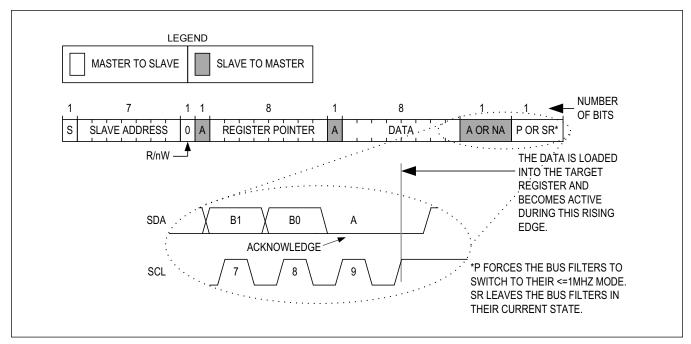

#### Writing to a Single Register

<u>Figure 8</u> shows the protocol for the I<sup>2</sup>C master device to write one byte of data to the MAX17271/MAX17273. This protocol is the same as the SMBus specification's write byte protocol.

The write byte protocol is as follows:

- The master sends a start command (S).

- The master sends the 7-bit slave address followed by a write bit (R/W = 0).

- The addressed slave asserts an acknowledge (A) by pulling SDA low.

- The master sends an 8-bit register pointer.

- The slave acknowledges the register pointer.

- The master sends a data byte.

- · The slave updates with the new data

- The slave acknowledges or not acknowledges the data byte. The next rising edge on SDA will load the data byte into its target register and the data will become active.

The master sends a stop condition (P) or a repeated start condition (Sr). Issuing a P ensures that the bus input filters are set for 1MHz or slower operation. Issuing an Sr leaves the bus input filters in their current state.

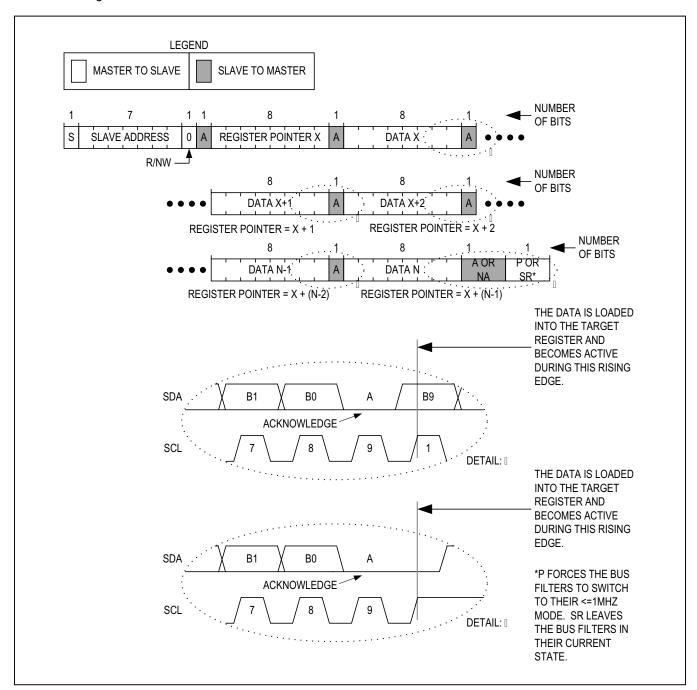

#### Writing Multiple Bytes to Sequential Registers

<u>Figure 9</u> shows the protocol for writing to a sequential registers. This protocol is similar to the write byte protocol above, except the master continues to write after it receives the first byte of data. When the master is done writing it issues a stop or repeated start.

The writing to sequential registers protocol is as follows:

- The master sends a start command (S).

- The master sends the 7-bit slave address followed by a write bit (R/W = 0).

- The addressed slave asserts an acknowledge (A) by pulling SDA low.

- The master sends an 8-bit register pointer.

- The slave acknowledges the register pointer.

- The master sends a data byte.

- The slave acknowledges the data byte. The next rising edge on SDA load the data byte into its target register and the data will become active.

Figure 8. Writing to a Single Register with the Write Byte Protocol

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

- Steps 6 to 7 are repeated as many times as the master requires.

- During the last acknowledge related clock pulse, the master can issue an acknowledge or a not acknowledge.

- The master sends a stop condition (P) or a repeated start condition (Sr). Issuing a P ensures that the bus input filters are set for 1MHz or slower operation. Issuing an Sr leaves the bus input filters in their current state.

Figure 9. Writing to Sequential Registers X to N

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

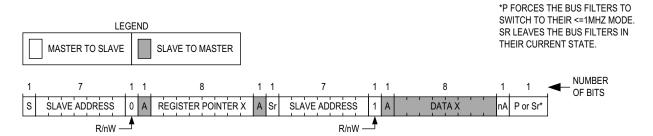

#### Reading from a Single Register

<u>Figure 10</u> shows the protocol for the I<sup>2</sup>C master device to read one byte of data to the MAX17271/MAX17273. This protocol is the same as the SMBus specification's read byte protocol. The read byte protocol is as follows:

- The master sends a start command (S).

- The master sends the 7-bit slave address followed by a write bit (R/W = 0).

- The addressed slave asserts an acknowledge (A) by pulling SDA low.

- The master sends an 8-bit register pointer.

- The slave acknowledges the register pointer.

- The master sends a repeated start command (Sr).

- The master sends the 7-bit slave address followed by a read bit (R/W = 1).

- The addressed slave asserts an acknowledge by pulling SDA low.

- The addressed slave places 8-bits of data on the bus from the location specified by the register pointer.

- The master issues a not acknowledge (nA).

- The master sends a stop condition (P) or a repeated start condition (Sr). Issuing a P ensures that the bus input filters are set for 1MHz or slower operation. Issuing an Sr leaves the bus input filters in their current state.

Note that, when the the MAX17271/MAX17273 receives a stop, it does not modify its register pointer.

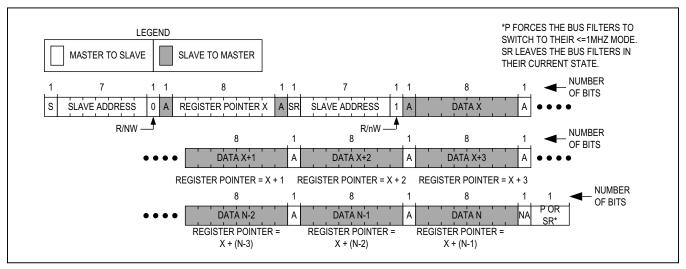

#### **Reading from Sequential Registers**

Figure 11 shows the protocol for reading from sequential registers. This protocol is similar to the read byte protocol except the master issues an acknowledge to signal the slave that it wants more data: when the master has all the data it requires it issues a not acknowledge (nA) and a stop (P) to end the transmission.

Figure 10. Reading from a Single Register with the Read Byte Protocol

Figure 11. Reading Continuously from Sequential Registers X to N

## nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

The continuous read from sequential registers protocol is as follows:

- The master sends a start command (S).

- The master sends the 7-bit slave address followed by a write bit (R/W = 0).

- The addressed slave asserts an acknowledge (A) by pulling SDA low.

- The master sends an 8-bit register pointer.

- The slave acknowledges the register pointer.

- The master sends a repeated start command (Sr).

- The master sends the 7-bit slave address followed by a read bit (R/W = 1). When reading the RTC timekeeping registers, secondary buffers are loaded with the timekeeping register data during this operation.

- The addressed slave asserts an acknowledge by pulling SDA low.

- The addressed slave places 8-bits of data on the bus from the location specified by the register pointer.

- The master issues an acknowledge (A) signaling the slave that it wishes to receive more data.

- Steps 9 to 10 are repeated as many times as the master requires. Following the last byte of data, the master must issue a not acknowledge (nA) to signal that it wishes to stop receiving data.

The master sends a stop condition (P) or a repeated start condition (Sr). Issuing a stop (P) ensures that the bus input filters are set for 1MHz or slower operation. Issuing an Sr leaves the bus input filters in their current state.

Note that, when the MAX77650/MAX77651 receives a stop, it does not modify its register pointer.

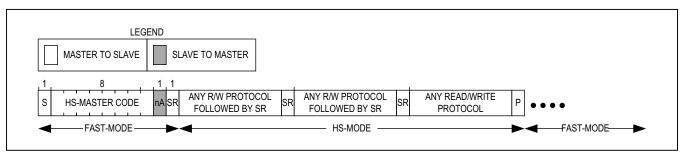

#### Engaging HS-mode for operation up to 3.4MHz

<u>Figure 12</u> shows the protocol for engaging HS-mode operation. HS-mode operation allows for a bus operating speed up to 3.4MHz.

The engaging HS mode protocol is as follows:

- Begin the protocol while operating at a bus speed of 1MHz or lower

- The master sends a start command (S).

- The master sends the 8-bit master code of 0b0000 1XXX where 0bXXX are don't care bits.

- The addressed slave issues a not acknowledge (nA).

- The master may now increase its bus speed up to 3.4MHz and issue any read/write operation.

The master may continue to issue high-speed read/write operations until a stop (P) is issued. To continue operations in high speed mode, use repeated start (Sr).

Figure 12. Engaging HS Mode

# nanoPower Triple/Dual-Output, Single-Inductor, Multiple-Output (SIMO) Buck-Boost Regulator

## **Register Map**

| ADDRESS  | NAME            | MSB                      |       |       |       |            |            |        | LSB      |

|----------|-----------------|--------------------------|-------|-------|-------|------------|------------|--------|----------|

| REGISTER | REGISTER MAP    |                          |       |       |       |            |            |        |          |

| 0x09     | GLBL_CNFG[7:0]  | -                        | -     | SWR   | DRV   | /[1:0]     | TIDL[1:0]  |        | BIAS OFF |

| 0x10     | GLBL_INT[7:0]   | ON                       | _     | OVLO  | VOKB  | POKB3      | POKB2      | POKB1  | THI      |