Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

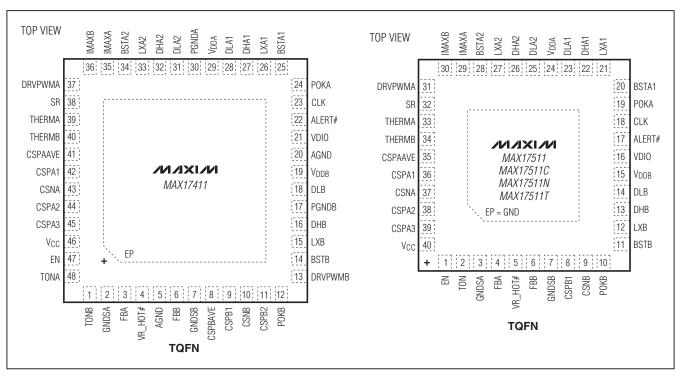

The MAX17411/MAX17511/MAX17511C/MAX17511N/ MAX17511T are dual-output, step-down, constant on-time Quick-PWM™ controllers for VR12/IMVP-7 CPU core supplies. The controllers consist of two high-current switching power supplies for CPU and GFX cores. The CPU regulator (regulator A) is a three-phase constant on-time architecture. The GFX regulator (regulator B) is also constant on-time architecture. The MAX17411 supports 2-phase operation and the MAX17511/MAX17511C/MAX17511N/MAX17511T support 1-phase operation. The MAX17411/MAX17511/ MAX17511C/MAX17511N/MAX17511T include two internal drivers on regulator A and one internal driver on regulator B. External drivers such as the MAX17491 enable the additional phases.

Both regulator A and regulator B include output voltage sensing and accurate load-line gain. Switching frequencies are programmable from 200kHz to 600kHz per phase. Output overvoltage protection (OVP, MAX17411/ MAX17511/MAX17511C/MAX17511N), undervoltage protection (UVP), and thermal protection ensure effective and reliable operation. When any of these protection features detect a fault, the controller shuts down both outputs.

The multiphase regulators include transient-phase overlap and active overshoot suppression, which speed up the response time and reduce the total output capacitance. The CPU and GFX outputs are controlled independently by writing the appropriate data into a functionmapped register file. VID code transitions and soft-start are enabled with a precision slew-rate control circuit. The SVID interface also allows each regulator to be individually set into a low-power, single-phase, pulse-skipping state to optimize efficiency. The MAX17411 is available in a 48-pin, 6mm x 6mm, TQFN package. The MAX17511/ MAX17511C/MAX17511N/MAX17511T are available in a 40-pin, 5mm x 5mm, TQFN lead-free package.

### **Applications**

VR12/IMVP-7 CPU Core Power Supplies Notebooks/Desktops/Servers

#### **Features**

- ♦ Intel VR12/IMVP-7-Compliant Serial Interface

- ♦ 3-/2-/1-Phase Quick-PWM CPU Core Regulator Two Internal Drivers and One External Driver **Transient-Phase Overlap Mode Dynamic Phase Selection**

- ♦ 2-/1-Phase Quick-PWM GFX Regulator One Internal and One External Driver

- Active Overshoot Suppression

- ♦ 8-Bit VR12/IMVP-7 DAC

- ♦ ±0.5% Vout Accuracy Over Line, Load, and **Temperature**

- **◆ Active Voltage Positioning with Programmable**

- **♦ Accurate Lossless Current Balance**

- ♦ Accurate Droop and Current Limit

- Remote Output and Ground Sense

- ♦ Power-Good Window Comparators (POKA and POKB)

- ◆ 4.5V to 24V Battery-Input Voltage Range

- Programmable 200kHz to 600kHz Switching Frequency

- **♦** External Thermal-Fault Detection Output (VR HOT#)

- ♦ Overvoltage (MAX17411/MAX17511/MAX17511C/ MAX17511N), Undervoltage, and Thermal-Fault **Protection**

- ♦ Slew-Rate Controlled Soft-Start

- ♦ Passive Soft-Shutdown (20Ω Discharge Switches)

- Integrated Boost Switches

- ♦ Low-Profile, 48-Lead/40-Lead TQFN Packages

Quick PWM is a trademark of Maxim Integrated Products, Inc.

### **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE | FEATURE                    |

|--------------|-----------------|-------------|----------------------------|

| MAX17411GTM+ | -40°C to +105°C | 48 TQFN-EP* | 3-/2-/1-Phase + 2-/1-Phase |

| MAX17511GTL+ | -40°C to +105°C | 40 TQFN-EP* | 3-/2-/1-Phase + 1-Phase    |

#### Ordering Information continued on last page.

- +Denotes a lead(Pb)-free/RoHS-compliant package.

- \*EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

|                   | _          |                                   |

|-------------------|------------|-----------------------------------|

|                   |            | 0.3V to +6V                       |

|                   |            | 0.3V to +6V                       |

| CSPAAVE, CSPBAVE  |            |                                   |

|                   |            | 0.3V to +6V                       |

|                   |            | 0.3V to (VCC + 0.3V)              |

|                   |            | 0.3V to (VCC + 0.3V)              |

|                   |            | 0.3V to +6V                       |

| VR_HOT# to GND (A | (GND)      | 0.3V to +6V                       |

|                   |            | 0.3V to (VCC + 0.3V)              |

| GNDSA, GNDSB to   | GND (AGND) | 0.3V to +0.3V                     |

| TON to GND        |            | 0.3V to +26V                      |

| DRVPWMA to GND (  | (AGND)     | 0.3V to (V <sub>DDA</sub> + 0.3V) |

| DRVPWMB to GND (  | (AGND)     | 0.3V to (V <sub>DDB</sub> + 0.3V) |

| DLA_ to GND (PGND | O)         | $-0.3V$ to $(V_{DDA} + 0.3V)$     |

| DLB to GND (PGND) | )          | 0.3V to (V <sub>DDB</sub> + 0.3V) |

|                   |            |                                   |

| BSTA_ to VDDA0.3V to +26V<br>BSTB to VDDB0.3V to +26V |

|-------------------------------------------------------|

| LXA_ to BSTA6V to +0.3V                               |

| LXB to BSTB6V to +0.3V                                |

| LX_ to GND (AGND)6V to +26V                           |

| DHA_ to LXA0.3V to (VBSTA_ + 0.3V)                    |

| DHB to LXB0.3V to (VBSTB + 0.3V)                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| 40-Pin TQFN (derate 35.7mW/°C above +70°C) 2857.1mW   |

| 48-Pin TQFN (derate 37mW/°C above +70°C)2963mW        |

| Operating Temperature Range40°C to +105°C             |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +165°C               |

| Lead Temperature (soldering, 10s)+300°C               |

| Soldering Temperature (reflow)+260°C                  |

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

40 TQFN

48 TOFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......28°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )........1.6°C/W

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......27°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )........1.3°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Circuits of Figures 1 and 2. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC, VGNDS\_ = 0V, VFB\_ = VCSP\_AVE = VCSP\_ = VCSN\_ = 1V; [SerialVID = 1.00, FPWM MODE]; **TA = 0°C to +85°C**, unless otherwise noted. Typical values are at TA = +25°C. All devices 100% tested at TA = +25°C. Limits over temperature guaranteed by design.)

| PARAMETER                     | SYMBOL | CONDITIONS                                                                    |                                 | MIN   | TYP   | MAX   | UNITS |  |  |

|-------------------------------|--------|-------------------------------------------------------------------------------|---------------------------------|-------|-------|-------|-------|--|--|

| PWM CONTROLLER                |        |                                                                               |                                 |       |       |       |       |  |  |

| Input Voltage Range           |        | VCC, VDDA, VDDB                                                               |                                 | 4.5   |       | 5.5   | V     |  |  |

| DC Output Voltage<br>Accuracy |        | Measured at FB_ with                                                          | DAC codes from 1.000V to 1.520V | -0.5  |       | +0.5  | %     |  |  |

|                               |        | respect to GNDS_;<br>includes load regulation                                 | DAC codes from 0.800V to 0.995V | -5    |       | +5    | mV    |  |  |

|                               |        | error (Note 2)                                                                | DAC codes from 0.250V to 0.795V | -8    |       | +8    | IIIV  |  |  |

| Line Regulation Error         |        | VCC = 4.5V to 5.5V, V <sub>IN</sub> =                                         | 4.5V to 24V                     |       | 0.1   |       | mV    |  |  |

| VSETTLED Bit Accuracy         |        | Upward transitions                                                            |                                 | -15   | -10   | -5    | mV    |  |  |

| VSETTLED Bit Accuracy         |        | Downward transitions                                                          |                                 | 5     | 10    | 15    | IIIV  |  |  |

| GNDS_ Input Range             |        |                                                                               |                                 | -200  |       | +200  | mV    |  |  |

| GNDS_ Gain                    | AGNDS  | ΔVOUT/ΔVGNDS_                                                                 |                                 | 0.97  | 1.00  | 1.03  | V/V   |  |  |

| GNDS_ Input Bias Current      |        | T <sub>A</sub> = +25°C                                                        | T <sub>A</sub> = +25°C          |       |       | +0.5  | μΑ    |  |  |

| TON Shutdown Current          |        | EN = GND, V <sub>IN</sub> = 24V, V <sub>CC</sub> = 0V, T <sub>A</sub> = +25°C |                                 |       | 0.01  | 0.1   | μΑ    |  |  |

| Boot Voltage                  |        | MAX17511N only, Reg A and Reg B                                               |                                 | 1.094 | 1.100 | 1.106 | V     |  |  |

|                               | Vвоот  | MAX17511C only, Reg B of                                                      | only                            | 0.895 | 0.900 | 0.905 | V     |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC,  $VGNDS_ = 0V$ ,  $VFB_ = VCSP_AVE = VCSP_ = VCSN_ = 1V$ ; [SerialVID = 1.00, FPWM MODE];  $TA = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $TA = +25^{\circ}C$ . All devices 100% tested at  $TA = +25^{\circ}C$ . Limits over temperature guaranteed by design.)

| PARAMETER                                   | SYMBOL                                            | CONI                                                                                                                                                                | DITIONS                                        | MIN | TYP  | MAX | UNITS    |  |

|---------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|------|-----|----------|--|

|                                             |                                                   | Measured at DHA_ (600 RTON = 96.7k $\Omega$ (MAX17 RTON = 48.35k $\Omega$ (MAX MAX17511N/MAX17511                                                                   | 7411 only),<br>17511/MAX17511C/                | 157 | 185  | 213 |          |  |

| DHA_ On-Time (Note 3)                       | tona                                              | Measured at DHA_, $V_{IN}$<br>R <sub>TON</sub> = 200k $\Omega$ (MAX17-1)<br>(MAX17511/MAX175110<br>MAX17511T)                                                       | 411 only), R <sub>TON</sub> = $100$ k $\Omega$ | 276 | 307  | 338 | ns       |  |

|                                             |                                                   | Measured at DHA_ (200 RTON = 303.3k $\Omega$ (MAX1 RTON = 151.65k $\Omega$ (MAX17511N/MAX17511                                                                      | 7411 only),<br>X17511/MAX17511C/               | 470 | 554  | 638 |          |  |

| DHB On-Time (Note 3)                        |                                                   | Measured at DHB (600k<br>R <sub>TON</sub> = 96.7k $\Omega$ (MAX17<br>R <sub>TON</sub> = 48.35k $\Omega$ (MAX<br>MAX17511N/MAX17511                                  | 7411 only),<br>17511/MAX17511C/                | 128 | 151  | 174 |          |  |

|                                             | tONB                                              | Measured at DHB, $V_{IN}$ = RTON = 200k $\Omega$ (MAX17-1) (MAX17511/MAX17511T)                                                                                     | 411 only), RTON = $100$ k $\Omega$             | 226 | 251  | 277 | ns       |  |

|                                             |                                                   | Measured at DHB (200kHz + 10%),<br>R <sub>TON</sub> = 303.3k $\Omega$ (MAX17411 only), R <sub>TON</sub> = 151.65k $\Omega$ (MAX17511/MAX17511C/MAX17511N/MAX17511T) |                                                | 385 | 453  | 521 |          |  |

| Minimum Off-Time (Note 3)                   | toff(MIN)                                         | Measured at DH_                                                                                                                                                     |                                                | 150 | 200  | 250 | ns       |  |

| Minimum DRVPWM_ Pulse Width                 |                                                   |                                                                                                                                                                     |                                                |     | 40   |     | ns       |  |

| BIAS CURRENTS                               |                                                   |                                                                                                                                                                     |                                                |     |      |     |          |  |

| Quiescent Supply Current (VCC)              | IBIAS                                             | Measured at V <sub>CC</sub> , SKIP the regulation point                                                                                                             | mode, FB_ forced above                         |     | 5    | 10  | mA       |  |

| Quiescent Supply Current (VDD_)             | IDRV                                              | T <sub>A</sub> = +25°C, measured FB_ forced above the re                                                                                                            |                                                |     | 0.02 | 1   | μΑ       |  |

| Shutdown Supply Current (VCC)               |                                                   | Measured at VCC, EN =                                                                                                                                               | GND                                            |     | 16   | 30  | μΑ       |  |

| Shutdown Supply Current (V <sub>DD</sub> _) |                                                   | $T_A = +25^{\circ}C$ , measured                                                                                                                                     | at V <sub>DD</sub> , EN = GND                  |     | 0.01 | 1   | μA       |  |

| SLEW-RATE CONTROL                           |                                                   |                                                                                                                                                                     |                                                |     |      |     |          |  |

| Slew-Rate Accuracy                          |                                                   | Van OV ar Van EV                                                                                                                                                    | SetVID - fast slew rate = 10mV/µs (min)        | 10  |      |     |          |  |

|                                             | VSR = 0V or VSR = 5V<br>VSR = 3V or<br>VSR = 1.5V | A2H - OA OL A2H = 2A                                                                                                                                                | SetVID - slow slew rate<br>= 2.5mV/µs (min)    | 2.5 |      |     | DO)//::2 |  |

|                                             |                                                   | V <sub>SR</sub> = 3V or                                                                                                                                             | SetVID - fast slew rate = 20mV/µs (min)        | 20  |      |     | mV/μs    |  |

|                                             |                                                   | SetVID - slow slew rate = 5mV/µs (min)                                                                                                                              | 5                                              |     |      |     |          |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC,  $VGNDS_ = 0V$ ,  $VFB_ = VCSP_AVE = VCSP_ = VCSN_ = 1V$ ; [SerialVID = 1.00, FPWM MODE]; TA = 0°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C. All devices 100% tested at TA = +25°C. Limits over temperature guaranteed by design.)

| PARAMETER                                                                                      | SYMBOL   | CONDITIONS                                                                                                                                              | MIN                        | TYP  | MAX                        | UNITS |

|------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|----------------------------|-------|

| Soft-Start Slew Rate                                                                           |          | Non-zero V <sub>BOOT</sub>                                                                                                                              | 2.5                        |      |                            | mV/µs |

| Discharge Switch<br>Resistance                                                                 |          | CSNA, CSNB                                                                                                                                              |                            | 20   |                            | Ω     |

|                                                                                                |          | Low                                                                                                                                                     |                            |      | 0.4                        |       |

|                                                                                                |          | Mid-low                                                                                                                                                 | 1.2                        |      | 1.8                        |       |

| SR Four-Level Logic<br>Thresholds                                                              |          | Mid-high                                                                                                                                                | 2.2                        |      | V <sub>C</sub> C<br>- 1.2V | V     |

|                                                                                                |          | High                                                                                                                                                    | V <sub>C</sub> C<br>- 0.4V |      |                            |       |

| FAULT PROTECTION                                                                               |          |                                                                                                                                                         |                            |      |                            |       |

| Upper POK_ (MAX17411/<br>MAX17511/MAX17511C/<br>MAX17511N/MAX17511T)<br>and Output Overvoltage | Vovp     | SKIP mode after output reaches the regulation voltage or PWM mode; measured at FB_ with respect to the voltage target set by the VID code (see Table 3) | 200                        | 250  | 300                        | mV    |

| Protection Trip Threshold(MAX17411/ MAX17511/MAX17511C/                                        | ,<br> C/ | Soft-start, SKIP mode, and output has not reached the regulation voltage; measured at FB_                                                               | 1.72                       | 1.77 | 1.82                       | V     |

| MAX17511N)                                                                                     |          | Minimum OVP threshold, measured at FB_                                                                                                                  |                            | 0.8  |                            |       |

| Upper POK_ and Output<br>Overvoltage Propagation<br>Delay                                      | tovp     | FB_ forced 25mV above trip threshold (MAX17411/MAX17511/MAX17511C/MAX17511N)                                                                            |                            | 5    |                            | μs    |

| Lower POK_ and Output<br>Undervoltage Protection<br>Trip Threshold                             | Vuvp     | Measured at FB_ with respect to unloaded output voltage                                                                                                 | -300                       | -250 | -200                       | mV    |

| Lower POK_ Propagation Delay                                                                   |          | FB_ forced 25mV below trip threshold                                                                                                                    |                            | 5    |                            | μs    |

| Output Undervoltage<br>Propagation Delay                                                       | tuvp     | FB_ forced 25mV below trip threshold                                                                                                                    | 100                        | 200  | 350                        | μs    |

| POK_ Output Low Voltage                                                                        |          | ISINK = 4mA                                                                                                                                             |                            |      | 0.3                        | V     |

| POK_ Leakage Current                                                                           |          | High state, POK_ forced to 5V, TA = +25°C                                                                                                               |                            |      | 1                          | μΑ    |

| POK_ Startup Delay and Transitions Blanking Time                                               | tpok_    | Measured from the time when FB_ reaches the target voltage                                                                                              |                            | 20   |                            | μs    |

| VCC Undervoltage-Lockout<br>Threshold                                                          | Vuvlo    | Rising edge, 50mV typical hysteresis, controller disabled below this level                                                                              | 4.05                       | 4.25 | 4.45                       | V     |

MIXIM

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC,  $VGNDS_ = 0V$ ,  $VFB_ = VCSP_AVE = VCSP_ = VCSN_ = 1V$ ; [SerialVID = 1.00, FPWM MODE];  $TA = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $TA = +25^{\circ}C$ . All devices 100% tested at  $TA = +25^{\circ}C$ . Limits over temperature guaranteed by design.)

| PARAMETER                                    | SYMBOL   |                                    | CONDITIONS                                                                                                                                            | MIN  | TYP                  | MAX                  | UNITS  |

|----------------------------------------------|----------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------------|--------|

| THERMAL PROTECTION                           |          |                                    |                                                                                                                                                       |      |                      |                      |        |

| VR_HOT# Trip Threshold                       |          | edge; specify a                    | Measured at THERM_ with respect to V <sub>CC</sub> falling edge; specify as % error for all TEMP MAX DAC code settings, typical hysteresis = 100mV    |      |                      | 50.5                 | %      |

| Thermal Zone Registers Trip<br>Points        |          | with respect to corresponding      | Thermal zone comparator trip points, measured with respect to VCC; voltage threshold corresponding to TMAX x (1 - N%), N = 0, 3, 6, 9, 12, 15, 18, 25 |      | 50 +<br>24 x<br>N/31 | 51 +<br>24 x<br>N/31 | %      |

| THERM_ Input Leakage                         | ITHRM    | VTHERM_ = 2.5\                     | /, T <sub>A</sub> = +25°C                                                                                                                             | -100 |                      | +100                 | nA     |

| VR_HOT# Leakage Current                      |          | High-Z state (The forced to 5V, Ta | HERM_ > 0.505 x VCC), VR_HOT#<br>\( = +25°C\)                                                                                                         |      |                      | 1                    | μA     |

| Internal Thermal Fault<br>Shutdown Threshold | TTSHDN   | Typical hysteresis = 15°C          |                                                                                                                                                       |      | 160                  |                      | °C     |

| VALLEY CURRENT LIMIT A                       | ND DROOP |                                    |                                                                                                                                                       |      |                      |                      |        |

|                                              |          |                                    | RSENSE = $0.65m\Omega$ , $I_{MAXA} = 39A$                                                                                                             | 22.5 | 25.5                 | 28.5                 |        |

|                                              |          |                                    | RSENSE = $0.65$ m $\Omega$ , IMAXA = $36$ A                                                                                                           | 21.5 | 24.5                 | 27.5                 |        |

|                                              |          |                                    | RSENSE = $0.65$ m $\Omega$ , I <sub>MAXA</sub> = $30$ A                                                                                               | 17.0 | 20.0                 | 23.0                 | ]      |

|                                              |          |                                    | RSENSE = $0.65$ m $\Omega$ , IMAXA = $26$ A                                                                                                           | 15.0 | 18.0                 | 21.0                 |        |

|                                              |          |                                    | RSENSE = $0.75$ m $\Omega$ , I <sub>MAXA</sub> = $39$ A                                                                                               | 27.0 | 30.0                 | 33.0                 |        |

|                                              |          | VCSP VCSN_,                        | RSENSE = $0.75$ m $\Omega$ , IMAXA = $36$ A                                                                                                           | 25.0 | 28.0                 | 31.0                 |        |

|                                              |          | V <sub>SR</sub> = 0V,              | RSENSE = $0.75$ m $\Omega$ , I <sub>MAXA</sub> = $30$ A                                                                                               | 20.0 | 23.0                 | 26.0                 |        |

| Valley Current-Limit                         | VILIMA   | VsR = 1.5V,                        | RSENSE = $0.75$ m $\Omega$ , IMAXA = $26$ A                                                                                                           | 17.0 | 20.0                 | 23.0                 | mV     |

| Threshold Voltage (Positive)                 | VILIMA   | or one-phase                       | RSENSE = $0.85$ m $\Omega$ , I <sub>MAXA</sub> = $39$ A                                                                                               | 30.0 | 33.0                 | 36.0                 | ] '''' |

|                                              |          | operation                          | RSENSE = $0.85m\Omega$ , I <sub>MAXA</sub> = $36A$                                                                                                    | 28.0 | 31.0                 | 34.0                 |        |

|                                              |          |                                    | RSENSE = $0.85$ m $\Omega$ , I <sub>MAXA</sub> = $30$ A                                                                                               | 22.5 | 25.5                 | 28.5                 |        |

|                                              |          |                                    | RSENSE = $0.85$ m $\Omega$ , I <sub>MAXA</sub> = $26$ A                                                                                               | 20.0 | 23.0                 | 26.0                 | ]      |

|                                              |          |                                    | RSENSE = $0.95$ m $\Omega$ , I <sub>MAXA</sub> = $39$ A                                                                                               | 33.5 | 36.5                 | 39.5                 |        |

|                                              |          |                                    | RSENSE = $0.95m\Omega$ , I <sub>MAXA</sub> = $36A$                                                                                                    | 31.0 | 34.0                 | 37.0                 |        |

|                                              |          |                                    | RSENSE = $0.95m\Omega$ , IMAXA = $30A$                                                                                                                | 25.0 | 28.0                 | 31.0                 |        |

|                                              |          |                                    | RSENSE = $0.95m\Omega$ , I <sub>MAXA</sub> = $26A$                                                                                                    | 21.5 | 24.5                 | 27.5                 |        |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2.  $V_{IN} = 10V$ ,  $V_{CC} = V_{DDA} = V_{DDB} = 5V$ ,  $E_{IN} = V_{CC}$ ,  $V_{GNDS} = 0V$ ,  $V_{FB} = V_{CSP}$ ,  $V_{FB}$

| PARAMETER                    | SYMBOL |                                            | CONDITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|------------------------------|--------|--------------------------------------------|----------------------------------------------------|------|------|------|-------|

|                              |        |                                            | RSENSE = $0.65m\Omega$ , IMAXA = $39A$             | 29.0 | 33.0 | 37.0 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , IMAXA = $36A$             | 28.0 | 32.0 | 36.0 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , $I_{MAXA} = 30A$          | 22.0 | 26.0 | 30.0 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , IMAXA = $26A$             | 19.5 | 23.5 | 27.5 |       |

|                              |        |                                            | RSENSE = $0.75m\Omega$ , $I_{MAXA} = 39A$          | 35.0 | 39.0 | 43.0 |       |

|                              |        | VCSP VCSN_,                                | RSENSE = $0.75m\Omega$ , IMAXA = $36A$             | 32.5 | 36.5 | 40.5 |       |

|                              |        | VsR = 3V or                                | RSENSE = $0.75m\Omega$ , $I_{MAXA} = 30A$          | 26.0 | 29.9 | 33.8 |       |

| Valley Current-Limit         | \/     | VSR = 5V,                                  | RSENSE = $0.75m\Omega$ , IMAXA = $26A$             | 22.0 | 26.0 | 30.0 | m\/   |

| Threshold Voltage (Positive) | VILIMA | exclude<br>one-phase                       | RSENSE = $0.85m\Omega$ , $I_{MAXA} = 39A$          | 39.0 | 43.0 | 47.0 | mV    |

|                              |        | operaton                                   | RSENSE = $0.85m\Omega$ , $I_{MAXA} = 36A$          | 36.5 | 40.5 | 44.5 |       |

|                              |        |                                            | RSENSE = $0.85m\Omega$ , $I_{MAXA} = 30A$          | 29.0 | 33.0 | 37.0 |       |

|                              |        |                                            | RSENSE = $0.85m\Omega$ , $I_{MAXA} = 26A$          | 26.0 | 30.0 | 34.0 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , $I_{MAXA} = 39A$          | 43.5 | 47.5 | 51.5 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , $I_{MAXA} = 36A$          | 40.0 | 44.0 | 48.0 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , IMAXA = $30A$             | 32.5 | 36.5 | 40.5 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , $I_{MAXA} = 26A$          | 28.0 | 32.0 | 36.0 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , IMAXB = $39A$             | 22.5 | 25.5 | 28.5 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , $I_{MAXB} = 36A$          | 21.5 | 24.5 | 27.5 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , IMAXB = $23A$             | 13.0 | 16.0 | 19.0 |       |

|                              |        |                                            | RSENSE = $0.65m\Omega$ , $I_{MAXB} = 20A$          | 11.0 | 14.0 | 17.0 |       |

|                              |        |                                            | RSENSE = $0.75m\Omega$ , IMAXB = $39A$             | 27.0 | 30.0 | 33.0 |       |

|                              |        | VCSP VCSN_,                                | RSENSE = $0.75m\Omega$ , $I_{MAXB} = 36A$          | 25.0 | 28.0 | 31.0 |       |

|                              |        | $VCSP_{\perp} VCSN_{\perp}$ , $VSR = 0V$ , | RSENSE = $0.75m\Omega$ , IMAXB = $23A$             | 15.0 | 18.0 | 21.0 |       |

| Valley Current-Limit         | \/u    | VSR = 1.5V,                                | RSENSE = $0.75m\Omega$ , $I_{MAXB} = 20A$          | 13.0 | 16.0 | 19.0 | mV    |

| Threshold Voltage (Positive) | VILIMB | or one-phase                               | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 39A$          | 30.0 | 33.0 | 36.0 | IIIV  |

|                              |        | operation                                  | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 36A$          | 28.0 | 31.0 | 34.0 |       |

|                              |        |                                            | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 23A$          | 17.0 | 20.0 | 23.0 |       |

|                              |        |                                            | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 20A$          | 15.0 | 18.0 | 21.0 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , I <sub>MAXB</sub> = $39A$ | 33.5 | 36.5 | 39.5 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , IMAXB = $36A$             | 31.0 | 34.0 | 37.0 |       |

|                              |        |                                            | RSENSE = $0.95m\Omega$ , I <sub>MAXB</sub> = $23A$ | 20.0 | 23.0 | 26.0 |       |

|                              |        |                                            | RSENSE = $0.95$ m $\Omega$ , IMAXB = $20$ A        | 17.0 | 20.0 | 23.0 |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC,  $VGNDS_ = 0V$ ,  $VFB_ = VCSP_AVE = VCSP_ = VCSN_ = 1V$ ; [SerialVID = 1.00, FPWM MODE];  $TA = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $TA = +25^{\circ}C$ . All devices 100% tested at  $TA = +25^{\circ}C$ . Limits over temperature guaranteed by design.)

| PARAMETER                                          | SYMBOL |                              | CONDITIONS                                | MIN   | TYP                  | MAX          | UNITS |

|----------------------------------------------------|--------|------------------------------|-------------------------------------------|-------|----------------------|--------------|-------|

|                                                    |        |                              | RSENSE = $0.65m\Omega$ , IMAXB = $39A$    | 29.0  | 33.0                 | 37.0         |       |

|                                                    |        |                              | RSENSE = $0.65m\Omega$ , IMAXB = $36A$    | 28.0  | 32.0                 | 36.0         |       |

|                                                    |        |                              | RSENSE = $0.65m\Omega$ , $I_{MAXB} = 23A$ | 17.0  | 21.0                 | 25.0         |       |

|                                                    |        |                              | RSENSE = $0.65m\Omega$ , IMAXB = $20A$    | 14.0  | 18.0                 | 22.0         |       |

|                                                    |        |                              | RSENSE = $0.75m\Omega$ , $I_{MAXB} = 39A$ | 35.0  | 39.0                 | 43.0         |       |

|                                                    |        | VCSP VCSN_,                  | RSENSE = $0.75m\Omega$ , IMAXB = $36A$    | 32.5  | 36.5                 | 40.5         |       |

|                                                    |        | $V_{SR} = 3V \text{ or}$     | RSENSE = $0.75m\Omega$ , $I_{MAXB} = 23A$ | 19.5  | 23.5                 | 27.5         |       |

| Valley Current-Limit                               | \/     | $V_{SR} = 5V$ ,              | RSENSE = $0.75m\Omega$ , IMAXB = $20A$    | 17.0  | 21.0                 | 25.0         | mV    |

| Threshold Voltage (Positive)                       | VILIMB | exclude                      | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 39A$ | 39.0  | 43.0                 | 47.0         | IIIV  |

|                                                    |        | one-phase                    | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 36A$ | 36.5  | 40.5                 | 44.5         |       |

|                                                    |        | operaton                     | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 23A$ | 22.0  | 26.0                 | 30.0         |       |

|                                                    |        |                              | RSENSE = $0.85m\Omega$ , $I_{MAXB} = 20A$ | 19.5  | 23.5                 | 27.5         |       |

|                                                    |        |                              | RSENSE = $0.95m\Omega$ , $I_{MAXB} = 39A$ | 43.5  | 47.5                 | 51.5         |       |

|                                                    |        |                              | RSENSE = $0.95m\Omega$ , $I_{MAXB} = 36A$ | 40.0  | 44.0                 | 48.0         |       |

|                                                    |        |                              | RSENSE = $0.95m\Omega$ , IMAXB = $23A$    | 26.0  | 30.0                 | 34.0         |       |

|                                                    |        |                              | RSENSE = $0.95m\Omega$ , $I_{MAXB} = 20A$ | 22.0  | 26.0                 | 30.0         |       |

| Current-Limit Threshold<br>Voltage (Zero Crossing) | Vzero  | VGND - VLX_                  |                                           |       | 1                    |              | mV    |

| Current-Balance Offset<br>Voltage                  |        |                              |                                           | -1.5  |                      | +1.5         | mV    |

| CSPAAVE, CSPBAVE, CSP_,<br>Input Current           |        | T <sub>A</sub> = +25°C       |                                           | -0.12 |                      | +0.12        | μΑ    |

| CSN_ Pulldown Current                              |        |                              |                                           | 7     |                      | 14           | μA    |

| Phase Disable Threshold                            |        | CSPB2, CSPB1,                | CSPA3, CSPA2, CSPA1                       | 3     | V <sub>C</sub> C - 1 | VCC -<br>0.4 | V     |

| FB_ Droop Amplifier (GMD)<br>Offset                |        | (VCSP_AVE - VCS              | SN_) at I <sub>FB</sub> _ = 0mA           | -1.0  |                      | +1.0         | mV    |

| FB_ Droop Amplifier (GMD)<br>Transconductance      |        | ΔIFB_/Δ(VCSP_AVCSP_AVE - VCS | vE - VCSN_),<br>N_ = -15mV to +15mV       | 591   | 600                  | 609          | μS    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC,  $VGNDS_ = 0V$ ,  $VFB_ = VCSP_AVE = VCSP_ = VCSN_ = 1V$ ; [SerialVID = 1.00, FPWM MODE];  $TA = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $TA = +25^{\circ}C$ . All devices 100% tested at  $TA = +25^{\circ}C$ . Limits over temperature guaranteed by design.)

| PARAMETER                 | SYMBOL | CONDITIONS                                                                      | MIN                                                       | TYP I                          | VIAX            | UNITS                                                                           |                                |  |                 |  |

|---------------------------|--------|---------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------|-----------------|---------------------------------------------------------------------------------|--------------------------------|--|-----------------|--|

| IMAX_ LOGIC               |        |                                                                                 |                                                           |                                |                 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 0, fault                                                              |                                                           |                                | 3.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 1, RSENSE = $0.65m\Omega$ , $I_{MAX} = 39A$                           | 14.20 x<br>V <sub>CC</sub> /50                            |                                | 4.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        |                                                                                 |                                                           |                                |                 | Threshold 2, R <sub>SENSE</sub> = $0.65$ m $\Omega$ , I <sub>MAX</sub> = $36$ A | 15.20 x<br>V <sub>CC</sub> /50 |  | 5.65 x<br>CC/50 |  |

|                           |        |                                                                                 | Threshold 3, RSENSE = $0.65m\Omega$ , IMAXA/B = $30A/23A$ | 16.20 x<br>V <sub>CC</sub> /50 |                 | 6.65 x<br>CC/50                                                                 |                                |  |                 |  |

|                           |        | Threshold 4, RSENSE = $0.65m\Omega$ , IMAXA/B = $26A/20A$                       | 17.20 x<br>V <sub>CC</sub> /50                            |                                | 7.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 5, R <sub>SENSE</sub> = $0.75$ m $\Omega$ , I <sub>MAX</sub> = $3$ 9A | 18.20 x<br>V <sub>CC</sub> /50                            |                                | 3.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 6, RSENSE = $0.75m\Omega$ , IMAX = $36A$                              | 19.20 x<br>V <sub>CC</sub> /50                            |                                | 9.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 7, RSENSE = $0.75m\Omega$ , IMAX = $30A/23A$                          | 20.20 x<br>V <sub>CC</sub> /50                            |                                | 0.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

| MAY Day in The Late       |        | ,                                                                               | Threshold 8, RSENSE = $0.75m\Omega$ , IMAX = $26A/20A$    | 21.20 x<br>V <sub>CC</sub> /50 |                 | 1.65 x<br>CC/50                                                                 | V                              |  |                 |  |

| MAX_ Detection Thresholds |        |                                                                                 | Threshold 9, RSENSE = $0.85m\Omega$ , IMAX = $39A$        | 22.20 x<br>V <sub>CC</sub> /50 |                 | 2.65 x<br>CC/50                                                                 |                                |  |                 |  |

|                           |        | Threshold 10, RSENSE = $0.85m\Omega$ , IMAX = $36A$                             | 23.20 x<br>V <sub>CC</sub> /50                            |                                | 3.65 x          |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 11, R <sub>SENSE</sub> = $0.85$ m $\Omega$ , IMAXA/B = $30$ A/23A     | 24.20 x<br>VCC/50                                         |                                | 4.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 12, R <sub>SENSE</sub> = $0.85$ m $\Omega$ , IMAXA/B = $26$ A/20A     | 25.20 x<br>Vcc/50                                         |                                | 5.65 x          |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 13, R <sub>SENSE</sub> = $0.95m\Omega$ , $I_{MAX} = 39A$              | 26.20 x<br>VCC/50                                         |                                | 6.65 x          |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 14, R <sub>SENSE</sub> = 0.95mΩ, I <sub>MAX</sub> = 36A               | 27.20 x<br>VCC/50                                         |                                | 7.65 x          |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 15, R <sub>SENSE</sub> = $0.95$ m $\Omega$ , IMAXA/B = $30$ A/23A     | 28.20 x<br>Vcc/50                                         |                                | 3.65 x          |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 16, RSENSE = $0.95m\Omega$ , IMAXA/B = $26A/20A$                      | 29.20 x<br>V <sub>CC</sub> /50                            |                                | 9.65 x<br>CC/50 |                                                                                 |                                |  |                 |  |

|                           |        | Threshold 17, fault                                                             | 30.20 x<br>Vcc/50                                         |                                |                 |                                                                                 |                                |  |                 |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2.  $V_{IN} = 10V$ ,  $V_{CC} = V_{DDA} = V_{DDB} = 5V$ ,  $E_{IN} = V_{CC}$ ,  $E_{IN} = 0$ ,

| PARAMETER                                       | SYMBOL                | CONDI                                                     | TIONS                                    | MIN                        | TYP  | MAX         | UNITS |  |

|-------------------------------------------------|-----------------------|-----------------------------------------------------------|------------------------------------------|----------------------------|------|-------------|-------|--|

| GATE DRIVERS                                    |                       |                                                           |                                          |                            |      |             |       |  |

| DH_ Gate-Driver On-Resistance                   | Ron(dh)               | BST LX_ forced to 5V                                      | High state (pullup) Low state (pulldown) |                            | 0.9  | 2.5         | Ω     |  |

|                                                 |                       | High state (pullup)                                       | Low state (pulldown)                     |                            | 0.7  |             |       |  |

| DL_ Gate-Driver On-Resistance                   | RON(DL)               | High state (pullup)  Low state (pulldown)                 |                                          |                            | 0.7  | 0.7         | Ω     |  |

|                                                 |                       | '' '                                                      | . V DOTD +- V                            |                            | 0.23 | 0.7         |       |  |

| Internal BST_ Switch On-<br>Resistance          | R <sub>BST</sub>      | BSTA1 to V <sub>DDA</sub> , BSTA2 to V <sub>DD</sub> = 5V | VDDA, BSTB to VDDB,                      |                            | 10   | 20          | Ω     |  |

| DH_ Gate-Driver Source<br>Current               | I <sub>DH</sub> (SRC) | DH_ forced to 2.5V, BST_                                  | - LX_ forced to 5V                       |                            | 2.2  |             | А     |  |

| DH_ Gate-Driver Sink<br>Current                 | IDH(SINK)             | DH_ forced to 2.5V, BST_                                  | - LX_ forced to 5V                       |                            | 2.7  |             | А     |  |

| DL_ Gate-Driver Source<br>Current               | IDL(SRC)              | DL_ forced to 2.5V                                        |                                          |                            | 2.7  |             | А     |  |

| DL_ Gate-Driver Sink<br>Current                 | IDL(SINK)             | DL_ forced to 2.5V                                        |                                          |                            | 8    |             | А     |  |

| Driver Propagation Delay                        |                       | DH_ low to DL_ high                                       |                                          |                            | 30   |             | ns    |  |

| Driver Fropagation Delay                        |                       | DL_ low to DH_ high                                       |                                          |                            | 30   |             | 115   |  |

| DL_ Transition Time                             |                       | DL_ falling, C <sub>DL</sub> = 3nF                        |                                          |                            | 20   |             | ns    |  |

| DL_ Hansidon fille                              |                       | DL_ rising, CDL = 3nF                                     |                                          |                            | 20   |             | 110   |  |

| DH_ Transition Time                             |                       | DH_ falling, C <sub>DH</sub> = 3nF                        |                                          |                            | 20   |             | 20    |  |

| DH_ Transition Time                             |                       | DH_ rising, CDH = 3nF                                     |                                          |                            | 20   |             | ns    |  |

| DRVPWMA, DRVPWMB<br>Logic-High Voltage          |                       | ISOURCE = 3mA                                             |                                          | V <sub>DD</sub> _<br>- 0.4 |      |             | V     |  |

| DRVPWMA, DRVPWMB<br>Logic-Low Voltage           |                       | ISINK = 3mA                                               |                                          |                            |      | 0.4         | V     |  |

| LOGIC AND I/O                                   |                       |                                                           |                                          |                            |      |             |       |  |

| Enable Input High Voltage                       | V <sub>EN_IH</sub>    |                                                           |                                          | 0.67                       |      |             | V     |  |

| Enable Input Low Voltage                        | VEN_IL                |                                                           |                                          |                            |      | 0.33        | V     |  |

| Enable Input Current                            |                       | $T_A = +25^{\circ}C$                                      |                                          | -1                         |      | +1          | μΑ    |  |

| SERIALVID INTERFACE (pe                         | r Intel Seria         | IVID Specification—see the                                | ne Detailed Description)                 |                            |      |             |       |  |

| SerialVID Input Low Voltage (CLK, VDIO)         | VIL                   |                                                           |                                          | -0.1                       |      | +0.45       | V     |  |

| SerialVID Input High Voltage (CLK, VDIO)        | VIH                   |                                                           |                                          | 0.65                       |      | VTT +<br>1V | V     |  |

| SerialVID Output High<br>Voltage (VDIO, ALERT#) | Voн                   | Open-drain pullup to VTT                                  |                                          |                            | VTT  |             | V     |  |

| SerialVID Output Low Level (VDIO, ALERT#)       | VoL                   | Open-drain pullup to VTT,                                 | Rpu = 50Ω                                |                            |      | 0.36        | V     |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2. VIN = 10V, VCC = VDDA = VDDB = 5V, EN = VCC,  $VGNDS_ = 0V$ ,  $VFB_ = VCSP_AVE = VCSP_ = VCSN_ = 1V$ ; [SerialVID = 1.00, FPWM MODE];  $TA = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $TA = +25^{\circ}C$ . All devices 100% tested at  $TA = +25^{\circ}C$ . Limits over temperature guaranteed by design.)

| PARAMETER                                                              | SYMBOL | CONDITIONS                                           | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------------------|--------|------------------------------------------------------|------|-----|------|-------|

| SerialVID Open-Drain<br>Output On-Resistance<br>(VDIO, ALERT#, VRHOT#) | Ron    | ISINK = 30mA                                         | 4    |     | 13   | Ω     |

| SerialVID Logic-Input<br>Leakage Current<br>(CLK, VDIO)                |        | T <sub>A</sub> = +25°C                               | -1   |     | +1   | μΑ    |

| ALERT# Deasserted<br>Leakage Current                                   |        | T <sub>A</sub> = +25°C, V <sub>A</sub> LERT# = 3.3V  |      |     | 1    | μА    |

| SerialVID Logic Slew Rate (CLK, VDIO, ALERT#)                          |        |                                                      | 0.5  |     | 2.0  | V/ns  |

| SerialVID Input Capacitance                                            | CPAD   |                                                      |      |     | 4    | рF    |

| CLK Frequency                                                          | fCLK   |                                                      | 13   | 25  | 33.3 | MHz   |

| CLK Absolute Min/Max<br>Period                                         |        | Specified as a percentage of fCLK                    | -5   |     | +5   | %     |

| CLK High Time                                                          | tHIGH  | Specified as a percentage of t <sub>CLK</sub> period | 45   |     |      | %     |

| CLK Low Time                                                           | tLOW   | Specified as a percentage of t <sub>CLK</sub> period | 45   |     |      | %     |

| Rise Time                                                              | trise  |                                                      | 0.25 | ·   | 2.5  | ns    |

| Fall Time                                                              | tfall  |                                                      | 0.25 |     | 2.5  | ns    |

| Duty Cycle                                                             |        |                                                      | 45   |     | 55   | %     |

| SerialVID Inactivity Timeout                                           | trstna |                                                      | 0.14 |     | 0.40 | μs    |

#### **ELECTRICAL CHARACTERISTICS**

(Circuits of Figures 1 and 2.  $V_{IN} = 10V$ ,  $V_{CC} = V_{DDA} = V_{DDB} = 5V$ ,  $EN = V_{CC}$ ,  $V_{GNDS} = 0V$ ,  $V_{FB} = V_{CSP} = V_$

| PARAMETER                     | SYMBOL                                                | CON                                | DITIONS                            | MIN   | TYP | MAX   | UNITS |

|-------------------------------|-------------------------------------------------------|------------------------------------|------------------------------------|-------|-----|-------|-------|

| PWM CONTROLLER                |                                                       |                                    |                                    |       |     |       |       |

| Input Voltage Range           |                                                       | VCC, VDDA, VDDB                    |                                    | 4.5   |     | 5.5   | V     |

|                               |                                                       | Measured at FB_                    | DAC codes from 1.000V<br>to 1.520V | -0.8  |     | +0.8  | %     |

| DC Output Voltage<br>Accuracy | with respect to GNDS_; includes load regulation error | DAC codes from 0.800V<br>to 0.995V | -8                                 |       | +8  | mV    |       |

|                               |                                                       | (Note 2)                           | DAC codes from 0.250 to 0.795V     | -8    |     | +8    | IIIV  |

| Vostti en DIT Aggurgay        |                                                       | Upward transitions                 |                                    | -15   |     | -5    | mV    |

| VSETTLED BIT Accuracy         |                                                       | Downward transitions               |                                    | 5     |     | 15    | IIIV  |

| GNDS_ Input Range             |                                                       |                                    |                                    | -200  |     | +200  | mV    |

| GNDS_ Gain                    | AGNDS                                                 | ΔVOUT/ΔVGNDS_                      |                                    | 0.97  |     | 1.03  | V/V   |

| Boot Voltage                  | \/poot                                                | MAX17511N only, Reg A and Reg B    |                                    | 1.091 |     | 1.109 | V     |

|                               | Vвоот                                                 | MAX17511C only, Reg                | B only                             | 0.892 |     | 0.908 | ] v   |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2.  $V_{IN} = 10V$ ,  $V_{CC} = V_{DDA} = V_{DDB} = 5V$ ,  $EN = V_{CC}$ ,  $V_{GNDS} = 0V$ ,  $V_{FB} = V_{CSP}AVE = V_{CSP} = V_{CSP} = 1V$ ; [SerialVID = 1.00, FPWM MODE];  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Specifications to  $-40^{\circ}C$  and  $+105^{\circ}C$  are guaranteed by design, not production tested.)

| PARAMETER                      | SYMBOL    | COND                                                                                                                                                                 | ITIONS                                                                                                                                                                  | MIN       | TYP MAX                 | UNITS  |  |

|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|--------|--|

|                                |           | Measured at DHA_ (600kl<br>R <sub>TON</sub> = 96.7kΩ (MAX174<br>(MAX17511/MAX17511C/                                                                                 | ,                                                                                                                                                                       | 157       | 213                     |        |  |

| DHA_ On-Time (Note 3)          | tona      | Measured at DHA_, $V_{IN}$ = R <sub>TON</sub> = 200k $\Omega$ (MAX174 (MAX17511/MAX17511C/                                                                           |                                                                                                                                                                         | 276       | 338                     | ns     |  |

|                                |           | Measured at DHA_ (200kHz - 10%),<br>R <sub>TON</sub> = 303.3k $\Omega$ (MAX17411 only), R <sub>TON</sub> = 151.65k $\Omega$ (MAX17511/MAX17511C/MAX17511N/MAX17511T) | 470                                                                                                                                                                     | 638       |                         |        |  |

|                                |           | Measured at DHB (600kl RTON = 96.7k $\Omega$ (MAX1748.35k $\Omega$ (MAX17511/MAMAX17511T)                                                                            | 411 only), RTON =                                                                                                                                                       | 128       | 174                     |        |  |

| DHB On-Time (Note 3)           | tONB      | $R_{TON} = 200k\Omega$ (MAX174                                                                                                                                       | Measured at DHB, $V_{IN}$ = 12V (300kHz + 10%),<br>$R_{TON}$ = 200k $\Omega$ (MAX17411 only), $R_{TON}$ = 100k $\Omega$<br>(MAX17511/MAX17511C/MAX17511N/<br>MAX17511T) |           | 277                     | ns     |  |

|                                |           | Measured at DHB (200kHz + 10%), RTON = 303.3k $\Omega$ (MAX17411 only), RTON = 151.65k $\Omega$ (MAX17511/MAX17511C/MAX17511N/MAX17511T)                             |                                                                                                                                                                         | 385       | 521                     |        |  |

| Minimum Off-Time<br>(Note 3)   | toff(MIN) | Measured at DH_                                                                                                                                                      |                                                                                                                                                                         | 150       | 250                     | ns     |  |

| BIAS CURRENTS                  |           |                                                                                                                                                                      |                                                                                                                                                                         |           |                         |        |  |

| Quiescent Supply Current (VCC) | IBIAS     | Measured at VCC, SKIP r the regulation point                                                                                                                         | mode, FB_ forced above                                                                                                                                                  |           | 10                      | mA     |  |

| Shutdown Supply Current (VCC)  |           | Measured at VCC, EN = 0                                                                                                                                              | GND                                                                                                                                                                     |           | 30                      | μΑ     |  |

| SLEW-RATE CONTROL              |           |                                                                                                                                                                      |                                                                                                                                                                         |           |                         |        |  |

|                                |           | V <sub>SR</sub> = 0V or V <sub>SR</sub> = 5V                                                                                                                         | SetVID - fast slew rate = 10mV/µs (min)                                                                                                                                 | 10        |                         |        |  |

| Slew-Rate Accuracy             |           | A2K = 0.0 OL A2K = 2A                                                                                                                                                | SetVID - slow slew rate = 2.5mV/µs (min)                                                                                                                                | 2.5       |                         | m\//uo |  |

|                                |           | Von - 2V or Von 15V                                                                                                                                                  | SetVID - fast slew rate = 20mV/µs (min)                                                                                                                                 | 20        |                         | mV/µs  |  |

|                                |           | $V_{SR} = 3V \text{ or } V_{SR} = 1.5V$                                                                                                                              | SetVID - slow slew rate = 5mV/µs (min)                                                                                                                                  | 5         |                         |        |  |

| Soft-Start Slew Rate           |           | Non-zero VBOOT                                                                                                                                                       |                                                                                                                                                                         | 2.5       |                         | mV/μs  |  |

|                                |           | Low                                                                                                                                                                  |                                                                                                                                                                         |           | 0.4                     |        |  |

| SR Four-Level Logic            |           | Mid-low                                                                                                                                                              |                                                                                                                                                                         | 1.2       | 1.8                     | V      |  |

| Thresholds                     |           | Mid-high                                                                                                                                                             |                                                                                                                                                                         |           | V <sub>C</sub> C - 1.2V | V      |  |

|                                |           | High                                                                                                                                                                 |                                                                                                                                                                         | VCC - 0.4 | V                       |        |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuits of Figures 1 and 2.  $V_{IN} = 10V$ ,  $V_{CC} = V_{DDA} = V_{DDB} = 5V$ ,  $E_{IN} = V_{CC}$ ,  $V_{GNDS} = 0V$ ,  $V_{FB} = V_{CSP} = V_{CSP}$

| PARAMETER                                                                                                                    | SYMBOL    |                                        | CONDITIONS                                                                                           | MIN                  | TYP  | MAX                  | UNITS |

|------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|-------|

| FAULT PROTECTION                                                                                                             | 01202     | 1                                      |                                                                                                      |                      |      |                      | 00    |

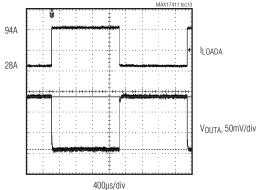

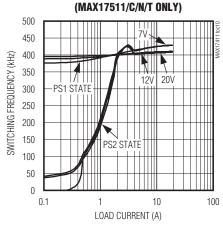

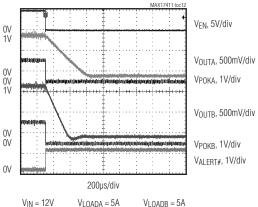

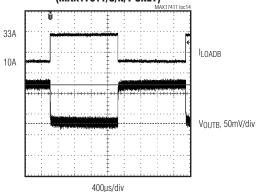

| Upper POK_ (MAX17411/<br>MAX17511/MAX17511N/<br>MAX17511T) and Output<br>Overvoltage Protection Trip<br>Threshold (MAX17411/ | Vovp      | voltage or PWM                         | r output reaches the regulation<br>mode; measured at FB_ with<br>oltage target set by the VID code   | 200                  |      | 300                  | mV    |