# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

19-4723; Rev 0; 7/09

EVALUATION KIT AVAILABLE

# 1-Phase Quick-PWM Intel IMVP-6.5/GMCH Controllers

### **General Description**

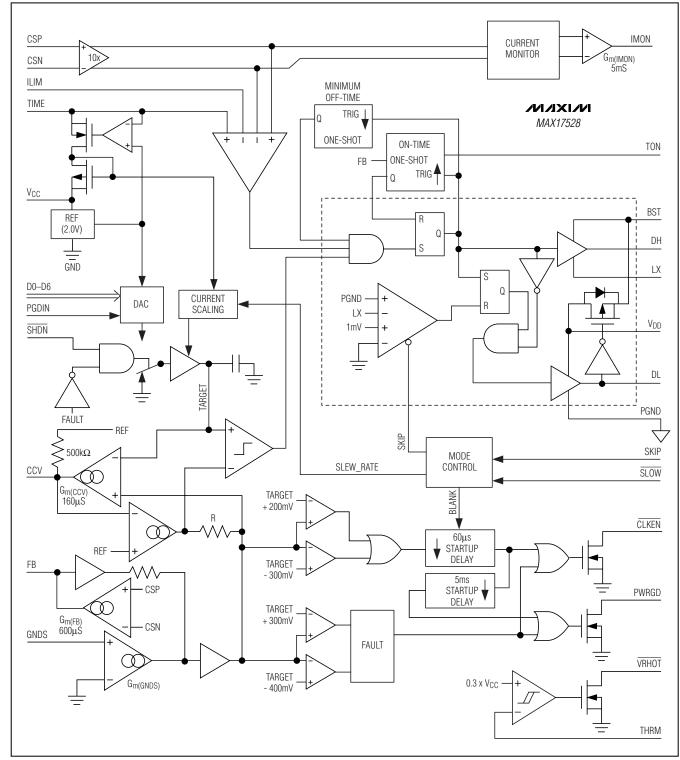

The MAX17528 comprises 1-phase Quick-PWM<sup>™</sup> stepdown VID power-supply controllers for Intel notebook CPUs. The Quick-PWM control provides instantaneous response to fast-load current steps. Active voltage positioning reduces power dissipation and bulk output capacitance requirements and allows ideal positioning compensation for tantalum, polymer, or ceramic bulk output capacitors.

The MAX17528 is intended for two different notebook CPU/GPU core applications: either bucking down the battery directly to create the core voltage, or bucking down the +5V system supply. The single-stage conversion method allows these devices to directly step down high-voltage batteries for the highest possible efficiency. Alternatively, 2-stage conversion (stepping down the +5V system supply instead of the battery) at higher switching frequency provides the minimum possible physical size.

A slew-rate controller allows controlled transitions between VID codes. A thermistor-based temperature sensor provides programmable thermal protection. A current monitor provides an analog output current proportional to the processor load current.

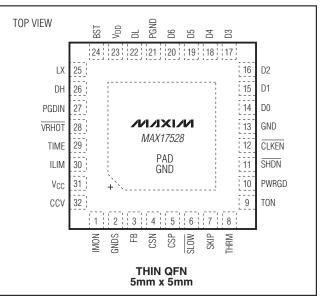

The MAX17528 implements both the Intel IMVP-6.5 CPU core specifications (CLKEN pullup to 3.3V), as well as the Intel GMCH graphics core specifications (CLKEN = GND). The MAX17528 is available in a 32-pin, 5mm x 5mm TQFN package.

#### **Applications**

IMVP-6.5 Core Power Supply

Intel GMCH 2009

Intel Calpella Platforms

Graphics Core Power Supply

Voltage-Positioned Step-Down Converters

1-to-4 Lithium-Ion (Li+)-Cell Battery-to-CPU Core Supply Converters

Notebooks/Desktops/Servers

#### \_Features

- 1-Phase Quick-PWM Controller

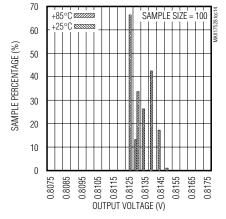

- ♦ ±0.5% V<sub>OUT</sub> Accuracy Over Line, Load, and Temperature

- 7-Bit IMVP-6.5 DAC

- IMVP-6.5 and GMCH Compliant

- Active Voltage Positioning with Adjustable Gain

- Accurate Droop and Current Limit

- Remote Output and Ground Sense

- ♦ Adjustable Output-Voltage Slew Rate

- Power-Good Window Comparator

- Current Monitor

- Temperature Comparator

- Drives Large Synchronous Rectifier FETs

- ♦ 2V to 26V Battery Input Range

- Adjustable Switching Frequency (600kHz max)

- Undervoltage and Thermal-Fault Protection

- Soft-Startup and Soft-Shutdown

- Internal Boost Diode

#### **\_Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX17528GTJ+ | -40°C to +105°C | 32 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

### Pin Configuration

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

####

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , V <sub>DD</sub> to GND0.3V to +6V        | BST to GND0.3V to +36V                                |

|------------------------------------------------------------|-------------------------------------------------------|

| D0–D6 to GND0.3V to +6V                                    | LX to BST6V to +0.3V                                  |

| CSP, CSN to GND0.3V to +6V                                 | BST to V <sub>DD</sub> 0.3V to +30V                   |

| ILIM, THRM, PGDIN, VRHOT, PWRGD to GND0.3V to +6V          | DH to LX0.3V to ( $V_{BST}$ + 0.3V)                   |

| CLKEN to GND0.3V to +6V                                    | Continuous Power Dissipation (32-pin, 5mm x 5mm TQFN) |

| SKIP, SLOW to GND0.3V to +6V                               | Up to +70°C1702mW                                     |

| CCV, FB, IMON, TIME to GND0.3V to (V <sub>CC</sub> + 0.3V) | Derating above +70°C21.3mW/°C                         |

| SHDN to GND (Note 1)0.3V to +30V                           | Operating Temperature Range40°C to +105°C             |

| TON to GND0.3V to +30V                                     | Junction Temperature+150°C                            |

| GNDS, PGND to GND0.3V to +0.3V                             | Storage Temperature Range65°C to +165°C               |

| DL to PGND0.3V to (V <sub>DD</sub> + 0.3V)                 | Lead Temperature (soldering, 10s)+300°C               |

Note 1: SHDN can be forced to 12V for the purpose of debugging prototype breadboards using the no-fault test mode, which disables fault protection.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

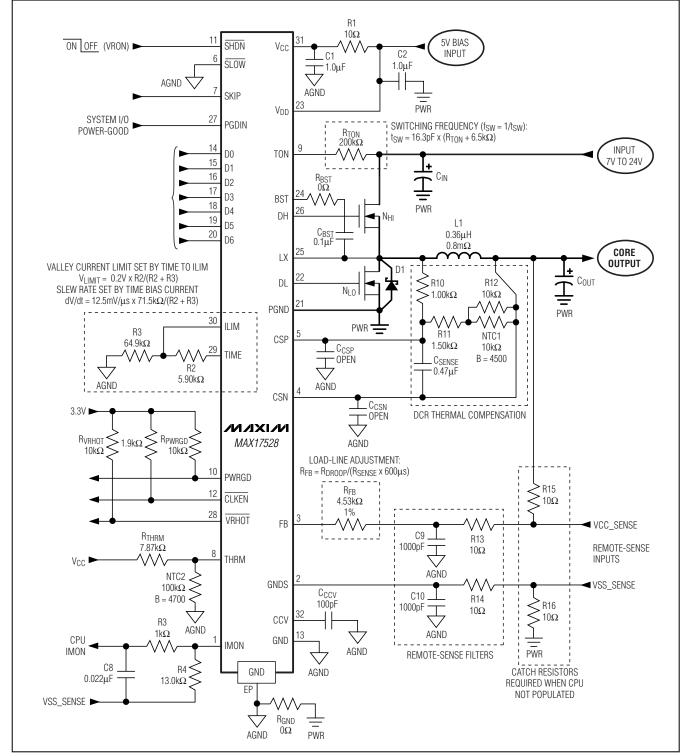

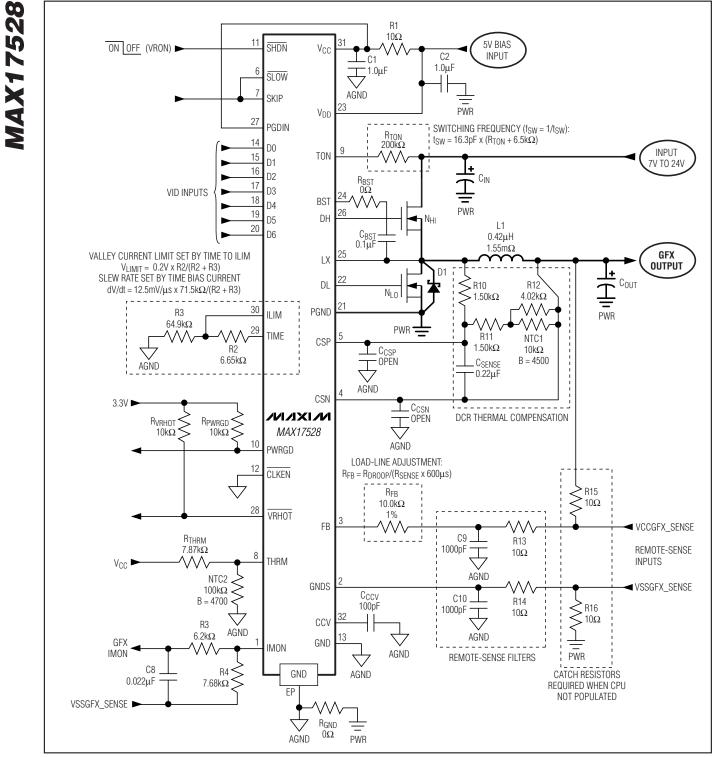

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100).  $T_A = 0^{\circ}C$  to +85°C, unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                  | SYMBOL | CONDITIONS                                                                                               |                                                                          | MIN  | ТҮР   | MAX   | UNITS |

|----------------------------|--------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|-------|-------|-------|

| PWM CONTROLLER             |        | ·                                                                                                        |                                                                          |      |       |       |       |

| Input-Voltage Range        |        | V <sub>CC</sub> , V <sub>DD</sub>                                                                        |                                                                          | 4.5  |       | 5.5   | V     |

|                            |        | Measured at FB with                                                                                      | DAC codes from<br>0.8125V to 1.5000V                                     | -0.5 |       | +0.5  | %     |

| DC Output-Voltage Accuracy |        | respect to GNDS;<br>includes load-<br>regulation error                                                   | DAC codes from<br>0.3750V to 0.8000V                                     | -7   |       | +7    | mV    |

|                            |        | (Note 3)                                                                                                 | DAC codes from 0V<br>to 0.3625V                                          | -20  |       | +20   | IIIV  |

| Boot Voltage               | VBOOT  | IMVP-6.5 (CLKEN pull                                                                                     | IMVP-6.5 ( $\overline{\text{CLKEN}}$ pullup to 3.3V with 1.9k $\Omega$ ) |      | 1.100 | 1.106 | V     |

| Line Regulation Error      |        | $V_{CC} = 4.5V$ to 5.5V, VI                                                                              | N = 4.5V to 26V                                                          |      | 0.1   |       | %     |

| GNDS Input Range           |        |                                                                                                          |                                                                          | -200 |       | +200  | mV    |

| GNDS Gain                  | AGNDS  | $\Delta V_{OUT}/\Delta V_{GNDS}$ , -200m'                                                                | $\Delta V_{OUT}/\Delta V_{GNDS}$ , -200mV $\leq V_{GNDS} \leq +200$ mV   |      | 1.00  | 1.03  | V/V   |

| GNDS Input Bias Current    | IGNDS  | $T_A = +25^{\circ}C$                                                                                     |                                                                          | -2   |       | +2    | μA    |

| TIME Voltage               | VTIME  | $V_{CC} = 4.5V$ to 5.5V,<br>ITIME = 28µA (RTIME =                                                        | $V_{CC} = 4.5V$ to 5.5V,<br>ITIME = 28µA (RTIME = 71.5k $\Omega$ )       |      | 2.000 | 2.015 | V     |

|                            |        | $R_{TIME} = 71.5 k\Omega (12.5)$                                                                         | mV/µs nominal)                                                           | -10  |       | +10   |       |

|                            |        | $R_{TIME} = 35.7 k\Omega (25m)$<br>178k $\Omega (5mV/\mu s nomin$                                        | · · · · · · · · · · · · · · · · · · ·                                    | -15  |       | +15   |       |

| TIME Slew-Rate Accuracy    |        | Soft-start and soft-shu<br>R <sub>TIME</sub> = $35.7$ k $\Omega$ (3.12<br>$178$ k $\Omega$ (0.625mV/µs n | 5mV/µs nominal) to                                                       | -20  |       | +20   | %     |

|                            |        | SLOW = GND,<br>R <sub>TIME</sub> = 35.7kΩ (12.5<br>178kΩ (2.5mV/μs nom                                   | ,                                                                        | -20  |       | +20   |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100).  $T_A = 0^{\circ}C$  to +85°C, unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                                                                                   | SYMBOL             | CON                                                                                                                                                                                                                                                                 | IDITIONS                                                | MIN  | ТҮР  | MAX  | UNITS |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|-------|

|                                                                                                                                             |                    | V <sub>IN</sub> = 12V,                                                                                                                                                                                                                                              | $R_{TON} = 96.75 k\Omega$                               | 142  | 167  | 192  |       |

| On-Time                                                                                                                                     | ton                | $V_{FB} = 1.2V$                                                                                                                                                                                                                                                     | $R_{TON} = 200 k\Omega$                                 | 300  | 333  | 366  | ns    |

|                                                                                                                                             |                    | (Note 4)                                                                                                                                                                                                                                                            | $R_{TON} = 303.25 k\Omega$                              | 425  | 500  | 575  |       |

| Minimum Off-Time                                                                                                                            | toff(MIN)          | Measured at DH (No                                                                                                                                                                                                                                                  | ote 4)                                                  |      | 300  | 375  | ns    |

| TON Shutdown Input Current                                                                                                                  |                    | $\overline{SHDN} = GND, V_{IN} = 5V, T_A = +25^{\circ}C$                                                                                                                                                                                                            | $= 26V, V_{CC} = V_{DD} = 0V \text{ or}$                |      | 0.01 | 1    | μA    |

| BIAS CURRENTS                                                                                                                               |                    | •                                                                                                                                                                                                                                                                   |                                                         |      |      |      | •     |

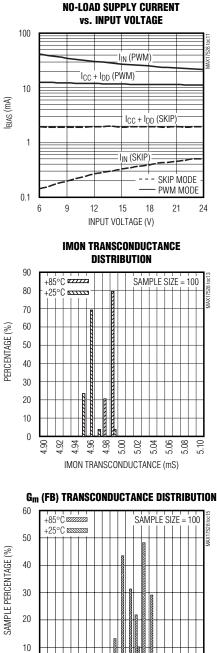

| Quiescent Supply Current (V <sub>CC</sub> )                                                                                                 | ICC                | Measured at V <sub>CC</sub> , V<br>above the regulation                                                                                                                                                                                                             | SKIP = 5V, FB forced<br>n point                         |      | 1.5  | 3    | mA    |

| Quiescent Supply Current (V <sub>DD</sub> )                                                                                                 | IDD                | Measured at V <sub>DD</sub> , S<br>FB forced above the<br>T <sub>A</sub> = +25°C                                                                                                                                                                                    |                                                         |      | 0.02 | 1    | μA    |

| Shutdown Supply Current (V <sub>CC</sub> )                                                                                                  |                    | Measured at V <sub>CC</sub> , S                                                                                                                                                                                                                                     | HDN = GND                                               |      | 15   | 30   | μA    |

| Shutdown Supply Current (V <sub>DD</sub> )                                                                                                  |                    | Measured at V <sub>DD</sub> , S                                                                                                                                                                                                                                     | $\overline{HDN} = GND, T_A = +25^{\circ}C$              |      | 0.01 | 1    | μA    |

| FAULT PROTECTION                                                                                                                            |                    |                                                                                                                                                                                                                                                                     |                                                         |      |      |      | 1     |

| Output Undervoltage-Protection<br>Threshold                                                                                                 | VUVP               | Measured at FB with output voltage                                                                                                                                                                                                                                  | h respect to unloaded                                   | -450 | -400 | -350 | mV    |

| Output Undervoltage<br>Propagation Delay                                                                                                    | tuvp               | FB forced 25mV bel                                                                                                                                                                                                                                                  | ow trip threshold                                       |      | 10   |      | μs    |

| IMVP-6.5 $\overline{\text{CLKEN}}$ Startup Delay<br>(Boot Time Period, $\overline{\text{CLKEN}}$ Pullup<br>to 3.3V with 1.9k $\Omega$ )     | tвоот              | IMVP-6.5: $\overline{\text{CLKEN}}$ pullup to 3.3V with 1.9k $\Omega$ ;<br>measured from the time when FB reaches<br>the boot target voltage (Note 3); the time<br>needed for FB to reach this target voltage is<br>based on the slew rate set by R <sub>TIME</sub> |                                                         | 20   | 60   | 100  | μs    |

|                                                                                                                                             |                    | IMVP-6.5: CLKEN pu<br>measured at startup<br>CLKEN goes low                                                                                                                                                                                                         | llup to 3.3V with 1.9k $\Omega$ ;<br>from the time when | 3    | 5    | 8    |       |

| PWRGD Startup Delay                                                                                                                         |                    | GMCH: CLKEN = GND; measured from the<br>time when FB reaches the target voltage (Note<br>3); the time needed for FB to reach this target<br>voltage is based on the slew rate set by RTIME                                                                          |                                                         | 3    | 5    | 8    | ms    |

| PWRGD and CLKEN (IMVP-6.5,<br>CLKEN Pullup to 3.3V with                                                                                     |                    | Measured at FB<br>with respect to<br>unloaded output                                                                                                                                                                                                                | Lower threshold,<br>falling edge<br>(undervoltage)      | -350 | -300 | -250 | mV    |

| 1.9kΩ) Threshold                                                                                                                            |                    | voltage, 15mV<br>hysteresis (typ)                                                                                                                                                                                                                                   | Upper threshold, rising edge (overvoltage)              | +150 | +200 | +250 |       |

| PWRGD and $\overline{\text{CLKEN}}$ (IMVP-6.5,<br>$\overline{\text{CLKEN}}$ Pullup to 3.3V with<br>1.9k $\Omega$ ) Transition Blanking Time | <sup>t</sup> BLANK | Measured from the time when FB reaches<br>the target voltage (Note 3) based on the<br>slew rate set by RTIME                                                                                                                                                        |                                                         |      | 20   |      | μs    |

| PWRGD and $\overline{\text{CLKEN}}$ (IMVP-6.5,<br>$\overline{\text{CLKEN}}$ Pullup to 3.3V with<br>1.9k $\Omega$ ) Delay                    |                    | FB forced 25mV outside the PWRGD<br>trip thresholds                                                                                                                                                                                                                 |                                                         |      | 10   |      | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100). **T<sub>A</sub> = 0°C to +85°C**, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                                    | SYMBOL             | CO                                                                | NDITIONS                                                     | MIN   | ТҮР  | MAX   | UNITS |

|--------------------------------------------------------------|--------------------|-------------------------------------------------------------------|--------------------------------------------------------------|-------|------|-------|-------|

| IMVP-6.5 CLKEN Output<br>Low Voltage                         |                    | IMVP-6.5: CLKEN p<br>I <sub>SINK</sub> = 3mA                      | ullup to 3.3V with 1.9k $\Omega$ ;                           |       |      | 0.4   | V     |

| IMVP-6.5 CLKEN High<br>Leakage Current                       |                    | IMVP-6.5: VPGDIN =                                                | = 5V, V <u>CLKEN</u> = 3.3V                                  |       | 2    | 4     | μA    |

| IMVP-6.5 CLKEN Shutdown<br>Leakage Current                   |                    | IMVP-6.5: VSHDN =                                                 | GND, V <u>CLKEN</u> = 3.3V                                   |       | 0.01 | 1     | μA    |

| PWRGD Output Low Voltage                                     |                    | I <sub>SINK</sub> = 3mA                                           |                                                              |       |      | 0.4   | V     |

| PWRGD Leakage Current                                        |                    | High state, PWRGD                                                 | forced to 5V, $T_A = +25^{\circ}C$                           |       |      | 1     | μA    |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold            | VUVLO(VCC)         | Rising edge, 65mV controller disabled                             | / typical hysteresis,<br>below this level                    | 4.05  | 4.27 | 4.48  | V     |

| CSN Discharge Resistance in UVLO and Shutdown                |                    | SHDN = GND and d<br>(not switching)                               | rivers disabled                                              |       | 8    |       | Ω     |

| THERMAL PROTECTION                                           |                    |                                                                   |                                                              |       |      |       | 1     |

| VRHOT Trip Threshold                                         |                    |                                                                   | M with respect to V <sub>CC</sub> ;<br>al hysteresis = 100mV | 29.2  | 30   | 30.8  | %     |

| VRHOT Delay                                                  | t <u>vrhot</u>     | THRM forced 25mV below the VRHOT trip threshold; falling edge     |                                                              |       | 10   |       | μs    |

| VRHOT Output On-Resistance                                   | RVRHOT             | Low state                                                         |                                                              |       | 2    | 8     | Ω     |

| VRHOT Leakage Current                                        | IVRHOT             | High state, $\overline{VRHOT}$ forced to 5V, $T_A = +25^{\circ}C$ |                                                              |       |      | 1     | μA    |

| THRM Input Leakage                                           | ITHRM              | $V_{THRM} = 0V$ to 5V, $T_A = +25^{\circ}C$                       |                                                              | -100  |      | +100  | nA    |

| Thermal-Shutdown Threshold                                   | TSHDN              | Typical hysteresis                                                | s = 15°C                                                     |       | +160 |       | °C    |

| VALLEY CURRENT LIMIT AND D                                   | ROOP               |                                                                   |                                                              |       |      |       |       |

| Current-Limit Threshold Voltage                              | V <sub>LIMIT</sub> | V <sub>CSP</sub> - V <sub>CSN</sub>                               | $V_{TIME} - V_{ILIM} = 100 mV$                               | 7     | 10   | 13    | mV    |

| (Positive Adjustable)                                        |                    | VCSP - VCSN                                                       | VTIME - VILIM = 500mV                                        | 45    | 50   | 55    | 1110  |

| Current-Limit Threshold Voltage<br>(Positive Default) Preset |                    | V <sub>CSP</sub> - V <sub>CSN</sub> , ILIM                        | = V <sub>CC</sub>                                            | 20    | 22.5 | 25    | mV    |

| Current-Limit Threshold Voltage<br>(Negative) Accuracy       | VLIMIT(NEG)        | V <sub>CSP</sub> - V <sub>CSN</sub> , nomi                        | nally -125% of V <sub>LIMIT</sub>                            | -4    |      | +4    | mV    |

| Current-Limit Threshold Voltage<br>(Zero Crossing)           | VZERO              | $V_{PGND}$ - $V_{LX}$ , SKIP = $V_{CC}$                           |                                                              |       | 1    |       | mV    |

| CSP, CSN Common-Mode<br>Input Range                          |                    |                                                                   |                                                              | 0     |      | 2     | V     |

| CSP, CSN Input Current                                       |                    | $T_A = +25^{\circ}C$                                              |                                                              | -0.2  |      | +0.2  | μA    |

| ILIM Input Current                                           |                    | $T_A = +25^{\circ}C$                                              |                                                              | -100  |      | +100  | nA    |

| DC Droop Amplifier (GMD) Offset                              |                    | (V <sub>CSP</sub> - V <sub>CSN</sub> ) at I <sub>FF</sub>         | B = 0                                                        | -0.75 |      | +0.75 | mV    |

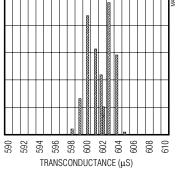

| DC Droop Amplifier (GMD)<br>Transconductance                 |                    |                                                                   | ; $V_{FB} = V_{CSN} = 0.45V$ to<br>CSN) = -15.0mV to +15.0mV | 592   | 600  | 608   | μS    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100). **TA = 0°C to +85°C**, unless otherwise specified. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                                           | SYMBOL               | со                                                                                | NDITIONS              | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------------------------|----------------------|-----------------------------------------------------------------------------------|-----------------------|------|------|------|-------|

| GATE DRIVERS                                        | •                    |                                                                                   |                       | •    |      |      | •     |

| DH Cata Driver On Registeres                        | Destroy              | BST - LX forced                                                                   | High state (pullup)   |      | 0.9  | 2.5  |       |

| DH Gate-Driver On-Resistance                        | R <sub>ON</sub> (DH) | to 5V                                                                             | Low state (pulldown)  |      | 0.7  | 2.0  |       |

| DL Gate-Driver On-Resistance                        | Bonie                | High state (pullup                                                                | )                     |      | 0.7  | 2.0  |       |

| DE Gale-Driver Off-Resistance                       | RON(DL)              | Low state (pulldow                                                                | vn)                   |      | 0.25 | 0.7  |       |

| DH Gate-Driver Source Current                       | IDH(SOURCE)          | DH forced to 2.5V                                                                 | BST - LX forced to 5V |      | 2.2  |      | A     |

| DH Gate-Driver Sink Current                         | IDH(SINK)            | DH forced to 2.5V                                                                 | BST - LX forced to 5V |      | 2.7  |      | A     |

| DL Gate-Driver Source Current                       | IDL(SOURCE)          | DL forced to 2.5V                                                                 |                       |      | 2.7  |      | A     |

| DL Gate-Driver Sink Current                         | IDL(SINK)            | DL forced to 2.5V                                                                 |                       |      | 8    |      | A     |

| Driver Propagation Dalay                            |                      | DH low to DL high                                                                 |                       |      | 20   |      |       |

| Driver Propagation Delay                            |                      | DL low to DH high                                                                 |                       |      | 20   |      | ns    |

| DL Transition Time                                  |                      | DL falling, C <sub>DL</sub> = 3                                                   | 3nF                   |      | 20   |      |       |

| DE Transition Time                                  |                      | DL rising, C <sub>DL</sub> = 3                                                    | nF                    |      | 20   |      | ns    |

| DH Transition Time                                  |                      | DH falling, C <sub>DH</sub> =                                                     | 3nF                   |      | 20   |      |       |

| DH Transition Time                                  |                      | DH rising, $C_{DH} = 3nF$                                                         |                       |      | 20   |      | ns    |

| Internal BST Switch On-Resistance                   | R <sub>BST</sub>     | $I_{BST} = 10 \text{mA}, V_{DD} = 5 \text{V} (\text{Note 6})$                     |                       |      | 10   | 20   |       |

| CURRENT MONITOR                                     |                      |                                                                                   |                       |      |      |      |       |

| Current-Monitor<br>Transconductance                 | G <sub>m(IMON)</sub> | $\Delta I_{\rm IMON} / \Delta (V_{\rm CSP} - V_{\rm CSN}) = 0.45 V \text{ to } 2$ |                       | 4.9  | 5.0  | 5.1  | mS    |

| Current-Monitor Offset<br>Referred to V(CSP, CSN)   |                      | $I_{IMON} = 0$                                                                    |                       | -1.0 |      | +1.0 | mV    |

| IMON Clamp Voltage                                  | VIMON                | IIMON = -1mA                                                                      |                       | 1.05 | 1.10 | 1.15 | V     |

| LOGIC AND I/O                                       | -                    |                                                                                   |                       | 1    |      |      | 1     |

| Logic-Input High Voltage                            | VIH                  | PGDIN                                                                             |                       | 2.3  |      |      | V     |

| Logic-Input Low Voltage                             | VIL                  | PGDIN                                                                             |                       |      |      | 1.0  | V     |

| Low-Voltage Logic-<br>Input High Voltage            | VIHLV                | SHDN, SKIP, SLOV                                                                  | ₩, D0–D6              | 0.67 |      |      | V     |

| Low-Voltage Logic-<br>Input Low Voltage             | VILLV                | SHDN, SKIP, SLOW, D0-D6                                                           |                       |      |      | 0.33 | V     |

| Logic-Input Current                                 |                      | PGDIN, SHDN, SKIP, SLOW, D0–D6 = 0 or 5V, $T_A = +25^{\circ}C$                    |                       | -1   |      | +1   | μA    |

| CLKEN Logic-Input High Voltage for IMVP-6.5 Startup |                      |                                                                                   |                       | 2.3  |      |      | V     |

| CLKEN Logic-Input Low Voltage for GMCH              |                      |                                                                                   |                       |      |      | 1.0  | V     |

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100).  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise specified.) (Note 2)

| PARAMETER                                                                                                                               | SYMBOL            | CONDI                                                                                                                                                             | TIONS                                | MIN   | MAX   | UNITS |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|-------|-------|

| PWM CONTROLLER                                                                                                                          |                   |                                                                                                                                                                   |                                      |       |       |       |

| Input-Voltage Range                                                                                                                     |                   | V <sub>CC</sub> , V <sub>DD</sub>                                                                                                                                 |                                      | 4.5   | 5.5   | V     |

|                                                                                                                                         |                   | Measured at FB with                                                                                                                                               | DAC codes from<br>0.8125V to 1.5000V | -0.75 | +0.75 | %     |

| DC Output-Voltage Accuracy                                                                                                              |                   | respect to GNDS;<br>includes load-<br>regulation error                                                                                                            | DAC codes from<br>0.3750V to 0.8000V | -10   | +10   |       |

|                                                                                                                                         |                   | (Note 3)                                                                                                                                                          | DAC codes from 0V<br>to 0.3625V      | -25   | +25   | mV    |

| Boot Voltage                                                                                                                            | VBOOT             | IMVP-6.5 (CLKEN pullu                                                                                                                                             | p to 3.3V with 1.9kΩ)                | 1.085 | 1.115 | V     |

| GNDS Input Range                                                                                                                        |                   |                                                                                                                                                                   |                                      | -200  | +200  | mV    |

| GNDS Gain                                                                                                                               | AGNDS             | $\Delta V_{OUT}/\Delta V_{GNDS}$ , -200m                                                                                                                          | $V \le V_{GNDS} \le +200 mV$         | 0.95  | 1.05  | V/V   |

| TIME Voltage                                                                                                                            | VTIME             | V <sub>CC</sub> = 4.5V to 5.5V,<br>I <sub>TIME</sub> = 28µA (R <sub>TIME</sub> =                                                                                  | = 71.5kΩ)                            | 1.98  | 2.02  | V     |

|                                                                                                                                         |                   | $R_{TIME} = 71.5 k\Omega (12.5)$                                                                                                                                  | mV/µs nominal)                       | -10   | +10   |       |

|                                                                                                                                         |                   | $R_{TIME} = 35.7$ kΩ (25m<br>178kΩ (5mV/µs nomir                                                                                                                  | ,                                    | -15   | +15   |       |

| TIME Slew-Rate Accuracy                                                                                                                 |                   | Soft-start and soft-shu<br>R <sub>TIME</sub> = $35.7$ k $\Omega$ (3.12<br>$178$ k $\Omega$ (0.625mV/µs n                                                          | 5mV/µs nominal) to                   | -20   | +20   | %     |

|                                                                                                                                         |                   | $\overline{\text{SLOW}} = \text{GND},$<br>$R_{\text{TIME}} = 35.7 \text{k}\Omega (12.5)$<br>$178 \text{k}\Omega (2.5 \text{mV/}\mu \text{s normalized})$          |                                      | -20   | +20   |       |

|                                                                                                                                         |                   |                                                                                                                                                                   | $R_{TON} = 96.75 k\Omega$            | 142   | 192   |       |

| On-Time                                                                                                                                 | ton               | $V_{IN} = 12V, V_{FB} = 1.2V$<br>(Note 4)                                                                                                                         | $R_{TON} = 200 k\Omega$              | 300   | 366   | ns    |

|                                                                                                                                         |                   |                                                                                                                                                                   | $R_{TON} = 303.25 k\Omega$           | 425   | 575   |       |

| Minimum Off-Time                                                                                                                        | toff(MIN)         | Measured at DH (Note                                                                                                                                              | e 4)                                 |       | 400   | ns    |

| BIAS CURRENTS                                                                                                                           |                   |                                                                                                                                                                   |                                      |       |       |       |

| Quiescent Supply Current (V <sub>CC</sub> )                                                                                             | ICC               | Measured at V <sub>CC</sub> , V <sub>SK</sub><br>FB forced above the r                                                                                            |                                      |       | 3     | mA    |

| FAULT PROTECTION                                                                                                                        |                   | ·                                                                                                                                                                 |                                      |       |       |       |

| Output Undervoltage-Protection<br>Threshold                                                                                             | Vuvp              | Measured at FB with respect to unloaded output voltage                                                                                                            |                                      | -460  | -340  | mV    |

| IMVP-6.5 $\overline{\text{CLKEN}}$ Startup Delay<br>(Boot Time Period, $\overline{\text{CLKEN}}$ Pullup<br>to 3.3V with 1.9k $\Omega$ ) | <sup>t</sup> BOOT | IMVP-6.5, $\overline{\text{CLKEN}}$ pulle<br>1.9k $\Omega$ ; measured from<br>reaches the boot targe<br>the time needed for FI<br>voltage is based on th<br>RTIME | 20                                   | 100   | μs    |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100). **T<sub>A</sub> = -40°C to +105°C**, unless otherwise specified.) (Note 2)

| PARAMETER                                                    | SYMBOL      | co                                                                                                                                                                                                               | NDITIONS                                                     | MIN  | MAX  | UNITS |

|--------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|-------|

|                                                              |             |                                                                                                                                                                                                                  | pullup to 3.3V with 1.9k $\Omega$ ; p from the time when     | 3    | 8    | ms    |

| PWRGD Startup Delay                                          |             | GMCH, <u>CLKEN</u> = GND; measured from the<br>time when FB reaches the target voltage<br>(Note 3); the time needed for FB to reach<br>this target voltage is based on the slew rate<br>set by R <sub>TIME</sub> |                                                              | 3    | 8    | μs    |

| PWRGD and CLKEN (IMVP-6.5,                                   |             | Measured at FB<br>with respect to                                                                                                                                                                                | Lower threshold, falling edge (undervoltage)                 | -360 | -240 | mV    |

| CLKEN Pullup to 3.3V with 1.9k $\Omega$ ) Threshold          |             | unloaded output<br>voltage, 15mV<br>hysteresis (typ)                                                                                                                                                             | Upper threshold, rising edge (overvoltage)                   | +140 | +260 |       |

| IMVP-6.5 CLKEN Output<br>Low Voltage                         |             | IMVP-6.5: $\overline{\text{CLKEN}}$<br>1.9k $\Omega$ , I <sub>SINK</sub> = 3m                                                                                                                                    | pullup to 3.3V with<br>nA                                    |      | 0.4  | V     |

| IMVP-6.5 CLKEN High<br>Leakage Current                       |             | IMVP-6.5 = PGDIN                                                                                                                                                                                                 | $IMVP-6.5 = PGDIN = 5V,  V_{\overline{CLKEN}} = 3.3V$        |      | 4    | μA    |

| PWRGD Output Low Voltage                                     |             | I <sub>SINK</sub> = 3mA                                                                                                                                                                                          |                                                              |      | 0.4  | V     |

| V <sub>CC</sub> Undervoltage Lockout<br>(UVLO) Threshold     | VUVLO(VCC)  | Rising edge, 65m<br>controller disable                                                                                                                                                                           | V typical hysteresis,<br>d below this level                  | 4.0  | 4.5  | V     |

| THERMAL PROTECTION                                           |             |                                                                                                                                                                                                                  |                                                              |      |      |       |

| VRHOT Trip Threshold                                         |             |                                                                                                                                                                                                                  | M with respect to V <sub>CC</sub> ;<br>al hysteresis = 100mV | 29   | 31   | %     |

| VRHOT Output On-Resistance                                   | RVRHOT      | Low state                                                                                                                                                                                                        |                                                              |      | 8    | Ω     |

| VALLEY CURRENT LIMIT AND D                                   | ROOP        |                                                                                                                                                                                                                  |                                                              |      |      |       |

| Current-Limit Threshold Voltage                              | VLIMIT      | VCSP - VCSN                                                                                                                                                                                                      | V <sub>TIME</sub> - V <sub>ILIM</sub> = 100mV                | 7    | 13   | mV    |

| (Positive Adjustable)                                        | ↓ LIIVII I  |                                                                                                                                                                                                                  | VTIME - VILIM = 500mV                                        | 45   | 55   |       |

| Current-Limit Threshold Voltage<br>(Positive Default Preset) |             | V <sub>CSP</sub> - V <sub>CSN</sub> , ILIM = V <sub>CC</sub>                                                                                                                                                     |                                                              | 20   | 25   | mV    |

| Current-Limit Threshold Voltage<br>(Negative) Accuracy       | VLIMIT(NEG) | $V_{\mbox{CSP}}$ - $V_{\mbox{CSN}}$ , nominally -125% of $V_{\mbox{LIMIT}}$                                                                                                                                      |                                                              | -5   | +5   | mV    |

| CSP, CSN Common-Mode<br>Input Range                          |             |                                                                                                                                                                                                                  |                                                              | 0    | 2    | V     |

| DC Droop Amplifier (GMD) Offset                              |             | (V <sub>CSP</sub> - V <sub>CSN</sub> ) at I <sub>F</sub>                                                                                                                                                         | B = 0                                                        | -1.0 | +1.0 | mV    |

| DC Droop Amplifier (GMD)<br>Transconductance                 |             | $\Delta I_{FB}/\Delta (V_{CSP} - V_{CSN}); FB = V_{CSN} = 0.45V \text{ to}$<br>2.0V, and (V_{CSP} - V_{CSN}) = -15.0mV to<br>+15.0mV                                                                             |                                                              | 588  | 612  | μS    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{DD} = V_{CC} = 5V$ ,  $\overline{CLKEN}$  pullup to 3.3V with  $1.9k\Omega$ ,  $\overline{SHDN} = \overline{SLOW} = ILIM = PGDIN = V_{CC}$ , SKIP = GNDS = PGND = GND,  $V_{FB} = V_{CSP} = V_{CSN} = 1.200V$ , D0–D6 set for 1.20V (D0–D6 = 0001100). **T<sub>A</sub> = -40°C to +105°C**, unless otherwise specified.) (Note 2)

| PARAMETER                                              | SYMBOL                | C                                                                                 | CONDITIONS              |      | ТҮР | MAX  | UNITS    |

|--------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------|-------------------------|------|-----|------|----------|

| GATE DRIVERS                                           |                       | ·                                                                                 |                         | ·    |     |      |          |

| DH Gate-Driver On-Resistance                           | RONIDUN               | BST - LX forced                                                                   | High state (pullup)     |      |     | 2.5  |          |

| Dh'dale-Dhver Oh-nesistance                            | R <sub>ON</sub> (DH)  | to 5V                                                                             | Low state (pulldown)    |      |     | 2.0  |          |

| DL Gate-Driver On-Resistance                           | RONIDU                |                                                                                   | High state (pullup)     |      |     | 2.0  |          |

| De Gale-Driver On-Nesistance                           | Ron(dl)               |                                                                                   | Low state (pulldown)    |      |     | 0.7  |          |

| Internal BST Switch<br>On-Resistance                   | R <sub>BST</sub>      | $I_{BST} = 10 \text{mA}, V_{DI}$                                                  | ) = 5V                  |      |     | 20   |          |

| CURRENT MONITOR                                        |                       |                                                                                   |                         | •    |     |      | <u> </u> |

| Current-Monitor<br>Transconductance                    | G <sub>m</sub> (IMON) | $\Delta I_{IMON}/\Delta (V_{CSP} - V_{CSN}),$<br>V <sub>CSN</sub> = 0.45V to 2.0V |                         | 4.9  |     | 5.1  | mS       |

| Current-Monitor Offset<br>Referred to V(CSP, CSN)      |                       | I <sub>IMON</sub> = 0                                                             |                         | -1.5 |     | +1.5 | mV       |

| I <sub>MON</sub> Clamp Voltage                         | VIMON                 | IIMON = -1mA                                                                      |                         | 1.05 |     | 1.15 | V        |

| LOGIC AND I/O                                          |                       | ·                                                                                 |                         | ·    |     |      |          |

| Logic-Input High Voltage                               | VIH                   | PGDIN                                                                             |                         | 2.3  |     |      | V        |

| Logic-Input Low Voltage                                | VIL                   | PGDIN                                                                             |                         |      |     | 1.0  | V        |

| Low-Voltage Logic-<br>Input High Voltage               | VIHLV                 | SHDN, SKIP, SLO                                                                   | SHDN, SKIP, SLOW, D0-D6 |      |     |      | V        |

| Low-Voltage Logic-<br>Input Low Voltage                | VILLV                 | SHDN, SKIP, SLOW, D0–D6                                                           |                         |      |     | 0.33 | V        |

| CLKEN Logic-Input High Voltage<br>for IMVP-6.5 Startup |                       |                                                                                   |                         | 2.3  |     |      | V        |

| CLKEN Logic-Input Low Voltage<br>for GMCH              |                       |                                                                                   |                         |      |     | 1.0  | V        |

Note 2: Limits are 100% production tested at  $T_A = +25^{\circ}$ C. Maximum and minimum limits over temperature are guaranteed by design and characterization.

Note 3: The equation for the target voltage  $\mathsf{V}_{\mathsf{TARGET}}$  is:

V<sub>TARGET</sub> = the slew-rate-controlled version of V<sub>DAC</sub>, where V<sub>DAC</sub> = 0V for shutdown, V<sub>DAC</sub> = V<sub>BOOT</sub> (IMVP-6.5) or V<sub>VID</sub> (GMCH) during startup, and V<sub>DAC</sub> = V<sub>VID</sub> otherwise (the V<sub>VID</sub> voltages for all possible VID codes are given in Table 2). In pulse-skipping mode, the output rises by approximately 1.5% when transitioning from continuous conduction to no load. **Note 4:** On-time and minimum off-time specifications are measured from 50% to 50% at the DH pin, with LX forced to 0V, BST forced

to 5V, and a 500pF capacitor from DH to LX to simulate external MOSFET gate capacitance. Actual in-circuit times can be different due to MOSFET switching speeds.

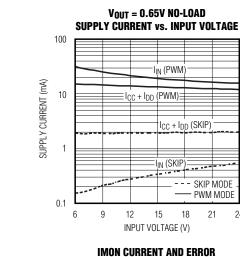

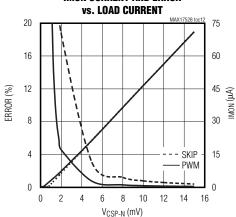

#### **Typical Operating Characteristics**

**0.9V OUTPUT EFFICIENCY** 0.9V OUTPUT VOLTAGE 0.65V OUTPUT EFFICIENCY vs. LOAD CURRENT vs. LOAD CURRENT vs. LOAD CURRENT 0.92 100 100 SKIP MODE SKIP MODE PWM MODE 12V 90 90 0.90 OUTPUT VOLTAGE (V) 7٧ EFFICIENCY (%) EFFICIENCY (%) 80 80 0.88 PWM MODE 70 70 20\ 0.86 60 60 SKIP MODE PWM MODE 50 50 0.84 5 20 0.01 0.1 10 100 0 10 15 25 0.01 0.1 10 1 1 LOAD CURRENT (A) LOAD CURRENT (A) LOAD CURRENT (A) **0.65V OUTPUT VOLTAGE OUTPUT EFFICIENCY OUTPUT VOLTAGE** vs. LOAD CURRENT vs. LOAD CURRENT vs. LOAD CURRENT 0.67 100 1.12 SKIP MODE PWM MODE 1.10 90 0.66 SKIP MODE () 1.08 1.06 1.04 1.04 SKIP MODE 7V OUTPUT VOLTAGE (V) EFFICIENCY (%) 80 0.65 PWM MODE 70 0.64 PWM MODE 1.02 20 0.63 60 1.00 ; 0.62 50 0.98 0 2 4 6 8 10 0.01 0.1 10 0 2 4 6 8 10 1 LOAD CURRENT (A) LOAD CURRENT (A) LOAD CURRENT (A) SWITCHING FREQUENCY **SWITCHING FREQUENCY** VOUT = 0.9V NO-LOAD **SUPPLY CURRENT vs. INPUT VOLTAGE** vs. LOAD CURRENT vs. LOAD CURRENT 100 500 300 SKIP MODE 450 I<sub>IN</sub> (PWM) PWM MODE 250 400 ICC + IDD (PWM) SWITCHING FREQUENCY (kHz) SWITCHING FREQUENCY (kHz) I I I I PWM MODE SUPPLY CURRENT (mA) 350 200 10 300 ICC + IDD (SKIP) 250 150 200 100 1 150 I<sub>IN</sub> (SKIP  $V_{OUT} = 0.9V$ SKIP MODE 100 50 SKIP MODE 50 PWM MODE 0 0 0.1 0.01 0.1 10 100 0.01 10 6 9 12 15 18 21 24 1 0.1 1 LOAD CURRENT (A) INPUT VOLTAGE (V) INPUT VOLTAGE (V)

**MAX17528**

$(T_A = +25^{\circ}C)$ , unless otherwise noted. Circuit of Figure 1.)

SKIP MODE

PWM MODE

21

24

18

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C)$ , unless otherwise noted. Circuit of Figure 1.)

0

M/X/M

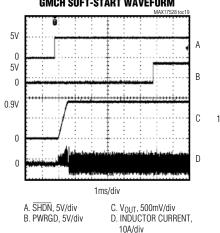

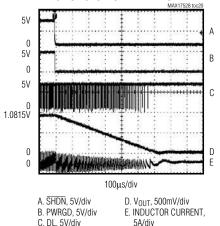

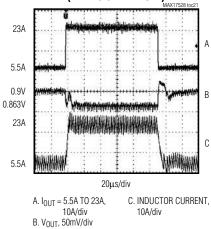

**IMVP-6.5 SOFT-START IMVP-6.5 SOFT-START** WAVEFORM (UP TO CLKEN) WAVEFORM (UP TO PWRGD) **IMVP-6.5 SHUTDOWN WAVEFORM** 5V 5V 5V А А 0 5V 0 Λ В 3.3V 5V В 0 0 5V 0 В 5V С С 0 0 1V 1V 5V С D D 0 0.9V 0 Ε 0 0 D Ε 0 0 1ms/div 200µs/div 100µs/div C. V<sub>OUT</sub>, 500mV/div D. INDUCTOR CURRENT, 10A/div D. V<sub>OUT</sub>, 500mV/div E. INDUCTOR CURRENT, A. SHDN, 5V/div A. SHDN, 5V/div A. SHDN, 5V/div E. DL, 5V/div B. PWRGD, 5V/div C. CLKEN, 5V/div B. CLKEN, 5V/div B. CLKEN, 3.3V/div D. V<sub>OUT</sub>, 1V/div 10A/div C. PWRGD, 5V/div F. INDUCTOR CURRENT, 5A/div LOAD-TRANSIENT RESPONSE **GMCH SHUTDOWN WAVEFORM** (IMVP-6.5 HFM MODE) **GMCH SOFT-START WAVEFORM** 5V 23A 5V А A 0 A 0 5V В

### \_Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted. Circuit of Figure 1.)$

DPRSLPVR = HIGH, SLOW = LOW, LOAD-TRANSIENT RESPONSE **VID5 TRANSITION** LOAD-TRANSIENT RESPONSE (IMVP-6.5 LFM MODE) , I, 8A 9.5A 1V А A 1.5A 0 3.5A MMMMM 1V 1.0815V www 0.8375V В В 0.825V R 1.03V www.weynwww 0.6V 8A С С 9.5A С 1.5A 0 3.5A 40µs/div 20µs/div 20µs/div A.  $I_{OUT} = 3.5A \text{ TO } 9.5A$ , A.  $I_{OUT} = 1.5A \text{ TO 8A},$ C. INDUCTOR CURRENT, A. VID5, 1V/div C. INDUCTOR CURRENT, C. INDUCTOR CURRENT, 5A/div 5A/div B. V<sub>OUT</sub>, 200mV/div 10A/div 5A/div 10A/div B. V<sub>OUT</sub>, 50mV/div B. V<sub>OUT</sub>, 20mV/div  $I_{OUT} = 1A$ **D2 50mV DYNAMIC VID** DPRSLPVR = HIGH, SLOW = HIGH, D0 12.5mV DYNAMIC VID CODE CHANGE **CODE CHANGE VID5 TRANSITION** 5V 5V 1V А А A 0 0 0 1V В 0.9V В 0.9V В 0.8875V 0.85V 0.6V С С 0 С Λ 0 10µs/div 10µs/div 40µs/div A. VID5, 1V/div C. INDUCTOR CURRENT, A. D0, 5V/div C. INDUCTOR CURRENT, A. D2, 5V/div C. INDUCTOR CURRENT,

B. VOUT, 20mV/div

2A/div

B. VOUT, 50mV/div

**Typical Operating Characteristics (continued)** (T<sub>A</sub> = +25°C, unless otherwise noted. Circuit of Figure 1.)

2A/div

B. V<sub>OUT</sub>, 200mV/div

$I_{OUT} = 1A$

10A/div

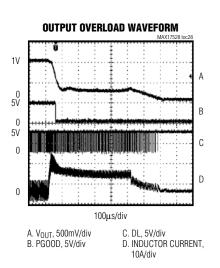

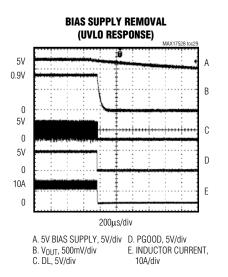

### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted. Circuit of Figure 1.)$

|      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | Current Monitor Output. The MAX17528 IMON output sources a current that is directly proportional to the current-sense voltage as defined by:                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | $I_{IMON} = G_{m(IMON)} \times (V_{CSP} - V_{CSN})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | where $G_{m(IMON)} = 5mS$ (typ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | The IMON current is unidirectional (sources current out of IMON only) for positive current-sense values. For negative current-sense voltages, the IMON current is zero. Connect an external resistor between IMON and VSS_SENSE to create the desired IMON gain based on the following equation:                                                                                                                                                                                                                                                                                                              |

| IMON | $R_{IMON} = 0.999V/(IMAX \times R_{SENSE} \times G_{m(IMON)})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | where IMAX is defined in the <i>Current Monitor (IMON)</i> section of the Intel IMVP-6.5 specification and based on discrete increments (20A, 30A, 40A, etc.,), $R_{SENSE}$ is the typical effective value of the current-sense element (sense resistor or inductor DCR) that is used to provide the current-sense voltage, and $G_{m(IMON)}$ is the typical transconductance amplifier gain as defined in the <i>Electrical Characteristics</i> table.                                                                                                                                                       |

|      | The IMON voltage is internally clamped to a maximum of 1.1V (typ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | The transconductance amplifier and voltage clamp are internally compensated, so IMON cannot directly drive large capacitance values. To filter the IMON signal, use an RC filter as shown in                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Figure 1. IMON is pulled to ground when the MAX17528 is in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GNDS | Remote Ground-Sense Input. Connect directly to the CPU or GMCH V <sub>SS</sub> sense pin (ground sense) or directly to the ground connection of the load. GNDS internally connects to a transconductance amplifier that adjusts the feedback voltage, compensating for voltage drops between the regulator's ground and the processor's ground.                                                                                                                                                                                                                                                               |

|      | Output of the Voltage-Positioning Transconductance Amplifier. Connect a resistor, R <sub>FB</sub> , between FB and the positive side of the feedback remote sense to set the steady-state droop based on the                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | voltage-positioning gain requirement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | $R_{FB} = R_{DROOP}/(R_{SENSE} \times GMD)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FB   | where $R_{DROOP}$ is the desired voltage-positioning slope, GMD = 600µS typ and $R_{SENSE}$ is the value of the current-sense resistor that is used to provide the (CSP, CSN), current-sense voltage. If lossless sensing is used, $R_{SENSE} = R_L$ . In this case, consider using a thermistor-resistor network to minimize the temperature dependence of the voltage-positioning slope. Droop can be disabled by shorting FB to the positive remote-sense point, but doing so increases the minimum ESR requirement of the output capacitance for stability, and FB might therefore need to be driven by a |

|      | carefully designed feed-forward network. FB is high impedance in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

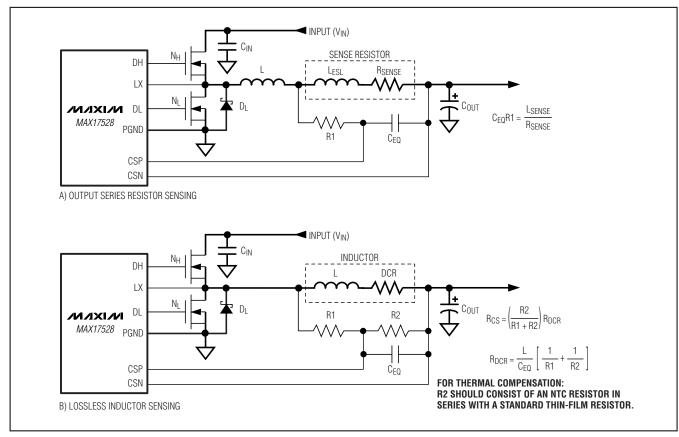

| CSN  | Negative Inductor Current-Sense Input. Connect CSN to the negative terminal of the inductor current-sensing resistor or directly to the negative terminal of the inductor if the lossless DCR sensing method is used (see Figure 4).<br>Under V <sub>CC</sub> UVLO conditions and after soft-shutdown is completed, CSN is internally pulled to GND                                                                                                                                                                                                                                                           |

|      | through a 10 $\Omega$ FET to discharge the output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CSP  | Positive Inductor Current-Sense Input. Connect CSP to the positive terminal of the inductor current-<br>sensing resistor or directly to the positive terminal of the filtering capacitor used when the<br>lossless DCR sensing method is used (see Figure 4).                                                                                                                                                                                                                                                                                                                                                 |

| SLOW | Active-Low Slew-Rate Select Input. This 1.0V logic input signal selects between the nominal and slow (half of nominal rate) slew rates. When SLOW is forced high, the selected nominal slew rate is set by the time resistance. When SLOW is forced low, the slew rate is reduced to half of the nominal slew rate.<br>For IMVP-6.5 applications (CLKEN pullup to 3.3V with 1.9k $\Omega$ ), the fast slew rate is not needed.<br>Connect SLOW to GND.<br>For GMCH 2009 applications (CLKEN = GND), connect to the system GFXDPRSLPVR signal.                                                                 |

|      | GNDS<br>FB<br>CSN<br>CSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### \_Pin Description (continued)