Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

#### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

The MAX1937/MAX1938/MAX1939 comprise a family of synchronous, two-phase, step-down controllers capable of delivering load currents up to 60A. The controllers utilize Quick-PWM™ control architecture in conjunction with active load-current voltage positioning. Quick-PWM control provides instantaneous load-step response, while programmable voltage positioning allows the converter to utilize full transient regulation limits, reducing the output capacitance requirement. The two phases operate 180° out-of-phase with an effective 500kHz switching frequency, thus reducing input and output current ripple, as well as reducing input filter capacitor requirements.

19-2498; Rev 1; 10/02

EVALUATION KIT **AVAILABLE**

The MAX1937/MAX1938/MAX1939 are compliant with AMD Hammer, Intel®, Voltage-Regulator Module (VRM) 9.0/9.1, and AMD Athlon™ Mobile VID code specifications (see Table 1 for VID codes). The internal DAC provides ultra-high accuracy of ±0.75%. A controlled VID voltage transition is implemented to minimize both undervoltage and overvoltage overshoot during VID input change.

Remote sensing is available for high output-voltage accuracy. The MOSFET switches are driven by a 6V gate-drive circuit to minimize switching and crossover conduction losses to achieve efficiency as high as 90%. The MAX1937/MAX1938/MAX1939 feature cycleby-cycle current limit to ensure that the current limit is not exceeded. Crowbar protection is available to protect against output overvoltage.

#### **Applications**

Notebook and Desktop Computers Servers and Workstations **Blade Servers High-End Switches**

**High-End Routers**

Macro Base Stations

Typical Application Circuits and Functional Diagram appear at end of data sheet.

Quick-PWM is a trademark of Maxim Integrated Products, Inc. Athlon is a trademark of Advanced Micro Devices, Inc. Intel is a registered trademark of Intel Corp.

#### **Features**

- ♦ ±0.75% Output Voltage Accuracy

- ♦ Instant Load-Transient Response

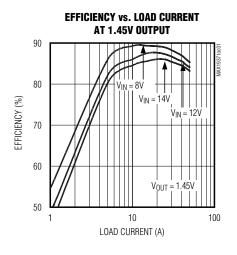

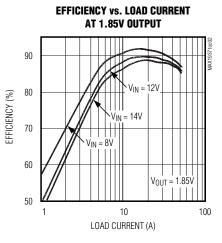

- ♦ Up to 90% Efficiency Eliminates Heatsinks

- ♦ Up to 60A Output Current

- ♦ 8V to 24V Input Range

- ♦ User-Programmable Voltage Positioning

- ♦ Controlled VID Voltage Transition

- ♦ 500kHz Effective Switching Frequency

- **♦ MAX1937: AMD Hammer Compatible**

- MAX1938: Intel VRM 9.0/9.1 Compatible

- ♦ MAX1939: AMD Athlon Mobile Compatible

- ♦ Soft-Start

- ♦ Power-Good (PWRGD) Output

- ♦ Cycle-by-Cycle Current Limit

- ♦ Output Overvoltage Protection (OVP)

- ♦ RDS(ON) or RSENSE Current Sensing

- ♦ Remote Voltage Sensing

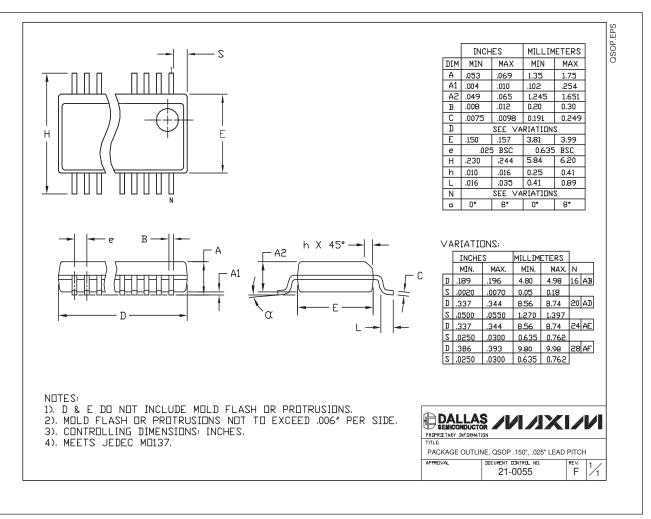

- ♦ 28-Pin QSOP Package

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1937EEI | -40°C to +85°C | 28 QSOP     |

| MAX1938EEI | -40°C to +85°C | 28 QSOP     |

| MAX1939EEI | -40°C to +85°C | 28 QSOP     |

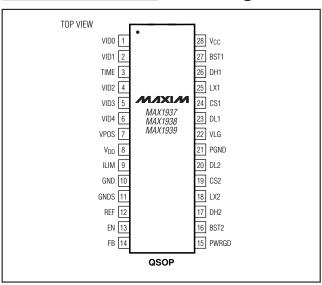

#### **Pin Configuration**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND      | 0.3V to +28V                    | DH:    |

|-----------------------------|---------------------------------|--------|

| VDD, PWRGD, ILIM, FB to GND | 0.3V to +6V                     | DH     |

| EN, GNDS, VPOS, REF, VID_,  |                                 | $DL^2$ |

| TIME to GND                 | 0.3V to V <sub>VDD</sub> + 0.3V | Cor    |

| PGND to GND                 |                                 | 2      |

| CS1, CS2 to GND             | 2V to +28V                      | Оре    |

| VLG to GND                  | 0.3V to +7V                     | Jun    |

| BST1, BST2 to GND           | 0.3V to +35V                    | Stor   |

| LX1 to BST1                 | 7V to +0.3V                     | Lea    |

| LX2 to BST2                 | 7V to +0.3V                     |        |

|                             |                                 |        |

| DH1 to LX1                           | 0.3V to V <sub>BST1</sub> + 0.3V |

|--------------------------------------|----------------------------------|

| DH2 to LX2                           | 0.3V to V <sub>BST2</sub> + 0.3V |

| DL1, DL2 to PGND                     | 0.3V to V <sub>VLG</sub> + 0.3V  |

| Continuous Power Dissipation (TA = - | +70°C)                           |

| 28-Pin QSOP (derate 20.8mW/°C a      | above +70°C)860.2mW              |

| Operating Temperature Range          | 40°C to +85°C                    |

| Junction Temperature                 | +150°C                           |

| Storage Temperature Range            |                                  |

| Lead Temperature (soldering, 10s)    | +300°C                           |

|                                      |                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(VCC = 12V, V_{EN} = V_{VDD} = 5V, PGND = GNDS = GND = 0, VID_ = GND, C_{VPOS} = 47pF, C_{REF} = 0.1\mu F, V_{ILIM} = 1V, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                | CONDITIONS                                                               | MIN      | TYP   | MAX   | UNITS |

|------------------------------------------|--------------------------------------------------------------------------|----------|-------|-------|-------|

| GENERAL                                  |                                                                          | <b>.</b> |       |       | I.    |

| V 0 " D                                  | MAX1937                                                                  | 6        |       | 24    |       |

| VCC Operating Range                      | MAX1938/MAX1939                                                          | 8        |       | 24    | V     |

| V <sub>DD</sub> Operating Range          |                                                                          | 4.5      | 5     | 5.5   | V     |

| VLG Operating Range                      | V <sub>VLG</sub> > V <sub>VDD</sub>                                      | 4.5      |       | 6.5   | V     |

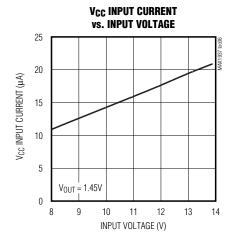

| V <sub>CC</sub> Operating Supply Current | FB above threshold (no switching)                                        |          | 20    | 40    | μΑ    |

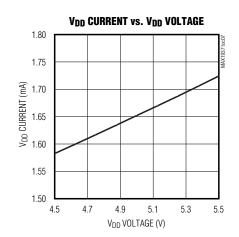

| V <sub>DD</sub> Operating Supply Current | FB above threshold (no switching)                                        |          | 1.4   | 2.5   | mA    |

| VLG Operating Supply Current             | FB above threshold (no switching)                                        | 20       |       | 60    | μΑ    |

| V <sub>CC</sub> Shutdown Current         | EN = GND                                                                 |          | <1    | 5     | μΑ    |

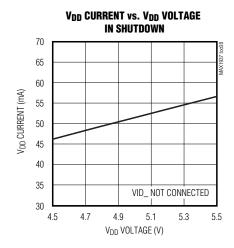

| V <sub>DD</sub> Shutdown Current         | EN = GND, VID_ not connected                                             |          | 50    | 100   | μΑ    |

| VLG Shutdown Current                     | EN = GND                                                                 |          | <1    | 5     | μΑ    |

| TIME Output Voltage                      |                                                                          | 1.96     | 2.00  | 2.04  | V     |

| ILIM Input Bias                          | V <sub>ILIM</sub> = 1.5V                                                 | -250     |       | +250  | nA    |

| VPOS Output Voltage                      | S Output Voltage CS_= GND, VPOS connected to REF through a 75kΩ resistor |          | 2.0   | 2.04  | V     |

| REFERENCE                                |                                                                          | <b>.</b> |       |       | I.    |

| Reference Voltage                        | -50μA ≤ I <sub>REF</sub> ≤ 50μA                                          | 1.987    | 2.000 | 2.013 | V     |

| SOFT-START                               |                                                                          |          |       |       |       |

|                                          | MAX1937                                                                  | 1.1      |       | 5.5   |       |

| Ramp Period                              | MAX1938                                                                  | 1.5      |       | 6.2   | ms    |

|                                          | MAX1939                                                                  | 1.3      |       | 6.5   |       |

| Soft-Start Voltage Step                  |                                                                          |          | 25    |       | mV    |

| ERROR AMPLIFIER                          |                                                                          |          |       |       |       |

| FB Input Resistance                      | Resistance from FB to GND                                                |          | 180   |       | kΩ    |

| GNDS Input Bias Current                  |                                                                          | -5       |       | +5    | μΑ    |

| Output Regulation Voltage<br>Accuracy    |                                                                          | -0.75    |       | +0.75 | %     |

\_\_\_ /N/XI/M

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 12V, V_{EN} = V_{VDD} = 5V, PGND = GNDS = GND = 0, VID_ = GND, C_{VPOS} = 47pF, C_{REF} = 0.1\mu F, V_{ILIM} = 1V, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                | CONDITIONS                                                                            |                                                               |       | TYP   | MAX   | UNITS                                 |  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|-------|-------|-------|---------------------------------------|--|

| FAULT PROTECTION                                         | 1                                                                                     |                                                               | •     |       |       |                                       |  |

| V <sub>DD</sub> Undervoltage Lockout<br>(UVLO) Threshold | Rising or falling VD                                                                  | D                                                             | 4.00  | 4.25  | 4.45  | V                                     |  |

| V <sub>DD</sub> UVLO Hysteresis                          |                                                                                       |                                                               |       | 80    |       | mV                                    |  |

| VLG UVLO Threshold                                       | Rising or falling VL                                                                  | G                                                             | 4.00  | 4.25  | 4.45  | V                                     |  |

| VLG UVLO Hysteresis                                      |                                                                                       |                                                               |       | 40    |       | mV                                    |  |

| Thermal Shutdown                                         | Rising temperature                                                                    | e, typical hysteresis = 15°C                                  |       | 160   |       | °C                                    |  |

| Deference LIVI O Threehold                               | Rising edge                                                                           |                                                               |       | 1.600 |       | V                                     |  |

| Reference UVLO Threshold                                 | Falling edge                                                                          |                                                               |       | 1.584 |       | V                                     |  |

| Output Overvoltage Fault                                 | Distance and falling                                                                  | MAX1937/MAX1938                                               | 1.97  | 2.00  | 2.03  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

| Threshold                                                | Rising and falling                                                                    | MAX1939                                                       | 2.215 | 2.250 | 2.285 | V                                     |  |

| Output UVLO Threshold                                    | Rising and falling pregulation voltage                                                | percentage of the nominal                                     | 65    | 70    | 75    | %                                     |  |

| CURRENT LIMIT                                            |                                                                                       |                                                               |       |       |       |                                       |  |

| Current-Limit Threshold                                  | PGND to CS_, V <sub>ILIM</sub> = 1.5V                                                 |                                                               |       | 150   | 165   | mV                                    |  |

|                                                          | PGND to CS_, V <sub>ILIM</sub> = 1V                                                   |                                                               |       | 100   | 110   |                                       |  |

|                                                          | PGND to CS_, V <sub>ILI</sub>                                                         | M = 0.5V                                                      | 45    | 50    | 55    |                                       |  |

| CS Input Offset Voltage                                  | CS_ = GND                                                                             |                                                               | -3    |       | +3    | mV                                    |  |

| CS_ Input Bias Current                                   | CS_ = GND                                                                             |                                                               | -5    |       | +5    | μΑ                                    |  |

| VOLTAGE POSITIONING                                      |                                                                                       |                                                               |       |       |       |                                       |  |

| VPOS Input Offset Voltage                                |                                                                                       |                                                               | -3    |       | +3    | mV                                    |  |

| VPOS Gain                                                | From CS_ to FB; V                                                                     | $_{CS1}$ , $V_{CS2} = 0$ , -100mV; $R_{VPOS} = 75$ k $\Omega$ | 72.5  | 75.0  | 77.5  | %/V                                   |  |

| VPOS Gain                                                | From CS1, CS2 to FB; $V_{CS1}$ , $V_{CS2}$ = +13mV, -113mV; $R_{VPOS}$ = 75k $\Omega$ |                                                               |       | 75    | 82    | %/V                                   |  |

| TIMER AND DRIVERS                                        | <u>.</u>                                                                              |                                                               |       |       |       |                                       |  |

| On-Time                                                  | LX1 = LX2 = CS1 = CS2 = GND, V <sub>FB</sub> = 1.5V                                   |                                                               |       | 525   | 630   | ns                                    |  |

| Minimum Off-Time                                         | DH1 low to DH2 hi                                                                     | DH1 low to DH2 high, and DH2 low to DH1 high                  |       |       | 390   | ns                                    |  |

|                                                          | MAX1                                                                                  |                                                               |       | 60    |       |                                       |  |

| Brook Boforo Mako Timo                                   | DH_ low to DL_ hig                                                                    | MAX1939                                                       |       | 60    |       | ns                                    |  |

| Break-Before-Make Time                                   | DI Joye to DU 5:                                                                      | MAX1937/MAX1938                                               |       | 85    |       |                                       |  |

|                                                          | DL_ low to DH_ high MAX1939                                                           |                                                               |       | 70    |       |                                       |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 12V, V_{EN} = V_{VDD} = 5V, PGND = GNDS = GND = 0, VID_ = GND, C_{VPOS} = 47pF, C_{REF} = 0.1\mu F, V_{ILIM} = 1V, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                       |                                               | CONDITIONS                              | MIN  | TYP   | MAX  | UNITS |

|---------------------------------|-----------------------------------------------|-----------------------------------------|------|-------|------|-------|

| DH_ On-Resistance in Low State  | V <sub>BST1</sub> = V <sub>BST2</sub> = 6V,   | LX1 = LX2 = GND                         |      | 1.5   | 3.0  | Ω     |

| DH_ On-Resistance in High State | V <sub>BST</sub> _ = 6V, LX_ = G1             | ND                                      |      | 1.5   | 3.0  | Ω     |

| DL_ On-Resistance in Low State  |                                               |                                         |      | 0.5   | 1.7  | Ω     |

| DL_ On-Resistance in High State |                                               |                                         |      | 1.5   | 3.0  | Ω     |

| BST_ Leakage Current            | V <sub>BST_</sub> = 30V, V <sub>LX_</sub> = 2 | 24V                                     |      |       | 50   | μΑ    |

| LX_ Leakage Current             | $V_{BST_{}} = 30V, V_{LX_{}} = 30V$           | 24V                                     |      |       | 50   | μΑ    |

| EN AND VID                      |                                               |                                         |      |       |      |       |

| Low Level Threshold             |                                               |                                         |      |       | 0.8  | V     |

| High Level Threshold            |                                               |                                         |      |       |      | V     |

| Pullup Resistance               | Internally pulled up to                       | Internally pulled up to V <sub>DD</sub> |      |       | 200  | kΩ    |

| PWRGD                           |                                               |                                         |      |       |      |       |

| PWRGD Upper Trip Level          |                                               |                                         | 10.0 | 12.5  | 15.0 | %     |

| PWRGD Lower Trip Level          |                                               |                                         | -15  | -12.5 | -10  | %     |

| Output Low Level                |                                               |                                         |      |       | 0.4  | V     |

| Output High Leakage             |                                               |                                         |      |       | 1    | μΑ    |

| CONTROLLED VID CHANGE           |                                               |                                         |      |       |      |       |

|                                 |                                               | $R_{\text{TIME}} = 120 \text{k}\Omega$  | 6.17 | 6.67  | 7.25 |       |

| On-the-Fly VID Change Slew Rate | 25mV per step                                 | $R_{\text{TIME}} = 47 \text{k}\Omega$   | 2.35 | 2.63  | 2.99 | μs    |

| Tideo                           |                                               | $R_{\text{TIME}} = 470 \text{k}\Omega$  | 23.5 | 26.3  | 29.9 |       |

| VID_ Change Frequency Range     |                                               |                                         |      |       | 380  | kHz   |

| PWRGD Blanking Time             | $V_{VDD} = 4.5V \text{ to } 5.5V$             | 125                                     | 200  | 350   | μs   |       |

MIXIN

#### **ELECTRICAL CHARACTERISTICS**

$(V_{VCC} = 12V, V_{EN} = V_{VDD} = 5V, PGND = GNDS = GND, VID_= GND, C_{VPOS} = 47pF, C_{REF} = 0.1 \mu F, V_{ILIM} = 1V, T_A = -40 ^{\circ}C to +85 ^{\circ}C, unless otherwise noted.)$  (Note 1)

| PARAMETER                                |                                        | MIN                                       | TYP      | MAX | UNITS |    |

|------------------------------------------|----------------------------------------|-------------------------------------------|----------|-----|-------|----|

| GENERAL                                  | •                                      |                                           |          |     |       |    |

|                                          | MAX1937                                |                                           | 6        |     | 24    |    |

| V <sub>CC</sub> Operating Range          | MAX1938/MAX193                         | 8                                         |          | 24  | V     |    |

| V <sub>DD</sub> Operating Range          |                                        |                                           |          |     | 5.5   | V  |

| VLG Operating Range                      | V <sub>VLG</sub> ≥ V <sub>VDD</sub>    |                                           | 4.5      |     | 6.5   | V  |

| V <sub>CC</sub> Operating Supply Current | FB above threshold                     | d (no switching)                          |          |     | 40    | μΑ |

| V <sub>DD</sub> Operating Supply Current | FB above threshold                     | d (no switching)                          |          |     | 2.5   | mA |

| VLG Operating Supply Current             | FB above threshold                     | d (no switching)                          | 20       |     | 60    | μΑ |

| V <sub>CC</sub> Shutdown Current         | EN = GND                               |                                           |          |     | 5     | μΑ |

| V <sub>DD</sub> Shutdown Current         | EN = GND, VID_ n                       | ot connected                              |          |     | 100   | μΑ |

| VLG Shutdown Current                     | EN = GND                               |                                           |          |     | 5     | μΑ |

| TIME Output Voltage                      |                                        |                                           | 1.96     |     | 2.04  | V  |

| ILIM Input Bias                          | V <sub>ILIM</sub> = 1V                 |                                           | -250     |     | +250  | nA |

| VPOS Output Voltage                      | CS_ = GND, VPOS resistor               | S connected to REF through a 75k $\Omega$ | 1.96     |     | 2.04  | V  |

| REFERENCE                                |                                        |                                           | I        |     |       |    |

| Reference Voltage                        | -50µA ≤ I <sub>REF</sub> ≤ 50µ         | ıA                                        | 1.98     |     | 2.02  | V  |

| SOFT-START                               | ,                                      |                                           | <b>I</b> |     |       |    |

|                                          | MAX1937                                | 1.1                                       |          | 5.5 | ms    |    |

| Ramp Period                              | MAX1938                                | 1.5                                       |          | 6.6 |       |    |

|                                          | MAX1939                                | 1.3                                       |          | 7.0 |       |    |

| ERROR AMPLIFIER                          | •                                      |                                           | •        |     |       |    |

| GNDS Input Bias Current                  |                                        |                                           | -5       |     | +5    | μΑ |

| Output Regulation Voltage<br>Accuracy    |                                        |                                           | -1       |     | +1    | %  |

| FAULT PROTECTION                         | l                                      |                                           |          |     |       | 1  |

| V <sub>DD</sub> UVLO Threshold           | Rising or falling VD                   | DD                                        | 4.00     |     | 4.45  | V  |

| VLG UVLO Threshold                       | Rising or falling VL                   | G                                         | 4.00     |     | 4.45  | V  |

| Output Overvoltage Fault                 | D: : 16 III                            | MAX1937/MAX1938                           | 1.97     |     | 2.03  | ., |

| Threshold                                | Rising and falling                     | MAX1939                                   | 2.215    |     | 2.285 | V  |

| Output UVLO Threshold                    | Rising and falling pregulation voltage | 65                                        |          | 75  | %     |    |

| CURRENT LIMIT                            | •                                      |                                           | -        |     |       |    |

|                                          | PGND to CS_, V <sub>ILII</sub>         | M = 1.5V                                  | 135      |     | 165   |    |

| Current-Limit Threshold                  | PGND to CS_, V <sub>ILII</sub>         | 90                                        |          | 110 | mV    |    |

|                                          | PGND to CS_, V <sub>ILII</sub>         | 45                                        |          | 55  |       |    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{VCC} = 12V, V_{EN} = V_{VDD} = 5V, PGND = GNDS = GND, VID_= GND, C_{VPOS} = 47pF, C_{REF} = 0.1 \mu F, V_{ILIM} = 1V, T_A = -40 ^{\circ}C to +85 ^{\circ}C, unless otherwise noted.) (Note 1)$

| PARAMETER                          |                                                         | CONDITIONS                                     | MIN  | TYP | MAX  | UNITS |  |

|------------------------------------|---------------------------------------------------------|------------------------------------------------|------|-----|------|-------|--|

| CS Input Offset Voltage            | CS_ = GND                                               | CS_ = GND                                      |      |     | +5   | mV    |  |

| CS_ Input Bias Current             | CS_ = GND                                               |                                                | -5   |     | +5   | μΑ    |  |

| VOLTAGE POSITIONING                |                                                         |                                                |      |     |      | •     |  |

| VPOS Input Offset Voltage          |                                                         |                                                | -5   |     | +5   | mV    |  |

| VPOS Gain                          | From CS_ to FB; V <sub>CS1</sub> ,                      | $V_{CS2} = 0$ , -100mV; $R_{VPOS} = 75k\Omega$ | 72.5 |     | 77.5 | %/V   |  |

| VPOS Gain                          | From CS1, CS2 to FB;<br>R <sub>VPOS</sub> = $75k\Omega$ | $V_{CS1}$ , $V_{CS2} = +13mV$ , $-113mV$ ;     | 68   |     | 82   | %/V   |  |

| TIMER AND DRIVERS                  |                                                         |                                                |      |     |      | I.    |  |

| On-Time                            | LX1 = LX2 = CS1 = CS                                    | $62 = GND, V_{FB} = 1.5V$                      | 420  |     | 630  | ns    |  |

| Minimum Off-Time                   | DH1 low to DH2 high,                                    | and DH2 low to DH1 high                        | 260  |     | 390  | ns    |  |

| DH_ On-Resistance in Low State     | $V_{\rm BST1} = V_{\rm BST2} = 6V$ , L                  | X1 = LX2 = GND                                 |      |     | 3    | Ω     |  |

| DH_ On-Resistance in High State    | V <sub>BST</sub> _ = 6V, LX_ = GN                       | D                                              |      |     | 3    | Ω     |  |

| DL_ On-Resistance in Low State     |                                                         |                                                |      |     | 1.7  | Ω     |  |

| DL_ On-Resistance in High State    |                                                         |                                                |      |     | 3    | Ω     |  |

| BST_ Leakage Current               | V <sub>BST</sub> = 30V, V <sub>L</sub> X = 24           | 4V                                             |      |     | 50   | μΑ    |  |

| LX_ Leakage Current                | V <sub>BST</sub> = 30V, V <sub>L</sub> X = 24           | 4V                                             |      |     | 50   | μΑ    |  |

| EN AND VID_                        |                                                         |                                                |      |     |      |       |  |

| Low Level Threshold                |                                                         |                                                |      |     | 8.0  | V     |  |

| High Level Threshold               |                                                         |                                                | 1.6  |     |      | V     |  |

| Pullup Resistance                  | Internally pulled up to                                 | V <sub>DD</sub>                                | 50   |     | 200  | kΩ    |  |

| PWRGD                              |                                                         |                                                |      |     |      |       |  |

| PWRGD Upper Trip Level             |                                                         |                                                | 10   |     | 15   | %     |  |

| PWRGD Lower Trip Level             |                                                         |                                                | -15  |     | -10  | %     |  |

| Output Low Level                   |                                                         |                                                |      |     | 0.4  | V     |  |

| Output High Leakage                |                                                         |                                                |      |     | 1    | μΑ    |  |

| CONTROLLED VID CHANGE              |                                                         |                                                |      |     |      |       |  |

| 0 11 51 115 01 01                  |                                                         | $R_{TIME} = 120k\Omega$                        | 6.17 |     | 7.25 |       |  |

| On-the-Fly VID Change Slew<br>Rate | 25mV per step                                           | $R_{TIME} = 47k\Omega$                         | 2.35 |     | 2.99 | μs    |  |

| Tato                               |                                                         | $R_{TIME} = 470k\Omega$                        | 23.5 |     | 29.9 |       |  |

| VID_ Change Frequency Range        |                                                         |                                                | 38   |     | 380  | kHz   |  |

| PWRGD Blanking Time                | $V_{VDD} = 4.5V \text{ to } 5.5V$                       |                                                | 125  |     | 350  | μs    |  |

**Note 1:** Specifications to -40°C are guaranteed by design and not production tested.

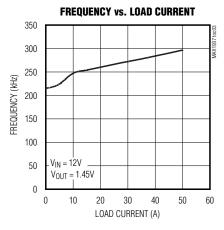

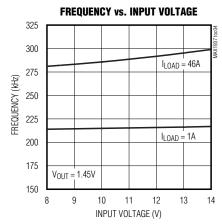

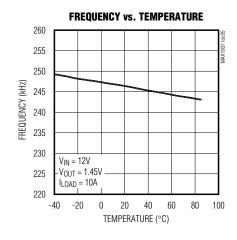

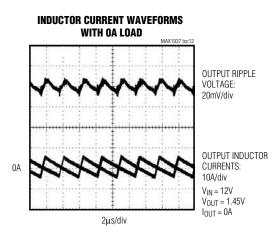

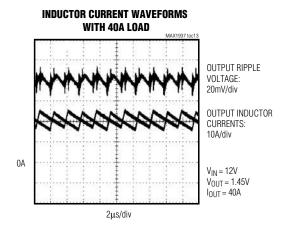

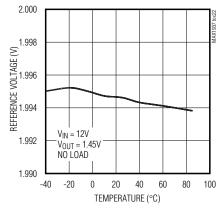

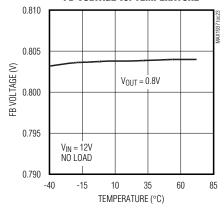

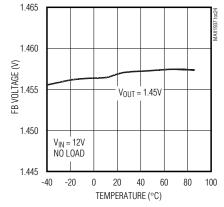

#### **Typical Operating Characteristics**

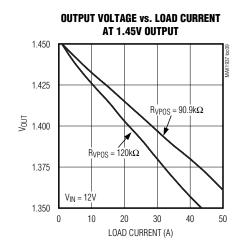

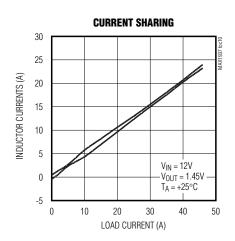

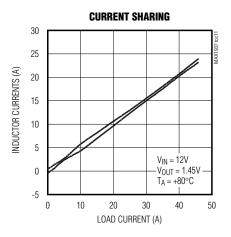

$(V_{IN} = 12V, V_{OUT} = 1.45V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

$(V_{IN} = 12V, V_{OUT} = 1.45V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

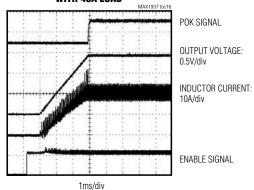

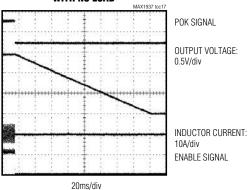

SOFT-START WAVEFORMS

$(V_{IN} = 12V, V_{OUT} = 1.45V, T_A = +25^{\circ}C, unless otherwise noted.)$

**LOAD TRANSIENT**

## 1A TO 40A TO 1A MAX1937 to:14 OUTPUT VOLTAGE: 50mV/div INDUCTOR CURRENTS: 10A/div TRANSIENT CONTROL SIGNAL:

C6 = 47pF

$R2 = 91.1k\Omega$

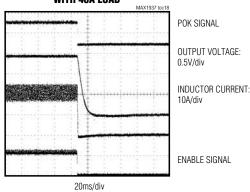

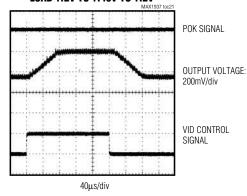

# POK SIGNAL OUTPUT VOLTAGE: 0.5V/div INDUCTOR CURRENT: 10A/div ENABLE SIGNAL

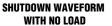

#### SOFT-START WAVEFORMS WITH 40A LOAD

40µs/div

#### SHUTDOWN WAVEFORM WITH 40A LOAD

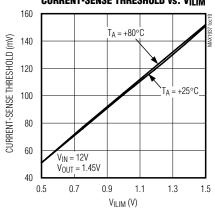

#### **CURRENT-SENSE THRESHOLD VS. VILIM**

#### Typical Operating Characteristics (continued)

$(V_{IN} = 12V, V_{OUT} = 1.45V, T_A = +25^{\circ}C, unless otherwise noted.)$

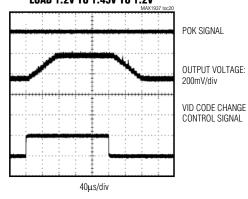

#### VID CODE CHANGE ON-THE-FLY WITH 40A Load 1.2V to 1.45V to 1.2V

#### VID CODE CHANGE ON-THE-FLY WITH 1A LOAD 1.2V TO 1.45V TO 1.2V

#### **REFERENCE VOLTAGE vs. TEMPERATURE**

#### **FB VOLTAGE vs. TEMPERATURE**

#### FB VOLTAGE vs. TEMPERATURE

#### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VID0            | Voltage Identification Input Bit 0. See Table 1. Internal 100kΩ pullup resistor to V <sub>DD</sub> .                                                                                                                                                                                                                                   |

| 2   | VID1            | Voltage Identification Input Bit 1. See Table 1. Internal 100k $\Omega$ pullup resistor to V <sub>DD</sub> .                                                                                                                                                                                                                           |

| 3   | TIME            | Connect to an external resistor (47k $\Omega$ to 470k $\Omega$ ) for VID change slew-rate control.                                                                                                                                                                                                                                     |

| 4   | VID2            | Voltage Identification Input Bit 2. See Table 1. Internal $100k\Omega$ pullup resistor to $V_{DD}$ .                                                                                                                                                                                                                                   |

| 5   | VID3            | Voltage Identification Input Bit 3. See Table 1. Internal $100k\Omega$ pullup resistor to $V_{DD}$ .                                                                                                                                                                                                                                   |

| 6   | VID4            | Voltage Identification Input Bit 4. See Table 1. Internal $100k\Omega$ pullup resistor to $V_{DD}$ .                                                                                                                                                                                                                                   |

| 7   | VPOS            | Voltage Positioning. Connect a resistor between VPOS and REF to set the output voltage-positioning droop, or connect directly to REF for no output voltage positioning. Connect a 47pF capacitor from VPOS to GND.                                                                                                                     |

| 8   | V <sub>DD</sub> | IC Analog Power-Supply Input. Connect a 5V supply to V <sub>DD</sub> .                                                                                                                                                                                                                                                                 |

| 9   | ILIM            | Current-Limit Threshold per Phase. Connect ILIM to V <sub>DD</sub> to set a default current limit of 120mV, or connect to a voltage-divider from REF to GND to adjust the current limit. See the <i>Setting the Current Limit</i> section.                                                                                             |

| 10  | GND             | Ground                                                                                                                                                                                                                                                                                                                                 |

| 11  | GNDS            | Remote Ground Sense. Connect GNDS to the output ground at the load. For VRM applications, also connect a $100\Omega$ resistor from GNDS to PGND locally.                                                                                                                                                                               |

| 12  | REF             | Reference Output. Connect a 0.1µF capacitor from REF to GND.                                                                                                                                                                                                                                                                           |

| 13  | EN              | Enable Input. Leave unconnected or drive high for normal operation. Drive low for shutdown.                                                                                                                                                                                                                                            |

| 14  | FB              | Remote Feedback Sense. Connect FB to the output at the load. For VRM applications, also connect a $100\Omega$ resistor from FB to the output locally.                                                                                                                                                                                  |

| 15  | PWRGD           | Power-Good Output. Open-drain output is high impedance when the output is in regulation and pulled low when the output deviates more than 12.5% from the voltage set by the VID code. PWRGD is also low in shutdown or during any fault condition. To use as a logic output, connect a pullup resistor from PWRGD to the logic supply. |

| 16  | BST2            | High-Side MOSFET Gate-Driver Bootstrap Input. Connect 0.22µF or higher value bypass capacitor from BST2 to LX2. Keep trace length as short as possible. Connect a Schottky diode between BST2 and VLG. See the <i>Selecting a BST Capacitor</i> section.                                                                               |

| 17  | DH2             | High-Side MOSFET Gate-Drive Output. Connect to the high-side MOSFET gate. DH2 is pulled low in shutdown.                                                                                                                                                                                                                               |

| 18  | LX2             | Inductor Connection. Connect to the switched side of the inductor.                                                                                                                                                                                                                                                                     |

| 19  | CS2             | Negative Current-Sense Input. Connect to a current-sense resistor in series with the low-side MOSFET, or connect to LX2 to use the low-side MOSFET's on-resistance for current sensing.                                                                                                                                                |

| 20  | DL2             | Low-Side MOSFET Gate-Driver Output. Connect to the low-side MOSFET gate. DL2 is pulled low in shutdown.                                                                                                                                                                                                                                |

| 21  | PGND            | Power Ground. Connect to power ground at the point where the current-sense resistors or low-side MOSFET sources connect. PGND is used as the positive current-sense connection.                                                                                                                                                        |

#### **Pin Description (continued)**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                 |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22  | VLG              | DL_ Driver Power-Supply Input. Connect to a 4.5V to 6.5V supply for powering the low-side MOSFET gate drive, and the bootstrap circuit for driving the high-side MOSFETs. Ensure that V <sub>VLG</sub> is greater than or equal to V <sub>VDD</sub> .    |

| 23  | DL1              | Low-Side MOSFET Gate-Driver Output. Connect to the low-side MOSFET gate. DL1 is pulled low in shutdown.                                                                                                                                                  |

| 24  | CS1              | Negative Current-Sense Input. Connect to a current-sense resistor in series with the low-side MOSFET or connect to LX1 to use the low-side MOSFET's on-resistance for current sensing.                                                                   |

| 25  | LX1              | Inductor Connection. Connect to the switched side of the inductor.                                                                                                                                                                                       |

| 26  | DH1              | High-Side MOSFET Gate-Drive Output. Connect to the high-side MOSFET gate. DH1 is pulled low in shutdown.                                                                                                                                                 |

| 27  | BST1             | High-Side MOSFET Gate-Driver Bootstrap Input. Connect 0.22µF or higher value bypass capacitor from BST1 to LX1. Keep trace length as short as possible. Connect a Schottky diode between BST1 and VLG. See the <i>Selecting a BST Capacitor</i> section. |

| 28  | V <sub>C</sub> C | Input Voltage Sense. Connect to the input supply at the high-side MOSFET drain. The voltage sensed at V <sub>CC</sub> is used to set the on-time.                                                                                                        |

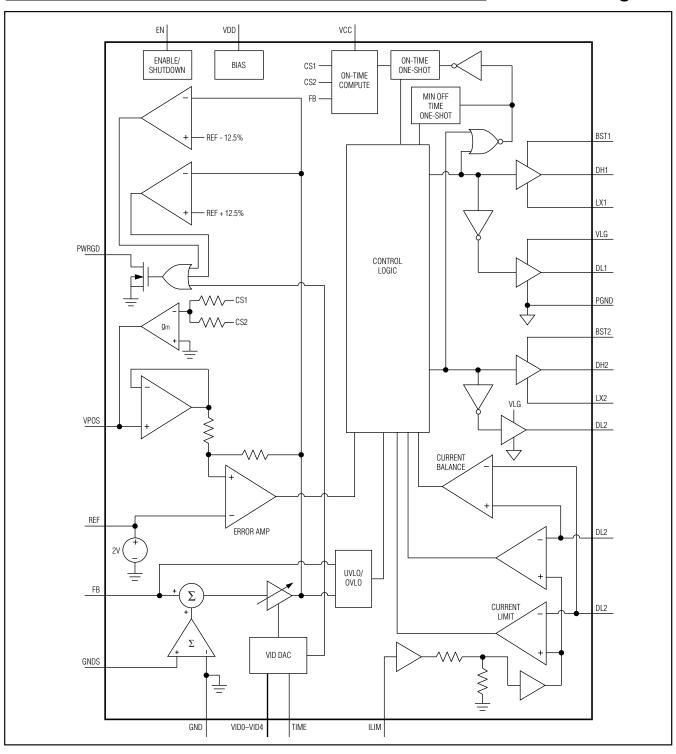

#### **Detailed Description**

The MAX1937/MAX1938/MAX1939 is a family of synchronous, two-phase step-down controllers capable of delivering load currents up to 60A. The controllers use Quick-PWM control architecture in conjunction with active load current voltage positioning. Quick-PWM control provides instantaneous load-step response, while programmable voltage positioning allows the converter to utilize full transient regulation limits, reducing the output capacitance requirement. Furthermore, the two phases operate 180° out-of-phase with an effective 500kHz switching frequency, thus reducing input and output current ripple, as well as reducing input filter capacitor requirements.

The MAX1937/MAX1938/MAX1939 are compliant with the AMD Hammer, Intel VRM 9.0/VRM 9.1, and AMD Athlon Mobile VID code specifications (see Table 1 for VID codes). The internal DAC provides ultra-high accuracy of ±0.75%. A controlled VID voltage transition is implemented to minimize both undervoltage and overvoltage overshoot during VID input change.

Remote sensing is available for high output-voltage accuracy. The MOSFET switches are driven by with a 6V gate-drive circuit to minimize switching and crossover conduction losses to achieve efficiency as high as 90%. The MAX1937/MAX1938/ MAX1939 feature cycle-by-cycle current limit to ensure current limit is not exceeded. Crowbar protection is available to protect against output overvoltage.

#### **On-Time One-Shot**

The heart of the Quick-PWM core is the one-shot that sets the high-side switch on-time. This fast, low-jitter, one-shot circuitry varies the on-time in response to the input and output voltages. The high-side switch on-time is inversely proportional to the voltage applied to VCC and directly proportional to the output voltage. This algorithm results in a nearly constant switching frequency, despite the lack of a fixed-frequency clock generator. The benefits of a constant switching frequency are twofold: the frequency selected avoids noise-sensitive regions, and the inductor ripple current operating point remains relatively constant, resulting in easy design methodology and predictable output voltage ripple:

$$t_{ON} = \frac{K(V_{OUT} + V_{DROP})}{V_{VCC}}$$

where the constant K is 4 $\mu$ s and V<sub>DROP</sub> is the voltage drop across the low-side MOSFET's on-resistance plus the drop across the current-sense resistor (V<sub>DROP</sub>  $\approx$  75mV), if used.

The on-time one-shot has good accuracy at the operating point specified in the *Electrical Characteristics*. Ontimes at operating points far removed from the conditions specified in the *Electrical Characteristics* can vary over a wide range. For example, the regulators run slower with input voltages greater than 12V because of the very short on-times required.

M/IXI/N/

**Table 1. VID Programmed Output Voltage**

| \//D4 | MDO  | VIDO | VID4 | MDO  |          | V <sub>OUT</sub> (V) |          |

|-------|------|------|------|------|----------|----------------------|----------|

| VID4  | VID3 | VID2 | VID1 | VID0 | MAX1937  | MAX1938              | MAX1939  |

| 0     | 0    | 0    | 0    | 0    | 1.550    | 1.850                | 2.000    |

| 0     | 0    | 0    | 0    | 1    | 1.525    | 1.825                | 1.950    |

| 0     | 0    | 0    | 1    | 0    | 1.500    | 1.800                | 1.900    |

| 0     | 0    | 0    | 1    | 1    | 1.475    | 1.775                | 1.850    |

| 0     | 0    | 1    | 0    | 0    | 1.450    | 1.750                | 1.800    |

| 0     | 0    | 1    | 0    | 1    | 1.425    | 1.725                | 1.750    |

| 0     | 0    | 1    | 1    | 0    | 1.400    | 1.700                | 1.700    |

| 0     | 0    | 1    | 1    | 1    | 1.375    | 1.675                | 1.650    |

| 0     | 1    | 0    | 0    | 0    | 1.350    | 1.650                | 1.600    |

| 0     | 1    | 0    | 0    | 1    | 1.325    | 1.625                | 1.550    |

| 0     | 1    | 0    | 1    | 0    | 1.300    | 1.600                | 1.500    |

| 0     | 1    | 0    | 1    | 1    | 1.275    | 1.575                | 1.450    |

| 0     | 1    | 1    | 0    | 0    | 1.250    | 1.550                | 1.400    |

| 0     | 1    | 1    | 0    | 1    | 1.225    | 1.525                | 1.350    |

| 0     | 1    | 1    | 1    | 0    | 1.200    | 1.500                | 1.300    |

| 0     | 1    | 1    | 1    | 1    | 1.175    | 1.475                | Shutdown |

| 1     | 0    | 0    | 0    | 0    | 1.150    | 1.450                | 1.275    |

| 1     | 0    | 0    | 0    | 1    | 1.125    | 1.425                | 1.250    |

| 1     | 0    | 0    | 1    | 0    | 1.100    | 1.400                | 1.225    |

| 1     | 0    | 0    | 1    | 1    | 1.075    | 1.375                | 1.200    |

| 1     | 0    | 1    | 0    | 0    | 1.050    | 1.350                | 1.175    |

| 1     | 0    | 1    | 0    | 1    | 1.025    | 1.325                | 1.150    |

| 1     | 0    | 1    | 1    | 0    | 1.000    | 1.300                | 1.125    |

| 1     | 0    | 1    | 1    | 1    | 0.975    | 1.275                | 1.100    |

| 1     | 1    | 0    | 0    | 0    | 0.950    | 1.250                | 1.075    |

| 1     | 1    | 0    | 0    | 1    | 0.925    | 1.225                | 1.050    |

| 1     | 1    | 0    | 1    | 0    | 0.900    | 1.200                | 1.025    |

| 1     | 1    | 0    | 1    | 1    | 0.875    | 1.175                | 1.000    |

| 1     | 1    | 1    | 0    | 0    | 0.850    | 1.150                | 0.975    |

| 1     | 1    | 1    | 0    | 1    | 0.825    | 1.125                | 0.950    |

| 1     | 1    | 1    | 1    | 0    | 0.800    | 1.100                | 0.925    |

| 1     | 1    | 1    | 1    | 1    | Shutdown | Shutdown             | Shutdown |

**Note:** In the above table, a zero indicates the VID\_ pin is connected to GND or driven low, indicates the VID\_ pin is driven high or not connected.

While the on-time is set by the input and output voltage, other factors contribute to the switching frequency. The on-time guaranteed in the *Electrical Characteristics* is influenced by switching delays in the external high-side MOSFET. Resistive losses in the inductor, both MOSFETs, output capacitor ESR, and PC board copper losses in

the output and ground, tend to raise the switching frequency at higher output currents. Switch dead-time can also increase the effective on-time, reducing the switching frequency. This effect occurs when the inductor current reverses at light or negative load currents. With reversed inductor current, the inductor's

EMF causes LX to go high earlier than normal, extending the on-time by a period equal to the DH rising dead-time.

When the controller operates in continuous mode, the dead-time is no longer a factor, and the actual switching frequency is:

$$f_{SW} = \frac{V_{OUT} + V_{DROP1}}{t_{ON}(V_{VCC} + V_{DROP1} - V_{DROP2})}$$

where VDROP1 is the sum of the parasitic voltage drops in the inductor discharge path, including the synchronous rectifier, inductor, and PC board resistances; VDROP2 is the sum of the resistances in the charging path, including the high-side MOSFET, inductor, and PC board resistances.

#### Synchronized 2-Phase Operation

The two phases of the MAX1937/MAX1938/MAX1939 operate 180° out-of-phase to reduce input filtering requirements, reduce electromagnetic interference (EMI), and improve efficiency. This effectively lowers cost and saves board space, making the MAX1937/MAX1938/MAX1939 ideal for cost-sensitive applications.

With dual synchronized out-of-phase operation, the MAX1937/MAX1938/MAX1939s' high-side MOSFETs turn on 180° out-of-phase. The instantaneous input current peaks of both regulators do not overlap, resulting in reduced input voltage ripple and RMS ripple current. This reduces the input capacitance requirement, allowing fewer or less expensive capacitors, and reduces shielding requirements for EMI. The 180° out-of-phase waveforms are shown in the *Typical Operating Characteristics*.

Each phase operates with a 250kHz switching frequency. Since the two regulators operate 180° out-of-phase, an effective switching of 500kHz is seen at the input and output. In addition to being at a higher frequency (compared to a single-phase regulator), both the input and output ripple have lower amplitude.

#### **Phase Overlap**

To minimize the crosstalk noise in the two phases, the maximum duty cycle of the MAX1937/MAX1938/MAX1939 is less than 50%. To provide a fast transient response, these devices have a phase-overlap mode that allows the two phases to operate in phase when a heavy-load transient is detected. In-phase operation continues until the output voltage returns to the nominal output voltage regulation value.

Once regulation is achieved, the controller returns to 180° out-of-phase operation. A minimum current-adaptive phase-selection algorithm is used to determine which phase is used to start the first out-of-phase cycle. Once the output voltage returns to the nominal output voltage regulation value, the subsequent cycle starts with the phase that has the lowest inductor current. For example, if the current-sense inputs indicate that phase 2 has lower inductor current than phase 1, the controller turns on phase 2's high-side MOSFET first when returning to normal operation.

#### Differential Voltage Sensing and Error Comparator

The MAX1937/MAX1938/MAX1939 use differential sensing of the output voltage to achieve the highest possible accuracy of the output voltage. This allows the error comparator to sense the actual voltage at the load, so that the controller can compensate for losses in the power output and ground lines.

FB and GNDS are used for the differential output voltage sensing. The controller triggers the next cycle (turn on the high-side MOSFET) when the error comparator is low (VFB - VGNDS is less than the VID regulation voltage), VCS is below the current-limit threshold, and the minimum off-time one-shot has timed out.

Traces from FB and GNDS should be routed close to each other and as far away as possible from sources of noise (such as the inductors and high di/dt traces). If noise on these connections cannot be prevented, then use RC filters. To filter FB, connect a  $100\Omega$  series resistor from the positive sense trace to FB, and connect a 1000pF capacitor from FB to GND right at the FB pin. For GNDS, connect a  $100\Omega$  series resistor from the negative sense trace to GNDS, and connect a 1000pF capacitor from GNDS to GND at the GNDS pin.

For VRM applications, connect a 10k $\Omega$  resistor from FB to the output locally (on the VRM board), and connect a 10k $\Omega$  resistor from GNDS to PGND locally (on the VRM board). FB and GNDS also connect to the output at the load (off the VRM board, at the microprocessor). This provides the benefits of differential output voltage sensing mentioned above and the safety of regulating the output voltage on the board in case the external sense connections get disconnected.

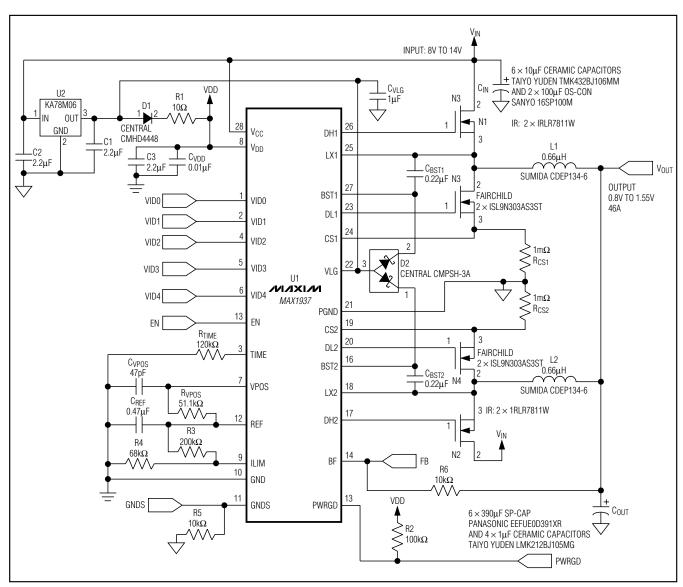

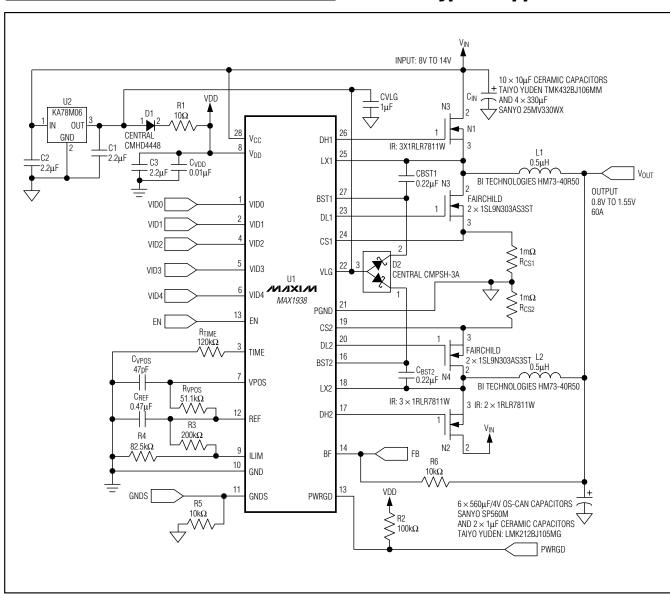

#### **External Linear Regulator**

A 6V linear regulator (U2) is used to step down the main supply. The output of this linear regulator is connected to VLG to provide power for the low-side gate drive and bootstrap circuit. Using 6V for this supply improves efficiency by providing a stronger gate drive than a 5V supply. To reduce switching noise on VLG,

Figure 1. MAX1937 Application Circuit

connect a capacitor (C<sub>VLG</sub>) from VLG to PGND. Place this capacitor as close as possible to the VLG pin.

The MAX1937/MAX1938/MAX1939 also require an external 5V supply connected to VDD. A diode with a forward voltage drop of about 1V (D1) is used to stepdown the 6V supply to power the IC, as shown in Figure 1. The diode connects between the linear regulator output and the RC filter used to filter the voltage at VDD (R1, CVDD, and C3). In the PC board layout, place CVDD as close as possible to the VDD pin.

#### High-Side Gate-Drive Supply (BST\_)

The drive voltage for the high-side MOSFETs is generated using a bootstrap circuit. The capacitor, CBST\_, should be sized properly to minimize the ripple voltage for switching. The ripple voltage should be less than 200mV. For more information on selecting capacitors for the BST circuit, see the *Selecting a BST Capacitor* section. To minimize the forward voltage drop across the bootstrap diodes (D2), use Schottky diodes. The recommended value for the boost capacitors (CBST\_) is 0.22µF.

#### **MOSFET Drivers**

The DH\_ and DL\_ drivers are optimized for driving large high-side (N1 and N2) and larger low-side MOSFETs (N3 and N4). This is consistent with the low duty-cycle operation of the controller. The DL\_ low-side drive waveform is always the complement of the DH\_ high-side drive waveform, with a fixed dead-time between one MOSFET turning off and the other turning on to prevent cross-conduction or shoot-through current.

The internal transistor that drives DL\_ low is robust with a  $0.5\Omega$  (typ) on-resistance. This helps prevent DL\_ from being pulled up during the fast rise time of the LX\_ node due to capacitive coupling from the drain to the gate of the low-side synchronous-rectifier MOSFET. However, some combinations of high-side and low-side MOSFETs may cause excessive gate-drain coupling, leading to poor efficiency, EMI, and shoot-through currents. This is often remedied by adding a resistor (typically less than  $5\Omega$ ) in series with BST\_, which increases the turn-on time of the high-side MOSFET without degrading the turn-off time.

#### **Current-Limit Circuit**

The MAX1937/MAX1938/MAX1939 use either the on-resistance of the low-side MOSFETs or a current-sense resistor to monitor the inductor current. Using the low-side MOSFETs' on-resistance as the current-sense element provides a lossless and inexpensive solution ideal for high-efficiency or cost-sensitive applications. The disadvantage to this method is that the on-resistance of MOSFETs vary from part to part, and overtemperature, which means it cannot be counted on for high accuracy. If high accuracy is needed, use current-sense resistors, which provide an accurate current limit under all conditions but reduce efficiency slightly because of the power lost in the resistors.

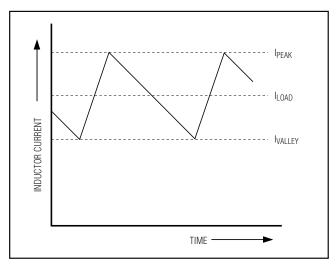

The current-limit circuit employs a "valley" current-sensing algorithm to monitor the inductor current. If the current-sense signal does not drop below the current-limit threshold, the controller does not initiate a new cycle. This limits the maximum value of IVALLEY to the current set by the current-limit threshold (Figure 2).

The current-limit threshold is adjustable over a wide range, allowing for a range of current-sense resistor values. The voltage on ILIM sets the current-limit threshold between PGND and CS\_ to 0.1 × V<sub>ILIM</sub>. The 10mV to 200mV adjustment range corresponds to ILIM voltages from 100mV to 2V. The ILIM voltage is set by a resistor-divider between REF and GND. See the *Setting the Current Limit* section for details.

#### **Current Balancing**

The DC current balancing between phases depends on the accuracy of the current-sense elements and the offset of the current-balance amplifier.

The maximum offset of the current-balance amplifier (VCBOFFSET) is ±3mV. The current-balance accuracy can be calculated from:

Current-balance accuracy =  $V_{CBOFFSET}$  / ( $I_L \times R_{CS}$ ) where  $I_L$  is the peak inductor current and  $R_{CS}$  is the value of the current-sense resistor.

The current-balance accuracy is most important at full load. With a load current of 50A ( $I_L=25A$ ) and  $2m\Omega$  current-sense resistors, the worst-case current-balance accuracy is:

Current-balance accuracy =  $0.003 / (25 \times 0.002) = 6\%$

If the on-resistance of the low-side MOSFETs is used for current sensing, the part-to-part variation of the MOSFET on-resistance is a significant factor in the current balance. The matching between MOSFETs should be on the order of 15%, worst case. Thus, even if the current-balance amplifier has no offset, the DC-current balance could be as bad as 15%. In practice, a little help is received from the thermal ballasting of the MOSFETs. That is to say, the positive temperature coefficient of the on-resistance of MOSFETs reduces the mismatch current between the two phases.

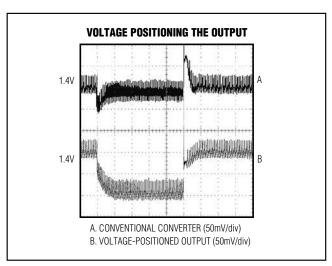

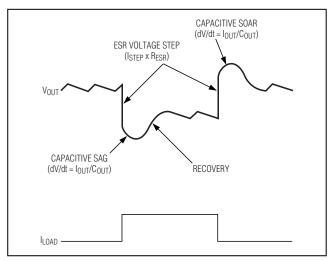

#### **Voltage Positioning (VPOS)**

During a load transient, the output voltage instantly changes by the ESR of the output capacitors times the change in load current ( $\Delta V_{OUT} = -ESR_{COUT} \times \Delta I_{LOAD}$ ). Conventional DC-DC converters respond by regulating the output voltage back to its nominal state after the load transient occurs (Figure 3). However, the CPU requires that the output voltage remain within a specific voltage band. Dynamically positioning the output voltage allows the use of fewer output capacitors and reduces power consumption under heavy load.

For a conventional (nonvoltage-positioned) circuit, the total output voltage deviation from light load to full load and back to light load is:

$V_{P-P1} = 2 \times (ESR_{COUT} \times \Delta I_{LOAD}) + V_{SAG} + V_{SOAR}$  where  $V_{SAG}$  and  $V_{SOAR}$  are defined in the *Output Capacitor Selection* section. Setting the converter to regulate at a lower voltage when under load allows a larger voltage step when the output current suddenly decreases. The total voltage change for a voltage-positioned circuit is:

$V_{P-P2} = (ESRCOUT \times \Delta I_{LOAD}) + V_{SAG} + V_{SOAR}$

Figure 2. Inductor Current Waveform

The maximum allowable voltage change during a transient is fixed by the supply range of the CPU ( $V_{P-P1} = V_{P-P2}$ ). This means that the voltage-positioned circuit tolerates twice the ESR in the output capacitors. Because the ESR specification is achieved by paralleling several capacitors, fewer capacitors are needed for the voltage-positioned circuit. Figure 4 shows transient response regions.

An additional benefit of voltage positioning is reduced power consumption at high-load currents. Because the output voltage is lower under heavy load, the CPU draws less current. The result is lower power dissipation in the CPU.

#### Voltage Reference (REF)

A 2V reference is provided on the MAX1937/MAX1938/ MAX1939 through the REF pin. REF is capable of sourcing or sinking up to 50µA. In addition to providing a reference for the IC, REF is used for setting the current limit and voltage positioning. Connect a 0.47µF capacitor from REF to GND. This capacitor should be placed as close as possible to the REF pin.

A UVLO is provided for the reference voltage. The reference voltage must rise above 1.600V to activate the controller. The controller is disabled if the reference voltage falls below 1.584V.

#### Enable Input (EN) and Soft-Start

When EN is low, DL\_ and DH\_ are held low (turning off the MOSFETs), leaving LX\_ high impedance. In addition, the reference is turned off and PWRGD is pulled low. In shutdown, total current consumption is about 50µA (typ).

Figure 3. Voltage-Positioning and Nonvoltage-Positioning Waveforms

In the case of shutdown by VID code, only DL\_ and DH\_ are held low. The rest of the controller is enabled.

When EN is driven high, the startup sequence begins. Once the reference voltage rises above its 1.6V UVLO threshold, the controller begins switching and starts to ramp up the output voltage. The output voltage is ramped up in 25mV steps every 50µs until the output reaches the nominal output voltage.

#### **Fault Conditions**

The MAX1937/MAX1938/MAX1939 contain internal circuitry to protect themselves and surrounding circuitry from damage from output overvoltage and output undervoltage conditions. When either of these conditions occurs, DH\_ is pulled low, DL\_ is driven high, and PWRGD is pulled low. These pins remain in this state until either power is cycled on VDD or EN is toggled high-low-high.

#### **Setting the Output Voltage (VID )**

An internal DAC is used to set the output regulation voltage. A 5-bit code on inputs VID0–VID4 is used to specify the output voltage. Some codes disable the output. There is an internal  $100 \mbox{k}\Omega$  pullup resistor to VDD on each of the VID\_ inputs. Connecting VID\_ to GND sets the bit to logic low (0); connecting VID\_ to VDD or leaving it unconnected sets the bit to logic high (1). Use external pullup resistors to speed the low-to-high logic transition, or for lower logic voltages. See Table 1 for a list of codes and corresponding output regulation voltages for each of the parts.

The VID\_ codes for the MAX1937 comply with AMD Hammer code. The VID\_ codes on the MAX1938 are

Figure 4. Transient Response Regions

set for Intel VRM 9.0/9.1 and AMD Athlon. The MAX1939 is set for AMD Athlon Mobile.

#### VID\_ Change Slew Rate (TIME)

The MAX1937/MAX1938/MAX1939 allow the VID\_ code to be changed while the converter is operating (on-the-fly). The slew rate at which the output voltage is changing is controlled through TIME. The slew rate is adjusted externally by connecting a  $47 k\Omega$  to  $470 k\Omega$  resistor (RTIME) from TIME to GND. To set the slew rate, select the RTIME resistor using the following equation:

$$R_{\text{TIME}} = \frac{521}{SR} (\Omega)$$

where SR is the slew rate of the output voltage in  $V/\mu s$ . The output voltage is stepped up or down in 25mV steps until it reaches the voltage set by the new VID code.

#### **Power-Good Output (PWRGD)**

PWRGD is an open-drain output that is pulled low when the output voltage deviates more than 12.5% from its regulation voltage (set by VID\_ inputs). PWRGD is pulled low in shutdown, input UVLO, and during startup. Any fault condition forces PWRGD low until the fault is cleared, and the IC is reset by cycling power at VDD or momentarily toggling EN. For logic-level output voltages, connect an external pullup resistor between PWRGD and the logic power supply. A  $100k\Omega$  resistor works well in most applications.

#### **Design Procedure**

#### **Output Inductor Selection**

For most applications, an inductor value of  $0.5\mu H$  to  $1\mu H$  is recommended. The inductance is set by the desired amount of inductor current ripple (LIR). A larger inductance value minimizes output ripple current and increases efficiency, but slows transient response. For the best compromise of size, cost, and efficiency, a LIR of 30% to 40% is recommended (LIR = 0.3 to 0.4). The inductor value is found from:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times I_{LOAD(MAX)} \times LIR}$$

where  $f_{SW}$  is the actual switching frequency of a phase. The selected inductor should have the lowest possible equivalent DC resistance and a saturation current greater than the peak inductor current (IPEAK). IPEAK is found from:

$$I_{PEAK} = I_{LOAD(MAX)} \times \left(1 + \frac{LIR}{2}\right)$$

#### **Output Capacitor Selection**

The output capacitor must have low enough ESR to meet output ripple and load-transient requirements. Also, the capacitance value must be high enough to absorb the inductor energy going from a full-load to a no-load condition without tripping the OVP circuit.

In CPU core power supplies and other applications where the output is subject to large load transients, the output capacitor's size typically depends on how much ESR is needed to prevent the output from dipping too low under a load transient. Ignoring the sag due to finite capacitance:

$$Resr = Vstep(Max) / \Delta I_{LOAD(Max)}$$

The actual capacitance value required relates to the physical size needed to achieve low ESR, as well as to the chemistry of the capacitor technology. Thus, the capacitor is usually selected by ESR and voltage rating rather than by capacitance value (this is true of OSCONs, SP capacitors, POSCAPs, and other electrolytic capacitors). Generally, ceramic capacitors are not recommended for bulk output capacitance but make excellent high-frequency decoupling capacitors.

Once enough capacitance is added to meet the overshoot requirement, undershoot at the rising load edge

(VSAG) is no longer a problem. The amount of overshoot from stored inductor energy can be calculated as:

$$V_{SOAR} = \frac{I^2_{PEAK} \times L}{2 \times C_{OUT} \times V_{OUT}}$$

where IPEAK is the peak inductor current.

The undershoot at the rising load edge of a load transient is calculated from:

$$V_{SAG} = \frac{L \times \Delta I^{2}LOAD \times \left[\frac{V_{OUT} \times K}{V_{IN}} + t_{OFF(MIN)}\right]}{2 \times C_{OUT} \times V_{OUT} \times \left[\frac{(V_{IN} - V_{OUT}) \times K}{V_{IN}} - t_{OFF(MIN)}\right]}$$

where  $\Delta I_{\mbox{\scriptsize LOAD}}$  is the change in load current, and K is 4µs.

To ensure stability, make sure that the zero frequency created by the output capacitance, and the ESR of the output capacitor do not exceed 50kHz. The zero frequency is found from:

$$f_{zESR} = \frac{1}{2\pi \times ESR_{COUT} \times C_{OUT}}$$

Currently, aluminum electrolytic, Sanyo POSCAP, and Panasonic SP capacitors have ESR zero frequencies well below 50kHz. When using ceramic capacitors, it might be necessary to use a series resistance to ensure that the ESR zero is below 50kHz.

#### **Input Capacitor Selection**

The input capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. The input capacitor must meet the ripple current requirement (IRMS) imposed by the switching currents as defined by the following equation:

$$I_{RMS} = \frac{I_{LOAD}}{2} \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

IRMS has a maximum value when the input voltage equals twice the output voltage ( $V_{IN} = 2V_{OUT}$ ), so IRMS(MAX) = ILOAD / 2. For most applications, nontantalum capacitors (ceramic, aluminum electrolytic, polymer, or OS-CON) are preferred at the input because of their robustness with high inrush currents typical of sys-

tems that may be powered from very low impedance sources.

Multiple smaller value capacitors can be used in parallel to satisfy the ESR and capacitance requirements.

#### Selecting a BST Capacitor

The BST capacitors must be large enough to handle the gate-charging requirements of the high-side MOSFETs. For most applications, 0.22µF ceramic capacitors are recommended.

BST capacitors are needed to keep the voltage on the BST\_ pins from dropping too much when the high-side MOSFET gates are charged. A capacitor value that prevents VBST\_ from dropping more than 100mV to 200mV is adequate. The capacitance needed for the BST\_ capacitor is calculated from:

$$C_{BST} = \frac{Q_{GH}}{\Delta V_{BST}}$$

where  $Q_{GH}$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST\_}$  is the amount that the voltage on the BST\_ pin drops when the gate is charged. If using multiple MOSFETs in parallel, use the sum of all the gate charges for  $Q_{GH}.$

#### **Setting the Current Limit**

Current limit sets the maximum value of the inductor "valley" current. IVALLEY is calculated from the following equation:

$$I_{VALLEY} = \frac{I_{LOAD(MAX)}}{2} \times \left(1 - \frac{LIR}{2}\right)$$

The current-limit threshold (I<sub>LIMIT</sub>) must be set higher than the valley current:

The current-limit threshold is set by the voltage at ILIM and the value of the current-sense resistors:

$$I_{LIMIT} = \frac{V_{ILIM}}{10 \times R_{CS}}$$

where V<sub>ILIM</sub> is the voltage on the ILIM pin (0.1V to 2V) and R<sub>CS</sub> is the value of the current-sense resistor. If the on-resistance of the low-side MOSFET is used for current sensing, then the maximum value of the on-resistance (overtemperature and part-to-part variation) must be used for R<sub>CS</sub>.

$V_{ILIM}$  is set from 0.5V to 2V by connecting ILIM to a resistor-divider from REF to GND. Select resistors R3 and R4 such that the current through the divider is at least 5 $\mu$ A:

$$R3 + R4 \le 400k\Omega$$

A typical value for R3 is  $200k\Omega$ ; then solve for R4 using:

$$R4 = R3 \times \frac{V_{|L|M}}{2 - V_{|L|M}}$$

#### **Setting the Voltage Positioning**

Voltage positioning dynamically changes the outputvoltage set point in response to the load current. When the output is loaded, the signals fed back from the current-sense inputs adjust the output voltage set point, thereby decreasing power dissipation. The load-transient response of this control loop is extremely fast yet well controlled, so the amount of voltage change can be accurately confined within the limits stipulated in the microprocessor power-supply guidelines. To understand the benefits of dynamically adjusting the output voltage, see the *Voltage Positioning (VPOS)* section.

The amount of output voltage change is adjusted by an external gain resistor (RvPos). Connect RvPos between REF and VPOS. The output voltage changes in response to the load current as follows:

$$V_{OUT} = V_{VID} - g_{m(VPOS)} \times R_{VPOS} \times \left(\frac{I_{OUT} \times R_{CS}}{2}\right)$$

where V<sub>VID</sub> is the programmed output voltage set by the VID code (Table 1), and the voltage-positioning transconductance ( $g_{m(VPOS)}$ ) is typically 20µS. R<sub>CS</sub> is the value of the current-sense resistor connected from CS\_ to PGND. If the on-resistance of the low-side MOSFETs is used instead of current-sense resistors for current sensing, then use the maximum on-resistance of the low-side MOSFETs for R<sub>CS</sub> in the equation above.

#### **MOSFET Power Dissipation**

Power dissipation in the high-side MOSFET is worst at high duty cycles (maximum output voltage, minimum input voltage). Two major factors contribute to the high-side power dissipation, conduction losses, and switching losses. Conduction losses are because of current flowing through a resistance, and can be calculated from:

$$P_{D(HS)COND} = \frac{V_{OUT} \times I^2_{LOADMAX} \times R_{DS(ON)}}{4 \times V_{IN}}$$

where R<sub>DS(ON)</sub> is the on-resistance of the high-side MOSFET and V<sub>IN</sub> is the input voltage. To minimize conduction losses, select a MOSFET with a low R<sub>DS(ON)</sub>.

Switching losses are also a major contributor to power dissipation in the high-side MOSFET. Switching losses are difficult to precisely calculate and should be measured in the circuit. To estimate the switching losses, use the following equation:

$$P_{D(HS)SW} \cong (I_{PEAK} \times t_{fall} + I_{VALLEY} \times t_{rise}) \frac{V_{IN} \times f_{SW}}{2}$$