Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### MAX20328/MAX20328A

# **MUX Switch for USB Type-C Audio Adapter Accessories**

### **General Description**

The MAX20328/MAX20328A are USB Type-C audio interface ICs for use in portable devices. As USB Type-C and USB power delivery (PD) make a high-voltage charging solution readily available, the data and SBU lines are at risk of shorting to a high bus voltage, risking permanent damage to the portable device. USB 2.0 data lines also need protection when multiplexed with analog audio signals that vary from positive to negative voltages. The devices can detect a CC pin connection event to disable the microphone bias and eliminate pop up noise when an audio accessory is attached.

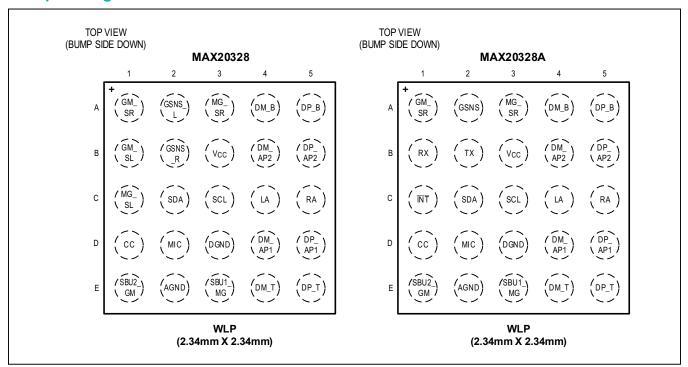

The MAX20328/MAX20328A come in a 5 x 5 array, 25-bump, 0.4mm pitch, 2.34mm x 2.34mm wafer-level package (WLP).

### **Applications**

- Smart Phones

- Phablets

- Tablet PCs

### **Benefits and Features**

- Versatile and Flexible Switch Configurations

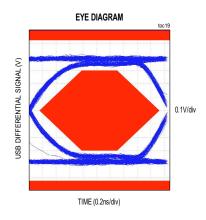

- · High-Speed USB Data or Audio Switch Paths

- Automatic Impedance Detection in Audio Configurations

- Full Manual Switch Control

- Beyond-the-Rails™ Signal Capability

- Overvoltage Protected Data and Audio Channels

- · Two Separate OVLO Blocks

- OVLO Threshold Programmable to 3.37V, 4.00V, 4.70V, or 5.00V

- Negative Voltage Capable Audio Channel

- ±5V Audio Signals (Limited by Positive OVLO Threshold)

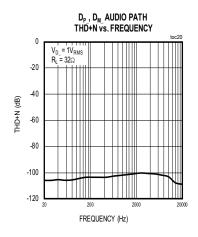

- -100dB THD+N

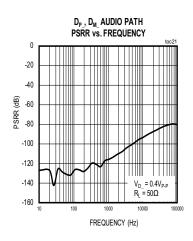

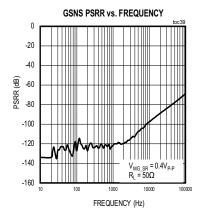

- -100dB PSRR at 217Hz

- High ESD and Surge-Protected USB Type-C Contacts

- ±12kV HBM

- ±25V Surge Capable on USB Type-C Pins

- Minimal Solution size

- 5 x 5 Array, 0.4mm Pitch 2.34mm x 2.34mm WLP

Ordering Information appears at end of data sheet.

Beyond-the-Rails is a trademark of Maxim Integrated Products, Inc.

### **Absolute Maximum Ratings (Note 2)**

| All voltages are referenced to AGND unle | ss otherwise noted    |

|------------------------------------------|-----------------------|

| V <sub>CC</sub> , MIC, SDA, SCL          | 0.3 to +6V            |

| DGND                                     |                       |

| CC                                       | 0.3 to +26V           |

| SBU1_MG, SBU2_GM, MG_SR,                 |                       |

| GM_SR (Note 1)                           | 0.3 to +12V           |

| MG_SL, GM_SL (MAX20328 Only) (Note       | 1)0.3 to +12V         |

| DP_T, DM_T, DP_B, DM_B (Note 1)          | 6 to min              |

| [(LA +                                   | 12V, RA + 12V), +12V] |

| DP_AP1, DM_AP1, DP_AP2, DM_AP2           | 0.3 to +6V            |

| LA, RA                                   | 6 to +6V              |

| GSNS_L (MAX20328 only)                   | 0.3 to min            |

| [+6V, (MG_SL +                           | 0.3V, GM_SL + 0.3V)]. |

| GSNS_R (MAX20328 only)                   | 0.3 to min           |

|------------------------------------------|----------------------|

| [+6V, (MG_SR + (                         | 0.3V, GM_SR + 0.3V)] |

| GSNS_ (MAX20328A only)                   | 0.3 to min           |

| [+6V, (MG_SR + (                         | 0.3V, GM_SR + 0.3V)] |

| TX, RX, INT (MAX20328A only)             | 0.3 to +6V           |

| Continuous Current Into Any Pin          | ±200mA               |

| Continuous Power Dissipation (Multilayer | Board)               |

| (Derate 19.07mW/°C above +70°C)          | 1525.6mW             |

| Operating Temperature Range              | 40°C to +85°C        |

| Junction Temperature                     | +150°C               |

| Storage Temperature Range                | 65°C to +150°C       |

| Soldering Temperature (Reflow)           | +260°C               |

|                                          |                      |

Note 1: Surge capable up to ±25V (IEC61000-4-5 Connector Class 0)

### **Package Thermal Characteristics (Note 2)**

WIF

Junction-to-Ambient Thermal Resistance, Four-Layer Board (θ<sub>JA</sub>)......52.43°C/W

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{CC} = 2.7V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.7V, T_A = +25^{\circ}\text{C}$ ) (Note 3)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                           | MIN | TYP   | MAX | UNITS |

|-------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| VCC                                             |                      |                                                                                                      |     |       |     |       |

| Supply Voltage Range                            | V <sub>CC</sub>      |                                                                                                      | 2.7 |       | 5.5 | V     |

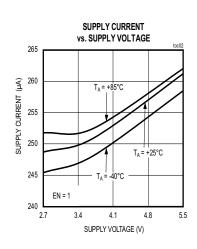

| Input Supply Current                            | Icc                  | V <sub>CC</sub> = 3.7V                                                                               |     | 256   | 400 | μA    |

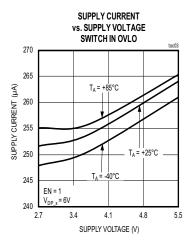

| OVLO Shutdown Current                           | I <sub>CC_O</sub>    | V <sub>DP_/DM_</sub> = 6V,<br>V <sub>LA/RA</sub> = V <sub>DP_/DM_AP_</sub> = 0V                      |     | 256   | 400 | μА    |

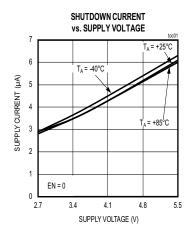

| Shutdown Current                                | I <sub>CC_SHDN</sub> | $V_{CC} = 3.7V, EN = 0$                                                                              |     | 3.9   | 7   | μA    |

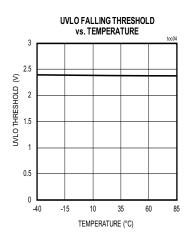

| Undervoltage Lockout (POR) Rising Threshold     | V <sub>UVLOR</sub>   |                                                                                                      |     | 2.395 |     | V     |

| Undervoltage Lockout (POR) Falling Threshold    | V <sub>UVLOF</sub>   |                                                                                                      |     | 2.365 |     | V     |

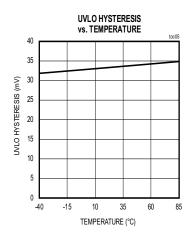

| Undervoltage Lockout (POR) Threshold Hysteresis | V <sub>UVLOH</sub>   |                                                                                                      |     | 30    |     | mV    |

| Start-up Delay                                  | <sup>t</sup> START   | From (V <sub>CC</sub> rising crosses V <sub>UVLOR</sub> OR EN from 0 to 1) to EOB rising from 0 to 1 |     | 0.85  | 2   | ms    |

$(V_{CC} = 2.7V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.7V, T_A = +25^{\circ}\text{C}$ ) (Note 3)

| PARAMETER                                           | SYMBOL                     | BOL CONDITIONS                                                          |                                                     | MIN   | TYP     | MAX               | UNITS |  |

|-----------------------------------------------------|----------------------------|-------------------------------------------------------------------------|-----------------------------------------------------|-------|---------|-------------------|-------|--|

| OVERVOLTAGE PROTECTION                              | DP/M_, SBU_, MG            | _S, GM_S                                                                |                                                     | •     |         |                   |       |  |

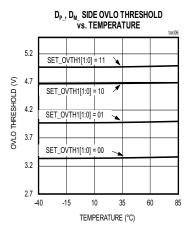

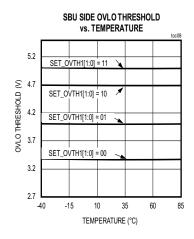

|                                                     |                            |                                                                         | SET_OVTH[1:0] = 00                                  | 3.220 | 3.37    | 3.520             |       |  |

| O                                                   | .,                         | V <sub>IN</sub>                                                         | SET_OVTH[1:0] = 01                                  | 3.845 | 4.0     | 4.155             | ,,    |  |

| Overvoltage Trip Level                              | V <sub>OVLO</sub>          | Rising<br>(Note 4)                                                      | SET_OVTH[1:0] = 10                                  | 4.535 | 4.7     | 4.865             | V     |  |

|                                                     |                            | ,                                                                       | SET_OVTH[1:0] = 11                                  | 4.830 | 5.0     | 5.170             |       |  |

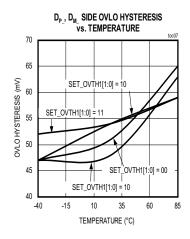

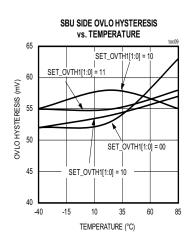

| Overvoltage Trip Level<br>Hysteresis                | V <sub>OVLOH</sub>         |                                                                         |                                                     |       | 60      |                   | mV    |  |

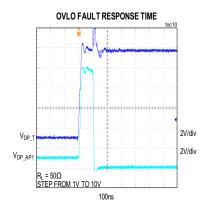

| Overvoltage Fault Protection<br>Response Time       | t <sub>FP</sub>            |                                                                         | o 10V step,<br>V, R <sub>L</sub> = 50Ω              |       | 100     |                   | ns    |  |

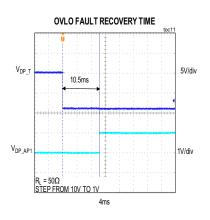

| DP/DM Overvoltage Fault<br>Protection Recovery Time | t <sub>FPR</sub>           |                                                                         | to 1V step,<br>V, $R_L = 50\Omega$                  |       | 10      |                   | ms    |  |

| DP_, DM_ (DATA AND AUDIO S                          | SWITCHES)                  |                                                                         |                                                     | •     |         |                   |       |  |

| Analog Signal Range Audio                           | V <sub>DP_/DM_</sub>       |                                                                         |                                                     | -5    |         | V <sub>OVLO</sub> | V     |  |

| Analog Signal Range Data                            | V <sub>DP_/DM_</sub>       |                                                                         |                                                     | 0     |         | V <sub>OVLO</sub> | V     |  |

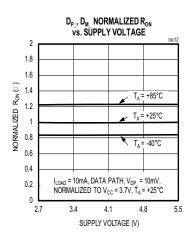

| Single Channel On Resistance                        | R <sub>ON-DP_/DM_</sub>    | V <sub>CC</sub> = 3.7                                                   | V, T <sub>A</sub> = +25°C                           |       | 2.24    | 4                 | Ω     |  |

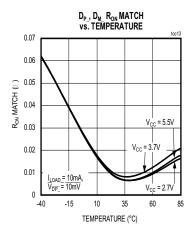

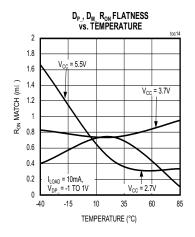

| On Resistance Match Between Channels                | ΔR <sub>ON-DP_/DM_</sub>   | V <sub>CC</sub> = 3.7<br>ID_ = 10m                                      | V, V <sub>DP/M</sub> _ = 0V,<br>A (Note 5)          |       | 0.02    | 0.21              | Ω     |  |

| On Resistance Flatness                              | R <sub>FLAT-DP_</sub> /DM_ | V <sub>CC</sub> = 3.7<br>V <sub>DP_/DM_</sub><br>(Note 6)               | V, I <sub>DP_/DM_</sub> = 10mA,<br>= -1.0V to +1.0V |       | 0.00005 | 0.02              | Ω     |  |

| Off Leakage Current                                 | I <sub>DP_/DM_</sub> OFF   | V <sub>CC</sub> = 3.7<br>V <sub>DP_/DM_</sub><br>V <sub>LA/RA</sub> = \ |                                                     | -0.5  | +0.5    | +1.5              | μA    |  |

|                                                     | I <sub>DP_/DM_</sub> ON    | $V_{CC} = 3.7$<br>$V_{DP/DM}$                                           | = 2.5V,<br><sub>DM_AP</sub> _ = Floating            | -0.7  | +0.4    | +1.5              |       |  |

| On Leakage Current                                  | I <sub>LA/RA_ON</sub>      | V <sub>CC</sub> = 3.7<br>V <sub>LA/RA</sub> = 2<br>V <sub>DP_/DM_</sub> |                                                     | -0.5  | +0.8    | +2.1              | μΑ    |  |

$(V_{CC} = 2.7V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.7V, T_A = +25^{\circ}\text{C}$ ) (Note 3)

| PARAMETER                                              | SYMBOL                   | CONDITIONS                                                                                                                        | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

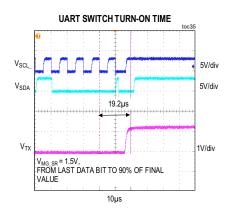

| Turn-On Time                                           | ton-dp_/dm_              | $V_{DP\_/DM\_}$ = 1.5V, $R_L$ = 50Ω, I <sup>2</sup> C control , time from last data bit processed to 90% of final value           |       | 50   |       | μs    |

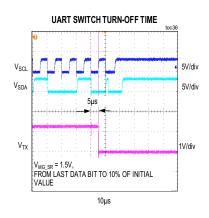

| Turn-Off Time                                          | toff-dp_/dm_             | $V_{DP\_/DM\_}$ = 1.5V, $R_L$ = 50 $\Omega$ , I <sup>2</sup> C control, time from last data bit processed to 10% of initial value |       | 5    |       |       |

| Output Skew Same Switch                                | tskss                    | (Note 7)                                                                                                                          |       | 40   |       | ps    |

| Output Skew Between<br>Switches                        | tskbs                    | (Note 7)                                                                                                                          |       | 40   |       | ps    |

| Break-Before-Make Time<br>Delay                        | <sup>t</sup> ввм         | $R_L$ = 50 $\Omega$ , Time delay between one side of the mux switch opening and the other side closing.                           |       | 10   |       | μs    |

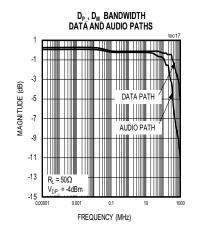

| Bandwidth                                              | BW <sub>DP_/DM_</sub>    | $BW_{DP\_/DM\_} = 0dBm,$ $R_S = R_L = 50\Omega$                                                                                   |       | 800  |       | MHz   |

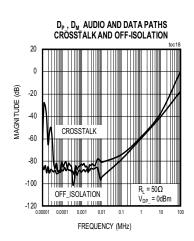

| Off Isolation                                          | V <sub>ISO-DP_/DM_</sub> | f = 20Hz to 20kHz,<br>V <sub>D</sub> _ = 400V <sub>Pk-Pk</sub> , R <sub>L</sub> = 50Ω                                             |       | -90  |       | dB    |

| Crosstalk (Note 8)                                     | V <sub>CT-DP_/DM_</sub>  | f = 20Hz to $20kHz$ ,<br>$V_{D_{-}} = 400V_{Pk-Pk}$ , $R_{L} = 50\Omega$                                                          |       | -80  |       | dB    |

| THD+N                                                  | THD <sub>DP_/DM_</sub>   | f = 20Hz to 20kHz,<br>$V_{D_{-}}$ = 1 $V_{Pk-Pk}$ , DC bias = 0V,<br>$R_{L}$ = 32, 600 $\Omega$                                   |       | -100 |       | dB    |

| PSRR                                                   | PSRR <sub>DP_/DM_</sub>  | $V_{CC} = 3.7V, V = 400 \text{mV}_{Pk-Pk},$<br>f = 217Hz, R <sub>S</sub> = R <sub>L</sub> = $50\Omega$                            |       | -110 |       | dB    |

|                                                        |                          | MANUAL_IDET = 1,<br>SET_IDET = 01                                                                                                 | 95    | 100  | 105   | μA    |

| L <sub>AUDIO</sub> Current Source                      | I <sub>LA_SRC</sub>      | MANUAL_IDET = 1,<br>SET_IDET = 10                                                                                                 | 1.05  | 1.1  | 1.15  | - mA  |

|                                                        |                          | MANUAL_IDET = 1,<br>SET_IDET = 11                                                                                                 | 5.25  | 5.5  | 5.75  | IIIA  |

| L <sub>AUDIO</sub> Current Source Ramp<br>Up/Down Time | t <sub>RAMP</sub>        |                                                                                                                                   | 43.75 | 50   | 56.25 | ms    |

|                                                        | MIC <sub>THR</sub>       | V <sub>CC</sub> = 3.7V, V <sub>MIC</sub> rising                                                                                   | 450   | 788  | 1150  |       |

| MIC Bias Detection Threshold                           | MIC <sub>THF</sub>       | V <sub>CC</sub> = 3.7V, V <sub>MIC</sub> falling                                                                                  | 350   | 701  | 1100  | mV    |

|                                                        | MIC <sub>TH_HYST</sub>   | V <sub>CC</sub> = 3.7V                                                                                                            |       | 87   |       |       |

| Total Detection Time                                   | t <sub>DET</sub>         | 3 ramps max detection time                                                                                                        |       | 600  |       | ms    |

$(V_{CC} = 2.7V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.7V, T_A = +25^{\circ}\text{C}$ ) (Note 3)

| PARAMETER                                                   | AMETER SYMBOL CONDITIONS |                                                                                                                                            | MIN  | TYP  | MAX               | UNITS |

|-------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------|-------|

| CC                                                          |                          | ,                                                                                                                                          |      |      |                   |       |

| CC Disconnect Detection<br>Threshold                        | V <sub>CC_DD_TH</sub>    | Audio Accessory mode, Rising                                                                                                               | 0.5  |      | 1.4               | ٧     |

| Leakage Current                                             | I <sub>L_CC</sub>        | CC = 5V                                                                                                                                    | -1   |      | +1                | μΑ    |

| Time to MIC Open and SBU_<br>Discharge Time From CC<br>High | tcc_mic_dis              | C <sub>SBU</sub> _ < 2µF                                                                                                                   |      | 7    |                   | μs    |

| SBU TO GROUND (GND SWIT                                     | CH)                      |                                                                                                                                            |      |      |                   |       |

| Analog Signal Range                                         | V <sub>SBU_G</sub>       |                                                                                                                                            | -0.3 |      | V <sub>OVLO</sub> | V     |

| On-Resistance                                               | R <sub>ON-SBU_G</sub>    | V <sub>CC</sub> = 3.7V, I = 100mA                                                                                                          |      | 80   | 150               | mΩ    |

| Bandwidth                                                   | B <sub>WSBU_G</sub>      | $V_{CC} = 3.7V, R_S = R_L = 50\Omega$                                                                                                      |      | 300  |                   | MHz   |

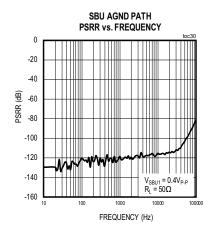

| PSRR                                                        | P <sub>SRRSBU_G</sub>    | $V_{CC} = 3.7V,$ $V_{SBU} = 400 \text{mV}_{Pk-Pk},$ $f = 217 \text{Hz}, R_S = R_L = 50 \Omega$                                             |      | -120 |                   | dB    |

| SBU TO MIC (MIC SWITCH)                                     |                          |                                                                                                                                            |      |      |                   |       |

| Analog Signal Range                                         | V <sub>SBU_MIC</sub>     |                                                                                                                                            | 0    |      | V <sub>OVLO</sub> | V     |

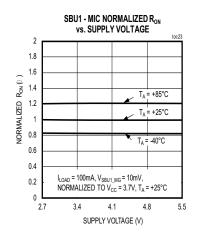

| On Resistance                                               | R <sub>ON-SBU_MIC</sub>  | V <sub>CC</sub> = 3.7V, I = 100mA                                                                                                          |      | 1.7  | 2.9               | Ω     |

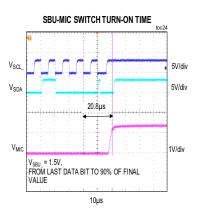

| Turn-On Time                                                | ton-sbu_mic              | V <sub>SBU</sub> _ = 1.5V, R <sub>L</sub> = 50Ω,<br>I <sup>2</sup> C Control, time from last data bit<br>processed to 90% of final value   |      | 20   |                   | μs    |

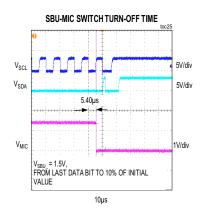

| Turn-Off Time                                               | toff-sbu_mic             | V <sub>SBU</sub> _ = 1.5V, R <sub>L</sub> = 50Ω,<br>I <sup>2</sup> C Control, time from last data bit<br>processed to 10% of initial value |      | 5    |                   | μs    |

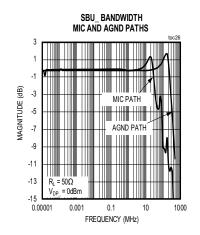

| Bandwidth                                                   | BW <sub>SBU_MIC</sub>    | $V_{SBU}$ = 0dBm, $R_S$ = $R_L$ = 50 $\Omega$                                                                                              |      | 30   |                   | MHz   |

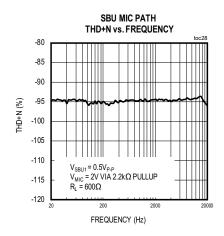

| THD+N                                                       | THD <sub>SBU_MIC</sub>   | $500 mV_{Pk-Pk}$ , DC bias = 2V with 2.2kΩ to MIC, f = $20 Hz - 20 kHz$ , R <sub>L</sub> = $600 \Omega$                                    |      | 100  |                   | dB    |

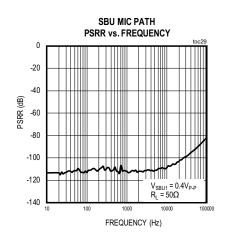

| PSRR                                                        | PSRR <sub>SBU_MIC</sub>  | $V_{CC} = 3.7V,$ $V_{SBU} = 400 \text{mV}_{Pk-Pk},$ $f = 217 \text{Hz}, R_S = R_{SL} = 50 \Omega$                                          |      | -110 |                   | dB    |

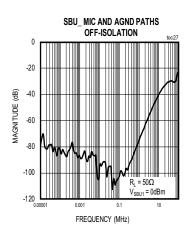

| Off Isolation                                               | V <sub>ISO-SBU_MIC</sub> | $V_{D_{-}} = 400 \text{mV}_{Pk-Pk}, \text{ f} = 20 \text{kHz}, $ $R_{L} = 50 \Omega$                                                       |      | -100 |                   | dB    |

$(V_{CC} = 2.7V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.7V, T_A = +25^{\circ}\text{C}$ ) (Note 3)

| PARAMETER                                        | SYMBOL                         | CONDITIONS                                                                                               | MIN  | TYP    | MAX               | UNITS |  |

|--------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|------|--------|-------------------|-------|--|

| GROUND SENSE AND UART S                          | SWITCHES (GM_S                 | R, GM_SL, MG_SR, MG_SL, TX, RX                                                                           |      |        |                   | 1     |  |

| Analog Cignal Dange                              | V <sub>GM/MG</sub>             | Ground sense switches                                                                                    | -0.3 |        | +2.5              |       |  |

| Analog Signal Range                              | V <sub>UART</sub>              | UART switches                                                                                            | -0.3 |        | V <sub>OVLO</sub> | V     |  |

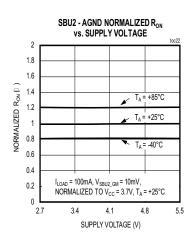

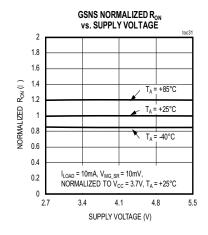

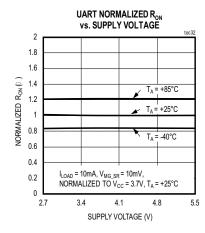

| On Resistance                                    | R <sub>ON-GSNS</sub> _         | Ground Sense, V <sub>GM_/MG_</sub> = 0V,<br>I <sub>LOAD</sub> = 100mA                                    |      | 1.8    | 3                 | Ω     |  |

|                                                  | R <sub>ON-UART</sub>           | UART, I <sub>LOAD</sub> = 10mA                                                                           |      | 6.5    | 11.5              |       |  |

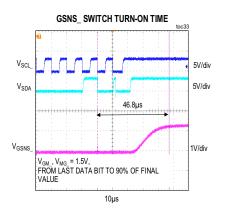

| Turn On Time                                     | ton-gsns                       | $V_{COM}$ = 1.5V, $R_L$ = 50 $\Omega$ , I <sup>2</sup> C control                                         |      | 45     |                   |       |  |

| Turn-On Time                                     | ton-uart                       | $V_{COM}$ = 1.5V, $R_L$ = 50 $\Omega$ , I <sup>2</sup> C control                                         |      | 20     |                   | μs    |  |

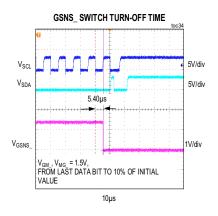

| Turn-Off Time                                    | <sup>t</sup> OFF-GSNS/<br>UART | $V_{COM}$ = 1.5V, $R_L$ = 50 $\Omega$ , OVLO event or I <sup>2</sup> C control                           |      | 5      |                   | μs    |  |

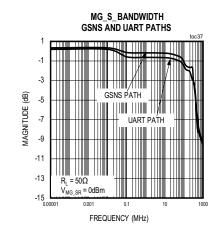

| Bandwidth                                        | BW <sub>GSNS</sub>             | $R_S = R_L = 50\Omega, C_L = 10pF$                                                                       |      | 300    |                   | MHz   |  |

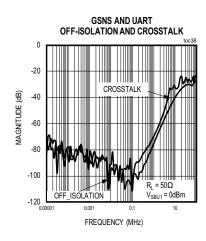

| Crosstalk                                        | V <sub>CT-GSNS</sub>           | $V_{CC} = 3.7V, R_S = R_L = 50\Omega,$<br>f = 20kHz                                                      |      | -100   |                   | dB    |  |

| Off Isolation                                    | V <sub>ISO-GSNS</sub>          | $f = 20kHz, V_{D_{-}} = 400mV_{Pk-Pk},$<br>$R_{L} = 50\Omega$                                            |      | -100   |                   | dB    |  |

| THD+N                                            | THD <sub>GSNS</sub>            | $V_{CC} = 3.7V, 10 \text{mV}_{Pk-Pk},$ DC bias = 0V, f = 20Hz - 20kHz, $R_S = 50\Omega, R_L = 200\Omega$ |      | 0.0004 |                   | %     |  |

| PSRR                                             | PSRR <sub>GSNS</sub>           | $V = 400 \text{mV}_{Pk-Pk}, f = 217 \text{Hz},$<br>$R_S = R_L = 50 \Omega$                               |      | -120   |                   | dB    |  |

| DIGITAL SIGNALS (SCL, SDA,                       | INT, MAX20328A                 | ONLY)                                                                                                    |      |        |                   |       |  |

| Output Voltage Low                               | V <sub>OL</sub>                | I <sub>SDA</sub> = 4mA                                                                                   |      |        | 0.4               | V     |  |

| Output Leakage                                   | I <sub>LEAK</sub>              | V <sub>SDA</sub> = 5.5V                                                                                  | -1   |        | 1                 | μA    |  |

| Input Voltage High                               | V <sub>IH</sub>                |                                                                                                          | 1.4  |        |                   | V     |  |

| Input Voltage Low                                | V <sub>IL</sub>                |                                                                                                          |      |        | 0.5               | V     |  |

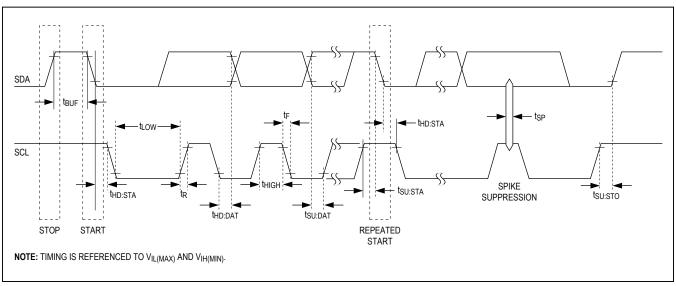

| SCL Clock Frequency                              | f <sub>SCL</sub>               |                                                                                                          |      |        | 400               | kHz   |  |

| Bus Free Time Between a STOP and START Condition | t <sub>BUF</sub>               |                                                                                                          | 1.3  |        |                   | μs    |  |

| START Condition (Repeated)<br>Hold Time          | thd:STA                        |                                                                                                          | 0.6  |        |                   | μs    |  |

| Low Period of SCL Clock                          | t <sub>LOW</sub>               |                                                                                                          | 1.3  |        |                   | μs    |  |

| High Period of SCL Clock                         | tHIGH                          |                                                                                                          | 0.6  |        |                   | μs    |  |

$(V_{CC}$  = 2.7V to 5.5V,  $T_A$  = -40°C to +85°C unless otherwise noted. Typical values are at  $V_{CC}$  = +3.7V,  $T_A$  = +25°C) (Note 3)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                   | MIN | TYP | MAX | UNITS |

|--------------------------------------------------|---------------------|----------------------------------------------|-----|-----|-----|-------|

| Setup Time for a Repeated START Condition        | t <sub>SU:STA</sub> |                                              | 0.6 |     |     | μs    |

| Data Hold Time                                   | t <sub>HD:DAT</sub> |                                              | 0   |     | 0.9 | μs    |

| Data Setup Time                                  | tsu:dat             |                                              | 100 |     |     | μs    |

| Setup Time for a STOP<br>Condition               | tsu:sto             |                                              | 0.6 |     |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input Filter | t <sub>SP</sub>     |                                              |     | 50  |     | ns    |

| THERMAL PROTECTION                               |                     |                                              | •   |     |     |       |

| Thermal Shutdown                                 | T <sub>SHDN</sub>   |                                              |     | 135 |     |       |

| Thermal Hysteresis                               | T <sub>HYST</sub>   |                                              |     | 20  |     |       |

| ESD PROTECTION                                   |                     |                                              |     |     |     |       |

| НВМ                                              |                     | DP_T, DM_T, DP_B, DM_B,                      |     | ±12 |     | kV    |

| Surge                                            |                     | SBU1_MG, SBU2_GM, MG_SL, MG_SR, GM_SL, GM_SR |     | ±25 |     | V     |

| НВМ                                              |                     | All other pins                               |     | ±2  |     | kV    |

Note 3: All devices are 100% production tested at T<sub>A</sub> = +25°C. All temperature limits are guaranteed by design.

Note 4: The switch turns off for voltages above V<sub>OVLO</sub>, protecting downstream circuits in case a fault condition occurs.

Note 5:  $\Delta R_{ON}(MAX) = ABS (R_{ON CH1} - R_{ON CH2}).$

Note 6: Flatness is defined as the difference between the maximum and minimum value of on-resistance, as measured over the specified analog signal range.

Note 7: Guaranteed by design.

Note 8: Between two switches.

### **Typical Operating Characteristics**

# **Bump Configurations**

### **Bump Description**

| BU       | IMP       |                 | FUNCTION                                                       |

|----------|-----------|-----------------|----------------------------------------------------------------|

| MAX20328 | MAX20328A | NAME            | FUNCTION                                                       |

| A1       | A1        | GM_SR           | Analog Ground/MIC Sense Input for Right Audio Channel          |

| A2       | _         | GSNS_L          | Ground Sense Output for Left Audio Channel                     |

| _        | A2        | GSNS            | Ground Sense Output                                            |

| A3       | A3        | MG_SR           | MIC/Analog Ground Sense Input for Right Audio Channel          |

| A4       | A4        | DM_B            | DM Bottom Side Data Line of the External USB Type-C Port       |

| A5       | A5        | DP_B            | DP Bottom Side Data Line of the External USB Type-C Port       |

| B1       | _         | GM_SL           | Analog Ground/MIC Sense Input for Left Audio Channel           |

| _        | B1        | RX              | UART RX Line                                                   |

| B2       | _         | GSNS_R          | Ground Sense Output for Right Audio Channel                    |

| _        | B2        | TX              | UART TX Line                                                   |

| В3       | В3        | V <sub>CC</sub> | Power Supply. Bypass to ground with 1µF effective capacitance. |

| B4       | B4        | DM_AP2          | DM Data Line to AP2                                            |

| B5       | B5        | DP_AP2          | DP Data Line to AP2                                            |

# **Bump Description (continued)**

| BU       | IMP       | NAME    | FUNCTION                                                                                  |

|----------|-----------|---------|-------------------------------------------------------------------------------------------|

| MAX20328 | MAX20328A | NAME    | FUNCTION                                                                                  |

| C1       | _         | MG_SL   | MIC/Analog Ground Sense Input for Left Audio Channel                                      |

| _        | C1        | ĪNT     | Open Drain Output for Interrupt Signaling. Active low.                                    |

| C2       | C2        | SDA     | I <sup>2</sup> C Data Line                                                                |

| C3       | C3        | SCL     | I <sup>2</sup> C Clock Line                                                               |

| C4       | C4        | LA      | Left Audio Channel Output                                                                 |

| C5       | C5        | RA      | Right Audio Channel Output                                                                |

| D1       | D1        | СС      | CC Line from the External USB Type-C Port                                                 |

| D2       | D2        | MIC     | MIC Output                                                                                |

| D3       | D3        | DGND    | Digital Ground. Connect DGND and AGND together for correct operation.                     |

| D4       | D4        | DM_AP1  | DM Data Line to AP1                                                                       |

| D5       | D5        | DP_AP1  | DP Data Line to AP1                                                                       |

| E1       | E1        | SBU2_GM | Analog Ground/MIC, SBU2 Line                                                              |

| E2       | E2        | AGND    | Analog Ground Substrate Connection. Connect DGND and AGND together for correct operation. |

| E3       | E3        | SBU1_MG | MIC/Analog Ground, SBU1 Line                                                              |

| E4       | E4        | DM_T    | DM Top Side Data Line of the External USB Type-C Port                                     |

| E5       | E5        | DP_T    | DP Top Side Data Line of the External USB Type-C Port                                     |

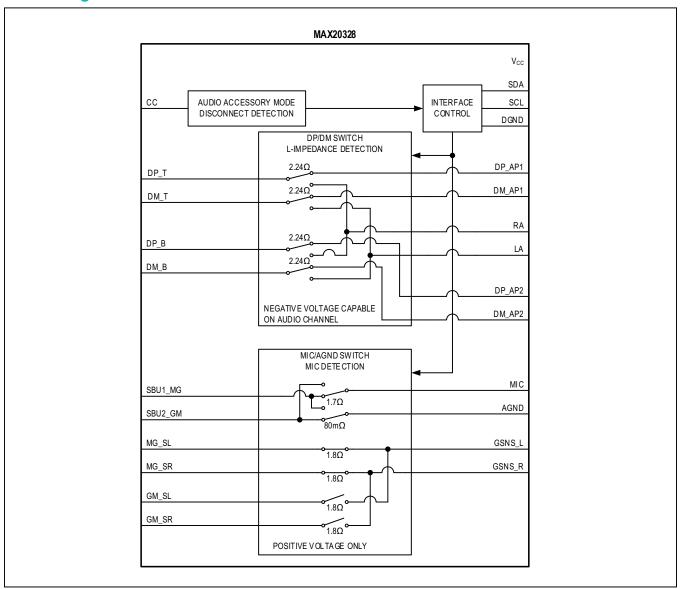

# **Block Diagram**

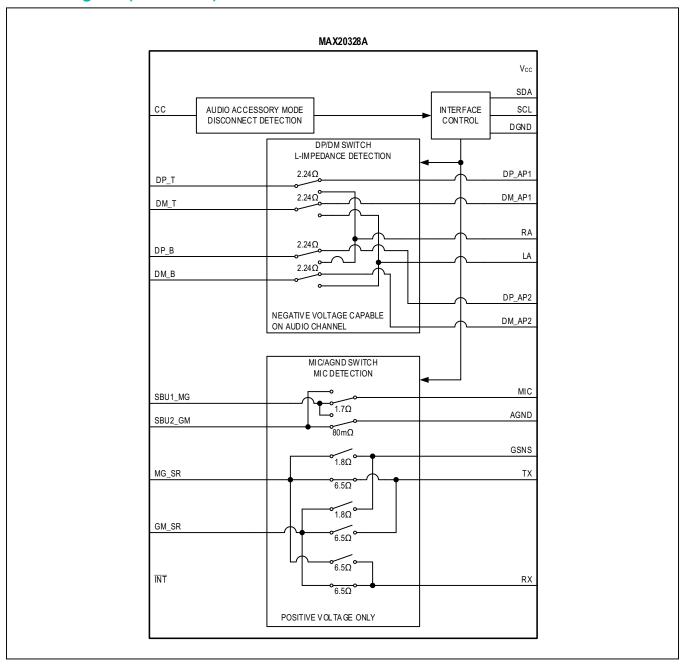

# **Block Diagram (continued)**

### **Detailed Description**

The MAX20328/MAX20328A are USB Type-C audio interface and protection ICs for use in portable devices. As USB power delivery makes a high-voltage charging solution readily available on Type-C connectors, the data and SBU lines are at risk of shorting to a high bus voltage, causing permanent damage to the portable device.

The MAX20328/MAX20328A route incoming signals through the USB Type-C data path or audio path based on information received from a Type-C controller IC or the application processor (AP) controller. The devices offer

automatic microphone orientation and impedance detection for audio devices, pop-up noise suppression, and surge protection on pins connected directly to the USB Type-C port.

### Operation

All switches are open until the MAX20328/MAX20328A are enabled. To enable the devices, write the EN bit (0x06[4]) high. Once enabled, the switches default to the behaviors selected by the MODE[2:0] bits (0x06[2:0]) in automatic mode. See <u>Table 1</u> and <u>Table 2</u> for the switch configurations of each MODE[2:0] setting.

**Table 1. MAX20328 Switch Configurations**

|                                    |        | SWITCH CONNECTION |        |        |              |              |                |                |                |                |  |  |

|------------------------------------|--------|-------------------|--------|--------|--------------|--------------|----------------|----------------|----------------|----------------|--|--|

| MODE[2:0]                          | DP_T   | DM_T              | DP_B   | DM_B   | SBU1<br>_MG  | SBU2<br>_GM  | MG_SL          | MG_SR          | GM_SL          | GM_SR          |  |  |

| OFF [000]                          | OPEN   | OPEN              | OPEN   | OPEN   | OPEN         | OPEN         | OPEN           | OPEN           | OPEN           | OPEN           |  |  |

| ON A [001]                         | DP_AP1 | DM_AP1            | DP_AP2 | DM_AP2 | MIC          | AGND         | OPEN           | OPEN           | GSNS_L         | GSNS_R         |  |  |

| ON B [010]                         | DP_AP1 | DM_AP1            | DP_AP2 | DM_AP2 | AGND         | MIC          | GSNS_L         | GSNS_R         | OPEN           | OPEN           |  |  |

| Set by 0x0D<br>and 0x0E [011]      | _      | _                 | _      | _      | _            | _            | _              | _              | _              | _              |  |  |

| UART [100]                         | DP_AP1 | DM_AP1            | DP_AP2 | DM_AP2 | OPEN         | OPEN         | OPEN           | GSNS_R         | GSNS_L         | OPEN           |  |  |

| USB [101]                          | DP_AP1 | DM_AP1            | DP_AP2 | DM_AP2 | OPEN         | OPEN         | OPEN           | OPEN           | OPEN           | OPEN           |  |  |

| Audio<br>Accessory                 | RA     | LA                | RA     | LA     | MIC<br>*(1)  | AGND<br>*(1) | OPEN<br>*(1)   | OPEN<br>*(1)   | GSNS_L<br>*(1) | GSNS_R<br>*(1) |  |  |

| (Dual Ground<br>Sense) [110]*      | NA     | LA                | I NA   | LA     | AGND<br>*(2) | MIC<br>*(2)  | GSNS_L<br>*(2) | GSNS_R<br>*(2) | OPEN<br>*(2)   | OPEN<br>*(2)   |  |  |

| Audio<br>Accessory                 | RA     | LA                | RA     | LA     | MIC<br>*(1)  | AGND<br>*(1) | OPEN<br>*(1)   | OPEN<br>*(1)   | GSNS_L<br>*(1) | OPEN<br>*(1)   |  |  |

| (Single<br>Ground<br>Sense) [111]* | , KA   | LA                | , RA   | LA     | AGND<br>*(2) | MIC<br>*(2)  | GSNS_L<br>*(2) | OPEN<br>*(2)   | OPEN<br>*(2)   | OPEN<br>*(2)   |  |  |

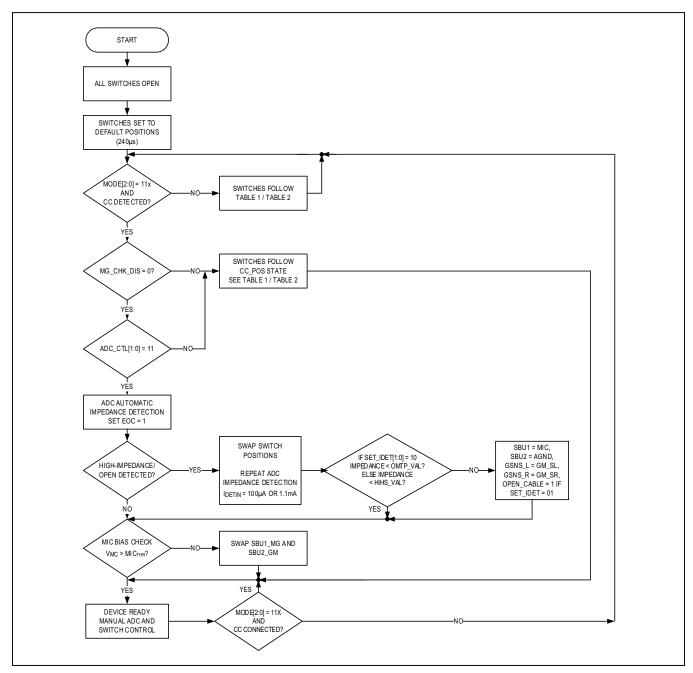

<sup>\*</sup> Controlled by the state machine. Refer to the state diagram of Figure 1.

<sup>\*(1)</sup> When MG\_CHK\_DIS = 1 OR ADC\_CTL ≠ 11, configuration valid when CC\_POS = 0

<sup>\*(2)</sup> When MG\_CHK\_DIS = 1 OR ADC\_CTL ≠ 11, configuration valid when CC\_POS = 1

**Table 2. MAX20328A Switch Configurations**

|                                               |                    |            |      |        | SWITCH CO    | ONNECTIO     | N          |              |            |              |            |

|-----------------------------------------------|--------------------|------------|------|--------|--------------|--------------|------------|--------------|------------|--------------|------------|

| MODE[2:0]                                     | DP_T               | DM_T       | DP_B | DM_B   | SBU1<br>_MG  | SBU2<br>_GM  | MG_SL      | MG_SR        | GM_SL      | GM_SR        |            |

| OFF [000]                                     | OPEN               | OPEN       | OPEN | OPEN   | OPEN         | OPEN         | _          | OPEN         | _          | OPEN         |            |

| ON A [001]                                    | DP_<br>AP1         | DM_<br>AP1 | OPEN | OPEN   | MIC          | AGND         | _          | TX           | _          | RX           |            |

| Default Mode<br>[010/011]                     | _                  | _          | _    | _      | _            | _            | _          | _            | _          | _            |            |

| UART [100]                                    | DP_ DM_<br>AP1 AP1 | OPEN       | OPEN | OPEN   | N ODEN       | OPEN —       | TX<br>*(1) |              | RX<br>*(1) |              |            |

| OAKI [100]                                    |                    | AP1        | OFEN | OI LIV | OI ZIV       | OI LIV       |            | RX<br>*(2)   | _          | TX<br>*(2)   |            |

| USB [101]                                     | OPEN               | OPEN       | DP_  | DM_    | OPEN         | OPEN         | ODEN       | TX<br>*(1)   |            | RX<br>*(1)   |            |

| 035 [101]                                     | OFLIN              | OFEN       | AP2  | AP2    | AP2          | OFEN         | OFLIN      | _            | RX<br>*(2) | _            | TX<br>*(2) |

| Audio Accessory<br>(Single ground<br>sense)   | RA                 | LA         | RA   | LA     | MIC<br>*(3)  | AGND*<br>(3) |            | OPEN<br>*(3) |            | GSNS<br>*(3) |            |

| SBU1_MG = MIC<br>SBU1_MG =<br>AGND [110/111]* | IVA                |            | 11/4 |        | AGND*<br>(4) | MIC<br>*(4)  | _          | GSNS<br>*(4) | _          | OPEN<br>*(4) |            |

<sup>\*</sup> Controlled by the state machine. Refer to the state diagram of Figure 1.

<sup>\*(1)</sup> CC\_POS = 0

<sup>\*(2)</sup> CC\_POS = 1

<sup>\*(3)</sup> When MG\_CHK\_DIS = 1 OR ADC\_CTL  $\neq$  11, configuration valid when CC\_POS = 0

<sup>\*(4)</sup> When MG\_CHK\_DIS = 1 OR ADC\_CTL ≠ 11, configuration valid when CC\_POS = 1

#### **Enable**

Both the MAX20328 and MAX20328A are enabled by default (EN = 1). To disable a device, write EN = 0 (0x06[4] = 0). In the disable state, all switches are open and the devices enter a low-current mode to minimize the

supply current. When a device is disabled, the ADC\_VAL register (0x01) and bits 0x02[7:6] and 0x02[3:0] are reset to 0. These bits provide information regarding the audio accessory impedance and microphone orientation. When EN is set to 1, the device runs through the state machine diagrammed in Figure 1.

Figure 1. Startup State Machine (FSM)

#### **Pop-Up Noise Suppression**

If a 3.5mm jack is removed from a USB Type-C audio adapter when the adapter is connected to a portable device, pop-up noise may be heard due to the MIC line bias. When the CC pin goes high to signal an audio accessory removal, the MIC/AGND and AGND/MIC switches disconnect from the MIC bias and discharge to ground within 50µs.

#### Impedance Detection

The MAX20328/MAX20328A can perform an impedance detection to measure the impedance of a connected audio accessory or detect an open cable. This function uses a precision, 8-bit ADC to measure the voltage dropped across the left audio channel while the IDET current source is active. An impedance measurement triggers automatically when EN is set to 1 if ADC\_CTL[1:0] = 11 and follows the state machine in Figure 1. Changing MODE[2:0] to 1xx while the device is enabled also trig-

gers an automatic measurement. If ADC\_CTL[1:0] = 01 or 10, impedance measurements are manually triggered by writing FORCE\_ADC\_START high.

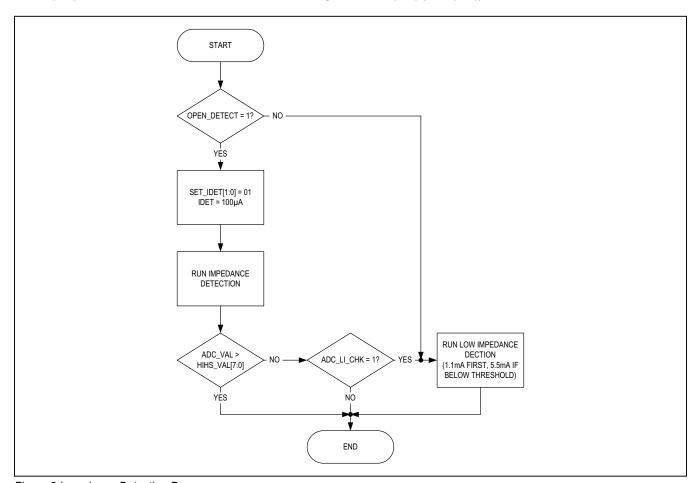

When OPEN\_DETECT = 1 (0x09[5]), the impedance detection starts with IDET =  $100\mu A$ . Otherwise, the 1.1mA and 5.5mA current sources are used for low impedance detection. Figure 2 details the impedance detection process.

#### **Current Sources**

Three current source values are available for impedance detection. For high impedance audio accessories and open cable detection, a 100µA source is used. When the accessory impedance is low, i.e. ADC\_VAL < HIHS\_VAL after EOC goes high, IDET switches to 1.1mA. For very low impedance accessories, the 1.1mA source increases to 5.5mA. The value of the current source used in the latest impedance measurement is available in SET\_IDET[1:0] (0x09[3:2]).

Figure 2.Impedance Detection Process

#### **ADC Result**

When the EOC bit goes high, the ADC result is available in ADC\_VAL (register 0x01). The following conversion extracts the channel impedance from ADC\_VAL and SET\_IDET[1:0]

$R = (ADC_VAL[7:0] \times 4.746mV) / SET_IDET[1:0]$

To account for potential offsets in the ADC and current source values, <u>Table 3</u> provides the minimum and maximum values the ADC may provide for common headset impedance values.

#### **Open Cable Check**

The MAX20328/MAX20328A can perform an open cable check during the impedance measurement. If the  $100\mu A$  current source detects a high impedance where ADC\_VAL > HIHS\_VAL, the OPEN\_CABLE bit (0x02[3]) goes high to signal the open cable.

#### **MIC/GND Detection**

Because a USB Type-C audio accessory can be inserted in two orientations, it is necessary to identify the MIC and GND lines. After an impedance detection, the state machine determines if the MIC/AGND switches are in the correct orientations. If ADC\_VAL is greater than the thresholds set in OMTP\_VAL or HIHS\_VAL, the switch positions are swapped and the impedance measurement is repeated.

In cases where the 3.5mm to USB Type-C adapter has a non-standard internal connection of one SBU to ground, there is the potential risk for the MIC line to be shorted to ground. To prevent this situation, the MAX20328/MAX20328A can check for the presence of a bias on the MIC line at the end of an automatic impedance detection. When MIC\_CHK\_DIS = 0 (0x07[1]), the devices check for a bias greater than MICTHR on the MIC line. If no bias is detected, the states of the MIC/AGND switches are swapped immediately after the DEVICE\_READY bit goes high. To prevent the bias check from incorrectly reassigning the switches, a bias voltage must be applied to MIC before running an impedance detection.

### I<sup>2</sup>C Interface

The MAX20328/MAX20328A use the two-wire I2C interface to communicate with a host application processor. The configuration settings and status information provided through this interface are detailed in the register descriptions (Tables 5-19). Both devices use the sevenbit slave address 0b0010101 (0x2A for writes, 0x2B for reads).

### **Applications Information**

### Applying Signals to an Open Switch

Due to the structure of the DP\_/DM\_ inputs, the switches will not close when a large, high frequency signal is applied to the open terminal. To ensure the desired path closes properly, avoid applying fast signals >1V to the DP\_/DM\_ pins before closing the switch.

Table 3. ADC to Impedance Range Conversion Guide

| ACCESSORY IMPEDANCE (Ω) | RESISTOR RANGE (Ω) |        | ADC CODE (HEX) |    | SET_IDET[1:0] |   |

|-------------------------|--------------------|--------|----------------|----|---------------|---|

| 16                      | 0                  | 22.4   | 00             | 1A | 1             | 1 |

| 32                      | 25.0               | 40.6   | 1D             | 2F | 1             | 1 |

| 64                      | 44.9               | 87.2   | 34             | 65 | 1             | 1 |

| 150                     | 94.9               | 189.8  | 16             | 2C | 1             | 0 |

| 300                     | 211.4              | 431.5  | 31             | 64 | 1             | 0 |

| 600                     | 474.6              | 957.8  | 6E             | DE | 1             | 0 |

| 2000                    | 1,001.4            | 12,150 | 15             | FF | 0             | Х |

### I<sup>2</sup>C Serial Interface

The  $I^2C$  serial interface is used to configure the device. Figure 3 shows the  $I^2C$  timing diagram.

### **Serial Addressing**

When in I<sup>2</sup>C mode, the devices operate as slave devices that send and receive data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial data line (SDA) and a serial-clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX20328/MAX20328A and generates the SCL clock that synchronizes the data transfer. The SDA line operates as both an input and an open drain output. A pullup resistor is required on SDA. The SCL line operates only as an input. A pullup resistor is required on SCL if there are multiple masters on

the 2-wire interface, or if the master in a single-master system has an open drain SCL output. Each transmission consists of a START condition sent by a master, followed by the MAX20328/MAX20328A 7-bit slave address plus R/W bit, a register address byte, one or more data bytes, and finally a STOP condition.

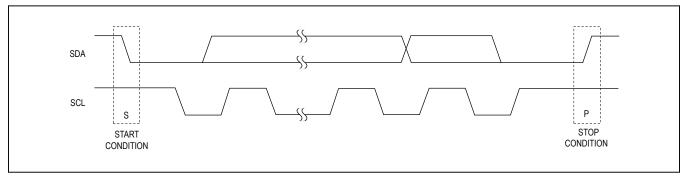

### **Start and Stop Conditions**

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high (Figure 4). When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

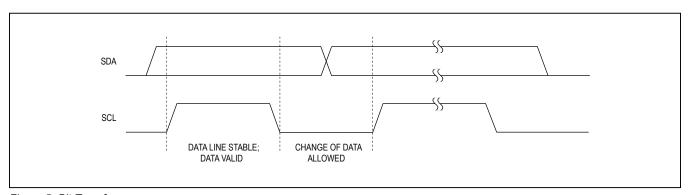

Figure 3. I<sup>2</sup>C Timing Diagram.

Figure 4. Start and Stop Conditions

#### **Bit Transfer**

One data bit is transferred during each clock pulse (Figure 5). The data on SDA must remain stable while SCL is high.

### **Acknowledge**

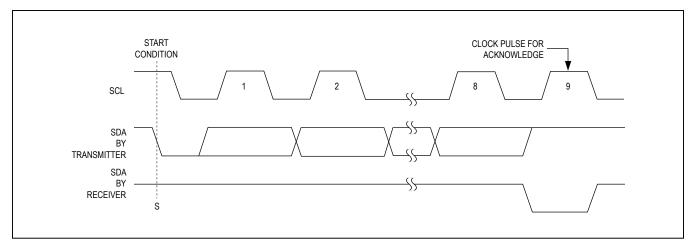

The acknowledge bit is a clocked 9th bit (Figure 6), which the recipient uses to handshake receipt of each byte of data. Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse. The SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the devices, it generates the acknowledge bit because the device is the recipient. When the device is transmitting to the master, the master generates the acknowledge bit because the master is the recipient. If the device does not pull SDA low, a not acknowledge is indicated.

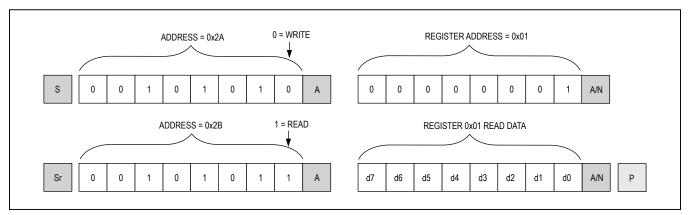

#### Slave Address

The devices have a 7-bit slave address. The bit following a 7-bit slave address is the  $R/\overline{W}$  bit, which is low for a write command and high for a read command. The slave address for the device is 0b00101011 for read commands and 0b00101010 for write commands. This is summarized in Table 4.

Table 4. I<sup>2</sup>C Slave Addresses

| ADDRESS FORMAT      | VALUE |           |  |  |

|---------------------|-------|-----------|--|--|

| ADDRESS FORMAI      | HEX   | BINARY    |  |  |

| 7-BIT SLAVE ADDRESS | 0x15  | 001 0101  |  |  |

| WRITE ADDRESS       | 0x2A  | 0010 1010 |  |  |

| READ ADDRESS        | 0x2B  | 0010 1011 |  |  |

Figure 5. Bit Transfer

Figure 6. Acknowledge

#### **Bus Reset**

The MAX20328/MAX20328A resets the bus with the  $I^2C$  start condition for reads. When the R/W bit is set to 1, the MAX20328/MAX20328A transmits data to the master, thus the master is reading from the device.

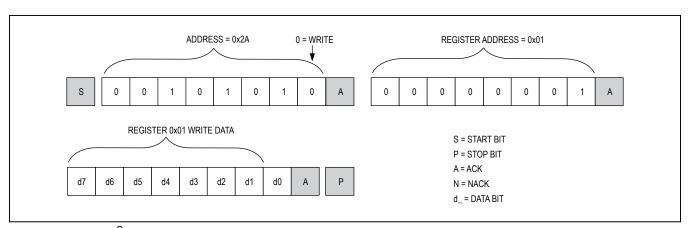

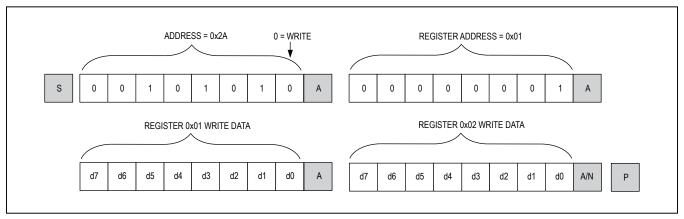

#### Format for Writing

A write to the devices comprises the transmission of the slave address with the R/W bit set to zero, followed by at least 1 byte of information. The first byte of information is the register address or command byte. The register address determines which register of the device is to be written by the next byte, if received. If a STOP (P) condition is detected after the register address is received, then the device takes no further action beyond storing the register address. Any bytes received after the register address are data bytes. The first data byte goes into the register selected by the register address and subsequent

data bytes go into subsequent registers (Figure 7). If multiple data bytes are transmitted before a STOP condition, these bytes are stored in subsequent registers because the register addresses auto-increments (Figure 8).

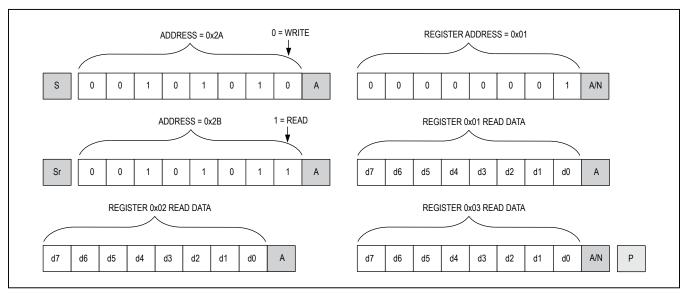

### Format for Reading

The MAX20328/MAX20328A is read using the internally stored register address as an address pointer, the same way the stored register address is used as an address pointer for a write. The pointer auto-increments after each data byte is read using the same rules as for a write. Thus, a read is initiated by first configuring the register address by performing a write (Figure 9). The master can now read consecutive bytes from the device, with the first data byte being read from the register addressed pointed by the previously written register address (Figure 10). Once the master sounds a NACK, the MAX20328/MAX20328A stop sending valid data.

Figure 7. Format for I<sup>2</sup>C Write

Figure 8. Format for Writing to Multiple Registers

Figure 9. Format for Reads (Repeated Start)

Figure 10. Format for Reading Multiple Registers