Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### MAX32650-MAX32652

#### **General Description**

DARWIN is a new breed of low-power microcontrollers built to thrive in the rapidly evolving Internet of Things (IoT). They are smart, with the biggest memories in their class and a massively scalable memory architecture. They run forever, thanks to wearable-grade power technology. They are also tough enough to withstand the most advanced cyberattacks. DARWIN microcontrollers are designed to run any application imaginable—in places where you would not dream of sending other microcontrollers.

Generation UP microcontrollers are designed to handle the increasingly complex applications demanded by today's advanced battery-powered devices and wireless sensors. The MAX32650–MAX32652 are ultra-low power memory-scalable microcontrollers designed specifically for high-performance, battery-powered applications. They are based on Arm® Cortex®-M4 with FPU CPU with 3MB flash and 1MB SRAM. Memory scalability is supported with multiple memory-expansion interfaces, including a HyperBus™/Xccela™ DDR interface and two SPI execute in place (SPIX) interfaces. A secure digital interface supports external high-speed memory cards, including SD, SDIO, MMC, SDHC, and microSD™.

Power management features provide five low power modes for clock, peripheral, and voltage control. Individual SRAM banks of 32KB, 96KB, or 1024KB (full retention) can be retained with reduced power consumption. A SmartDMA performs complex background processing while the CPU is off to dramatically reduces overall power consumption.

The MAX32651 is a secure version with a trust protection unit (TPU) that provides a modular arithmetic accelerator (MAA) for fast ECDSA, an AES engine, TRNG, SHA-256 hash, and secure bootloader. A memory decryption integrity unit (MDIU) provides on-the-fly data decryption (plain or executable) stored in external flash.

The MAX32652 is a high-density, 0.35mm pitch, 140-bump WLP package targeted for tiny form factor products that require high I/O counts.

#### **Applications**

- Sports Watches, Fitness Monitors

- Wearable Medical Patches, Portable Medical Devices

- Industrial Sensors, IoT

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

HyperBus is a trademark of Spansion.

Xccela is a trademark of Micron Technology, Inc.

MicroSD is a trademark of SD-3C, LLC.

## Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

#### **Benefits and Features**

- Ultra-Efficient Microcontroller for Battery-Powered Applications

- 120MHz Arm Cortex-M4 with FPU

- SmartDMA Provides Background Memory Transfers with Programmable Data Processing

- 120MHz High-Speed and 40MHz Low-Power Oscillators

- 7.3728MHz Low-Power Oscillators

- 32.768kHz and RTC Clock (Requires External Crystal)

- 8kHz Always-On Ultra-Low Power Oscillator

- 3MB Internal Flash, 1MB Internal SRAM

- 104µW/MHz Executing from Cache at 1.1V

- Five Low Power Modes: Active, Sleep, Background, Deep-Sleep, and Backup

- 1.8V and 3.3V I/O with No Level Translators

- Scalable Cached External Memory Interfaces:

- 120MB/s HyperBus/Xccela DDR Interface

- SPIXF/SPIXR for External Flash/RAM Expansion

- 240Mbps SDHC/eMMC/SDIO/microSD Interface

- Optimal Peripheral Mix Provides Platform Scalability

- 16-Channel DMA

- Three SPI Master (60MHz)/Slave (48MHz)

- One QuadSPI Master (60MHz)/Slave (48MHz)

- Up to Three 4Mbaud UARTs with Flow Control

- Two 1MHz I<sup>2</sup>C Master/Slave

- I<sup>2</sup>S Slave

- Four-Channel 7.8ksps 10-Bit Delta-Sigma ADC

- USB 2.0 Hi-Speed Device Interface with PHY

- 16 Pulse Train Generators

- · Six 32-Bit Timers with 8mA High Drive

- 1-Wire Master

- Trust Protection Unit (TPU) for IP/Data Security

- Modular Arithmetic Accelerator (MAA), True Random Number Generator (TRNG)

- Secure Nonvolatile Key Storage, SHA-256, AES-128/192/256

- Memory Decryption Integrity Unit, Secure Boot ROM

Ordering Information appears at end of data sheet.

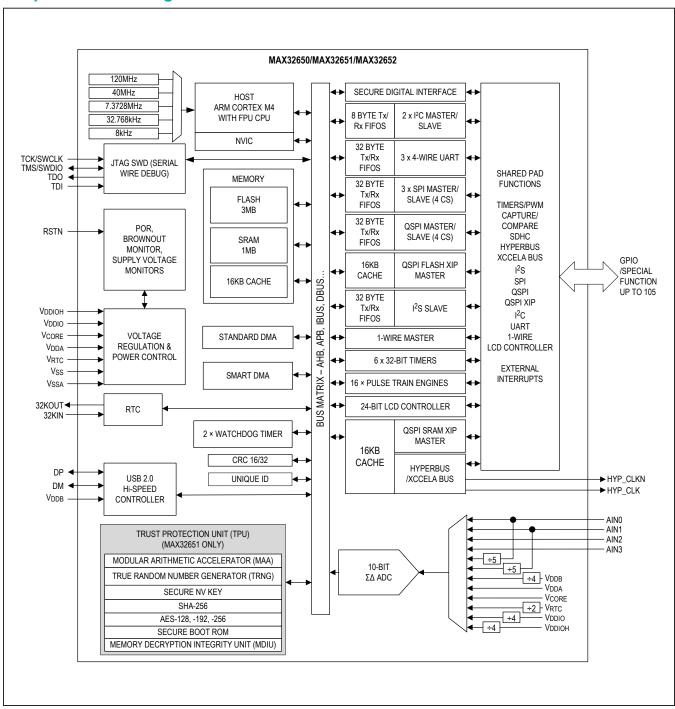

### **Simplified Block Diagram**

#### **Absolute Maximum Ratings**

| (All voltages with respect to V <sub>S</sub> | S, unless otherwise noted.)       | HYP_CLK, HYP_CLKN, P1.[21:18],             |                    |

|----------------------------------------------|-----------------------------------|--------------------------------------------|--------------------|

| V <sub>CORE</sub>                            | 0.3V to 1.21V                     | P1.[16:11], P3.0                           | 0.3V to 1.98V      |

| V <sub>DDA</sub>                             | 0.3V to 1.98V                     | V <sub>DDIO</sub> pins (sink)              | 100mA              |

| V <sub>DDIO</sub>                            | 0.3V to 1.98V                     | V <sub>DDIOH</sub> pins (sink)             | 100mA              |

| V <sub>DDIOH</sub>                           | 0.3V to 3.6V                      | V <sub>SSA</sub>                           | 100mA              |

| V <sub>RTC</sub>                             | 0.3V to 1.98V                     | V <sub>SS</sub>                            | 100mA              |

| RSTN, GPIO (V <sub>DDIO</sub> )              | 0.3V to V <sub>DDIO</sub> + 0.5V  | Output Current (sink) by Any GPIO Pin      | 25mA               |

|                                              | 0.3V to V <sub>DDIOH</sub> + 0.5V | Output Current (source) by Any GPIO Pin    | 25mA               |

| 32KIN, 32KOUT                                | 0.3V to V <sub>RTC</sub> + 0.2V   | Continuous Package Power Dissipation TQFF  | (multilayer board) |

| AIN[1:0]                                     | 0.3V to 5.5V                      | $T_A = +70$ °C (derate 45.5mW/°C above +70 | 0°C)2857.10mW      |

| AIN[3:2]                                     | 0.3V to V <sub>DDA</sub> + 0.2V   | Operating Temperature Range                | 40°C to +105°C     |

| V <sub>DDB</sub>                             | 0.3V to 3.6V                      | Storage Temperature Range                  | 65°C to +150°C     |

| DM, DP                                       | 0.3V to 3.6V                      | Soldering Temperature                      | +260°C             |

|                                              |                                   |                                            |                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

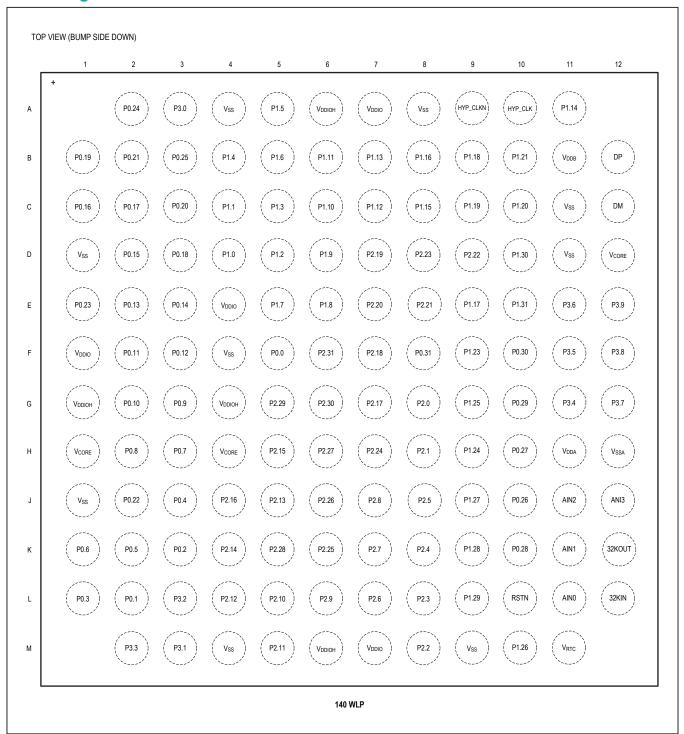

#### 140 WLP

| PACKAGE CODE                           | W1404A4+1                      |

|----------------------------------------|--------------------------------|

| Outline Number                         | 21-100219                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board   | 1:                             |

| Junction to Ambient (θ <sub>JA</sub> ) | 35.13°C/W                      |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

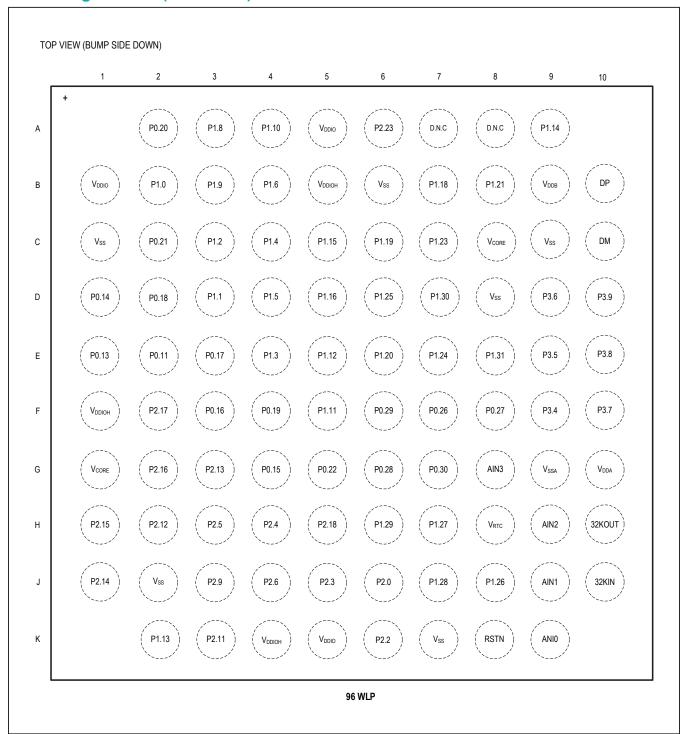

#### **96 WLP**

| <del></del>                            |                                |

|----------------------------------------|--------------------------------|

| PACKAGE CODE                           | W964A4+1                       |

| Outline Number                         | 21-100240                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 33.61°C/W                      |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

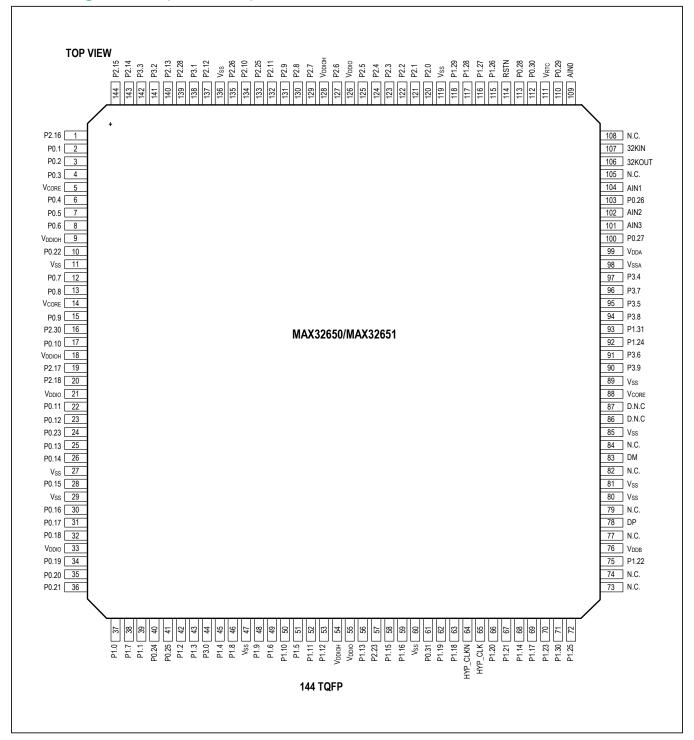

#### **144 TQFP**

| PACKAGE CODE                           | C144+1  |

|----------------------------------------|---------|

| Outline Number                         | 21-0087 |

| Land Pattern Number                    | 90-0144 |

| Thermal Resistance, Four-Layer Board:  |         |

| Junction to Ambient (θ <sub>JA</sub> ) | 28°C/W  |

| Junction to Case $(\theta_{JC})$       | 8°C/W   |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General Purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                                         | SYMBOL             | CONDITIONS                                                                                                                                                                                                                                                                     | MIN  | TYP   | MAX  | UNITS  |  |

|---------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|--------|--|

| POWER                                             | •                  |                                                                                                                                                                                                                                                                                |      |       |      |        |  |

| Supply Voltage, Core                              | V <sub>CORE</sub>  | f <sub>SYS CLK</sub> = 120MHz                                                                                                                                                                                                                                                  | 0.99 | 1.1   | 1.21 | V      |  |

| Supply Voltage, Analog                            | $V_{DDA}$          |                                                                                                                                                                                                                                                                                | 1.71 | 1.8   | 1.89 | V      |  |

| Supply Voltage, RTC                               | V <sub>RTC</sub>   |                                                                                                                                                                                                                                                                                | 1.71 | 1.8   | 1.89 | V      |  |

| Supply Voltage, GPIO                              | V <sub>DDIO</sub>  |                                                                                                                                                                                                                                                                                | 1.71 | 1.8   | 1.89 | V      |  |

| Supply Voltage, GPIO (High)                       | V <sub>DDIOH</sub> |                                                                                                                                                                                                                                                                                | 1.71 | 1.8   | 3.6  | V      |  |

|                                                   |                    | Monitors V <sub>CORE</sub>                                                                                                                                                                                                                                                     |      | 0.835 |      |        |  |

| Power-Fail Reset Voltage                          | V <sub>RST</sub>   | Monitors V <sub>DDA</sub>                                                                                                                                                                                                                                                      |      | 1.67  |      | V      |  |

| rower-rail Neset voltage                          | VRSI               | Monitors V <sub>RTC</sub>                                                                                                                                                                                                                                                      |      | 1.67  |      |        |  |

|                                                   |                    | Monitors V <sub>DDIO</sub>                                                                                                                                                                                                                                                     |      | 1.67  |      |        |  |

| Power-Fail Reset Voltage                          | V <sub>RST</sub>   | Monitors V <sub>DDB</sub>                                                                                                                                                                                                                                                      |      | 2.95  |      | V      |  |

| Power-Fail Reset Voltage                          | V <sub>RST</sub>   | Monitors V <sub>DDIOH</sub>                                                                                                                                                                                                                                                    |      | 1.67  |      | V      |  |

|                                                   |                    | Monitors V <sub>CORE</sub>                                                                                                                                                                                                                                                     |      | 0.594 |      |        |  |

| Power-On Reset Voltage                            | V <sub>POR</sub>   | Monitors V <sub>DDA</sub>                                                                                                                                                                                                                                                      |      | 1.52  | V    |        |  |

|                                                   |                    | Monitors V <sub>RTC</sub>                                                                                                                                                                                                                                                      |      | 1.17  |      |        |  |

| RAM Data Retention<br>Voltage                     | V <sub>DRV</sub>   |                                                                                                                                                                                                                                                                                |      | 0.81  |      | V      |  |

| V <sub>CORE</sub> Dynamic Current,<br>Active Mode | ICORE_DACT         | Total current into $V_{CORE}$ pins, $f_{SYS\_CLK}$ = 120MHz, $V_{CORE}$ = 1.1V, CPU in Active mode, executing from cache, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ , outputs source/sink 0mA                                                                      |      | 95    |      | µA/MHz |  |

| V <sub>CORE</sub> Fixed Current,                  |                    | 120MHz oscillator enabled, total current into V <sub>CORE</sub> pins, CPU in Active mode 0MHz execution, inputs tied to V <sub>SS</sub> , V <sub>DDIOH</sub> , or V <sub>DDIOH</sub> , outputs source/sink 0mA                                                                 |      | 1020  |      |        |  |

| Active Mode                                       | I ICODE EACT       | 7.3728MHz oscillator enabled, total current into V <sub>CORE</sub> pins, CPU in Active mode 0MHz execution, inputs tied to V <sub>SS</sub> , V <sub>DDIO</sub> , or V <sub>DDIOH</sub> , outputs source/sink 0mA                                                               |      | 356   |      | μΑ     |  |

| V <sub>DDA</sub> Fixed Current,<br>Active Mode    |                    | 120MHz oscillator enabled, total current into V <sub>DDA</sub> pins, CPU in Active mode 0MHz execution, inputs tied to V <sub>SS</sub> , V <sub>DDIO</sub> , or V <sub>DDIOH</sub> , outputs source/sink 0mA , V <sub>CORE</sub> and V <sub>DDA</sub> voltage monitors enabled |      | 348   |      | μΑ     |  |

|                                                   |                    | 7.3728MHz oscillator enabled, total current into $V_{DDA}$ pins, CPU in Active mode 0MHz execution, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ , outputs source/sink 0mA , $V_{CORE}$ and $V_{DDA}$ voltage monitors enabled                                        |      | 39    |      | μΛ     |  |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General Purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                                             | SYMBOL                  | CONDITIONS                                                                                                                         | MIN | TYP  | MAX | UNITS  |

|-------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| V <sub>CORE</sub> Dynamic Current,<br>Sleep Mode      | ICORE_DSLP              | Total current into V <sub>CORE</sub> pins, CPU in Sleep mode, standard DMA with two channels active                                |     | 114  |     | µA/MHz |

| V <sub>CORE</sub> Fixed Current,                      | loops so s              | f <sub>SYS_CLK</sub> = 120MHz, total current into V <sub>CORE</sub> pins, CPU in Sleep mode, standard DMA with two channels active |     | 1020 |     |        |

| Sleep Mode                                            | ICORE_FSLP              | $f_{SYS\_CLK}$ = 7.3728MHz, total current into $V_{CORE}$ pins, CPU in Sleep mode, standard DMA with two channels active           |     | 356  |     | · μΑ   |

| V <sub>DDA</sub> Fixed Current,                       | 1                       | f <sub>SYS_CLK</sub> = 120MHz, total current into V <sub>DDA</sub> pins, CPU in Sleep mode, Standard DMA with two channels active  |     | 348  |     |        |

| Sleep Mode                                            | IDDA_FSLP               | $f_{SYS\_CLK}$ = 7.3728MHz, total current into $V_{DDA}$ pins, CPU in Sleep mode, standard DMA with two channels active            |     | 49   |     | - μA   |

| V <sub>CORE</sub> Dynamic Current,<br>Background Mode | I <sub>CORE_DBKG</sub>  | $f_{SYS\_CLK}$ = 7.3728MHz, total current into $V_{CORE}$ pins, CPU in Deep-sleep mode, SmartDMA active                            |     | 66   |     | μΑ/MHz |

| V <sub>CORE</sub> Fixed Current,<br>Background Mode   | CORE_FBGD               | 7.3728MHz oscillator enabled, total current into $V_{\mbox{CORE}}$ pins, CPU in Deep-sleep mode, SmartDMA active                   |     | 162  |     | μА     |

| V <sub>CORE</sub> Fixed Current,<br>Deep-Sleep Mode   | ICORE_FDSL              | Standby state with full data retention                                                                                             |     | 70   |     | μA     |

| V <sub>DDA</sub> Fixed Current,<br>Deep-Sleep Mode    | I <sub>DDA_FDSL</sub>   | Standby state with full data retention, $V_{\mbox{CORE}}$ and $V_{\mbox{DDA}}$ voltage monitors enabled                            |     | 132  |     | nA     |

| V <sub>RTC</sub> Fixed Current,<br>Deep-Sleep Mode    | I <sub>DDRTC_FDSL</sub> | Standby state with full data retention, V <sub>RTC</sub> = 1.8V, RTC enabled                                                       |     | 540  |     | nA     |

| V <sub>CORE</sub> Fixed Current,<br>Backup Mode       | ICORE_FBKU              | No SRAM retention (0KB)                                                                                                            |     | 30   |     | nA     |

| V <sub>DDA</sub> Fixed Current,<br>Backup Mode        | I <sub>DDA_FBKU</sub>   | V <sub>DDA</sub> voltage monitor enabled                                                                                           |     | 132  |     | nA     |

|                                                       |                         | RTC enabled, retention regulator off                                                                                               |     | 540  |     |        |

| V <sub>RTC</sub> Fixed Current,<br>Backup Mode        | IDDRTC_FBKU             | RTC enabled, 32KB SRAM retained, retention regulator on                                                                            |     | 720  |     | nA     |

|                                                       |                         | RTC disabled, retention regulator off                                                                                              |     | 156  |     |        |

| Sleep Mode Resume<br>Time                             | t <sub>SLP_ON</sub>     |                                                                                                                                    |     | 575  |     | ns     |

| Deep-Sleep Mode                                       | too                     | Wake to 40MHz                                                                                                                      |     | 9    |     | lie.   |

| Resume Time                                           | t <sub>DSL_ON</sub>     | Wake to 120MHz                                                                                                                     | 18  |      |     | μs     |

| Backup Mode Resume<br>Time                            | t <sub>BKU_ON</sub>     |                                                                                                                                    |     | 5    |     | ms     |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General-purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                                               | SYMBOL              | CONDITIONS                                                  | MIN                    | TYP          | MAX              | UNITS |

|---------------------------------------------------------|---------------------|-------------------------------------------------------------|------------------------|--------------|------------------|-------|

| USB                                                     |                     |                                                             |                        |              |                  |       |

| USB Supply Voltage                                      | $V_{DDB}$           |                                                             | 3.0                    | 3.3          | 3.6              | V     |

| D+, D- Pin Capacitance                                  | C <sub>IN_USB</sub> | Pin to V <sub>SS</sub>                                      |                        | 8            |                  | pF    |

| Driver Output Resistance                                | $R_{DRV}$           | Steady state drive                                          |                        | 45<br>±10%   |                  | Ω     |

| USB/FULL SPEED                                          |                     |                                                             |                        |              |                  |       |

| Single-Ended Input High<br>Voltage (DP, DM)             | V <sub>IH_USB</sub> |                                                             | 2.0                    |              |                  | V     |

| Single-Ended Input Low<br>Voltage (DP, DM)              | V <sub>IL_USB</sub> |                                                             |                        |              | 0.6              | V     |

| Output High Voltage<br>(DP, DM)                         | V <sub>OH_USB</sub> | $R_L$ = 1.5 kΩ from DP and DM to $V_{SS}$ , $I_{OH}$ = -4mA | V <sub>DDB</sub> - 0.4 |              | V <sub>DDB</sub> | V     |

| Output Low Voltage<br>(DP, DM)                          | V <sub>OL_USB</sub> | $R_L$ = 1.5 kΩ from DP to $V_{DDB}$ , $I_{OL}$ = 4mA        | V <sub>SS</sub>        |              | 0.4              | V     |

| Differential Input<br>Sensitivity                       | $V_{DI}$            | DP to DM                                                    | 0.2                    |              |                  | V     |

| Common Mode Voltage<br>Range                            | $V_{CM}$            | Includes V <sub>DI</sub> range                              | 0.8                    |              | 2.5              | V     |

| Transition Time (Rise/Fall)<br>D+, D- (Note 11)         | t <sub>RF</sub>     | C <sub>L</sub> = 50pF                                       | 4                      |              | 20               | ns    |

| Pullup Resistor on<br>Upstream Ports                    | R <sub>PU</sub>     |                                                             | 1.05                   | 1.5          | 1.95             | kΩ    |

| USB/HI-SPEED                                            |                     |                                                             |                        |              |                  |       |

| Hi-Speed Data Signaling<br>Common-Mode Voltage<br>Range | V <sub>HSCM</sub>   |                                                             | -50                    |              | +500             | mV    |

| Hi-Speed Squelch                                        | $V_{HSSQ}$          | Squelch detected                                            |                        | 100          |                  | mV    |

| Detection Threshold                                     | * HSSQ              | No squelch detected                                         |                        | 200          |                  | 1110  |

| Hi-Speed Idle Level<br>Output Voltage                   | V <sub>HSOI</sub>   |                                                             | -10                    |              | +10              | mV    |

| Hi-Speed Low Level<br>Output Voltage                    | $V_{HSOL}$          |                                                             | -10                    |              | +10              | mV    |

| Hi-Speed High Level<br>Output Voltage                   | V <sub>HSOH</sub>   |                                                             |                        | 400<br>± 40  |                  | mV    |

| Chirp-J Output Voltage (Differential)                   | V <sub>CHIRPJ</sub> |                                                             |                        | 900<br>±200  |                  | mV    |

| Chirp-K Output Voltage<br>(Differential)                | V <sub>CHIRPK</sub> |                                                             |                        | -700<br>±200 |                  | mV    |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General Purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                                                                 | SYMBOL                  | CONDITIONS                                                                                 | MIN                          | TYP     | MAX                         | UNITS |

|---------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|------------------------------|---------|-----------------------------|-------|

| CLOCKS                                                                    |                         |                                                                                            |                              |         |                             |       |

| System Clock Frequency                                                    | f <sub>SYS_CLK</sub>    |                                                                                            | 0.256                        |         | 120,000                     | kHz   |

| System Clock Period                                                       | tsys_clk                |                                                                                            | 1/                           | fsys_cl | .K                          | ns    |

| High-Speed Oscillator Frequency                                           | f <sub>HSCLK</sub>      | Measured at +25°C, 120MHz                                                                  |                              | 120 ±1  |                             | MHz   |

| Low-Power Oscillator<br>Frequency                                         | fLPCLK                  |                                                                                            |                              | 40      |                             | MHz   |

| 7MHz Oscillator<br>Frequency                                              | f <sub>7</sub> MCLK     |                                                                                            |                              | 7.3728  |                             | MHz   |

| Nano-Ring Oscillator<br>Frequency                                         | f <sub>NANO</sub>       |                                                                                            |                              | 8       |                             | KHz   |

| RTC Input Frequency                                                       | f <sub>32KIN</sub>      | 32kHz watch crystal, $C_L$ = 6pF, ESR < 70kΩ                                               |                              | 32.768  |                             | kHz   |

| RTC Operating Current                                                     | I <sub>RTC_ACTSLP</sub> | Sleep or Active mode                                                                       |                              | 0.39    |                             | μΑ    |

| RTC Power Up Time                                                         | t <sub>RTC</sub> ON     |                                                                                            |                              | 250     |                             | ms    |

| GENERAL-PURPOSE I/O                                                       |                         |                                                                                            |                              |         |                             |       |

| Input Low Voltage for All GPIO                                            | V <sub>IL_VDDIO</sub>   | V <sub>DDIO</sub> selected as I/O supply                                                   |                              |         | 0.3 ×<br>V <sub>DDIO</sub>  | V     |

| Input Low Voltage for All<br>GPIO except P1.[21:18],<br>P1.[16:11], P3.0  | V <sub>IL_</sub> VDDIOH | V <sub>DDIOH</sub> selected as I/O supply                                                  |                              |         | 0.3 ×<br>V <sub>DDIOH</sub> | V     |

| Input Low Voltage for RSTN                                                | V <sub>IL_RSTN</sub>    |                                                                                            |                              |         | 0.3 ×<br>V <sub>DDIO</sub>  | V     |

| Input High Voltage for All GPIO                                           | V <sub>IH_VDDIO</sub>   | V <sub>DDIO</sub> selected as I/O supply                                                   | 0.75 ×<br>V <sub>DDIO</sub>  |         |                             | V     |

| Input High Voltage for All<br>GPIO except P1.[21:18],<br>P1.[16:11], P3.0 | V <sub>IH_</sub> VDDIOH | V <sub>DDIOH</sub> selected as I/O supply                                                  | 0.75 ×<br>V <sub>DDIOH</sub> |         |                             | V     |

| Input High Voltage for RSTN                                               | V <sub>IH_RSTN</sub>    |                                                                                            | 0.75 x<br>V <sub>DDIO</sub>  |         |                             | V     |

|                                                                           |                         | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 00, I <sub>OL</sub> = 1mA |                              | 0.2     | 0.4                         |       |

| Output Low Voltage for All                                                | V                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = 2mA |                              | 0.2     | 0.4                         | V     |

| GPIO                                                                      | Vol_vddio               | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 10, I <sub>OL</sub> = 4mA |                              | 0.2     | 0.4                         | V     |

|                                                                           |                         | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 11, I <sub>OL</sub> = 8mA |                              | 0.2     | 0.4                         |       |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General-purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                                           | SYMBOL                  | CONDITIONS                                                                                                                              | MIN                         | TYP | MAX   | UNITS |

|-----------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-------|-------|

|                                                     |                         | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 00, I <sub>OL</sub> = 1mA                                            |                             | 0.2 | 0.4   |       |

| Output Low Voltage for All                          | V                       | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub> = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = 2mA                              |                             | 0.2 | 0.4   |       |

| GPIO except P1.[21:18],<br>P1.[16:11], P3.0         | V <sub>OL_</sub> VDDIOH | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub> = 1.71V, DS[1:0] = 10, I <sub>OL</sub> = 4mA                              |                             | 0.2 | 0.4   | V     |

|                                                     |                         | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub> = 1.71V, DS[1:0] = 11, I <sub>OL</sub> = 8mA                              |                             | 0.2 | 0.4   |       |

| Combined I <sub>OL</sub> , All GPIO                 | I <sub>OL_TOTAL</sub>   |                                                                                                                                         |                             |     | 48    | mA    |

|                                                     |                         | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 00, I <sub>OL</sub> = -1mA                                             | V <sub>DDIO</sub><br>- 0.4  |     |       |       |

| Output High Voltage for                             | V                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = -2mA                                             | V <sub>DDIO</sub><br>- 0.4  |     |       | V     |

| All GPIO                                            | V <sub>OH</sub> _VDDIO  | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 10, $I_{OL}$ = -4mA                                                    | V <sub>DDIO</sub><br>- 0.4  |     |       | V     |

|                                                     |                         | V <sub>DDIO</sub> selected as I/O supply, V <sub>DDIO</sub> = 1.71V,<br>DS[1:0] = 00, I <sub>OL</sub> = -8mA                            | V <sub>DDIO</sub><br>- 0.4  |     |       |       |

|                                                     |                         | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub> = 1.71V, DS[1:0] = 00, I <sub>OL</sub> = -1mA                             | V <sub>DDIOH</sub><br>- 0.4 |     |       | V     |

| Output High Voltage for All GPIO except P1.[21:18], |                         | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = -2mA                                           | V <sub>DDIOH</sub><br>- 0.4 |     |       |       |

| P1.[16:11], P3.0                                    |                         | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 10, $I_{OL}$ = -8mA                                                  | V <sub>DDIOH</sub><br>- 0.4 |     |       |       |

|                                                     |                         | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 11, I <sub>OL</sub> = -8mA                                           | V <sub>DDIOH</sub><br>- 0.4 |     |       |       |

| Combined I <sub>OH</sub> , All GPIO                 | I <sub>OH_TOTAL</sub>   |                                                                                                                                         |                             |     | -48   | mA    |

| Input Hysteresis (Schmitt)                          | V <sub>IHYS</sub>       |                                                                                                                                         |                             | 300 |       | mV    |

| Input Leakage Current<br>Low                        | I <sub>IL</sub>         | $V_{DDIO}$ = 1.89V, $V_{DDIOH}$ = 3.6V, $V_{DDIOH}$ selected as I/O supply, $V_{IN}$ = 0V, internal pullup disabled                     | -1000                       |     | +1000 | nA    |

|                                                     | I <sub>IH</sub>         | $V_{\rm DDIO}$ = 1.89V, $V_{\rm DDIOH}$ = 3.6V, $V_{\rm DDIOH}$ selected as I/O supply, $V_{\rm IN}$ = 3.6V, internal pulldown disabled | -1000                       |     | +1000 | nA    |

| Input Leakage Current<br>High                       | l <sub>OFF</sub>        | $V_{DDIO}$ = 0V, $V_{DDIOH}$ = 0V, $V_{DDIO}$ selected as I/O supply, $V_{IN}$ < 1.89V                                                  | -1                          |     | +1    |       |

|                                                     | I <sub>IH3V</sub>       | $V_{DDIO} = V_{DDIOH} = 1.71V$ , $V_{DDIO}$ selected as I/O supply, $V_{IN} = 3.6V$                                                     | -2                          |     | +2    | μA    |

| Input Pullup Resistor<br>TMS, TCK, TDI              | R <sub>PU_T</sub>       |                                                                                                                                         |                             | 25  |       | kΩ    |

| Input Pullup Resistor<br>RSTN                       | R <sub>PU_R</sub>       |                                                                                                                                         |                             | 1   |       | ΜΩ    |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General-purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                          | SYMBOL               | CONDITIONS                                                  | MIN                     | TYP                 | MAX                | UNITS             |

|------------------------------------|----------------------|-------------------------------------------------------------|-------------------------|---------------------|--------------------|-------------------|

| Input Pullup/Pulldown              | R <sub>PU1</sub>     | Normal resistance                                           |                         | 25                  |                    | kΩ                |

| Resistor for All GPIO              | R <sub>PU2</sub>     | Highest resistance                                          |                         | 1                   |                    | МΩ                |

| FLASH MEMORY                       |                      |                                                             |                         |                     |                    |                   |

| Floob France Times                 | t <sub>M_ERASE</sub> | Mass erase                                                  |                         | 30                  |                    |                   |

| Flash Erase Time                   | t <sub>P</sub> ERASE | Page erase                                                  |                         | 30                  |                    | ms                |

| Flash Programming Time<br>Per Word | t <sub>PROG</sub>    |                                                             |                         | 60                  |                    | μs                |

| Flash Endurance                    |                      |                                                             | 10                      |                     |                    | kcycles           |

| Data Retention                     | t <sub>RET</sub>     | T <sub>A</sub> = +85°C                                      | 10                      |                     |                    | years             |

| ADC (DELTA-SIGMA)                  |                      |                                                             |                         |                     |                    |                   |

| Resolution                         |                      |                                                             |                         | 10                  |                    | Bits              |

| ADC Clock Rate                     | fACLK                |                                                             | 0.1                     |                     | 8                  | MHz               |

| ADC Clock Period                   | t <sub>ACLK</sub>    |                                                             |                         | 1/f <sub>ACLK</sub> |                    | μs                |

|                                    |                      | AIN[3:0], ADC_CHSEL = 0-3, ADC_REFSEL = 1                   | V <sub>SSA</sub> + 0.05 |                     | V <sub>BG</sub> /2 |                   |

| Input Voltage Range                | V <sub>AIN</sub>     | AIN[3:0], ADC_CHSEL = 0-3, ADC_REFSEL = 0                   | V <sub>SSA</sub> + 0.05 |                     | $V_{BG}$           | V                 |

|                                    |                      | AIN[1:0], ADC_CHSEL = 4-5, ADC_REFSEL = 0                   | V <sub>SSA</sub> + 0.05 |                     | 5.5                |                   |

| Input Impedance                    | R <sub>AIN</sub>     | AIN[1:0], ADC_CHSEL = 4-5, ADC active                       |                         | 40                  |                    | kΩ                |

|                                    |                      | Fixed capacitance to V <sub>SSA</sub>                       |                         | 1                   |                    | pF                |

| Analog Input Capacitance           | C <sub>AIN</sub>     | Dynamically switched capacitance                            |                         | 250                 |                    | fF                |

| Integral Nonlinearity              | INL                  |                                                             | -2                      |                     | +2                 | LSb               |

| Differential Nonlinearity          | DNL                  |                                                             | -1                      |                     | +2                 | LSb               |

| Offset Error                       | Vos                  |                                                             |                         | ±1                  |                    | LSb               |

| Gain Error                         | GE                   |                                                             |                         | ±2                  |                    | LSb               |

| ADC Active Current                 | I <sub>ADC</sub>     | ADC active, reference buffer enabled, input buffer disabled |                         | 210                 |                    | μA                |

| ADC Setup Time                     | t <sub>ADC_SU</sub>  | Any powerup of: ADC clock or ADC bias to CpuAdcStart        |                         |                     | 10                 | μs                |

| ADC Output Latency                 | t <sub>ADC</sub>     |                                                             |                         | 1025                |                    | t <sub>ACLK</sub> |

| ADC Sample Rate                    | f <sub>ADC</sub>     |                                                             |                         |                     | 7.8                | ksps              |

| ADC lawyth and                     |                      | AIN0 or AIN1, ADC inactive or channel not selected          |                         | 0.01                |                    | A                 |

| ADC Input Leakage                  |                      | AIN2 or AIN3, ADC inactive or channel not selected          |                         | 0.01                |                    | nA                |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General-purpose I/O are only tested at  $T_A$  = +105°C.)

| PARAMETER                           | SYMBOL              | CONDITIONS                                               | MIN | TYP | MAX | UNITS |

|-------------------------------------|---------------------|----------------------------------------------------------|-----|-----|-----|-------|

| AIN0/AIN1 Resistor<br>Divider Error |                     | ADC_CHSEL = 4 or 5, not including ADC offset/gain error. |     | ±2  |     | LSb   |

| Full-Scale Voltage                  | V <sub>FS</sub>     | ADC code = 0x3FF                                         |     | 1.2 |     | V     |

| Bandgap Temperature<br>Coefficient  | V <sub>TEMPCO</sub> | From +25°C to +105°C                                     |     | 15  |     | ppm   |

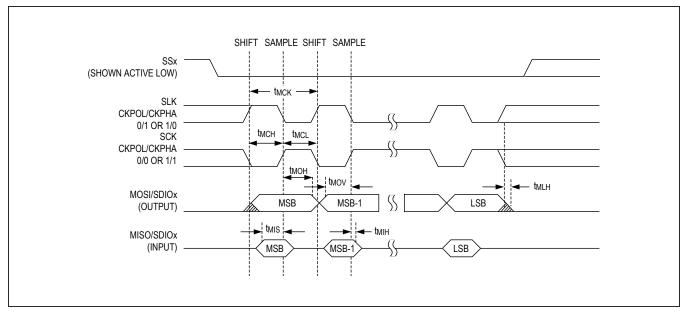

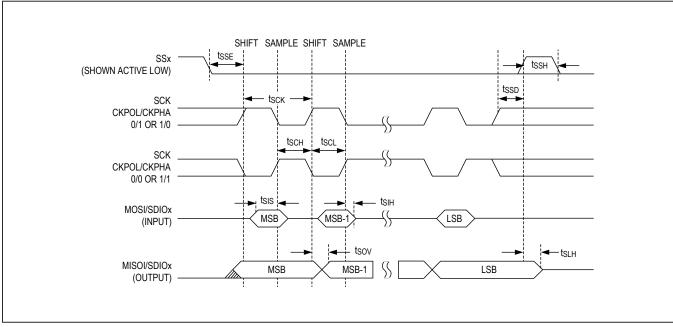

#### **Electrical Characteristics—SPI**

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                             | SYMBOL                              | CONDITIONS                                      | MIN                 | TYP                 | MAX | UNITS |

|-------------------------------------------------------|-------------------------------------|-------------------------------------------------|---------------------|---------------------|-----|-------|

| MASTER MODE                                           |                                     |                                                 |                     |                     |     |       |

| SPI Master Operating Frequency                        | f <sub>MCK</sub>                    | f <sub>MCK(MAX)</sub> = f <sub>SYS_CLK</sub> /2 |                     |                     | 60  | MHz   |

| SPI Master SCK Period                                 | t <sub>MCK</sub>                    |                                                 |                     | 1/f <sub>MCK</sub>  |     | ns    |

| SCK Output Pulse-Width<br>High/Low                    | t <sub>MCH</sub> , t <sub>MCL</sub> |                                                 | t <sub>MCK</sub> /2 |                     |     | ns    |

| MOSI Output Hold Time After SCK Sample Edge           | t <sub>MOH</sub>                    |                                                 | t <sub>MCK</sub> /2 |                     |     | ns    |

| MOSI Output Valid to Sample<br>Edge                   | t <sub>MOV</sub>                    |                                                 | t <sub>MCK</sub> /2 |                     |     | ns    |

| MISO Input Valid to SCK<br>Sample Edge Setup          | t <sub>MIS</sub>                    |                                                 |                     | 5                   |     | ns    |

| MISO Input to SCK Sample<br>Edge Hold                 | t <sub>MIH</sub>                    |                                                 |                     | t <sub>MCK</sub> /2 |     | ns    |

| SLAVE MODE                                            | ,                                   |                                                 | ·                   |                     |     |       |

| SPI Slave Operating Frequency                         | fsck                                |                                                 |                     |                     | 48  | MHz   |

| SPI Slave SCK Period                                  | t <sub>SCK</sub>                    |                                                 |                     | 1/f <sub>SCK</sub>  |     | ns    |

| SCK Input Pulse-Width<br>High/Low                     | t <sub>SCH</sub> , t <sub>SCL</sub> |                                                 |                     | t <sub>SCK</sub> /2 |     |       |

| SSx Active to First Shift Edge                        | t <sub>SSE</sub>                    |                                                 |                     | 10                  |     | ns    |

| MOSI Input to SCK Sample<br>Edge Rise/Fall Setup      | tsis                                |                                                 |                     | 5                   |     | ns    |

| MOSI Input from SCK Sample<br>Edge Transition Hold    | tsiH                                |                                                 |                     | 1                   |     | ns    |

| MISO Output Valid After SCLK<br>Shift Edge Transition | t <sub>SOV</sub>                    |                                                 |                     | 5                   |     | ns    |

| SCK Inactive to SSx Inactive                          | t <sub>SSD</sub>                    |                                                 |                     | 10                  |     | ns    |

| SSx Inactive Time                                     | tssh                                |                                                 |                     | 1/f <sub>SCK</sub>  |     | μs    |

Figure 1. SPI Master Mode Timing Diagram

Figure 2. SPI Slave Mode Timing Diagram

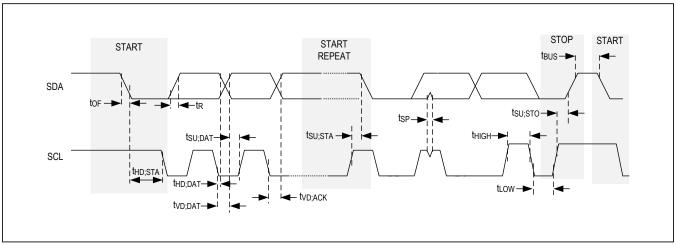

### Electrical Characteristics—I<sup>2</sup>C

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                                                       | MIN  | TYP | MAX | UNITS |

|-----------------------------------------------------|---------------------|------------------------------------------------------------------|------|-----|-----|-------|

| STANDARD MODE                                       |                     |                                                                  |      |     |     |       |

| Output Fall Time                                    | t <sub>OF</sub>     | Standard mode, from V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> |      | 150 |     | ns    |

| SCL Clock Frequency                                 | f <sub>SCL</sub>    |                                                                  | 0    |     | 100 | kHz   |

| Low Period SCL Clock                                | t <sub>LOW</sub>    |                                                                  | 4.7  |     |     | μs    |

| High Time SCL Clock                                 | tHIGH               |                                                                  | 4.0  |     |     | μs    |

| Setup Time for Repeated<br>Start Condition          | t <sub>SU;STA</sub> |                                                                  | 4.7  |     |     | μs    |

| Hold Time for Repeated Start<br>Condition           | t <sub>HD;STA</sub> |                                                                  | 4.0  |     |     | μs    |

| Data Setup Time                                     | t <sub>SU;DAT</sub> |                                                                  |      | 300 |     | ns    |

| Data Hold Time                                      | t <sub>HD;DAT</sub> |                                                                  |      | 10  |     | ns    |

| Rise Time for SDA and SCL                           | t <sub>R</sub>      |                                                                  |      | 800 |     | ns    |

| Fall Time for SDA and SCL                           | t <sub>F</sub>      |                                                                  |      | 200 |     | ns    |

| Setup Time for a Stop<br>Condition                  | t <sub>SU;STO</sub> |                                                                  | 4.0  |     |     | μs    |

| Bus Free Time Between a<br>Stop and Start Condition | t <sub>BUS</sub>    |                                                                  | 4.7  |     |     | μs    |

| Data Valid Time                                     | t <sub>VD;DAT</sub> |                                                                  | 3.45 |     |     | μs    |

| Data Valid Acknowledge Time                         | t <sub>VD;ACK</sub> |                                                                  | 3.45 |     |     | μs    |

| FAST MODE                                           |                     |                                                                  |      |     |     |       |

| Output Fall Time                                    | t <sub>OF</sub>     | From V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub>                |      | 150 |     | ns    |

| Pulse Width Suppressed by Input Filter              | t <sub>SP</sub>     |                                                                  |      | 75  |     | ns    |

| SCL Clock Frequency                                 | f <sub>SCL</sub>    |                                                                  | 0    |     | 400 | kHz   |

| Low Period SCL Clock                                | t <sub>LOW</sub>    |                                                                  | 1.3  |     |     | μs    |

| High Time SCL Clock                                 | tHIGH               |                                                                  | 0.6  |     |     | μs    |

| Setup Time for Repeated<br>Start Condition          | t <sub>SU;STA</sub> |                                                                  | 0.6  |     |     | μs    |

| Hold Time for Repeated Start Condition              | t <sub>HD;STA</sub> |                                                                  | 0.6  |     |     | μs    |

| Data Setup Time                                     | tsu;dat             |                                                                  |      | 125 |     | ns    |

| Data Hold Time                                      | t <sub>HD;DAT</sub> |                                                                  |      | 10  |     | ns    |

| Rise Time for SDA and SCL                           | t <sub>R</sub>      |                                                                  |      | 30  |     | ns    |

| Fall Time for SDA and SCL                           | t <sub>F</sub>      |                                                                  |      | 30  |     | ns    |

| Setup Time for a Stop<br>Condition                  | t <sub>SU;STO</sub> |                                                                  | 0.6  |     |     | μs    |

| Bus Free Time Between a<br>Stop and Start Condition | t <sub>BUS</sub>    |                                                                  | 1.3  |     |     | μs    |

| Data Valid Time                                     | t <sub>VD;DAT</sub> |                                                                  | 0.9  |     |     | μs    |

| Data Valid Acknowledge Time                         | t <sub>VD;ACK</sub> |                                                                  | 0.9  |     | ,   | μs    |

## **Electrical Characteristics—I<sup>2</sup>C (continued)**

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                                        | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------------|---------------------|---------------------------------------------------|------|-----|------|-------|

| FAST MODE PLUS                                      |                     |                                                   | ·    |     |      |       |

| Output Fall Time                                    | t <sub>OF</sub>     | From V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> |      | 80  |      | ns    |

| Pulse Width Suppressed by Input Filter              | t <sub>SP</sub>     |                                                   |      | 75  |      | ns    |

| SCL Clock Frequency                                 | f <sub>SCL</sub>    |                                                   | 0    |     | 1000 | kHz   |

| Low Period SCL Clock                                | t <sub>LOW</sub>    |                                                   | 0.5  |     |      | μs    |

| High Time SCL clock                                 | tHIGH               |                                                   | 0.26 |     |      | μs    |

| Setup Time for Repeated Start Condition             | t <sub>SU;STA</sub> |                                                   | 0.26 |     |      | μs    |

| Hold Time for Repeated Start Condition              | t <sub>HD;STA</sub> |                                                   | 0.26 |     |      | μs    |

| Data Setup Time                                     | t <sub>SU;DAT</sub> |                                                   |      | 50  |      | ns    |

| Data Hold Time                                      | t <sub>HD;DAT</sub> |                                                   |      | 10  |      | ns    |

| Rise Time for SDA and SCL                           | $t_{R}$             |                                                   |      | 50  |      | ns    |

| Fall Time for SDA and SCL                           | t <sub>F</sub>      |                                                   |      | 30  |      | ns    |

| Setup Time for a Stop<br>Condition                  | t <sub>SU;STO</sub> |                                                   | 0.26 |     |      | μs    |

| Bus Free Time Between a<br>Stop and Start Condition | t <sub>BUS</sub>    |                                                   | 0.5  |     |      | μs    |

| Data Valid Time                                     | t <sub>VD;DAT</sub> |                                                   | 0.45 |     |      | μs    |

| Data Valid Acknowledge Time                         | t <sub>VD;ACK</sub> |                                                   | 0.45 |     |      | μs    |

Figure 3. I<sup>2</sup>C Timing Diagram

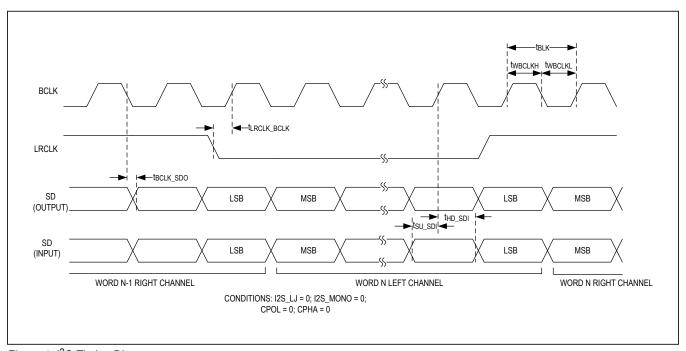

#### Electrical Characteristics—I<sup>2</sup>C Slave

(Timing specifications are guaranteed by design and not production tested,  $T_A = -40$ °C to +105°C.)

| PARAMETER                             | SYMBOL              | CONDITIONS            | MIN | TYP | MAX   | UNITS               |

|---------------------------------------|---------------------|-----------------------|-----|-----|-------|---------------------|

| Bit Clock Frequency                   | f <sub>BCLK</sub>   | 96kHz LRCLK frequency |     |     | 3.072 | MHz                 |

| BCLK High Time                        | twbclkh             |                       |     | 0.5 |       | 1/f <sub>BCLK</sub> |

| BCLK Low Time                         |                     |                       |     | 0.5 |       | 1/f <sub>BCLK</sub> |

| LRCLK Setup Time                      | tLRCLK_BLCK         |                       |     | 25  |       | ns                  |

| Delay Time, BCLK to SD (Output) Valid | tBCLK_SDO           |                       |     | 12  |       | ns                  |

| Setup Time for SD (Input)             | <sup>t</sup> su_sdi |                       |     | 6   |       | ns                  |

| Hold Time SD (Input)                  | t <sub>HD</sub> SDI |                       |     | 3   |       | ns                  |

Figure 4. I<sup>2</sup>S Timing Diagram

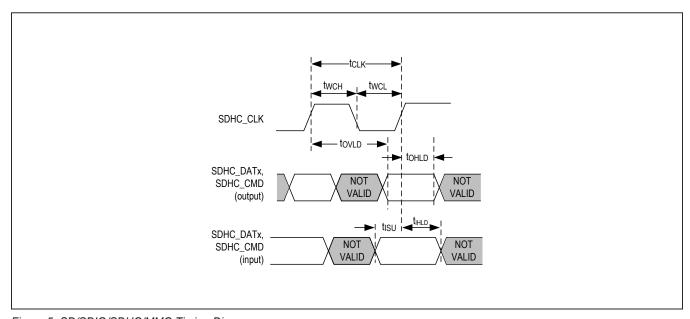

### **Electrical Characteristics—SD/SDIO/SDHC/MMC**

$(T_A = -40^{\circ}C \text{ to } +105^{\circ}C)$

| PARAMETER                                | SYMBOL            | CONDITIONS | MIN | TYP                         | MAX                   | UNITS |

|------------------------------------------|-------------------|------------|-----|-----------------------------|-----------------------|-------|

| Clock Frequency in Data<br>Transfer Mode | fSDHC_CLK         |            | 0   |                             | f <sub>HSCLK</sub> /2 | MHz   |

| Clock Period                             | t <sub>CLK</sub>  |            |     | 1/f <sub>SDHC_</sub><br>CLK |                       | ns    |

| Clock Low Time                           | t <sub>WCL</sub>  |            |     | 7                           |                       | ns    |

| Clock High Time                          | twch              |            |     | 7                           |                       |       |

| Input Setup Time                         | t <sub>ISU</sub>  |            |     | 5                           |                       | ns    |

| Input Hold Time                          | t <sub>IHLD</sub> |            |     | 1                           |                       | ns    |

| Output Valid Time                        | t <sub>OVLD</sub> |            |     | 5                           |                       | ns    |

| Output Hold Time                         | <sup>t</sup> OHLD |            |     | 6                           |                       | ns    |

Figure 5. SD/SDIO/SDHC/MMC Timing Diagram

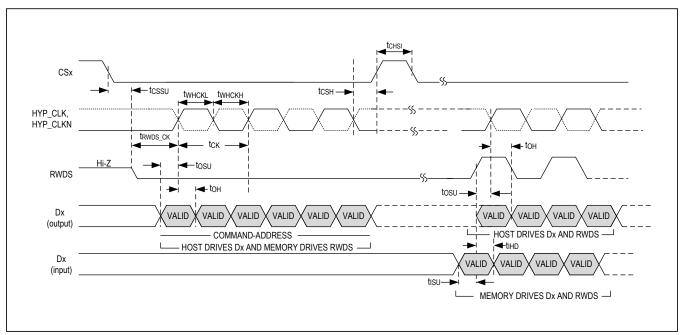

## **Electrical Characteristics—HyperBus**

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                        | SYMBOL               | CONDITIONS | MIN                         | TYP | MAX | UNITS |

|----------------------------------|----------------------|------------|-----------------------------|-----|-----|-------|

| HYP_CLK, HYP_CLKN<br>Frequency   | fHYP_CLK             |            |                             |     | 60  | MHz   |

| HYP_CLK, HYP_CLKN<br>Period      | tHYP_CLK             |            | 1/f <sub>HYP</sub> _<br>CLK |     |     | ns    |

| HYP_CLK, HYP_CLKN<br>High Time   | twhckh               |            |                             | 7   |     | ns    |

| HYP_CLK, HYP_CLKN<br>Low Time    | twhckl               |            |                             | 7   |     | ns    |

| CS Setup to RWDS                 | t <sub>CSSU</sub>    |            |                             | 6   |     | ns    |

| RWDS Setup to CK                 | t <sub>RWDS_CK</sub> |            |                             | 10  |     | ns    |

| Dx Output Setup                  | tosu                 |            |                             | 5   |     | ns    |

| Dx Output Hold                   | tон                  |            |                             | 3   |     | ns    |

| CS Hold After CK Falling<br>Edge | t <sub>CSH</sub>     |            |                             | 5   |     | ns    |

| CS High Between<br>Transactions  | <sup>t</sup> CHSI    |            |                             | 15  |     | ns    |

| Dx Input Setup to RWDS           | t <sub>ISU</sub>     |            |                             | 4   |     | ns    |

| Dx Input Hold                    | t <sub>IHD</sub>     |            |                             | 2   |     | ns    |

Figure 6. HyperBus/Xccela Bus Timing Diagram

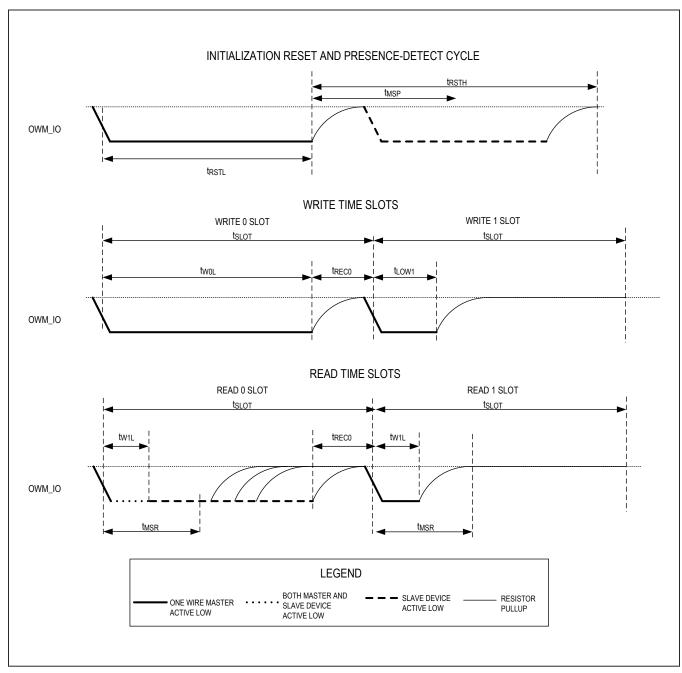

### **Electrical Characteristics—One Wire Master**

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER              | SYMBOL            | CONDITIONS                                                                          | MIN T | YP MAX | UNITS |  |

|------------------------|-------------------|-------------------------------------------------------------------------------------|-------|--------|-------|--|

| Write 0 Low Time       | 4                 | Standard                                                                            | (     | 60     |       |  |

| While o Low Time       | t <sub>WOL</sub>  | Overdrive                                                                           |       | 8      | μs    |  |

|                        |                   | Standard                                                                            |       | 6      |       |  |

| Write 1 Low Time       | t <sub>W1L</sub>  | Standard, Long Line mode                                                            |       | 8      | μs    |  |

|                        |                   | Overdrive                                                                           |       | 1      |       |  |

|                        |                   | Standard                                                                            | -     | 70     |       |  |

| Presence Detect Sample | t <sub>MSP</sub>  | Standard, Long Line mode                                                            | 8     | 35     | μs    |  |

|                        |                   | Overdrive                                                                           |       | 9      |       |  |

|                        |                   | Standard                                                                            |       | 15     |       |  |

| Read Data Value        | t <sub>MSR</sub>  | Standard, Long Line mode                                                            | 2     | 24     | μs    |  |

|                        |                   | Overdrive 3                                                                         |       | 3      |       |  |

|                        |                   | Standard         10           t <sub>REC0</sub> Standard, Long Line mode         20 |       | 10     |       |  |

| Recovery Time          | t <sub>REC0</sub> |                                                                                     |       | 20     | μs    |  |

|                        |                   | Overdrive 4                                                                         |       | 4      |       |  |

| Dood Time High         | +                 | Standard                                                                            | 480   |        | μs    |  |

| Reset Time High        | <sup>t</sup> RSTH | Overdrive                                                                           | 58    |        |       |  |

| Reset Time Low         | 4                 | Standard                                                                            |       | 600    |       |  |

| Reset Time LOW         | <sup>t</sup> RSTL | Overdrive 70                                                                        |       | 70     | – µs  |  |

| Time Clet              | 4                 | Standard                                                                            | 70    |        |       |  |

| Time Slot              | <sup>I</sup> SLOT | t <sub>SLOT</sub> Overdrive 12                                                      |       | 12     | μs    |  |

Figure 7. One-Wire Master Data Timing Diagram

## **Pin Configurations**

## **Pin Configurations (continued)**

## **Pin Configurations (continued)**

## **Pin Description**

|                                               | PIN                          |                                                       |                    |                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------|------------------------------|-------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 140 WLP                                       | 96 WLP                       | 144 TQFP                                              | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                  |

| POWER                                         |                              |                                                       |                    |                                                                                                                                                                                                                                                                                                                                                                           |

| H1, H4,<br>D12                                | G1, C8                       | 5, 14, 88                                             | V <sub>CORE</sub>  | Core Supply Voltage. This pin must be bypassed to V <sub>SS</sub> with a 1.0µF capacitor as close as possible to the package.                                                                                                                                                                                                                                             |

| H11                                           | G10                          | 99                                                    | $V_{DDA}$          | 1.8V Analog Supply Voltage. This pin must be bypassed to $V_{SSA}$ with 1.0 $\mu$ F and 0.01 $\mu$ F capacitors as close as possible to the package.                                                                                                                                                                                                                      |

| B11                                           | В9                           | 76                                                    | $V_{DDB}$          | USB Transceiver Supply Voltage. This pin must be bypassed to V <sub>SS</sub> with a 1.0µF capacitor as close as possible to the package.                                                                                                                                                                                                                                  |