Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Features

# +3.3V, 2.5Gbps Low-Power Laser Driver

## **General Description**

The MAX3273 is a compact, low-power laser driver for applications up to 2.7Gbps. The device uses a single +3.3V supply and typically consumes 30mA. The bias and modulation current levels are programmed by external resistors. An automatic power-control (APC) loop is incorporated to maintain a constant average optical power over temperature and lifetime. The laser driver is fabricated using Maxim's in-house, secondgeneration SiGe process.

The MAX3273 accepts differential CML-compatible clock and data input signals. Inputs are self-biased to allow AC-coupling. An input data-retiming latch can be enabled to reject input jitter if a clock signal is available.

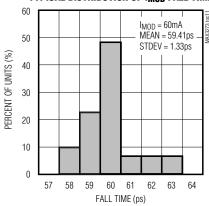

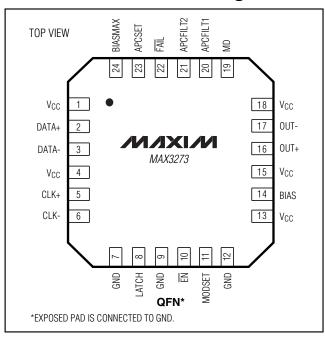

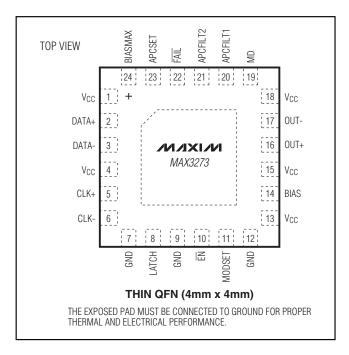

The driver can provide bias current up to 100mA and modulation current up to 60mAp-p with typical (20% to 80%) edge speeds of 59ps. A failure-monitor output is provided to indicate when the APC loop is unable to maintain average optical power. The MAX3273 is available in 4mm × 4mm, 24-pin QFN and thin QFN packages, as well as in die form.

## **Applications**

SONET OC-48 and SDH STM-16 **Transmission Systems** Add/Drop Multiplexers Digital Cross-Connects 2.5Gbps Optical Transmitters

### Pin Configurations appear at end of data sheet.

## **♦ 30mA Power-Supply Current**

- ♦ Single +3.3V Power Supply

- ♦ Up to 2.7Gbps (NRZ) Operation

- **♦ Automatic Average Power Control with Failure Monitor**

- ♦ Programmable Modulation Current from 5mA to 60mA

- ♦ Programmable Bias Current from 1mA to 100mA

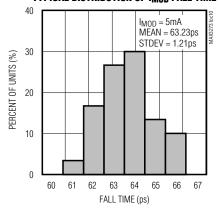

- ♦ Typical Fall Time of 59ps

- ♦ Selectable Data Retiming Latch

- ♦ Complies with ANSI, ITU, and Bellcore **SDH/SONET Specifications**

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE            | PACKAGE<br>CODE |

|-------------|----------------|----------------------------|-----------------|

| MAX3273EGG  | -40°C to +85°C | 24 QFN<br>(4mm × 4mm)      | G2444-1         |

| MAX3273ETG+ | -40°C to +85°C | 24 Thin QFN<br>(4mm × 4mm) | T2444-2         |

| MAX3273E/D  | -40°C to +85°C | Dice*                      | _               |

<sup>\*</sup>Dice are designed to operate from  $T_A = -40$ °C to +85°C, but are tested and guaranteed at  $T_A = +25^{\circ}C$  only.

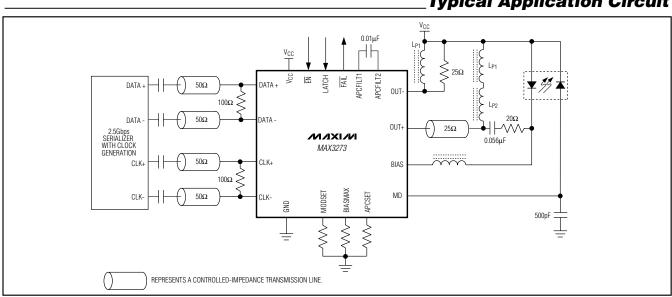

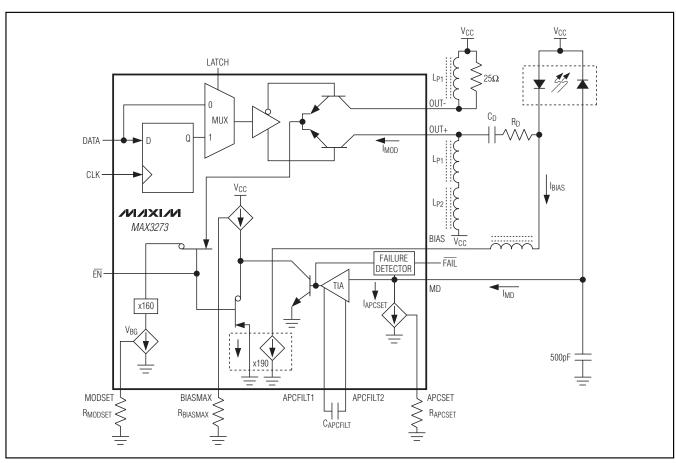

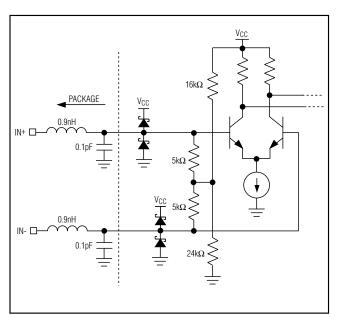

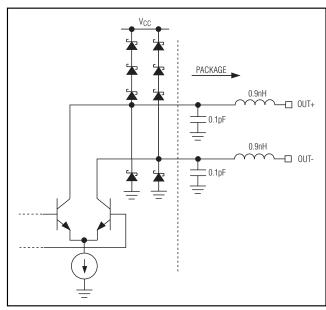

# Typical Application Circuit

<sup>+</sup>Denotes lead-free package.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VCC            |                                   |

|--------------------------------|-----------------------------------|

| Current into BIAS, OUT+, OUT   | 20mA to +150mA                    |

| Current into MD                | 5mA to +5mA                       |

| Voltage at DATA+, DATA-, CLK+, |                                   |

| CLK-, LATCH, EN, FAIL          | 0.5V to $(V_{CC} + 0.5V)$         |

| Voltage at MODSET, BIASMAX,    |                                   |

| APCSET, APCFILT1, APCFILT2     | 0.5V to +3.0V                     |

| Voltage at BIAS                | +1.0V to $(V_{CC} + 1.5V)$        |

| Voltage at OUT+, OUT           | +1.5V to (V <sub>CC</sub> + 1.5V) |

| Current into FAIL              | -10mA to +10mA                    |

| Continuous Power Dissipation ( $T_A = +85$ | °C)            |

|--------------------------------------------|----------------|

| 24-Pin QFN (derate 274mW/°C above          | +85°C)1781mW   |

| Storage Temperature Range                  | 55°C to +150°C |

| Operating Junction Temperature             | 55°C to +150°C |

| Die Attach Temperature (die)               |                |

| Lead Temperature (soldering, 10s)          | +300°C         |

|                                            |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.14V \text{ to } +3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ . Typical values are at  $V_{CC} = +3.3V, I_{BIAS} = 60\text{mA}$ ,  $I_{MOD} = 30\text{mA}$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                               | SYMBOL          | CONDITIONS                                  |                           | MIN                    | TYP                    | MAX                                     | UNITS            |

|-----------------------------------------|-----------------|---------------------------------------------|---------------------------|------------------------|------------------------|-----------------------------------------|------------------|

| Supply Current                          | Icc             | Excluding IBIAS and IMOD                    |                           |                        | 30                     | 45                                      | mA               |

| Bias-Current Range                      | IBIAS           | Voltage on BIAS pin (VBIAS                  | 1                         |                        | 100                    | mA                                      |                  |

| Bias Off-Current                        |                 | $\overline{EN}$ = high (Note 2), $V_{BIAS}$ |                           |                        | 0.2                    | mA                                      |                  |

| Rica Current Stability                  |                 | ADC open loop (Note 2)                      | I <sub>BIAS</sub> = 100mA |                        | 61                     |                                         | 20m/0C           |

| Bias-Current Stability                  |                 | APC open loop (Note 3)                      | I <sub>BIAS</sub> = 1mA   |                        | 198                    |                                         | ppm/°C           |

| Bias-Current Absolute Accuracy          |                 | APC open loop (Note 4)                      |                           | -15                    |                        | +15                                     | %                |

| Differential Input Voltage              | V <sub>ID</sub> | Figure 1                                    |                           | 0.2                    |                        | 1.6                                     | V <sub>P-P</sub> |

| Common-Mode Input Voltage               | VICM            |                                             |                           | V <sub>CC</sub> - 1.49 | V <sub>CC</sub> - 1.32 | V <sub>CC</sub> -<br>V <sub>ID</sub> /4 | V                |

| TTL Input High Voltage                  | VIH             |                                             |                           | 2.0                    |                        |                                         | V                |

| TTL Input Low Voltage                   | VIL             |                                             |                           |                        |                        | 0.8                                     | V                |

| TTL Output High                         | VoH             | Sourcing 50µA                               |                           | 2.4                    |                        |                                         | V                |

| TTL Output Low                          | V <sub>OL</sub> | Sinking 100µA                               |                           |                        |                        | 0.4                                     | V                |

| MD Voltage                              |                 |                                             |                           |                        |                        | 1.6                                     | V                |

| Monitor Diode DC-Current Range          | I <sub>MD</sub> | (Note 3)                                    |                           | 18                     |                        | 1000                                    | μΑ               |

| Monitor-Diode Bias Set Point            |                 | I <sub>MD</sub> = 1000μA                    |                           | -480                   | 83                     | +480                                    | 10.0             |

| Stability                               |                 | $I_{MD} = 18\mu A$                          |                           | -480                   | 159                    | +480                                    | ppm/°C           |

| Monitor-Diode Bias Absolute<br>Accuracy |                 |                                             |                           | -15                    |                        | +15                                     | %                |

## **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.14 \text{V to } +3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3 \text{V}, I_{BIAS} = 60 \text{mA}, I_{MOD} = 30 \text{mA}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})}$  (Notes 5, 6)

| PARAMETER                               | SYMBOL           | CONDITIONS               | MIN  | TYP | MAX  | UNITS  |

|-----------------------------------------|------------------|--------------------------|------|-----|------|--------|

| Modulation-Current Range                | I <sub>MOD</sub> | (Note 3)                 | 5    |     | 60   | mA     |

| Modulation Off-Current                  |                  | EN = high                |      |     | 0.2  | mA     |

| Modulation-Current Stability            |                  | $I_{MOD} = 60 \text{mA}$ | -480 | 64  | +480 | nnm/ºC |

| Modulation-Current Stability            |                  | $I_{MOD} = 5mA$          | -480 | 34  | +480 | ppm/°C |

| Modulation-Current Absolute<br>Accuracy |                  | (Note 4)                 | -15  |     | +15  | %      |

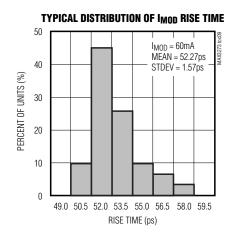

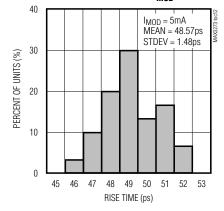

| Output Current Rise Time                | t <sub>R</sub>   | 20% to 80% (Note 7)      |      | 52  | 87   | ps     |

| Output Current Fall Time                | tF               | 20% to 80% (Note 7)      |      | 59  | 104  | ps     |

| Output Overshoot/Undershoot             | δ                | (Note 7)                 |      | 15  |      | %      |

| Enable and Startup Delay                |                  | APC open loop            |      | 364 |      | ns     |

| Maximum Consecutive Identical Digits    |                  |                          | 80   |     |      | bits   |

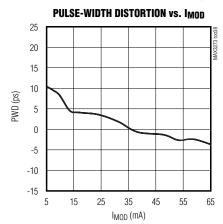

| Pulse-Width Distortion                  | PWD              | (Notes 7, 8)             |      | 3   | 45   | ps     |

| Random Jitter                           |                  |                          |      | 1.0 | 1.5  | psrms  |

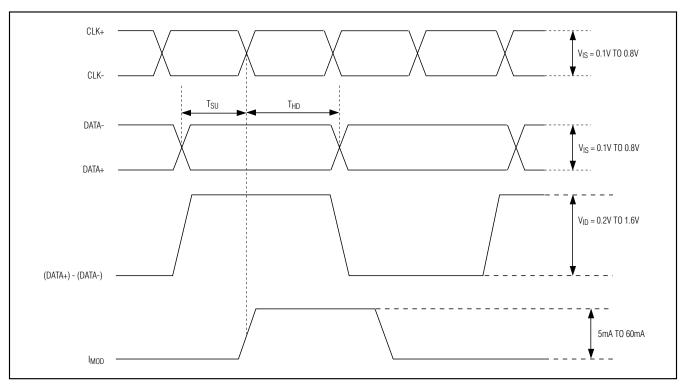

| Input Latch Setup Time                  | T <sub>SU</sub>  | LATCH = high (Figure 1)  |      | 75  | 150  | ps     |

| Input Latch Hold Time                   | T <sub>HD</sub>  | LATCH = high (Figure 1)  |      | 0   | 50   | ps     |

- Note 1: Specifications at -40°C are guaranteed by design and characterization. Dice are tested at  $T_A$ = +25°C only.

- Note 2: Both the bias and modulation currents are switched off if any of the current set pins is grounded.

- Note 3: Guaranteed by design and characterization.

- Note 4: Accuracy refers to part-to-part variation.

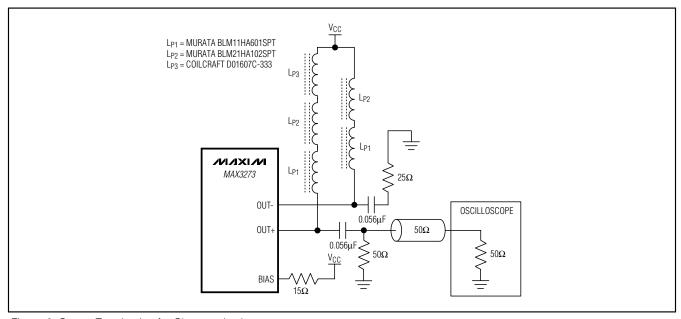

- Note 5: AC characterization was performed by using the circuit in Figure 2.

- **Note 6:** AC characteristics are guaranteed by design and characterization, and measured using a 2.5Gbps 2<sup>13</sup> 1 PRBS input data pattern with 80 consecutive zeros and 80 consecutive ones added.

- **Note 7:** Measured using a 2.5Gbps repeating 0000 1111 pattern.

- Note 8: PWD = (wide pulse narrow pulse) / 2.

Figure 1. Required Input Signal and Setup/Hold-Time Definition

Figure 2. Output Termination for Characterization

4 \_\_\_\_\_\_ *NIXI/*M

400m\<mark>/d</mark>v

# **Typical Operating Characteristics**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

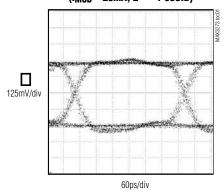

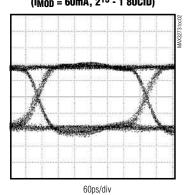

**ELECTRICAL EYE DIAGRAM**  $(I_{MOD} = 20mA, 2^{13} - 180CID)$

**ELECTRICAL EYE DIAGRAM** (I<sub>MOD</sub> = 60mA, 2<sup>13</sup> - 1 80CID)

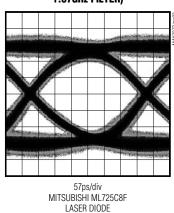

**OPTICAL EYE DIAGRAM** (2.488Gbps, 1300nm FP LASER, 1.87GHz FILTER)

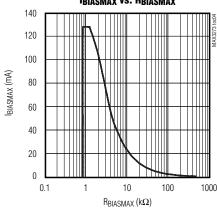

IBIASMAX VS. RBIASMAX 140

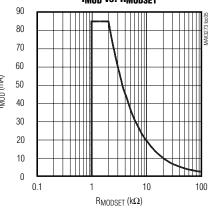

IMOD VS. RMODSET

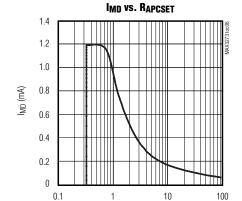

$\mathsf{R}_{\mathsf{APCSET}}\left(\mathsf{k}\Omega\right)$

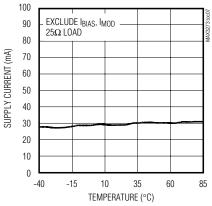

**SUPPLY CURRENT vs. TEMPERATURE**

# Typical Operating Characteristics (continued)

( $V_{CC} = 3.3V$ ,  $T_A = +25$ °C, unless otherwise noted.)

## TYPICAL DISTRIBUTION OF I<sub>MOD</sub> FALL TIME

## TYPICAL DISTRIBUTION OF I<sub>MOD</sub> FALL TIME

### TYPICAL DISTRIBUTION OF IMOD RISE TIME

# \_Pin Description

|                  | Ī              |                                                                                                                                                                                                                                 |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN              | NAME           | FUNCTION                                                                                                                                                                                                                        |

| 1, 4, 13, 15, 18 | Vcc            | Power-Supply Voltage                                                                                                                                                                                                            |

| 2                | DATA+          | Noninverting Data Input, with On-Chip Biasing                                                                                                                                                                                   |

| 3                | DATA-          | Inverting Data Input, with On-Chip Biasing                                                                                                                                                                                      |

| 5                | CLK+           | Noninverting Clock Input for Data Retiming, with On-Chip Biasing                                                                                                                                                                |

| 6                | CLK-           | Inverting Clock Input for Data Retiming, with On-Chip Biasing                                                                                                                                                                   |

| 7, 9, 12         | GND            | Ground                                                                                                                                                                                                                          |

| 8                | LATCH          | Data Retiming Enable Input, Active-High. Retiming disabled when floating or pulled low.                                                                                                                                         |

| 10               | ĒN             | TTL/CMOS Enable Input. Low for normal operation. Float or pull high to disable laser bias and modulation currents. Internal $100k\Omega$ pullup to $V_{CC}$ .                                                                   |

| 11               | MODSET         | A resistor connected from this pin to ground sets the desired modulation current.                                                                                                                                               |

| 14               | BIAS           | Laser Bias Current Output. Connect to the laser through an inductor.                                                                                                                                                            |

| 16               | OUT+           | Positive Modulation-Current Output. I <sub>MOD</sub> flows into this pin when input data is high.                                                                                                                               |

| 17               | OUT-           | Negative Modulation-Current Output. Current flows into this pin when input data is low. Connect to load equivalent to that on OUT+ to maintain differential output balance.                                                     |

| 19               | MD             | Monitor Diode Input. Connect this pin to the anode of the monitor diode. Leave floating for open-loop operation.                                                                                                                |

| 20               | APCFILT1       | A capacitor between APCFILT1 and APCFILT2 sets the dominant pole of the APC feedback loop (CAPCFILT = 0.01µF). Ground APCFILT1 for open-loop operation.                                                                         |

| 21               | APCFILT2       | See above.                                                                                                                                                                                                                      |

| 22               | FAIL           | TTL/CMOS Failure Output, Active-Low. Indicates APC failure when low.                                                                                                                                                            |

| 23               | APCSET         | A resistor connected from this pin to ground sets the desired average optical power. Connect a $100k\Omega$ resistor to GND for open-loop operation.                                                                            |

| 24               | BIASMAX        | A resistor connected from this pin to ground sets the maximum bias current. The APC function can subtract current from this maximum value, but cannot add to it. For open-loop operation, this pin sets the laser bias current. |

| EP               | EXPOSED<br>PAD | Ground. Solder this pad to ground.                                                                                                                                                                                              |

Figure 3. Functional Diagram

# **Detailed Description**

The MAX3273 laser driver consists of two main parts: a high-speed modulation driver and a laser-biasing block with automatic power control (APC). The circuit design is optimized for both high-speed and low-voltage (+3.3V) operation. To minimize the jitter of the input signal at speeds as high as 2.7Gbps, the device accepts a differential CML clock signal for data retiming. When LATCH is high, the input data is synchronized by the clock signal. When LATCH is low, the input data is directly applied to the output stage.

The output stage is composed of a high-speed differential pair and a programmable modulation current source. Because the modulation output drives a maximum current of 60mA into the laser with an edge speed of 59ps, large transient voltage spikes can be generated (due to the parasitic inductance of the laser). These transients and the laser-forward voltage leave insuffi-

cient headroom for the proper operation of the laser driver if the modulation output is DC-coupled to the laser diode. To solve this problem, the MAX3273's modulation output is AC-coupled to the cathode of a laser diode. An external pullup inductor is necessary to DC-bias the modulation output at VCC. Such a configuration isolates laser-forward voltage from the output circuitry and the supply voltage VCC. A simplified functional diagram is shown in Figure 3.

The MAX3273 modulation output is optimized for driving a  $25\,\Omega$  load. Modulation current swings of 75mA are possible, but because of minimum power-supply and jitter requirements at 2.5Gbps, the specified maximum modulation current is limited to 60mA. To interface with the laser diode, a damping resistor (RD) is required for impedance matching. An RC-shunt network might also be necessary to compensate for the laser-diode parasitic inductance, thereby improving the

optical output ringing and duty-cycle distortion. Refer to Maxim application note HFAN 02.0, *Interfacing Maxim Laser Drivers with Laser Diodes*, for more information.

At the data rate of 2.5Gbps, any capacitive load at the cathode of a laser diode degrades the optical output performance. Because the BIAS output is directly connected to the laser cathode, the parasitic capacitance associated with this pin is minimized by using an inductor to isolate the BIAS pin from the laser cathode.

### **Automatic Power Control (APC)**

To maintain constant average optical power, the MAX3273 incorporates an APC loop to compensate for the changes in laser threshold current over temperature and lifetime. A back-facet photodiode mounted in the laser package is used to convert the optical power into a photocurrent. The APC loop adjusts the laser bias current so that the monitor current is matched to a reference current set by RAPCSET. The time constant of the APC loop is determined by an external capacitor (CAPCFILT). To minimize the pattern-dependent jitter associated with the APC loop-time constant, and to guarantee loop stability, the recommended value for CAPCFILT is 0.01µF.

When the APC loop is functioning, the maximum allowable bias current is set by an external resistor, RBIASMAX. An APC failure flag (FAIL) is asserted low when the bias current can no longer be adjusted to achieve the desired average optical power.

APC closed-loop operation requires the user to set three currents with external resistors connected between ground and BIASMAX, MODSET, and APCSET (see Figure 3). Detailed guidelines for these resistor settings are described in the *Design Procedure* section.

### **Open-Loop Operation**

If necessary, the MAX3273 is fully operational without APC. To disable the APC loop, ground the APCFILT1 pin. In this case, the laser current is directly set by two external resistors connected from ground to BIASMAX and MODSET. See the *Design Procedure* section for more details on open-loop operation.

## **Optional Data Input Latch**

To minimize jitter in the input data, connect a synchronous differential clock signal to the CLK+ and CLK-inputs. When the LATCH control input is tied high, the input data is retimed on the rising edge of CLK+. If LATCH is tied low or left floating, the retiming function is disabled and the input data is directly connected to the output stage. When this latch function is not used, connect CLK+ to  $V_{\rm CC}$  and leave CLK- unconnected.

### **Output Enable**

The MAX3273 incorporates a TTL/CMOS input to enable the output. When  $\overline{\text{EN}}$  is low, the modulation and bias outputs are enabled. When  $\overline{\text{EN}}$  is high or floating, both the bias and modulation currents are off. The typical enable time is 364ns, and the typical disable time is 27ns when the bias is operated open loop.

### Slow-Start

For laser safety reasons, the MAX3273 incorporates a slow-start circuit that provides a delay of 364ns for enabling a laser diode.

### **APC Failure Monitor**

The MAX3273 provides an APC failure monitor (TTL/CMOS) to indicate an APC loop tracking failure. FAIL is asserted low when the APC loop no longer can regulate the bias current to maintain the desired monitor diode current. FAIL asserts low when the APC loop is disabled.

### **Short-Circuit Protection**

The MAX3273 provides short-circuit protection for the modulation and bias current sources. If BIASMAX, MODSET, or APCSET is shorted to ground, the bias and modulation output turns off.

# Design Procedure

When designing a laser transmitter, the optical output usually is expressed in terms of average power and extinction ratio. Table 1 gives relationships helpful in converting between the optical average power and the modulation current. These relationships are valid if the mark density and duty cycle of the optical waveform are 50%.

### **Programming the Modulation Current**

For a given laser power (Pavg), slope efficiency ( $\eta$ ), and extinction ration (re), the modulation current can be calculated using Table 1. See the IMOD vs. RMODSET graph in the *Typical Operating Characteristics* and select the value of RMODSET that corresponds to the required current at +25°C. The equation below provides a derivation of the modulation current using Table 1.

$$I_{MOD} = 2 \times \frac{P_{AVE}}{\eta} \times \frac{r_e - 1}{r_e + 1}$$

# Programming the Bias Current with APC Disabled

When using the MAX3273 in open-loop operation, the bias current is determined by the RBIASMAX resistor. To select this resistor, see the IBIASMAX vs. RBIASMAX graph in the *Typical Operating Characteristics* and select the value of RBIASMAX that corresponds to the required IBIASMAX at +25°C. Ground the APCFILT1 pin for open-loop operation.

# Programming the Bias Current with APC Enabled

When the MAX3273's APC feature is used, program the average optical power by adjusting the APCSET resistor. To select this resistor, determine the desired monitor current to be maintained over temperature and life. See the IMD vs. RAPCSET graph in the *Typical Operating Characteristics* and select the value of RAPCSET that corresponds to the required current.

When using the MAX3273 in closed-loop operation, the RBIASMAX resistor sets the maximum bias current available to the laser diode over temperature and life. The APC loop can subtract from this maximum value but cannot add to it. See the IBIASMAX vs. RBIASMAX graph in the *Typical Operating Characteristics* and select the value of RBIASMAX that corresponds to the end-of-life bias current at +85°C.

### **Interfacing with Laser Diodes**

To minimize optical output aberrations caused by signal reflections at the electrical interface to the laser diode, a series-damping resistor (RD) is required (see the *Typical Application Circuit*). Additionally, the MAX3273 outputs are optimized for a 25  $\Omega$  load. Therefore, the series combination of RD and RL (where RL represents the laser-diode resistance) should equal 25  $\Omega$ . Typical values for RD are 18  $\Omega$  to 23  $\Omega$ . For best performance, a bypass capacitor (0.01  $\mu$ F typical) should be placed as close as possible to the anode of the laser diode. Depending on the exact characteristics of the laser diode and PC board layout, a resistor (Rp) of 50  $\Omega$  to 100  $\Omega$  in parallel with pullup inductor LP1 can be useful in damping overshoot and ringing in the optical output.

In some applications (depending on laser-diode parasitic inductance), an RC-shunt network between the laser cathode and ground helps minimize optical output aberrations. Starting values for most coaxial lasers are R =  $75 \, \Omega$  in series with C = 3.3pF. These values should be experimentally adjusted until the optical output waveform is optimized.

## **Pattern-Dependent Jitter**

When transmitting NRZ data with long strings of consecutive identical digits (CIDs), LF droop can occur and contribute to pattern-dependent jitter (PDJ). To minimize this PDJ, three external components must be properly chosen: capacitor (CAPCFILT), which dominates the APC loop time constant; pullup inductor (LP); and AC-coupling capacitor (CD).

To filter out noise effects and guarantee loop stability, the recommended value for  $C_{APCFILT}$  is  $0.01\mu F$ . This results in an APC loop bandwidth of 100kHz or a time constant of  $15\mu s$ . As a result, the PDJ associated with an APC loop time constant can be ignored.

The time constant associated with the output pullup inductor (Lp  $\approx$  Lp<sub>2</sub>) and the AC-coupling capacitor (CD) affects the PDJ. For such a second-order network, the PDJ is dominated by Lp because of the low frequency cutoff. For a data rate of 2.5Gbps, the recommended value for CD is 0.056 $\mu$ F. During the maximum CID period, limit the peak voltage droop to less than 12% of the average (6% of the amplitude). The time constant can be estimated by:

$$12\% = 1 - e^{\frac{-t}{\tau_{LP}}}$$

$\tau_{LP} = 7.8t$

If  $\tau_{LP} = L_P / 25 \Omega$ , and  $t = 100 UI \approx 40 ns$ , then  $L_P = 7.8 \mu H$ . To reduce the physical size of this element (L<sub>P</sub>), use of SMD ferrite beads is recommended (Figure 2). To achieve even greater immunity to droop, use an optional third inductor (33  $\mu$ H, L<sub>P3</sub> in Figure 2).

### Input Termination Requirement

The MAX3273 data and clock inputs are CML compatible. However, it is not necessary to drive the IC with a standard CML signal. As long as the specified differential voltage swings are met, the MAX3273 operates properly.

### **Calculating Power Consumption**

The junction temperature of the MAX3273 dice must be kept below +150°C at all times. The total power dissipation of the MAX3273 can be estimated by the following:

$$P = V_{CC} \times I_{CC} + (V_{CC} - V_f) \times I_{BIAS} + I_{MOD} \times (V_{CC} - 25 \times I_{MOD} / 2)$$

where  $I_{\text{BIAS}}$  is the maximum bias current set by  $R_{\text{BIASMAX}}$ ,  $I_{\text{MOD}}$  is the modulation current, and  $V_{\text{f}}$  is the typical laser forward voltage.

Junction temperature =  $P(W) \times 37$  (°C/W)

**Table 1. Optical Power Relations**

| PARAMETER                 | SYMBOL           | RELATION                                              |

|---------------------------|------------------|-------------------------------------------------------|

| Average Power             | Pavg             | $P_{AVG} = (P_0 + P_1) / 2$                           |

| Extinction Ratio          | r <sub>e</sub>   | $r_e = P_1 / P_0$                                     |

| Optical Power of a 1      | P <sub>1</sub>   | $P_1 = 2P_{AVGre} / (r_e + 1)$                        |

| Optical Power of a 0      | P <sub>0</sub>   | $P_0 = 2P_{AVG} / (r_e + 1)$                          |

| Optical Amplitude         | P <sub>P-P</sub> | $P_{P-P} = P_1 - P_0 = 2P_{AVG}(r_e - 1) / (r_e + 1)$ |

| Laser Slope Efficiency    | η                | η = Pp-p / IMOD                                       |

| Modulation Current        | I <sub>MOD</sub> | I <sub>MOD</sub> = P <sub>P-P</sub> / η               |

| Threshold Current         | l <sub>TH</sub>  | P <sub>0</sub> at 1 ≥ I <sub>TH</sub>                 |

| Bias Current              | IBIAS            | IBIAS ≥ ITH + IMOD / 2                                |

| Laser-to-Monitor Transfer | PMON             | I <sub>MD</sub> / P <sub>AVG</sub>                    |

Note: Assuming a 50% average input duty cycle and mark density.

# Applications Information

An example of how to set up the MAX3273 follows.

#### Select Laser

A communication-grade laser should be selected for 2.5Gbps/2.7Gbps applications. Assume the laser output average power is  $P_{AVG} = 0$ , the minimum extinction ratio is  $r_e = 6.6$  (8.2dB), the operating temperature is -40°C to +85°C, and the laser diode has the following characteristics:

- Wavelength: λ= 1310nm

- Threshold Current: ITH = 22mA at +25°C

- Threshold Temperature Coefficient: β<sub>TH</sub> = 1.3%/°C

- Laser-to-Monitor Transfer: ρ<sub>MON</sub> = 0.2A/W

- Laser Slope Efficiency: η = 0.05mW/mA at +25°C

## **Determine RAPCSET**

The desired monitor diode current is estimated by I<sub>MD</sub> = Pavg  $\times$  pmon = 200µA. The I<sub>MD</sub> vs. Rapcset graph in the *Typical Operating Characteristics* shows that Rapcset should be 7.5k $\alpha$ .

### **Determine RMODSET**

To achieve a minimum extinction ratio ( $r_e$ ) of 6.6 over temperature and lifetime, calculate the required extinction ratio at +25°C. Assuming  $r_e$  = 20, the peak-to-peak optical power PP-P = 1.81mW, according to Table 1. The required modulation current is 1.81mW/ (0.05mW/mA) = 36.2mA. The IMOD vs. RMODSET graph in the *Typical Operating Characteristics* shows that RMODSET should be  $5k\Omega$ .

## **Determine RBIASMAX**

Calculate the maximum threshold current (ITH(MAX)) at TA =  $+85^{\circ}$ C and end of life. Assuming ITH(MAX) = 50mA, the maximum bias current should be: IBIASMAX = ITH(MAX) + (IMOD / 2). In this example, IBIASMAX = 68.1mA. The IBIASMAX vs. RBIASMAX graph in the Typical Operating Characteristics shows that RBIASMAX should be  $3.5k\Omega$ .

#### Interface Models

Figures 4 and 5 show simplified input and output circuits for the MAX3273 laser driver. If dice are used, replace package parasitic elements with bondwire parasitic elements.

## **Wire-Bonding Die**

For high-current density and reliable operation, the MAX3273 uses gold metalization. Make connections to the die with gold wire only, using ball-bonding techniques. Wedge bonding is not recommended. Die-pad size is 4 mils ( $100\mu m$ ) square, and die thickness is 14 mils ( $350\mu m$ ).

### **Layout Considerations**

To minimize inductance, keep the connections between the MAX3273 output pins and laser diode as close as possible. Optimize the laser-diode performance by placing a bypass capacitor as close as possible to the laser anode. Use good high-frequency layout techniques and multilayer boards with uninterrupted ground planes to minimize EMI and crosstalk.

## Laser Safety and IEC 825

Using the MAX3273 laser driver alone does not ensure that a transmitter design is compliant with IEC 825. The entire transmitter circuit and component selections must be considered. Customers must determine the level of fault tolerance required by their application, recognizing that Maxim products are not designed or authorized for use as components in systems intended for surgical implant into the body, for applications intended to support or sustain life, or for any other application where the failure of a Maxim product could create a situation where personal injury or death may occur.

## **Chip Information**

**TRANSISTOR COUNT: 1672**

PROCESS: SiGe

**ISOLATED SUBSTRATE**

Figure 4. Simplified Input Circuit

Figure 5. Simplified Output Circuit

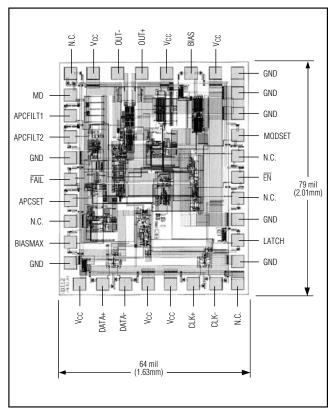

# **Pin Configurations**

# Chip Topography

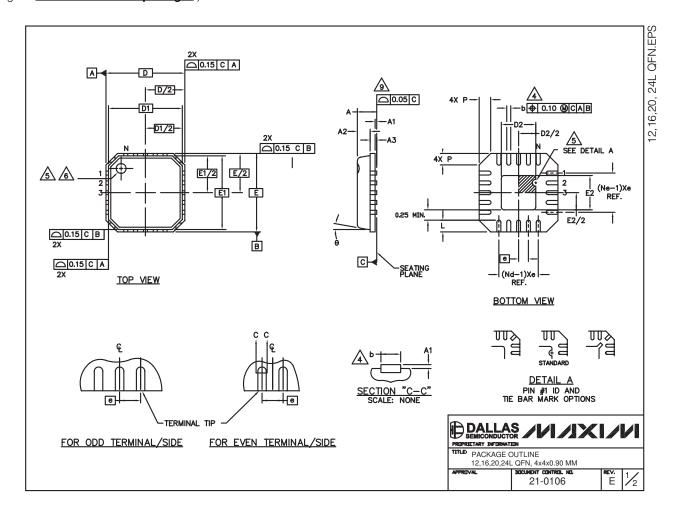

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

## **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### **NOTES:**

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM).

- 2. DIMENSIONING & TOLERANCES CONFORM MUST TO ASME Y14.5M. 1994.

- 3. N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

No IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/LASER MARKED. DETAILS OF PIN #1 IDENTIFIER IS OPTIONAL, BUT MUST BE LOCATED WITHIN ZONE INDICATED.

- 6 EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.05mm.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDING PART OF EXPOSED PAD FROM MEASURING.

- 10. MEETS JEDEC MO220; EXCEPT DIMENSION "b".

- 11. THIS PACKAGE OUTLINE APPLIES TO PUNCHED QFN (STEPPED SIDES).

| ľγ                       |      | COMMON    | ı    |                |  |  |  |  |  |  |

|--------------------------|------|-----------|------|----------------|--|--|--|--|--|--|

| o.<br>A                  |      | MENSION   |      | N <sub>O</sub> |  |  |  |  |  |  |

| ૄ                        | MIN. | NOM.      | MAX. | Tε             |  |  |  |  |  |  |

| Α                        | 0.80 | 0.90      | 1.00 |                |  |  |  |  |  |  |

| A1                       | 0.00 | 0.01      | 0.05 |                |  |  |  |  |  |  |

| A2                       | 0.00 | 0.65      | 0.80 |                |  |  |  |  |  |  |

| A3                       |      | 0.20 REF. |      |                |  |  |  |  |  |  |

| A2<br>A3<br>D<br>D1<br>E |      | 4.00 BSC  |      |                |  |  |  |  |  |  |

| D1                       |      | 3.75 BSC  |      |                |  |  |  |  |  |  |

| E                        |      | 4.00 BSC  |      |                |  |  |  |  |  |  |

| E1                       |      | 3.75 BSC  |      |                |  |  |  |  |  |  |

| Θ                        | 0.   | _         | 12°  |                |  |  |  |  |  |  |

| θ<br>P                   | 0.24 | 0.42      | 0.60 |                |  |  |  |  |  |  |

| S W B O | PITCH<br>MIN. | VARIAT   | ION A      | No <sub>TE</sub> | Sy Min O | PITCH<br>MIN. | VARIAT   | ION B | No <sub>TE</sub> | S Na O | PITCH<br>MIN. | VARIAT   | ION C | No <sub>TE</sub> | SYMBO | PITCH<br>MIN. | VARIAT   | ION D | No <sub>TE</sub> |

|---------|---------------|----------|------------|------------------|----------|---------------|----------|-------|------------------|--------|---------------|----------|-------|------------------|-------|---------------|----------|-------|------------------|

| e       |               | 0.80 BSC | 1017 17 13 |                  | e        |               | 0.65 BSC |       |                  | e      |               | 0.50 BSC |       |                  | 画     |               | 0.50 BSC |       | H                |

| N       |               | 12       |            | 3                | N        |               | 16       |       | 3                | N      |               | 20       |       | 3                | N     |               | 24       |       | 3                |

| Nd      |               | 3        |            | 3                | Nd       |               | 4        |       | 3                | Nd     |               | 5        |       | 3                | Nd    |               | 6        |       | 3                |

| Ne      |               | 3        |            | 3                | Ne       |               | 4        |       | 3                | Ne     |               | 5        |       | 3                | Ne    |               | 6        |       | 3                |

| П       | 0.50          | 0.60     | 0.75       |                  | П        | 0.50          | 0.60     | 0.75  |                  | L      | 0.50          | 0.60     | 0.75  |                  | L     | 0.30          | 0.40     | 0.50  |                  |

| ь       | 0.28          | 0.33     | 0.40       | 4                | ы        | 0.23          | 0.28     | 0.35  | 4                | ь      | 0.18          | 0.23     | 0.30  | 4                | b     | 0.18          | 0.23     | 0.30  | 4                |

|         |      | EXPOSED PAD VARIATION |      |      |      |      |  |  |  |  |  |  |  |

|---------|------|-----------------------|------|------|------|------|--|--|--|--|--|--|--|

| PKG.    |      | D2                    |      | 1 E2 |      |      |  |  |  |  |  |  |  |

| CODE    | MIN. | I NOM.                | MAX. | MIN. | NOM. | MAX. |  |  |  |  |  |  |  |

| G1244-2 | 1.95 | 2.10                  | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |  |

| G1644-1 | 1.95 | 2.10                  | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |  |

| G2044-3 | 1.95 | 2.10                  | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |  |

| G2044-4 | 1.55 | 1.70                  | 1.85 | 1.55 | 1.70 | 1.85 |  |  |  |  |  |  |  |

| G2444-1 | 1.95 | 2.10                  | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |  |

|         | ALLA<br>MICONDUCTO<br>TARY INFERNATION | S / VI / IX                   |      |     |

|---------|----------------------------------------|-------------------------------|------|-----|

|         | PACKAGE (<br>12,16,20,24L              | OUTLINE<br>L QFN, 4x4x0.90 MM |      |     |

| APPROVA | NL.                                    | 21-0106                       | REV. | 2/2 |

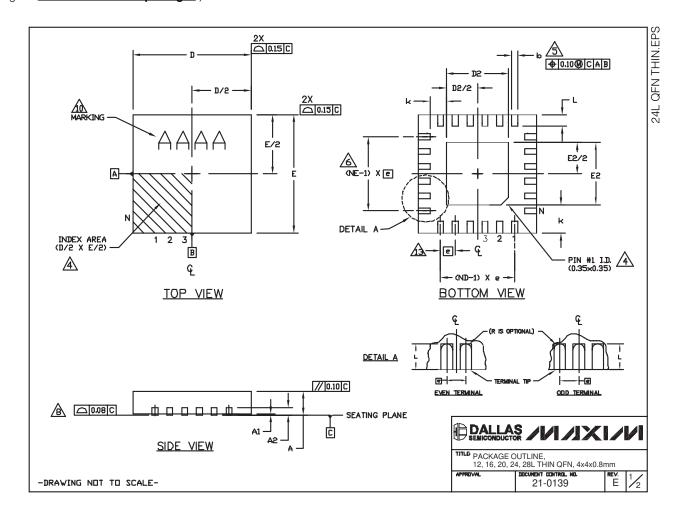

## **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

|                  | COMMON DIMENSIONS |         |      |         |           |      |        |           |        |           |         |      |           |         |      |  |

|------------------|-------------------|---------|------|---------|-----------|------|--------|-----------|--------|-----------|---------|------|-----------|---------|------|--|

| PKG              | 12                | 2L 4×   | :4   | 16L 4x4 |           |      | 20     | 20L 4×4   |        |           | 24L 4×4 |      |           | 28L 4×4 |      |  |

| REF.             | MIN.              | NDM.    | MAX. | MIN.    | NDM.      | MAX. | MIN.   | NDM.      | MAX.   | MIN.      | NDM.    | MAX. | MIN.      | NDM.    | MAX. |  |

| Α                | 0.70              | 0.75    | 0.80 | 0.70    | 0.75      | 0.80 | 0.70   | 0.75      | 0.80   | 0.70      | 0.75    | 0.80 | 0.70      | 0.75    | 0.80 |  |

| A1               | 0.0               | 0.02    | 0.05 | 0.0     | 0.02      | 0.05 | 0,0    | 0.02      | 0.05   | 0,0       | 0.02    | 0.05 | 0,0       | 0.02    | 0.05 |  |

| A2               | -                 | .20 RE  | F    | 0       | .20 RE    | F    | 0      | .20 RE    | F      | 0         | .20 RE  | F    | 0.20 REF  |         |      |  |

| b                | 0.25              | 0.30    | 0.35 | 0.25    | 0.30      | 0.35 | 0.20   | 0.25      | 0.30   | 0.18      | 0.23    | 0.30 | 0.15      | 0.20    | 0.25 |  |

| D                | 3,90              | 4.00    | 4.10 | 3.90    | 4.00      | 4.10 | 3.90   | 4.00      | 4.10   | 3.90      | 4.00    | 4.10 | 3.90      | 4.00    | 4.10 |  |

| Ε                | 3.90              | 4.00    | 4.10 | 3.90    | 4.00      | 4.10 | 3.90   | 4.00      | 4.10   | 3.90      | 4.00    | 4.10 | 3.90      | 4.00    | 4.10 |  |

| e                | -                 | 0.80 BS | C.   | 0.      | 0.65 BSC. |      | 0      | 0.50 BSC. |        | 0.50 BSC. |         |      | 0.40 BSC. |         |      |  |

| k                | 0.25              | -       | -    | 0.25    | -         |      | 0.25   | -         | -      | 0.25      | -       | -    | 0.25      | -       | -    |  |

| L                | 0.45              | 0.55    | 0.65 | 0.45    | 0.55      | 0.65 | 0.45   | 0.55      | 0.65   | 0.30      | 0.40    | 0.50 | 0.30      | 0.40    | 0.50 |  |

| N                |                   | 12      |      |         | 16        |      |        | 20        |        |           | 24      |      |           | 28      |      |  |

| N <sub>2</sub> D |                   | 3       |      |         | 4         |      |        | 5         |        |           | 6       |      |           | 7       |      |  |

| NE               |                   | 3       |      | 4       |           |      | 5      |           | 6      |           |         | 7    |           |         |      |  |

| Jedec            | VGG38             |         |      |         | WGGC      |      | WGGD-1 |           | WGGD-2 |           |         | WGGE |           |         |      |  |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |         |  |

|------------------------|------|------|------|------|------|------|---------|--|

| PKG.<br>CODES          | 1)2  |      |      | E2   |      |      | DOWN    |  |

|                        | MIN. | NDM. | MAX. | MIN. | NOM. | MAX. | ALLOVED |  |

| T1244-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES     |  |

| T1244-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO      |  |

| T1644-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES     |  |

| T1644-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO      |  |

| T2044-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES     |  |

| T2044-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO      |  |

| T2444-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES     |  |

| T2444-3                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | YES     |  |

| T2444-4                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | NO      |  |

| T2844-1                | 2.50 | 2.60 | 2.70 | 2.50 | 2.60 | 2.70 | NO      |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN

THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- bimension & applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from terminal tip.

- 6 ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm

- 12. WARPAGE SHALL NOT EXCEEND 0.10mm

- LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY

DALLAS / VI / IX I / VI

PACKAGE OUTLINE, 12, 16, 20, 24, 28L THIN QFN, 4x4x0.8mm

-DRAWING NOT TO SCALE-

| Rev 0;       | 8/01:  | Initial data sheet release.                                                              |

|--------------|--------|------------------------------------------------------------------------------------------|

| Rev 1;       | 12/02: | Removed CP pin from Pin Description (page 7).                                            |

|              |        | Removed CP and GND pins from Pin Configuration (page 13).                                |

|              |        | Updated package drawing with new revision (pages 14 and 15).                             |

| Rev 2; 5/03: |        | Updated Ordering Information and added package code (page 1).                            |

|              |        | Updated package drawing with new revision (page 14).                                     |

| Rev 3;       | 2/07:  | Added thin QFN package to Ordering Information (page 1).                                 |

|              |        | Updated Figure 3 (added connector dot to Failure Detector) (page 8).                     |

|              |        | Added missing connector dots to Figure 5 and added thin QFN pin configuration (page 13). |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

**Revision History**