Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Gas Flow Meter SoC**

## **General Description**

The MAX35104 is a gas flow meter system-on-chip (SoC) targeted as an analog front-end solution for the ultrasonic gas meter and medical ventilator markets. With a time measurement accuracy of 700ps and automatic differential time of flight (TOF), the device makes for simplified computation of gaseous flow.

Power consumption is the lowest available with ultra-low 62µA time-of-flight measurement and 125nA duty-cycled temperature measurement. Multi-hit (up to six per wave) capability with stop-enable windowing allows the device to be fine-tuned for the application. Internal analog switches, a configurable three-stage integrated operational amplifier chain amplifier, and an ultra-low input offset comparator provide the analog interface and control for a minimal electrical bill of material solution. A programmable highvoltage (up to 30V) pulse launcher provides up to 19dB of transducer launch amplitude adjustment to compensate for transducer aging and temperature, pressure, humidity affects. Early edge detection ensures measurements are made with consistent wave patterns to greatly improve accuracy and eliminate erroneous measurements. Built-in arithmetic logic unit provides TOF difference measurements and programmable receiver hit accumulators to minimize the host microprocessor access. For temperature measurement, the device supports a single 2-wire PT1000 platinum resistive temperature detector (RTD) or NTC thermistor. A simple 4-wire SPI interface allows any microcontroller to effectively configure the device for its intended measurement.

## **Applications**

- Ultrasonic Gas Meters

- Medical Ventilators

### **Benefits and Features**

- High Accuracy Flow Measurement for Billing and Leak Detection

- Time-to-Digital Accuracy Down to 700ps Measurement Range Up to 400µs

- 2 Channels: Single-Stop Channel

- High Accuracy Temperature Measurement for Precise Flow Calculations

- One 2-Wire Sensor: PT1000, PT500 RTD, and Thermistor Support

- Maximizes Battery Life with Low Device and Overall System Power

- Ultra-Low 62µA TOF Measurement and 125nA Duty-Cycled Temperature Measurement

- Event Timing Mode with Randomizer Reduces Host μC Overhead to Minimize System Power Consumption

- 2.3V to 3.6V Single-Supply Operation

- High Integration Solution Minimizes Parts Count and Reduces BOM Cost

- · Built-In Real-Time Clock

- Small, 5mm x 5mm, 40-Pin TQFN Package

- -40°C to +85°C Operation

<u>Ordering Information</u> appears at end of data sheet.

# **TABLE OF CONTENTS**

| General Description                          |   |

|----------------------------------------------|---|

| Benefits and Features                        |   |

| Absolute Maximum Ratings                     | 6 |

| Package Thermal Characteristics              | 6 |

| Recommended Operating Conditions             | 6 |

| Electrical Characteristics                   | 6 |

| Recommended External Crystal Characteristics |   |

| Timing Diagrams                              |   |

| Pin Configuration                            |   |

| Pin Description                              |   |

| Block Diagram                                |   |

| Detailed Description                         |   |

| Time-of-Flight (TOF) Measurement Operations  |   |

| Pulse Echo TOF Mode                          |   |

| Early Edge Detect                            |   |

| TOF Error Handling                           |   |

| Step-Up DC-DC Controller                     |   |

| Control and Operation                        |   |

| Compensation Component Values                |   |

| RSENSE                                       |   |

| Kelvin Sense                                 |   |

| Power Transistor                             |   |

| Inductor (L)                                 |   |

| Diode                                        |   |

| Output Filter Capacitor                      |   |

| Piezo Driver Regulator                       |   |

| Output Capacitor Selection                   |   |

| Transducer Driver                            |   |

| Analog Front-End                             |   |

| Temperature Measurement Operations           |   |

| Temperature Error Handling                   |   |

| Event Timing Operation                       |   |

| Continuous Event Timing Operation            |   |

| Continuous Interrupt Timing Operation        |   |

| TOF Sample Randomizer                        |   |

| Event Timing Mode 2                          |   |

| Event Timing Mode 3                          |   |

| Event Timing Mode 1                          |   |

| TABLE OF CONTENTS (continued)              |    |

|--------------------------------------------|----|

| Calibration Operation                      | 30 |

| Error Handling during Calibration          | 32 |

| RTC, Alarm, Watchdog, and Tamper Operation | 32 |

| RTC Operation                              | 32 |

| Alarm Operation                            | 32 |

| Watchdog Operation                         | 34 |

| Tamper Detect Operation                    | 34 |

| Device Interrupt Operations                | 34 |

| Interrupt Status Register                  | 34 |

| ĪNT Pin                                    | 34 |

| Serial Peripheral Interface Operation      | 34 |

| Opcode Commands                            | 34 |

| Execution Opcode Commands                  | 35 |

| TOF_UP Command (00h)                       | 35 |

| TOF_Down Command (01h)                     | 35 |

| TOF_DIFF Command (02h)                     | 35 |

| Temperature Command (03h)                  | 36 |

| Reset Command (04h)                        | 36 |

| Initialize Command (05h)                   | 36 |

| Bandpass Calibrate Command (06h)           | 36 |

| EVTMG1 Command (07h)                       | 36 |

| EVTMG2 Command (08h)                       | 36 |

| EVTMG3 Command (09h)                       | 36 |

| HALT Command (0Ah)                         | 36 |

| Calibrate Command (0Eh)                    | 36 |

| Register Opcode Commands                   | 37 |

| Read Register Command                      |    |

| Write Register Command                     | 37 |

| Register Memory Map                        | 39 |

| RTC and Watchdog Register Descriptions     | 45 |

| Configuration Register Descriptions        | 48 |

| Conversion Results Register Descriptions   | 73 |

| Ordering Information                       | 79 |

| Chip Information                           |    |

| Package Information                        | 79 |

| Revision History                           | 80 |

| LIST OF FIGURES                                              |    |

|--------------------------------------------------------------|----|

| Figure 1. SPI Timing Diagram Read                            |    |

| Figure 2. SPI Timing Diagram Write                           |    |

| Figure 3. Time-of-Flight Up Measurement Sequence             |    |

| Figure 4. Start/Stop for Time-to-Digital Timing              |    |

| Figure 5A. Pulse Echo Measurement Mode                       |    |

| Figure 5B. Early Edge Detect Received Wave Example           | 20 |

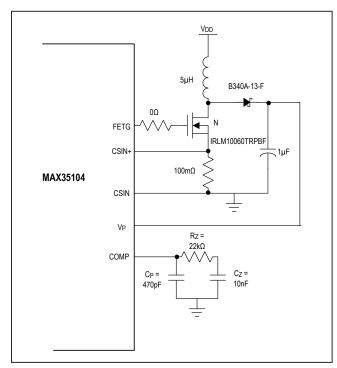

| Figure 6. Boost Circuits Components                          | 21 |

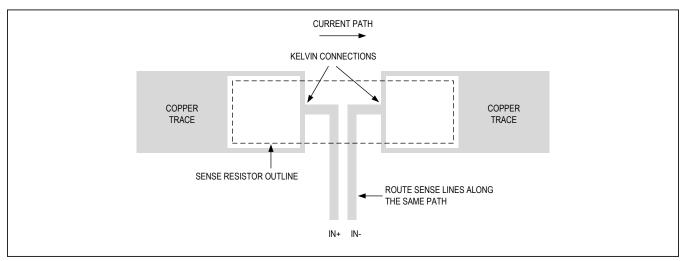

| Figure 7. Kelvin Sense Connection Layout Example             |    |

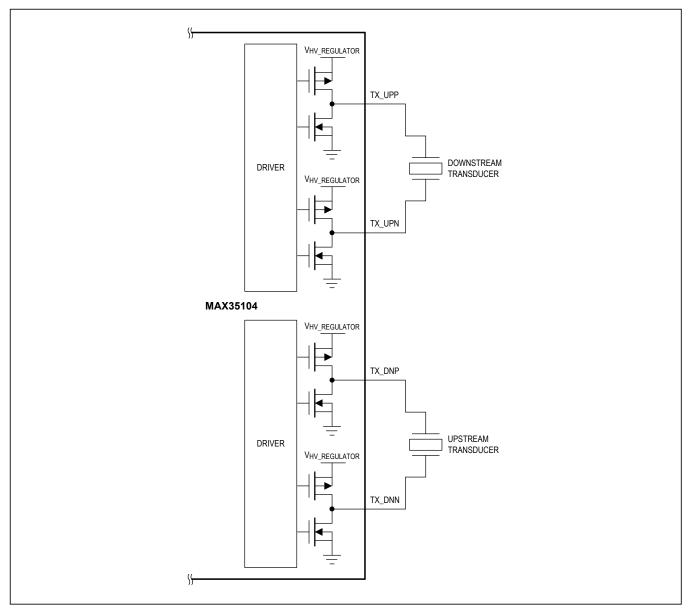

| Figure 8. Piezo Driver Connection                            | 24 |

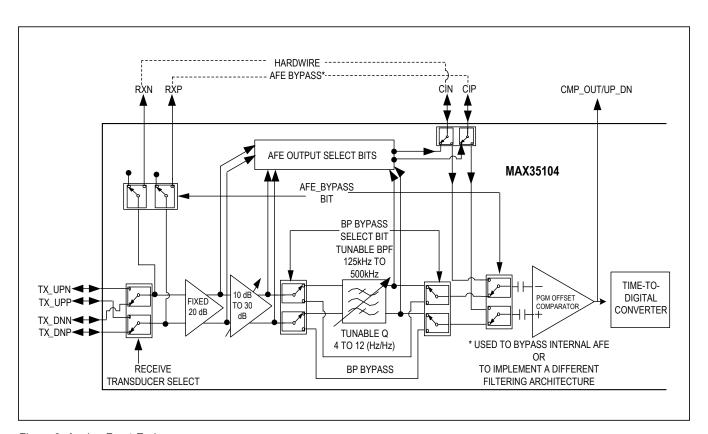

| Figure 9. Analog Front-End                                   |    |

| Figure 10. Temperature Command Execution Cycle Example       |    |

| Figure 11. EVTMG2 Command                                    | 29 |

| Figure 12. EVTMG2 Pseudo Code                                | 29 |

| Figure 13. EVTMG3 Command                                    |    |

| Figure 14. EVTMG3 Pseudo Code                                |    |

| Figure 15. EVTMG1 Pseudo Code                                |    |

| Figure 16. EVTMG1 Command                                    |    |

| Figure 17. Execution Opcode Command Protocol                 |    |

| Figure 18. Read Register Opcode Command Protocol             |    |

| Figure 19. Continuous Read Register Opcode Command Protocol  |    |

| Figure 20. Write Register Opcode Command Protocol            |    |

| Figure 21. Continuous Write Register Opcode Command Protocol |    |

| LIST OF TABLES                                               |    |

| Table 1. Two's Complement TOF_DIFF Conversion Example        | 18 |

| Table 2. RSENSE Example Values                               |    |

| Table 3. Example Gain Settings                               |    |

| Table 4. Randomizer Sampling                                 |    |

| Table 5. Opcode Commands                                     |    |

| Table 6. Register Memory Map                                 | 40 |

| Table 7. RTC Seconds Register                                |    |

| Table 8. RTC Mins_Hrs Register                               |    |

| Table 9. RTC Day_Date Register                               | 46 |

| Table 10. RTC Month Year Register                            |    |

| LIST OF TABLES (continued)                         |    |

|----------------------------------------------------|----|

| Table 11. Watchdog Alarm Counter Register          | 47 |

| Table 12. Alarm Register                           | 47 |

| Table 13. Switcher 1 Register                      | 48 |

| Table 14. Switcher 2 Register                      | 50 |

| Table 15. AFE 1 Register                           | 52 |

| Table 16. AFE 2 Register                           | 53 |

| Table 17. TOF1 Register                            | 54 |

| Table 18. TOF2 Register                            | 56 |

| Table 19. TOF3 Register                            | 58 |

| Table 20. TOF4 Register                            | 59 |

| Table 21. TOF5 Register                            | 60 |

| Table 22. TOF6 Register                            | 61 |

| Table 23. TOF7 Register                            | 63 |

| Table 24. Event Timing 1 Register                  | 65 |

| Table 25. Event Timing 2 Register                  | 66 |

| Table 26. TOF Measurement Delay Register           | 67 |

| Table 27. Calibration and Control Register         | 68 |

| Table 28. Real-Time Clock Register                 | 70 |

| Table 29. Interrupt Status Register                | 71 |

| Table 30. Control Register                         | 72 |

| Table 31. Conversion Results Registers Description | 73 |

## **Absolute Maximum Ratings**

| (Voltage relative to ground.)                             | Operating Temperature Range40°C to +85°C        |

|-----------------------------------------------------------|-------------------------------------------------|

| Voltage Range on V <sub>CC</sub> Pins0.5V to +4.0V        | Junction Temperature+150°C                      |

| Voltage Range on All Other                                | Storage Temperature Range55°C to +125°C         |

| Pins (not to exceed 4.0V)0.5V to (V <sub>CC</sub> + 0.3V) | Soldering Temperature (reflow)+260°C            |

| Voltage Range on High Voltage Pins32V                     | Lead Temperature (soldering, 10s)+300°C         |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)     | ESD Protection (All Pins, Human Body Model)±2kV |

| TQFN (derate 35.70mW/°C above +70°C)2857.10mW             |                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

**TQFN**

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .......28°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>).......2°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Recommended Operating Conditions**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Notes 2, 3)}$

| PARAMETER                              | SYMBOL               | CONDITIONS | MIN                    | TYP | MAX                    | UNITS |

|----------------------------------------|----------------------|------------|------------------------|-----|------------------------|-------|

| Supply Voltage                         | V <sub>CC</sub>      |            | 2.3                    | 3.3 | 3.6                    | ٧     |

| Input Logic 1 (RST, CSW, SCK, DIN, CE) | V <sub>IH</sub>      |            | V <sub>CC</sub> x 0.7  |     | V <sub>CC</sub> + 0.3  | ٧     |

| Input Logic 0 (RST, CSW, SCK, DIN, CE) | V <sub>IL</sub>      |            | -0.3                   |     | V <sub>CC</sub> x 0.3  | V     |

| Input Logic 1 (32KX1)                  | V <sub>IH32KX1</sub> |            | V <sub>CC</sub> x 0.85 |     | V <sub>CC</sub> + 0.3  | V     |

| Input Logic 0 (32KX1)                  | V <sub>IL32KX1</sub> |            | -0.3                   |     | V <sub>CC</sub> x 0.15 | V     |

### **Electrical Characteristics**

$(V_{CC}$  = +2.3V to +3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C.) (Notes 2, 3)

| PARAMETER                                         | SYMBOL             | CONDITIONS                                      | MIN                   | TYP  | MAX                   | UNITS |

|---------------------------------------------------|--------------------|-------------------------------------------------|-----------------------|------|-----------------------|-------|

| Input Leakage (CSW, RST, SCK, DIN, CE, CIP, CIN)  | ΙL                 |                                                 | -0.1                  |      | +0.1                  | μA    |

| Output Leakage (INT, WDO, T1,T2)                  | OL                 |                                                 | -0.1                  |      | +0.1                  | μA    |

| Output Voltage Low (32KOUT)                       | V <sub>OL32K</sub> | 2mA                                             |                       |      | 0.2 x V <sub>CC</sub> | V     |

| Output Voltage High (32KOUT)                      | V <sub>OH32K</sub> | -1mA                                            | 0.8 x V <sub>CC</sub> |      |                       | V     |

| Output Voltage High (DOUT, CMP_OUT/UP_DN)         | V <sub>OH</sub>    | -4mA                                            | 0.8 x V <sub>CC</sub> |      |                       | V     |

| Output Voltage High (TC)                          | V <sub>OHTC</sub>  | V <sub>CC</sub> = 3.6V, I <sub>OUT</sub> = -4mA | 3.4                   |      |                       | V     |

| Output Voltage Low (WDO, INT, DOUT, MP_OUT/UP_DN) | V <sub>OL</sub>    | 4mA                                             |                       |      | 0.2 x V <sub>CC</sub> | V     |

| Pulldown Resistance (TC)                          | R <sub>TC</sub>    | ITC                                             | 650                   | 1000 | 1750                  | Ω     |

$(V_{CC}$  = +2.3V to +3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C.) (Notes 2, 3)

| PARAMETER                                                               | SYMBOL             | CONDITIONS                                                                      | MIN | TYP                     | MAX | UNITS |

|-------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------|-----|-------------------------|-----|-------|

| Input Voltage Low (TC)                                                  | V <sub>ILTC</sub>  |                                                                                 |     | 0.36 x V <sub>C</sub> ( | )   | V     |

| Pulldown (RXP, RXN)                                                     |                    | AFE_BP = 0, pins disabled                                                       |     | 80                      |     | μA    |

| Resistance (T1, T2)                                                     | R <sub>ON</sub>    |                                                                                 |     | 1.5                     |     | Ω     |

| Input Capacitance ( $\overline{CE}$ , SCK, DIN, $\overline{RST}$ , CSW) | C <sub>IN</sub>    | Not tested                                                                      |     | 7                       |     | pF    |

| RST Low Time                                                            | t <sub>RST</sub>   |                                                                                 |     |                         | 100 | ns    |

| CURRENT                                                                 |                    |                                                                                 |     |                         |     |       |

| Standby Current                                                         | I <sub>DDQ</sub>   | No oscillators running                                                          |     |                         | 10  | μA    |

| 32kHz OSC Current                                                       | I <sub>32KHZ</sub> | 32kHz oscillator only, V <sub>CC</sub> = 3.6V                                   |     | 0.42                    | 1   | μA    |

| 4MHz OSC Current                                                        | I <sub>4MHZ</sub>  | 4MHz oscillator only, V <sub>CC</sub> = 3.6V                                    |     | 82                      | 135 | μA    |

| Time Measurement Unit<br>Current                                        | Ісстми             | V <sub>CC</sub> = 3.3V                                                          |     | 4.3                     | 8   | mA    |

| Calculator Current                                                      | I <sub>CCCPU</sub> |                                                                                 |     | 1.2                     | 3   | mA    |

| Device Current Drain                                                    | I <sub>CC</sub>    | V <sub>CC</sub> = 3.3V, TOF_DIFF = 2 per second, temperature = 1 per 30 seconds |     | 62                      |     | μA    |

| TRANSMITTER: BOOST SWITC                                                | CHER               |                                                                                 |     |                         |     |       |

| Output Voltage Range                                                    |                    |                                                                                 |     | 9<br>30                 |     | V     |

| Programmable Output Voltage<br>Step Size                                |                    |                                                                                 |     | 1.7                     |     | V     |

| Output Switching Frequency                                              |                    |                                                                                 | 100 |                         | 200 | kHz   |

| Current-Limit Trip Level                                                | V <sub>CS-SW</sub> |                                                                                 | 100 | 150                     | 200 | mV    |

| TRANSMITTER: FET GATE DR                                                | IVER               |                                                                                 |     |                         |     |       |

| External FET Gate Charge                                                | Q <sub>G</sub>     |                                                                                 |     |                         | 2   | nC    |

| Rise Time                                                               | t <sub>R</sub>     | C <sub>L</sub> = 1nF (Figure 2, Note 3)                                         |     | 100                     |     | ns    |

| Fall Time                                                               | t <sub>F</sub>     | C <sub>L</sub> = 1nF (Figure 2, Note 3)                                         |     | 100                     |     | ns    |

| TRANSMITTER: HIGH-VOLTAG                                                | E REGULATO         | OR                                                                              |     |                         |     |       |

| Output Voltage Range                                                    |                    | Low                                                                             |     | 5.4                     |     | V     |

| Output Voltage Range                                                    |                    | High                                                                            |     | 26.4                    |     | V     |

| Programmable Output Voltage<br>Step Size                                |                    |                                                                                 |     | 1.7                     |     | V     |

| Output Voltage Accuracy                                                 |                    |                                                                                 |     | 5                       |     | %     |

| Load Regulation                                                         |                    | I <sub>LOAD</sub> = 15mA                                                        |     | 150                     |     | mV    |

$(V_{CC}$  = +2.3V to +3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C.) (Notes 2, 3)

| PARAMETER                                            | SYMBOL               | CONDITIONS                                          | MIN | TYP  | MAX | UNITS             |

|------------------------------------------------------|----------------------|-----------------------------------------------------|-----|------|-----|-------------------|

| TRANSMITTER: PIEZO DRIVE                             | R                    |                                                     | '   |      |     |                   |

| Driver Output Resistance<br>Pulling Down (n-Channel) | R <sub>ON-N-PD</sub> | V <sub>IN</sub> = 10V, I <sub>LD</sub> =10mA        |     | 50   |     | Ω                 |

| Driver Output Resistance<br>Pulling Up (p-Channel)   | R <sub>ON-P-PU</sub> | V <sub>IN</sub> = 10V, I <sub>LD</sub> =10mA        |     | 50   |     | Ω                 |

| Output Leakage Current                               | I <sub>LK-PD</sub>   |                                                     |     | 0.05 |     | μA                |

| Rise Time                                            | t <sub>R-PD</sub>    | C <sub>L</sub> = 1nF                                |     | 100  |     | ns                |

| Fall Time                                            | t <sub>F-PD</sub>    | C <sub>L</sub> = 1nF                                |     | 100  |     | ns                |

| FILTER SPECIFICATION                                 |                      |                                                     | ·   |      |     |                   |

| Input Amplitude                                      |                      |                                                     | 1   |      | 10  | mV                |

| Differential Input Impedance                         |                      |                                                     |     | 4    |     | kΩ                |

| Programmable Gain Resolution                         | Per bit              |                                                     |     | 1.5  |     | dB                |

| COMPARATOR SPECIFICATIO                              | N                    |                                                     |     |      |     |                   |

| Input Offset Voltage                                 | V <sub>OFFSET</sub>  | C_OFFSETUP or C_OFFSETDN register programmed to 00h |     | 2    |     | mV                |

| Input Offset Step Size                               | V <sub>STEP</sub>    |                                                     |     | 1    |     | mV                |

| Receiver Sensitivity                                 | V <sub>SENS</sub>    | Stop hit detect level                               | 10  |      |     | mV <sub>P-P</sub> |

| ANALOG RECEIVER: BANDPA                              | ASS FILTER           |                                                     |     |      |     |                   |

| Center Frequency Accuracy                            | f <sub>0A</sub>      | f = 200kHz                                          |     | 6    |     | %                 |

| O Dongo                                              |                      |                                                     |     | 4    |     | Hz/Hz             |

| Q Range                                              |                      |                                                     |     | 12   |     | ПZ/ПZ             |

| Q Accuracy                                           |                      |                                                     |     | 20   |     | %                 |

| 200kHz PERFORMANCE                                   |                      |                                                     | '   |      |     | •                 |

| A1 Differential Gain                                 |                      | 200kHz, V <sub>IN</sub> = 6mV <sub>P-P</sub>        |     | 10   |     | V/V               |

| UP/DN Gain Match                                     |                      |                                                     |     | ±1   |     | %                 |

$(V_{CC}$  = +2.3V to +3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C.) (Notes 2, 3)

| PA                         | RAMETER                                                                                                                                                                                                                                                                                                                            | SYMBOL | CONDIT                                  | TIONS                                   | MIN  | TYP  | MAX | UNITS |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|-----------------------------------------|------|------|-----|-------|

|                            | PGA[3:0] = 0000b                                                                                                                                                                                                                                                                                                                   |        |                                         | V <sub>IN</sub> = 19.0mV <sub>P-P</sub> |      | 3.16 |     |       |

|                            | PGA[3:0]= 0001b                                                                                                                                                                                                                                                                                                                    |        | ]                                       | $V_{IN}$ = 16.3m $V_{P-P}$              |      | 3.69 |     |       |

|                            | PGA[3:0] = 0000b PGA[3:0] = 0001b PGA[3:0] = 0010b PGA[3:0] = 0011b PGA[3:0] = 0100b PGA[3:0] = 0101b PGA[3:0] = 0110b PGA[3:0] = 1010b PGA[3:0] = 1000b PGA[3:0] = 1001b PGA[3:0] = 1011b PGA[3:0] = 1011b PGA[3:0] = 1010b PGA[3:0] = 1110b PGA[3:0] = 1110b PGA[3:0] = 1111b PGA[3:0] = 1111b PGA[3:0] = 1111b PGA[3:0] = 1111b |        | V <sub>IN</sub> = 14.0mV <sub>P-P</sub> |                                         | 4.30 |      |     |       |

|                            | PGA[3:0]= 0011b                                                                                                                                                                                                                                                                                                                    |        |                                         | V <sub>IN</sub> = 12.0mV <sub>P-P</sub> |      | 5.01 |     |       |

|                            | PGA[3:0]= 0100b                                                                                                                                                                                                                                                                                                                    |        | ]                                       | $V_{IN} = 10.3 \text{mV}_{P-P}$         |      | 5.84 |     |       |

|                            | PGA[3:0]= 0101b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 8.80 \text{mV}_{P-P}$         |      | 6.81 |     |       |

|                            | PGA[3:0]= 0110b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 7.55 \text{mV}_{P-P}$         |      | 7.94 |     | - V/V |

| DCA Coin                   | PGA[3:0]= 0111b                                                                                                                                                                                                                                                                                                                    |        | - 600m)/                                | $V_{IN} = 6.48 \text{mV}_{P-P}$         |      | 9.26 |     |       |

| PGA Gain                   | PGA[3:0]= 1000b                                                                                                                                                                                                                                                                                                                    |        |                                         | V <sub>IN</sub> = 5.56mV <sub>P-P</sub> |      | 10.8 |     |       |

|                            | PGA[3:0]= 1001b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 4.76 \text{mV}_{P-P}$         |      | 12.6 |     |       |

|                            | PGA[3:0]= 1010b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 4.09 \text{mV}_{P-P}$         |      | 14.7 |     |       |

|                            | PGA[3:0]= 1011b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 3.51 \text{mV}_{P-P}$         |      | 17.1 |     |       |

|                            | PGA[3:0]= 1100b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 3.02 \text{mV}_{P-P}$         |      | 20.0 |     |       |

|                            | PGA[3:0]= 1101b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 2.58 \text{mV}_{P-P}$         |      | 23.3 |     |       |

|                            | PGA[3:0]= 1110b                                                                                                                                                                                                                                                                                                                    |        |                                         | $V_{IN} = 2.21 \text{mV}_{P-P}$         |      | 27.1 |     |       |

|                            | PGA[3:0]= 1111b                                                                                                                                                                                                                                                                                                                    |        |                                         | V <sub>IN</sub> = 1.90mV <sub>P-P</sub> |      | 31.6 |     |       |

| Filter Gain at 200kHz Trim |                                                                                                                                                                                                                                                                                                                                    |        | V <sub>IN</sub> = 19mV <sub>P-P</sub>   |                                         |      | 1.0  |     | V/V   |

| Filter Gain with Bypass    |                                                                                                                                                                                                                                                                                                                                    |        | V <sub>IN</sub> = 19mV <sub>P-P</sub>   |                                         |      | 0.01 |     | V/V   |

$(V_{CC} = +2.3V \text{ to } +3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = 3.3V \text{ and } T_A = +25^{\circ}\text{C.}) \text{ (Notes 2, 3)}$

| PARAMETER                   | SYMBOL                          | CONDITIONS                            | MIN | TYP  | MAX  | UNITS |

|-----------------------------|---------------------------------|---------------------------------------|-----|------|------|-------|

| TIME MEASUREMENT UNIT       |                                 |                                       |     |      |      |       |

| Measurement Range           | t <sub>MEAS</sub>               | Time of flight                        | 4   |      | 8000 | μs    |

| Time Measurement Accuracy   | t <sub>ACC</sub>                | Differential time measurement         |     | 700  |      | ps    |

| Time Measurement Resolution | t <sub>RES</sub>                |                                       |     | 3.8  |      | ps    |

| EXECUTION TIMES             |                                 |                                       |     |      |      |       |

| Power-On-Reset Time         |                                 | V <sub>CC</sub> MIN to POR bit set    |     | 275  |      | μs    |

| Case Switch Time            |                                 | CSW pin logic-high until CSWI bit set |     | 20   |      | ns    |

| CAL Command Time            |                                 | Command received until CAL bit set    |     | 1.25 |      | ms    |

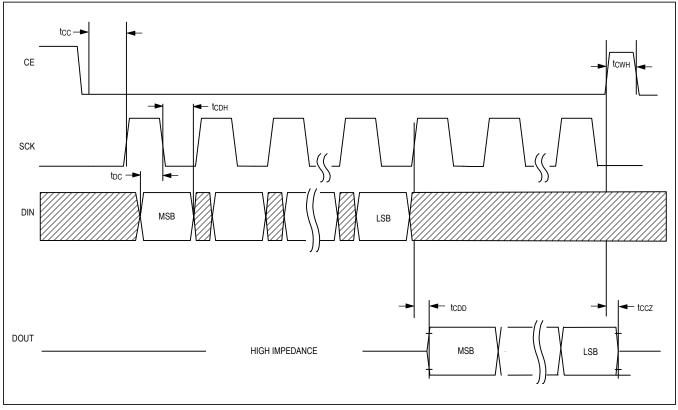

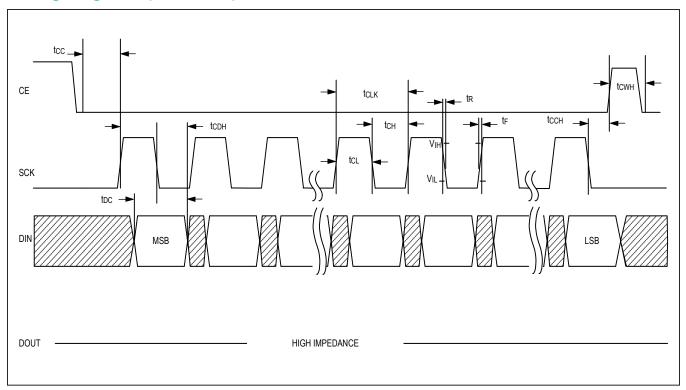

| SERIAL PERIPHERAL INTERFA   | ACE (Figure 1                   | and Figure 2)                         |     |      |      |       |

| DIN to SCK Setup            | t <sub>DC</sub>                 |                                       |     |      | 20   | ns    |

| SCK to DIN Hold             | tcdh                            |                                       |     | 2    | 20   | ns    |

| SCK to DOUT Delay           | t <sub>CDD</sub>                |                                       |     | 5    | 20   | ns    |

| SCK Low Time                |                                 | V <sub>CC</sub> ≥ 3.0V                | 25  | 4    |      | 20    |

| SCK LOW TIME                | t <sub>CL</sub>                 | V <sub>CC</sub> = 2.3V                | 50  | 30   |      | ns    |

| SCK High Time               | t <sub>CH</sub>                 |                                       | 25  | 4    |      | ns    |

| SCK Frequency               | tsck                            |                                       |     |      | 20   | MHz   |

| SCK Rise and Fall           | t <sub>R</sub> , t <sub>F</sub> |                                       |     |      | 10   | ns    |

| CE to SCK Setup             | t <sub>CC</sub>                 |                                       |     | 5    | 40   | ns    |

| SCK to CE Hold              | tcch                            |                                       |     |      | 20   | ns    |

| CE Inactive Time            | t <sub>CWH</sub>                |                                       |     | 2    | 40   | ns    |

| CE to DOUT High Impedance   | t <sub>CCZ</sub>                |                                       |     | 5    | 40   | ns    |

**Note 2:** All voltages are referenced to ground. Current entering the device are specified as positive and currents exiting the device are negative.

Note 3: Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

## **Recommended External Crystal Characteristics**

| PARAMETER                        | SYMBOL                   | CONDITIONS | MIN  | TYP    | MAX  | UNITS |

|----------------------------------|--------------------------|------------|------|--------|------|-------|

| 32kHz Nominal Frequency          | f <sub>32K</sub>         |            |      | 32.768 |      | kHz   |

| 32kHz Frequency Tolerance        | $\Delta f_{32K}/f_{32K}$ | 25°C       | -20  |        | +20  | ppm   |

| 32kHz Load Capacitance           | C <sub>L32K</sub>        |            |      | 12.5   |      | pF    |

| 32kHz Series Resistance          | R <sub>S32K</sub>        |            |      |        | 70   | kΩ    |

| 4MHz Crystal Nominal Frequency   | f <sub>4M</sub>          |            |      | 4.000  |      | MHz   |

| 4MHz Crystal Frequency Tolerance | $\Delta f_{4M}/f_{4M}$   | 25°C       | -30  |        | +30  | ppm   |

| 4MHz Crystal Loadapacitance      | $C_{L4M}$                |            |      | 12.0   |      | pF    |

| 4MHz Crystal Series Resistance   | R <sub>S4M</sub>         |            |      |        | 120  | Ω     |

| 4MHz Ceramic Nominal Frequency   |                          |            |      | 4.000  |      | MHz   |

| 4MHz Ceramic Frequency Tolerance |                          | 25°C       | -0.5 |        | +0.5 | %     |

| 4MHz Ceramic Load Capacitance    |                          |            |      | 30     |      | pF    |

## **Timing Diagrams**

Figure 1. SPI Timing Diagram Read

## **Timing Diagrams (continued)**

Figure 2. SPI Timing Diagram Write

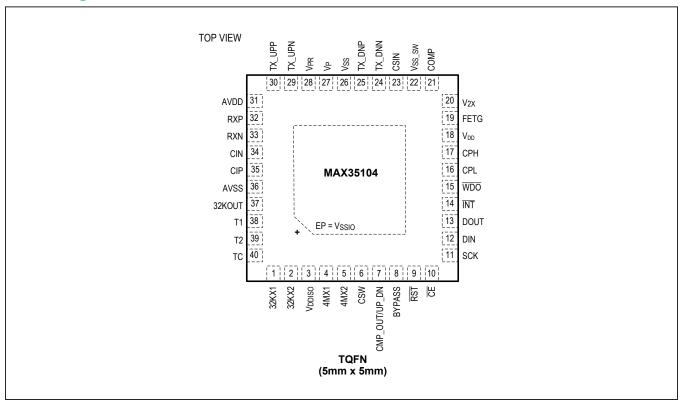

## **Pin Configuration**

## **Pin Description**

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                   |  |  |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | 32KX1              | Connections for 32.768kHz Quartz Crystal, Connect a 12pF ceramic capacitor from each pin to ground. An external CMOS 32.768kHz signal can also drive the device. In this configuration, the                                                                                                                |  |  |

| 2   | 32KX2              | 32KX1 pin is connected to the external signal and the 32KX2 pin is left unconnected.                                                                                                                                                                                                                       |  |  |

| 3   | V <sub>DDISO</sub> | LDO Supply Voltage. This pin should be decoupled to V <sub>SSISO</sub> with a 100nF ceramic capacitor (Note 1).                                                                                                                                                                                            |  |  |

| 4   | 4MX1               | Connections for 4MHz Quartz Crystal, connect a 12pF ceramic capacitor from each pin to ground. A ceramic resonator can also be used. An external CMOS 4MHz signal can also drive the device. In this configuration, the 4MX1 pin is connected to the external signal and the 4MX2 pin is left unconnected. |  |  |

| 5   | 4MX2               |                                                                                                                                                                                                                                                                                                            |  |  |

| 6   | CSW                | CMOS Digital Input Case Switch. Active high tamper detect input.                                                                                                                                                                                                                                           |  |  |

| 7   | CMP_OUT/UP_DN      | CMOS output that indicates the direction (upstream or downstream) of which the pulse launcher is currently launching pulses OR the comparator output (Note 2).                                                                                                                                             |  |  |

| 8   | BYPASS             | Connect this pin to ground with a 100nF ceramic capacitor to provide stability for the on-board low-dropout regulator. The effective series resistance of this capacitor needs to be in the range of $1\Omega$ to $2\Omega$ (Note 3).                                                                      |  |  |

# **Pin Description (continued)**

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9   | RST                | Active-Low Reset (CMOS Digital Input). Performs the same function as a power-on reset (POR).                                                                                                                                                                                                                                                                                                                        |  |  |

| 10  | CE                 | Active-Low Serial Peripheral Interface Chip Enable Input (CMOS Digital Input)                                                                                                                                                                                                                                                                                                                                       |  |  |

| 11  | SCK                | Serial Peripheral Interface Clock Input (CMOS Digital Input)                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 12  | DIN                | Serial Peripheral Interface Data Input (CMOS Digital Input)                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 13  | DOUT               | Serial Peripheral Interface Data Output (CMOS Output)                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 14  | ĪNT                | Active-Low, Open-Drain Interrupt Output. The pin is driven low when the device requires service from the host microprocessor.                                                                                                                                                                                                                                                                                       |  |  |

| 15  | WDO                | Active-Low, Open-Drain Watchdog Output. The pin is driven low when the watchdog counter reaches zero (if enabled).                                                                                                                                                                                                                                                                                                  |  |  |

| 16  | CPL                | Negative terminal of the flying capacitor for the voltage doubler. Connect this pin to CPH with a 100nF ceramic capacitor. (Note 4)                                                                                                                                                                                                                                                                                 |  |  |

| 17  | СРН                | Positive terminal of the flying capacitor for the voltage doubler. Connect this pin to CPL with a 100nF ceramic capacitor. (Note 4,5)                                                                                                                                                                                                                                                                               |  |  |

| 18  | V <sub>DD</sub>    | Supply Voltage. This pin should be decoupled to V <sub>SS</sub> with a 100nF and a 22µF ceramic capacito (Note 1).                                                                                                                                                                                                                                                                                                  |  |  |

| 19  | FETG               | PWM Modulated CMOS Gate Driver Output for External n-Channel Power Transistor used in the Boost Switcher. Place a $25\Omega$ series resistor between this pin and the transistor gate.                                                                                                                                                                                                                              |  |  |

| 20  | V <sub>2X</sub>    | Connect this pin to ground with a 100nF ceramic capacitor to provide stability for the on-board voltage doubler (Notes 3, 4).                                                                                                                                                                                                                                                                                       |  |  |

| 21  | COMP               | Error-Amplifier Output of Boost Converter. Connect the frequency-compensation network between COMP and AVSS. See Figure 6 (Notes 3, 4).                                                                                                                                                                                                                                                                             |  |  |

| 22  | V <sub>SS_SW</sub> | High-Current Ground Return for the Boost Switcher. Connect the current-sense resistor between this pin and CSIN+ (Note 4).                                                                                                                                                                                                                                                                                          |  |  |

| 23  | CSIN               | Positive Analog Input to the Current-Sense Amplifier for the Boost Switcher. Connect the current-sense resistor between this pin and CSIN (Note 4).                                                                                                                                                                                                                                                                 |  |  |

| 24  | TX_DNN             | Connect to the negative terminal of the piezo transducer located downstream of the gas flow. Performs the launching and receiving functions required for a time-of-flight measurement. In the launch case, it is the negative output of the bridged differential output driver pair. In the receive case, it is the negative input of the analog differential return signal from the piezo transducer (Notes 2, 4). |  |  |

| 25  | TX_DNP             | Connect to the positive terminal of the piezo transducer located downstream of the gas flow. Performs the launching and receiving functions required for a time-of-flight measurement. In the launch case, it is the positive output of the bridged differential output driver pair. In the receive case, it is the positive input of the analog differential return signal from the piezo transducer (Notes 2, 4). |  |  |

| 26  | V <sub>SS</sub>    | Ground Connection                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 27  | V <sub>P</sub>     | Resulting High-Voltage Bias Generated by the Boost Switcher Circuit. Used as the supply for the high-voltage regulator and to generate the feedback voltage fed into the error-amplifier for closed loop control. (Notes 3, 4).                                                                                                                                                                                     |  |  |

## **Pin Description (continued)**

| PIN | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 28  | V <sub>PR</sub>    | Connect this pin to ground with a $1\mu$ F ceramic capacitor to provide stability for the on-board high-voltage regulator. When the high-voltage regulator is not used and constantly disabled, short this pin to VP (Notes 3, 4).                                                                                                                                                                                  |  |  |  |

| 29  | TX_UPN             | Connected to the negative terminal of the piezo transducer located upstream of the gas flow. Performs the launching and receiving functions required for a time-of-flight measurement. In the launch case, it is the negative output of the bridged differential output driver pair. In the receive case, it is the negative input of the analog differential return signal from the piezo transducer (Notes 2, 4). |  |  |  |

| 30  | TX_UPP             | Connected to the positive terminal of the piezo transducer located upstream of the gas flow. Performs the launching and receiving functions required for a time-of-flight measurement. In the launch case, it is the positive output of the bridged differential output driver pair. In the receive case, it is the positive input of the analog differential return signal from the piezo transducer (Notes 2, 4). |  |  |  |

| 31  | AVDD               | Analog Supply Voltage. This pin should be decoupled to AVSS with a 100nF ceramic capacitor (Note 1).                                                                                                                                                                                                                                                                                                                |  |  |  |

| 32  | RXP                | Do Not Connect (DNC) When Utilizing the Internal Analog Front-End. Positive analog output from the selected transducer's differential return signal. When used with the CIP pin provides a way to construct an external analog front-end (Note 5).                                                                                                                                                                  |  |  |  |

| 33  | RXN                | Do Not Connect (DNC) When Utilizing the Internal Analog Front-End. Negative analog output from the selected transducer's differential return signal. When used with the CIN pin provides a way to construct an external analog front-end (Note 5).                                                                                                                                                                  |  |  |  |

| 34  | CIN                | Do Not Connect (DNC) When Utilizing the Internal Analog Front-End. Negative analog input to the differential receive comparator. When used with the RXN pin provides a way to construct an external analog front-end (Note 5). OR negative analog output of selectable AFE stages (Note 2).                                                                                                                         |  |  |  |

| 35  | CIP                | Do Not Connect (DNC) When Utilizing the Internal Analog Front-End. Positive analog input to the differential receive comparator. When used with the RXP pin provides a way to construct an external analog front-end (Note 5). OR positive analog output of selectable AFE stages (Note 2).                                                                                                                         |  |  |  |

| 36  | AVSS               | Ground Connection                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 37  | 32KOUT             | CMOS Output That Repeats the 32kHz Crystal Oscillator Frequency                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 38  | T1                 | Open-Drain Probe 1 Temperature Measurement (Note 5)                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 39  | T2                 | Open-Drain Probe 2 Temperature Measurement (Note 5)                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 40  | TC                 | Input/Output Temperature Measurement Capacitor Connection (Note 5)                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| EP  | V <sub>SSISO</sub> | Exposed Pad, Ground Connection                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

Note 1: A +2.7V to +3.6V supply. Typically sourced from a single lithium cell.

Note 2: Dual functionality pin.

Note 3: Do not connect to additional non-recommended external circuitry.

Note 4: High-voltage tolerant.

Note 5: This pin can be left open circuit if not needed.

Maxim Integrated | 15 www.maximintegrated.com

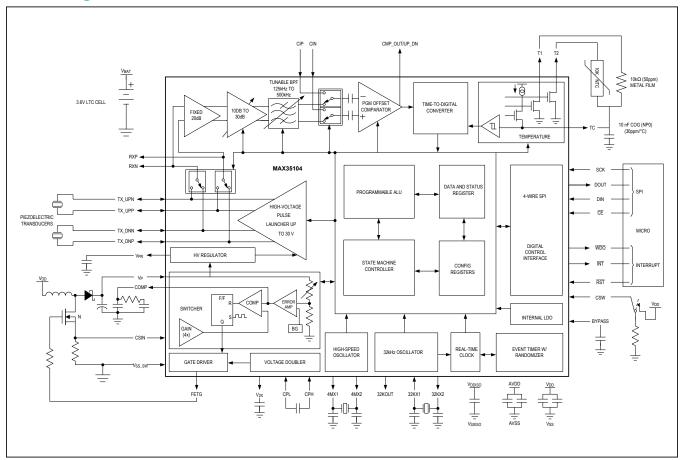

## **Block Diagram**

## **Detailed Description**

The MAX35104 is a gas flow meter SoC targeted as an analog front-end solution for the ultrasonic gas meter and medical ventilator markets. With a time measurement accuracy of 700ps and automatic differential Time-of-Flight measurement, the device makes for simplified computation of gaseous flow. Power consumption is the lowest available with ultra-low 62µA TOF measurement and 125nA duty-cycled temperature measurement.

Multihit (up to 6 per wave) capability with stop-enable windowing allows the device to be fine-tuned for the application. Internal analog switches, a configurable 3-stage integrated operational amplifier chain amplifier, and an ultra-low input offset comparator provide the analog interface and control for a minimal electrical bill of material

solution. A programmable high-voltage (up to 30V) pulse launcher provides up to 19dB of transducer launch amplitude adjustment to compensate for transducer aging and temperature, pressure, humidity affects.

Early edge detection ensures measurements are made with consistent wave patterns to greatly improve accuracy and eliminate erroneous measurements. A built-in arithmetic logic unit provides TOF difference measurements and programmable receiver hit accumulators to minimize the host microprocessor access. For temperature measurement, the device supports a single 2-wire PT1000 platinum resistive temperature detector (RTD) or NTC thermistor. A simple 4-wire SPI interface allows any microcontroller to effectively configure the device for its intended measurement.

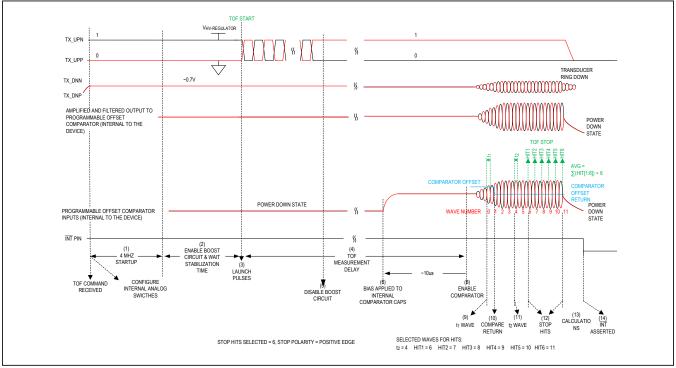

Figure 3. Time-of-Flight Up Measurement Sequence

### **Time-of-Flight (TOF) Measurement Operations**

TOF is measured by launching pulses from one piezoelectric transducer and receiving the pulses at a second transducer. The time between when the pulses are launched and received is defined as the time of flight. The device contains the functionality required to create a string of pulses, sense the receiving pulse string, and measure the time of flight. The device can measure two separate TOFs, which are defined as TOF Up and TOF Down.

A TOF Up measurement has pulses launched from the TX\_UPN and TX\_UPP pins, which is connected to the downstream transducer. The ultrasonic pulse is received at the upstream transducer, which is connected to the TX\_DNN and TX\_DNP pins. A TOF Down measurement has pulses launched from the TX\_DNN and TX\_DNP pins, which is connected to the upstream transducer. The ultrasonic pulse is received at the downstream transducer, which is connected to the TX\_UPN and TX\_UPP pins.

TOF measurements can be initiated by sending either the TOF\_UP, TOF\_DN, or TOF\_DIFF commands. TOF\_DIFF measurements can also be automatically executed using Event Timing Mode commands EVTMG1 or EVTMG2.

The steps involved in a single TOF measurement are described below and labeled in Figure 3.

- The 4MHz oscillator and LDO is enabled with a programmable settling delay time set by the CLK\_S[2:0] bits in Calibration and Control register.

- 2) The boost circuit is enabled and attempts to reach the targeted set output voltage. Once at the target voltage, the stabilization time to wait before moving to the next step is set by the ST[3:0] bits in the Switcher 2 register.

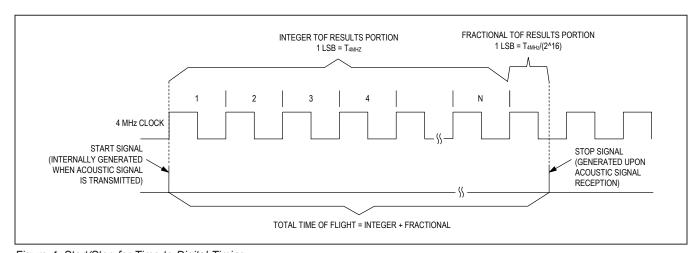

- 3) The pulse launcher drives the appropriate TX pins with a programmable sequence of pulses. The number of pulses launched is set by the PL[7:0] bits in the TOF1 register. The frequency of these 50% duty-cycle pulses is set by the DPL[3:0] bits, also in the TOF1 register. The start of these launch pulses generates a start signal for the Time-to-Digital Converter (TDC) and is considered to be time zero for the TOF measurement. This is denoted in Figure 4.

- 4) After a programmable delay time set in TOF Measurement Delay register, the comparator and hit detector at the appropriate pins are enabled. This delay allows the receiver to start recording hits when the received wave is expected, eliminating possible false hits from noise in the system.

- Once the pulse launcher has completed transmitting the sequence of pulses, the boost circuit is disabled.

- 6) A common mode bias is enabled on the internal capacitor connecting the output of the bandpass filter to the input of the programmable offset comparator. This bias charge time is fixed at approximately 10µs.

- 7) The comparator is enabled.

- 8) Stop hits are detected according to the programmed preferred edge of the acoustic signal sequence received at the appropriate pins according to the setting of the STOP\_POL bit in the TOF1 register. When a wave received at the receiving pins exceeds the Comparator Offset Voltage, which is set in the TOF6 and TOF7 registers, this wave is detected and identified as wave number 0. The width of the wave's pulse that exceeds the Comparator Offset Voltage is measured and stored as the t<sub>1</sub> time.

- The offset of the comparator then automatically and immediately switches to the Comparator Return Offset, which is set in the TOF6 and TOF7 registers.

- 10) The t<sub>2</sub> wave is detected and the width of the t<sub>2</sub> pulse is measured and stored as the t<sub>2</sub> time. The wave number for the measurement of the t<sub>2</sub> wave width is set by the T2WV[5:0] bits in the T0F2 register.

- 11) The preferred number of stop hits are then detected. For each hit, the measured TOF is stored in the appropriate HITxUPINT and HITxUPFrac or HITx-DNINT and HITxDNFRAC registers. The number of hits to detect is set by the STOP[2:0] bits in the TOF2 register. The wave number to measure for each stop hit is set by the Hitx Wave Select bits in the TOF3, TOF4, and TOF5 registers.

- 12) After receiving all the programmed hits, the device calculates the average of the recorded hits and stores this to AVGUPINT and AVGUPFrac or

- AVGDNInt and AVGDNFrac. The ratio of  $t_1/t_2$  and  $t_2/t_{\text{IDEAL}}$  are calculated and stored in the WVRUP or WVRDN register.

- 13) Once all the hit data, wave ratios, and averages become available in the Results registers, the TOF bit in the Interrupt Status register is set and the INT pin is asserted (if enabled) and remains asserted until the Interrupt Status register is accessed by the microprocessor with a Read register command.

The computation of the total time of flight is performed by counting the number of full and fractional 4MHz clock cycles that elapsed between the launch start and a hit stop as shown in Figure 4.

Table 1. Two's Complement TOF\_DIFF Conversion Example

| REGISTE           | R VALUE               | CONVERTER VALUE     |  |

|-------------------|-----------------------|---------------------|--|

| TOF_DIFFInt (hex) | TOF_DIFFFrac<br>(hex) | TOF DIFF Value (ns) |  |

| 7FFF              | FFFF                  | 8,191,999.9962      |  |

| 001C              | 0403                  | 7,003.9177          |  |

| 0001              | 00A1                  | 250.6142            |  |

| 0000              | 0089                  | 0.5226              |  |

| 0000              | 0001                  | 0.0038              |  |

| 0000              | 0000                  | 0.0000              |  |

| FFFF              | FFFF                  | -0.0038             |  |

| FFFF              | FFC0                  | -0.2441             |  |

| FFFE              | 1432                  | -480.2780           |  |

| FF1C              | 8001                  | -56,874.9962        |  |

| 8000              | 0000                  | -8,192,000.0000     |  |

Figure 4. Start/Stop for Time-to-Digital Timing

Each TOF measurement result is comprised of an integer portion and a fractional portion. The integer portion is a binary representation of the number of  $t_{4MHz}$  periods that contribute to the time results. The fractional portion is a binary representation of one  $t_{4MHz}$  period quantized to a 16-bit resolution. The maximum size of the integer is 7FFFh or (2<sup>15</sup> - 1) x  $t_{4MHz}$  or  $\sim$  8.19ms. The maximum size of the fraction is FFFFh or (2<sup>16</sup> - 1)/2<sup>16</sup> x  $t_{4MHz}$ . or  $\sim$  249.9961 ns.

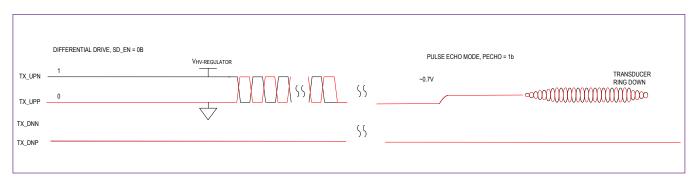

#### **Pulse Echo TOF Mode**

The device also has a pulse echo mode of operation. This mode allows time-of-flight measurements to be taken when only one transducer is used. The sole transducer transmits the high-voltage pulses and then receives the return signal. The time-of-flight measurement operation acts exactly as described in steps 1–13 except that the common mode of the AFE is applied to the same pins that transmitted the high-voltage pulses (Figure 5A).

The resulting data from the measurement is reported in the same manner as described in the TOF\_UP, TOF\_ DOWN, or TOF\_DIFF sections depending upon which command was executed.

The pulse echo mode is enabled by setting the PECHO bit in the Switcher 2 Register.

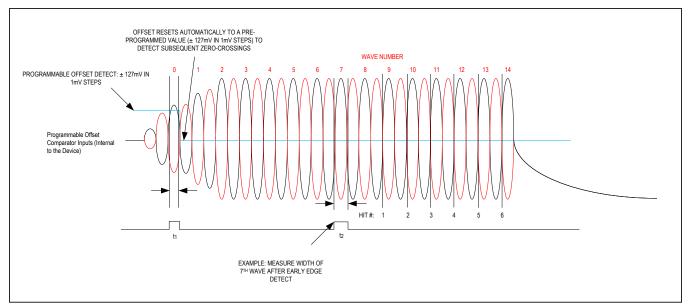

### **Early Edge Detect**

The Early Edge Detect method of measuring the TOF of acoustic waves is used for all the TOF commands including TOF\_UP, TOF\_DN, and TOF\_DIFF. This method allows the device to automatically control the input offset voltage of the receiver comparator so that it can provide advanced measurement accuracy. The input offset of the receiver comparator can be programmed with a range +127 LSBs if triggering on a positive edge and -127 LSBs

if triggering on a negative edge, with 1 LSB =  $V_{CC}/3072$ . Separate input offset settings are available for the Upstream received signal and the Downstream received signal. The input offset for the Upstream received signal is programmed using the C OFFSETUP[6:0] bits in the TOF6 register,. The input offset for the Downstream received signal is programmed using the C\_OFFSETDN[6:0] bits in the TOF7 register. Once the first hit is detected, the time t<sub>1</sub> equal to the width of the earliest detectable edge is measured. The input offset voltage is then automatically and immediately returned to a preprogrammed comparator offset value. This return offset value has a range of +127 LSB's to -128 LSB's in 1 LSB steps and is programmed into the C OFFSETUPR[7:0] bits in the TOF6 register for the Upstream received signal and programmed into the C OFFSETDNR[7:0] bits in the TOF7 register. This preprogrammed comparator offset return value is provided to allow for common-mode shifts that can be present in the received acoustic wave.

The device is now ready to measure the successive hits. The next selected wave that is measured is the  $t_2$  wave. In the example in <u>Figure 5B</u>, this is the 7th wave after the Early Edge Detect wave. The selection of the  $t_2$  wave is made with the T2WV[5:0] bits in the TOF2 register.

With reference to Figure 5B, the ratio  $t_1/t_2$  is calculated and registered for the user. This ratio allows determination of abrupt changes in flow rate, received signal strength, partially filled tube detection, and empty tube. It also provides noise suppression to prevent erroneous edge detection. Also, the ratio  $t_2/t_{\text{IDEAL}}$  is calculated and registered for the user. For this calculation,  $t_{\text{IDEAL}}$  is one-half the period of launched pulse. This ratio adds confirmation that the  $t_2$  wave is a strong signal, which provides insight into the common mode offset of the received acoustic wave.

Figure 5A. Pulse Echo Measurement Mode

Figure 5B. Early Edge Detect Received Wave Example

### **TOF Error Handling**

Any of the TOF measurements can result in an error. If an error occurs during the measurement, all the associated registers report FFFFh. If a TOF\_DIFF is being performed, the TOF\_DIFFInt and TOF\_DIF\_Frac registers report 7FFFh and FFFFh, respectively. The TOF\_DIFF\_AVG Results registers do not include the error measurement. If the measurement error is caused by the time measurement exceeding the timeout set by the TIMOUT[2:0] bits in the TOF2 register, then the TO bit in the Interrupt Status register is set and the INT device pin is asserted (if enabled).

### **Step-Up DC-DC Controller**

In order to increase the power transferred to the transducers during a launch sequence which is required to counteract the high attenuation factors for ultrasonic waves in gaseous mediums the device contains an integrated DC-DC Step-Up controller designed to operate in discontinuous-conduction mode (DCM boost). The controller provides adjustable-output voltage operation including programmable stabilization times with built in under voltage monitoring. The MAX35104's integrated gate driver utilizes the onboard voltage double in order to drive an external N-channel MOSFET's gate from ground to 2 x  $V_{\rm DD}$ . The controller uses an external sense resistor to control the peak inductor current and operates at adjustable switching frequencies.

The integrated boost controller in enabled and disabled automatically by the device. The logic enables the boost before executing a time of flight command and disables the boost once the transmit pulse train is complete, see example timing in the Figure 3. The boost is disabled upon completion of the transmit pulses in order to reduce overall system power consumption as well as to eliminate any controller switching noise that would be introduced during the return signal's timing measurements.

#### **Control and Operation**

The switching frequency of the controller is programmable from 100kHz to 200kHz in 4 steps set by the SFREQ[1:0] bits in the Switcher 1 register. In order to set the output voltage the controller uses an outer loop feedback topology along with a peak current mode inner loop control.

The controller's outer loop targets an output voltage from 9V to 30V based on the programmed value set by the VS[3:0] bits in the Switcher 1 register. An internal error amplifier creates a control voltage, which generates a duty-modulated signal to control the operation of the internal gate driver used to switch the external MOSFET.

Additionally, the MOSFET's source needs an external current sense resistor, which feeds back the inductor's current per cycle as a voltage and compares with the error amplifier's output to further adjust the duty-modulated signal, thus forming an inner loop.