Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **General Description**

The MAX3624 evaluation kit (EV kit) is an assembled demonstration board that provides convenient evaluation of the MAX3624 low-jitter, precision clock generator. The EV kit includes an on-board 25MHz crystal to allow immediate testing.

The EV kit includes switches to allow easy selection of different modes of operation. The reference input and clock outputs use SMA connectors and are AC-coupled to simplify connection to test equipment.

**Ordering Information**

| PART         | TEMP RANGE   | IC PACKAGE |

|--------------|--------------|------------|

| MAX3624EVKIT | 0°C to +85°C | 32 TQFP-EP |

### **Features**

- ♦ AC-Coupled I/Os for Ease of Testing

- ♦ Fully Assembled and Tested

- ♦ +3.3V Power-Supply Operation

- ♦ On-Board 25MHz Crystal

### **Part Suppliers**

| SUPPLIER | WEBSITE     |  |

|----------|-------------|--|

| NDK      | www.ndk.com |  |

### Component List

| DESIGNATION                                     | QTY | DESCRIPTION                           |

|-------------------------------------------------|-----|---------------------------------------|

| C1, C3, C4, C5,<br>C7–C10, C19,<br>C25–C30, C54 | 16  | 0.1µF ±10% ceramic capacitors (0402)  |

| C2                                              | 1   | 10μF ±10% ceramic capacitor (0603)    |

| C6, C57–C60                                     | 5   | 0.01µF ±10% ceramic capacitors (0402) |

| C22                                             | 1   | 27pF ±10% ceramic capacitor (0402)    |

| C23                                             | 1   | 33pF ±10% ceramic capacitor (0402)    |

| C65                                             | 1   | 4.7pF ±10% ceramic capacitor (0402)   |

| J1, J3, J5                                      | 0   | Not installed                         |

| J2, J48                                         | 2   | Test points                           |

| J4                                              | 1   | 2-pin header, 0.1in centers           |

| J13–J16, J18,<br>J19, J36, J43                  | 8   | SMA connectors                        |

| DESIGNATION                         | QTY | DESCRIPTION                         |

|-------------------------------------|-----|-------------------------------------|

| L1                                  | 1   | 2.7µH inductor                      |

| R1-R5, R7                           | 6   | 150Ω ±5% resistors (0402)           |

| R6, R8, R9                          | 0   | Not installed                       |

| R42                                 | 1   | 499Ω ±1% resistor (0402)            |

| R57                                 | 1   | 49.9Ω ±1% resistor (0402)           |

| R59                                 | 1   | 10.5Ω ±1% resistor (0402)           |

| R61                                 | 1   | 36Ω ±5% resistor (0402)             |

| SW1-SW3,<br>SW11                    | 4   | SP3T switches                       |

| SW4, SW6–SW9<br>SW12, SW13,<br>SW15 | 8   | SPDT switches                       |

| TP6, TP7                            | 2   | Test points                         |

| U1                                  | 1   | MAX3624UTJ+                         |

| Y1                                  | 1   | 25MHz crystal<br>NDK EXS00A-AT00429 |

| None                                | 1   | Shunt                               |

| None                                | 1   | PCB: MAX3624 Board, Rev B           |

### **Quick Start**

For evaluation of the MAX3624, configure the EV kit as

- 1) Determine which output is going to be evaluated and connect to the test equipment through SMA cables. Be sure not to leave any outputs unterminated, i.e., place  $50\Omega$  terminators on all unused outputs.

- 2) Connect a +3.3V power supply to J48 (VCC) and J2 (GND). Set the current limit to 200mA.

- 3) If the on-board crystal is used (IN\_SEL set high), the PLL divider should be set to divide by 25 (FB\_SEL1 and FB\_SEL0 set low) to achieve the standard output rates shown in Table 3.

- 4) Use Table 3 to set the output divider switches to achieve the output frequency desired.

- 5) Enable the output under test by setting the related output-enable switch, Qx\_OE, high.

### Table 1. Adjustment and Control Descriptions (see Quick Start first)

| COMPONENT | NAME              | FUNCTION                                                                                                                                             |  |

|-----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J4        | INDUCTOR<br>SHUNT | J4 shunts the power-supply inductor. Normal operation is J4 shunted.                                                                                 |  |

| SW1       | SELB1             | SW1 and SW2 set the output divider for the QB outputs. See Table 2 for more information.                                                             |  |

| SW2       | SELB0             | SW1 and SW2 set the output divider for the QB outputs. See Table 2 for more information.                                                             |  |

| SW3       | SELA1             | SW3 and SW11 set the output divider for the QA outputs. See Table 2 for more information.                                                            |  |

| SW4       | QAC_OE            | Set high to enable the LVCMOS output, QA_C. Set low to disable QA_C.                                                                                 |  |

| SW6       | BYPASS            | Set low to bypass the PLL. Set high to engage the PLL. Note that when the PLL is bypassed, the output dividers are automatically set to divide by 1. |  |

| SW7       | FB_SEL1           | SW7 and SW8 set the PLL divider. See Table 3 for more information.                                                                                   |  |

| SW8       | FB_SEL0           | SW7 and SW8 set the PLL divider. See Table 3 for more information.                                                                                   |  |

| SW9       | QA_OE             | Set high to enable LVPECL output QA. Set low to force a logic zero at QA.                                                                            |  |

| SW11      | SELA0             | SW3 and SW11 set the output divider for the QA outputs. See Table 2 for more information.                                                            |  |

| SW12      | QB1_OE            | Set high to enable LVPECL output QB1. Set low to force a logic zero at QB1.                                                                          |  |

| SW13      | IN_SEL            | Set high to select the crystal as the frequency source. Set low to select the REF_IN as the frequency source.                                        |  |

| SW15      | QB0_OE            | Set high to enable LVPECL output QB0. Set low to force a logic zero at QB0.                                                                          |  |

**Table 2. PLL Divider Settings**

| INPUT   |         | М       |  |

|---------|---------|---------|--|

| FB_SEL1 | FB_SEL0 | DIVIDER |  |

| LOW     | LOW     | ÷25     |  |

| LOW     | HIGH    | ÷24     |  |

| HIGH    | LOW     | ÷32     |  |

| HIGH    | HIGH    | ÷16     |  |

**Table 3. Output Divider Settings**

| INPUT       |             | NA/NB DIVIDER | OUTPUT<br>FREQUENCY<br>(MHz) |

|-------------|-------------|---------------|------------------------------|

| SELA1/SELB1 | SELA0/SELB0 |               | M = 25 AND<br>XTAL = 25MHz   |

| LOW         | LOW         | ÷2            | 312.5                        |

| LOW         | HIGH        | ÷3            | 208.33                       |

| HIGH        | LOW         | ÷4            | 156.25                       |

| HIGH        | HIGH        | ÷5            | 125                          |

| HIGH        | OPEN        | ÷6            | 104.16                       |

| OPEN        | HIGH        | ÷8            | 78.125                       |

| LOW         | OPEN        | ÷10           | 62.5                         |

| OPEN        | LOW         | ÷12           | 52.08                        |

| OPEN        | OPEN        | ÷1            | 625                          |

*Note:* 625MHz is beyond the maximum specified operating frequency.

### **Evaluates: MAX3624**

# 1AX3624 Evaluation Kit

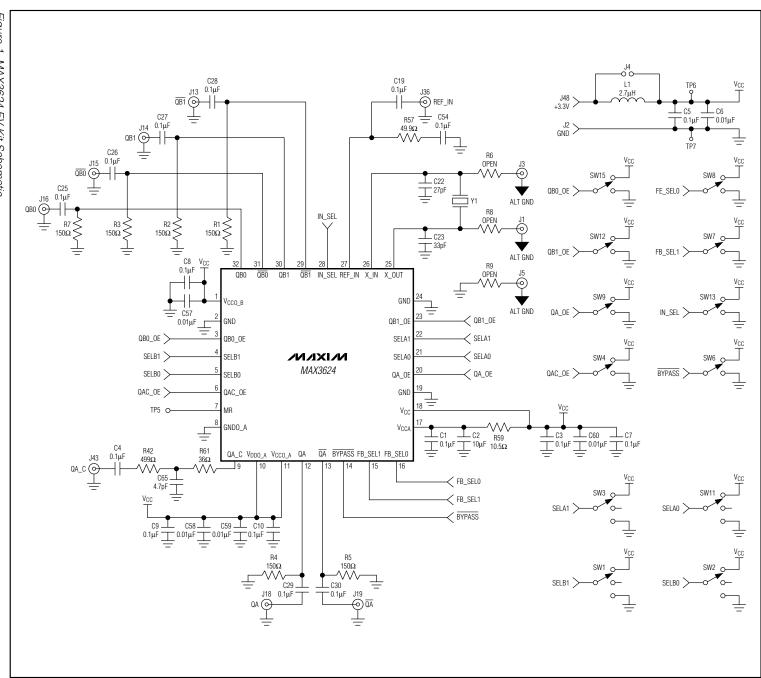

Figure 1. MAX3624 EV Kit Schematic

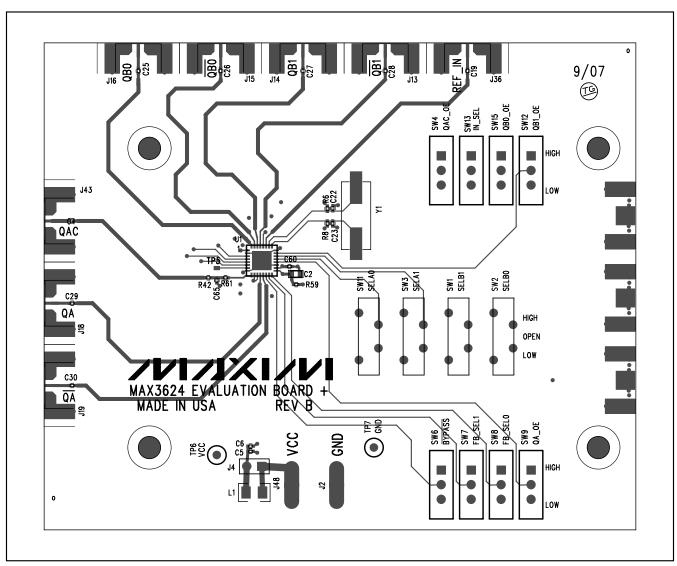

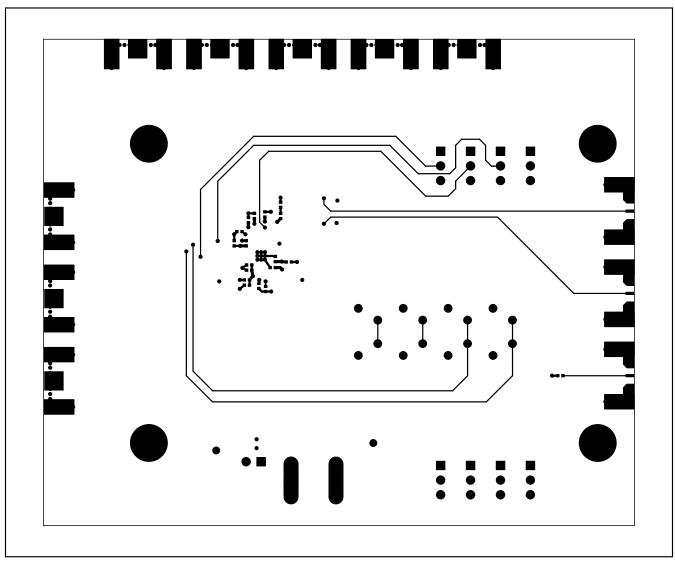

Figure 2. MAX3624 EV Kit Assembly Drawing—Top Side

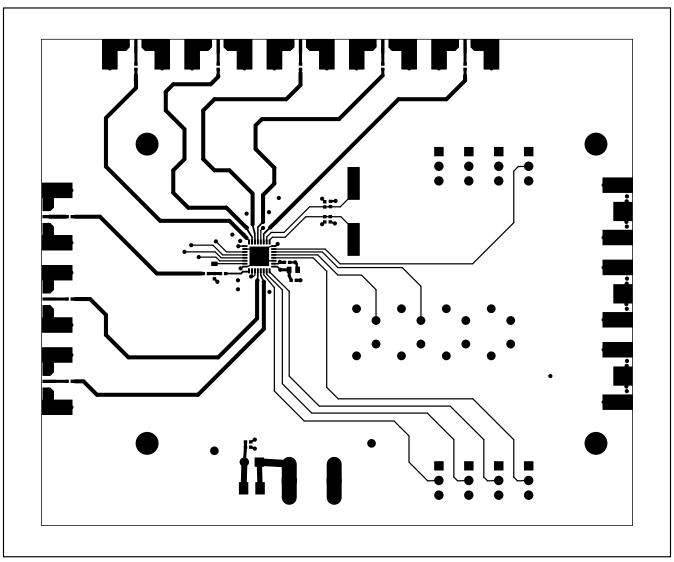

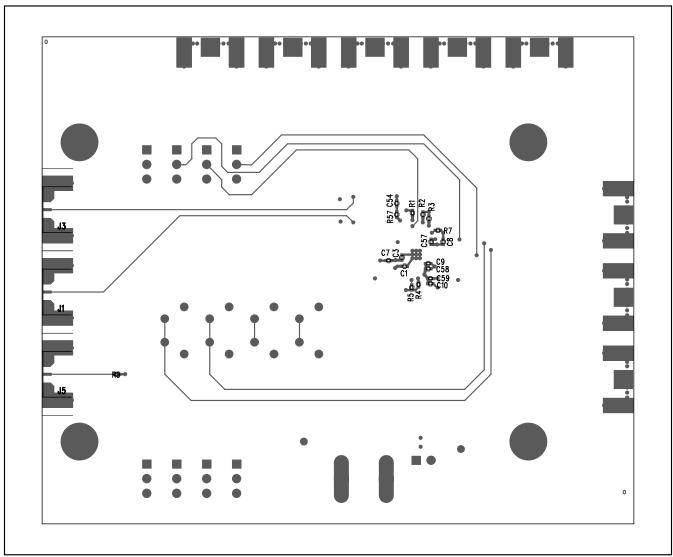

Figure 3. MAX3624 EV Kit Layout—Component Side

MIXIN \_\_\_\_\_\_

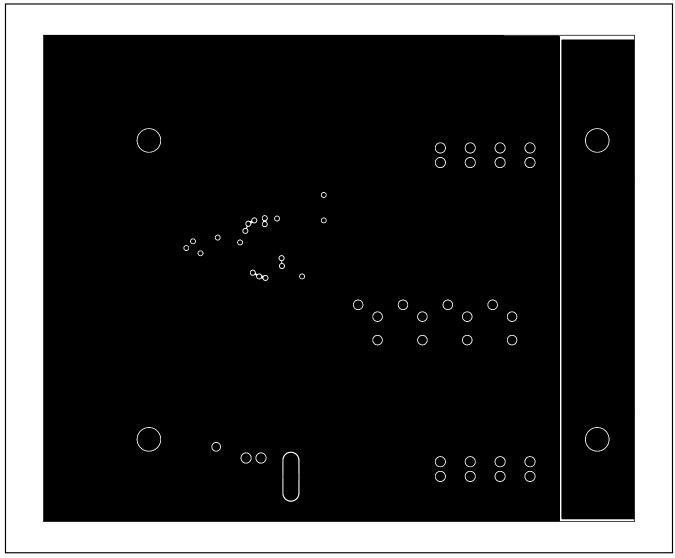

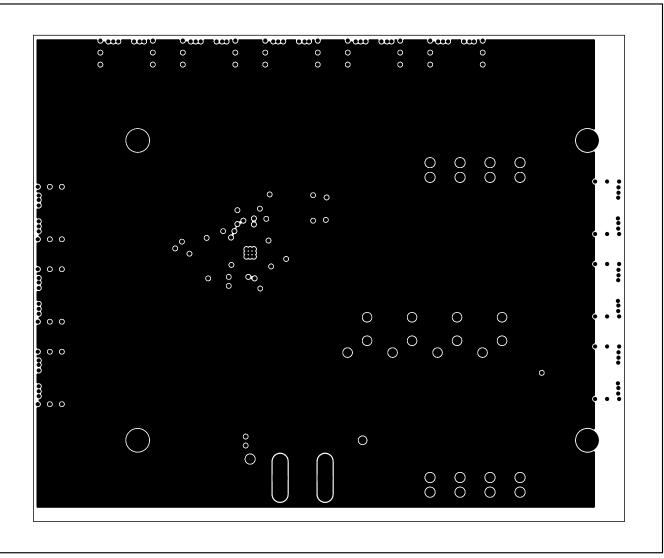

Figure 4. MAX3624 EV Kit Layout—Ground Plane

MAXIM \_\_\_\_\_

Figure 5. MAX3624 EV Kit Layout—Power Plane

3 \_\_\_\_\_\_*NIXIM*

Figure 6. MAX3624 EV Kit Layout—Solder Plane

Figure 7. MAX3624 EV Kit Assembly Drawing—Bottom Side