Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### General Description

The MAX3645 limiting amplifier functions as a data quantizer and is pin compatible with the Mindspeed MC2045-2 and MC2045-2Y postamplifiers. The amplifier accepts a wide range of input voltages and provides constant-level positive emitter-coupled logic (PECL) output voltages with controlled edge speeds.

The MAX3645 features an integrated power detector with complementary PECL loss-of-signal (LOS) outputs that indicate when the input power level drops below a programmable threshold. An optional squelch function holds the data outputs at static levels during a LOS condition.

The MAX3645 operates from a single +3.3V or +5.0V power supply over a -40°C to +85°C temperature range. It is available in 16-pin SO and 16-pin QSOP packages.

### Applications

SONET 155Mbps Transceivers Fast Ethernet Receivers FDDI 125Mbps Receivers FTTx Receivers **ESCON Receivers**

#### Features

- **♦ Pin Compatible with the Mindspeed** MC2045-2/MC2045-2Y

- ♦ 500µV Input Sensitivity (BER = 10<sup>-12</sup>)

- ♦ Compatible with 4B/5B Data Coding

- ♦ Programmable LOS Threshold

- ♦ Stable LOS Threshold Over Supply Range

- ♦ Output Disable Function and Automatic Squelch

- ♦ Single +3.3V or +5.0V Power Supply

- ♦ 18mA Supply Current

### Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX3645ESE  | -40°C to +85°C | 16 SO       |

| MAX3645EEE  | -40°C to +85°C | 16 QSOP     |

| MAX3645EEE+ | -40°C to +85°C | 16 QSOP     |

+ Denotes lead-free package.

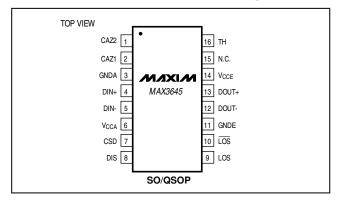

### Pin Configuration

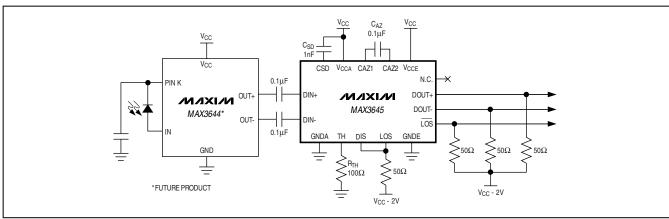

# Typical Application Circuit

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Voltage (V <sub>CCA</sub> , V <sub>CCE</sub> )0.5V to +7 | .0V |

|-----------------------------------------------------------------------|-----|

| Voltage at CAZ1, CAZ2, DIN+,                                          |     |

| DIN-, CSD, DIS, TH0.5V to (V <sub>CC</sub> + 0.                       | 5V) |

| PECL Output Current (DOUT+, DOUT-, LOS, LOS)50                        | mÀ  |

| Differential Voltage between CAZ1 and CAZ21.5V to +1                  | .5V |

| Differential Voltage between DIN+ and DIN1.5V to +1                   | .5V |

| Continuous Power Dissipation ( $T_A = +85^{\circ}C$ ) |         |

|-------------------------------------------------------|---------|

| 16-Pin SO (derate 8.7mW/°C above +85°C)               | 565mW   |

| 16-Pin QSOP (derate 8.3mW/°C above +85°C)             | 540mW   |

| Storage Ambient Temperature Range (Ts)65°C to         | +160°C  |

| Lead Temperature (soldering, 10s)                     | .+300°C |

|                                                       |         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.97V \text{ to } +5.5V, \text{ PECL outputs are terminated with } 50\Omega \text{ to } V_{CC} - 2V, R_{TH} = 100\Omega, C_{AZ} = 0.1 \mu\text{F}, C_{SD} = 1 n\text{F}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3V$ ,  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                     | SYMBOL                            | CONDITIONS                                                    | MIN                       | TYP                    | MAX                       | UNITS             |

|-------------------------------|-----------------------------------|---------------------------------------------------------------|---------------------------|------------------------|---------------------------|-------------------|

| POWER SUPPLY                  | •                                 |                                                               |                           |                        |                           |                   |

| Supply Current                | Icc                               | Excludes PECL termination currents                            |                           | 18                     | 27                        | mA                |

| INPUT SPECIFICATIONS          |                                   |                                                               |                           |                        |                           |                   |

| Input Resistance              | R <sub>IN</sub>                   | Single ended; V <sub>IN</sub> = ±200mV                        | 3.3                       | 4.8                    | 6.4                       | kΩ                |

| Input Consitiuity (Note 1)    | Variable                          | Single ended                                                  |                           |                        | 0.5                       | mV <sub>P-P</sub> |

| Input Sensitivity (Note 1)    | V <sub>IN-MIN</sub>               | Differential                                                  |                           |                        | 1.0                       |                   |

| Input Overland (Note 1)       | \/m                               | Single ended                                                  | 750                       |                        |                           | mV <sub>P-P</sub> |

| Input Overload (Note 1)       | V <sub>IN-MAX</sub>               | Differential                                                  | 1500                      |                        |                           |                   |

| Input-Referred Offset Voltage |                                   | Unterminated input, output offset divided by DC gain (Note 2) |                           | 2                      | 40                        | μV                |

| Input Common-Mode Voltage     | V <sub>СММ</sub>                  |                                                               |                           | V <sub>CC</sub> - 0.87 |                           | V                 |

| Input-Referred RMS Noise      | V <sub>IN-NOISE</sub>             | (Notes 2, 3)                                                  |                           | 36                     | 50                        | μV <sub>RMS</sub> |

| DIS Input High                | VIH                               | PECL or CMOS logic                                            | V <sub>CC</sub> -<br>1160 |                        | V <sub>CC</sub>           | mV                |

| DIS Input Low                 | VIL                               | PECL or CMOS logic                                            | 0                         |                        | V <sub>CC</sub> -<br>1480 | mV                |

| DIS Input Current             | I <sub>IL</sub> , I <sub>IH</sub> | 0V ≤ V <sub>DIS</sub> ≤ V <sub>CC</sub>                       | -10                       |                        | +10                       | μΑ                |

| OUTPUT SPECIFICATIONS         |                                   |                                                               |                           |                        |                           |                   |

| PECL Output-Voltage High      |                                   | (Notes 1, 2)                                                  | V <sub>CC</sub> -<br>1085 |                        | V <sub>CC</sub> -         | mV                |

| PECL Output-Voltage Low       |                                   | (Notes 1, 2)                                                  | V <sub>CC</sub> -<br>1830 |                        | V <sub>CC</sub> -<br>1555 | mV                |

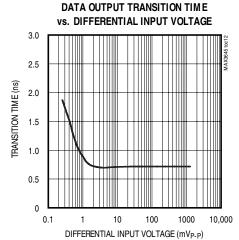

| Data Output Transition Time   | t <sub>R</sub> , t <sub>F</sub>   | 20% to 80% (Notes 1, 2, 4)                                    |                           | 0.7                    | 1.4                       | ns                |

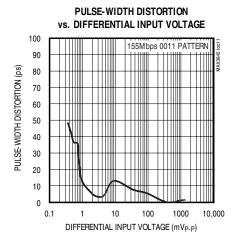

| Pulse-Width Distortion        | PWD                               | (Notes 1, 2, 4, 5)                                            |                           | 30                     | 200                       | ps                |

|                               |                                   |                                                               |                           |                        |                           |                   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=+2.97V\ to\ +5.5V,\ PECL\ outputs$  are terminated with  $50\Omega$  to  $V_{CC}$  -  $2V,\ R_{TH}=100\Omega,\ C_{AZ}=0.1\mu F,\ C_{SD}=1nF,\ T_A=-40^{\circ}C$  to  $+85^{\circ}C.$  Typical values are at  $V_{CC}=+3.3V,\ T_A=+25^{\circ}C,\ unless otherwise\ noted.)$

| PARAMETER                        | SYMBOL                                        | CONDITIONS                            | MIN | TYP  | MAX  | UNITS             |

|----------------------------------|-----------------------------------------------|---------------------------------------|-----|------|------|-------------------|

| TRANSFER CHARACTERISTICS         |                                               |                                       |     |      |      |                   |

| Bandwidth                        |                                               | Gain = 60dB                           | 150 | 250  |      | MHz               |

| Low Fraguency Cutoff             |                                               | C <sub>AZ</sub> = open                |     | 500  |      | 1411=             |

| Low-Frequency Cutoff             |                                               | $C_{AZ} = 0.1 \mu F$                  |     | 0.5  |      | kHz               |

| LOSS-OF-SIGNAL SPECIFICATION     | LOSS-OF-SIGNAL SPECIFICATIONS (Notes 2, 4, 6) |                                       |     |      |      |                   |

| LOS Sensitivity Range            |                                               | $0\Omega \le R_{TH} \le 2k\Omega$     | 2   |      | 20   | mV <sub>P-P</sub> |

| LOS Hysteresis                   |                                               | 10log (VDEASSERT/VASSERT)             | 1.4 | 2    |      | dB                |

| LOS Assert/Deassert Time         |                                               | (Note 7)                              | 2.3 |      | 80.0 | μs                |

|                                  |                                               | $R_{TH} = 0\Omega$ , low setting      | 0.5 | 0.9  | 1.3  |                   |

| LOS Assert Level                 |                                               | R <sub>TH</sub> = 1kΩ, medium setting | 4.8 | 6.6  | 8.3  | mV <sub>P-P</sub> |

|                                  |                                               | $R_{TH} = 2k\Omega$ , high setting    | 12  | 17   | 22   |                   |

| LOS Deassert Level               |                                               | $R_{TH} = 0\Omega$ , low setting      | 1.1 | 1.5  | 1.9  |                   |

|                                  |                                               | $R_{TH} = 1k\Omega$ , medium setting  | 8.0 | 10.8 | 13.5 | mV <sub>P-P</sub> |

|                                  |                                               | $R_{TH} = 2k\Omega$ , high setting    | 20  | 28   | 36   |                   |

| Signal-Dectect Filter Resistance | R <sub>SD</sub>                               | Pin 7                                 | 14  | 20   | 26   | kΩ                |

- Note 1: Between sensitivity and overload, the output amplitude is >95% of the fully limited amplitude and all AC specifications are met.

- Note 2: Guaranteed by design and characterization.

- Note 3: Noise is derived from BER measurement.

- Note 4: The data input transition time is controlled by a 4th-order Bessel filter with f-3dB = 0.75 × data rate.

- Note 5: PWD = [(width of wider pulse) (width of narrower pulse)] / 2, measured with 155Mbps 0011 pattern.

- **Note 6:** All LOS specifications are measured using a 155Mbps 2<sup>23</sup> 1 PRBS pattern.

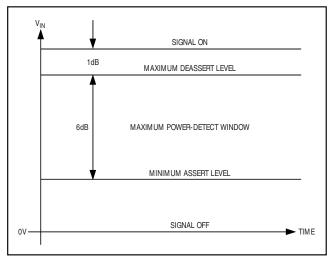

- Note 7: The signal at the input is switched between two amplitudes, SIGNAL\_ON and SIGNAL\_OFF, as shown in Figure 1.

Figure 1. Signal Levels for LOS Assert/Deassert Time Measurement

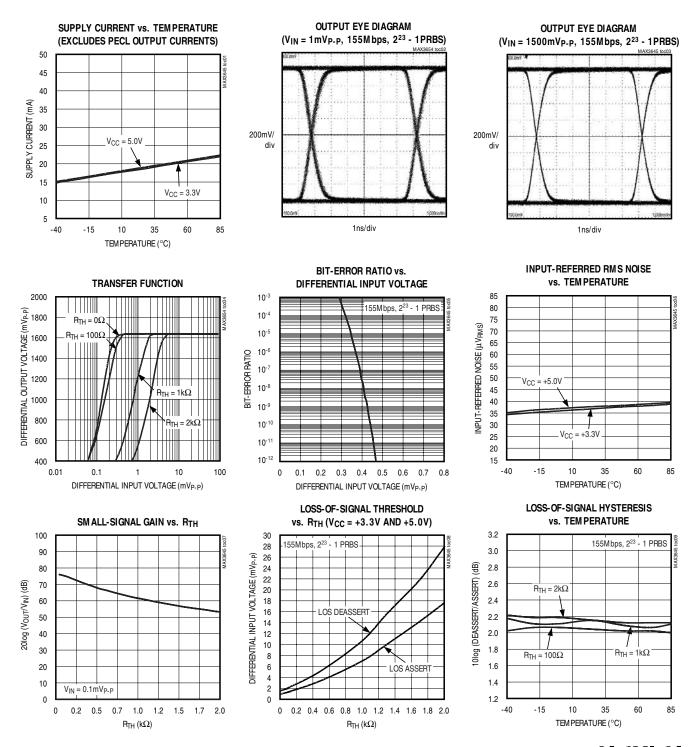

## Typical Operating Characteristics

$(V_{CC} = 3.3V, PECL \text{ outputs terminated with } 50\Omega \text{ to } V_{CC} - 2V, R_{TH} = 100\Omega, C_{AZ} = 0.1 \mu F, C_{SD} = 1 nF, T_A = +25 ^{\circ}C, unless \text{ otherwise noted.})$

## Typical Operating Characteristics (continued)

$(V_{CC} = 3.3V, PECL \text{ outputs terminated with } 50\Omega \text{ to } V_{CC} - 2V, R_{TH} = 100\Omega, C_{AZ} = 0.1 \mu F, C_{SD} = 1 nF, T_A = +25 ^{\circ}C, unless \text{ otherwise noted.})$

Pin Description

| PIN | MINDSPEED<br>MC2045-2<br>MC2045-2Y<br>PIN NAME | MAXIM<br>MAX3645<br>PIN NAME | FUNCTION                                                                                                                                                                                                                                                 |  |

|-----|------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | CAZ-                                           | CAZ2                         | Offset-Correction-Loop Capacitor Connection. A capacitor connected between this pin and CAZ1 sets the time constant of the offset correction loop. The offset correction is disabled when the CAZ1 and CAZ2 pins are shorted together.                   |  |

| 2   | CAZ+                                           | CAZ1                         | Offset-Correction-Loop Capacitor Connection. A capacitor connected between this pin and CAZ2 sets the time constant of the offset correction loop. The offset correction is disabled when the CAZ2 and CAZ1 pins are shorted together.                   |  |

| 3   | GNDA                                           | GNDA                         | Analog Supply Ground. Must be at the same potential as the GNDE pin.                                                                                                                                                                                     |  |

| 4   | D <sub>IN</sub>                                | DIN+                         | Positive Data Input                                                                                                                                                                                                                                      |  |

| 5   | DIN                                            | DIN-                         | Negative Data Input                                                                                                                                                                                                                                      |  |

| 6   | VCCA                                           | VCCA                         | +2.97V to +5.5V Analog Supply Voltage. Must be at same potential as the V <sub>CCE</sub> pin.                                                                                                                                                            |  |

| 7   | CF                                             | CSD                          | Signal-Detect-Filter Capacitor Connection. Connect the C <sub>SD</sub> capacitor between CSD and V <sub>CCA</sub> .                                                                                                                                      |  |

| 8   | JAM                                            | DIS                          | Disable Input, PECL or CMOS Compatible. Data outputs are held to a static logic 0 when DIS is asserted high. The LOS function remains active when the outputs are disabled. When connected to the LOS pin, an automatic squelch function is enabled.     |  |

| 9   | ST                                             | LOS                          | Positive Loss-of-Signal Output, PECL. LOS is high when the level of the input signal drops below the threshold set by the TH input. LOS is low when the signal level is above the threshold. LOS can be connected directly to DIS for automatic squelch. |  |

| 10  | ST                                             | TOS                          | Negative Loss-of-Signal Output, PECL. $\overline{\text{LOS}}$ is low when the level of the input signal drops below the threshold set by the TH input. $\overline{\text{LOS}}$ is high when the signal level is above the threshold.                     |  |

| 11  | GNDE                                           | GNDE                         | Digital Supply Ground. Must be at the same potential as the GNDA pin.                                                                                                                                                                                    |  |

| 12  | D <sub>OUT</sub>                               | DOUT-                        | Negative Data Output, PECL. A high at DIS forces DOUT- high.                                                                                                                                                                                             |  |

| 13  | Dout                                           | DOUT+                        | Positive Data Output, PECL. A high at DIS forces DOUT+ low.                                                                                                                                                                                              |  |

| 14  | V <sub>CCE</sub>                               | V <sub>CCE</sub>             | +2.97V to +5.5V Digital Supply Voltage. Must be at the same potential as the V <sub>CCA</sub> pin.                                                                                                                                                       |  |

| 15  | NC                                             | N.C.                         | No Connection                                                                                                                                                                                                                                            |  |

| 16  | V <sub>SET</sub>                               | TH                           | Loss-of-Signal Threshold Pin. Resistor (R <sub>TH</sub> ) to ground sets the LOS threshold. This pin cannot be left open.                                                                                                                                |  |

## Detailed Description

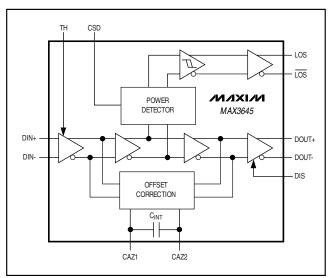

The MAX3645 consists of gain stages, offset correction, power detector, LOS indicators, and PECL output buffers. See Figure 2 for the functional diagram.

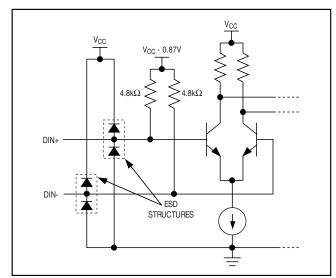

#### Data Input

The data inputs have a single-ended input resistance of  $4.8k\Omega$  and are internally DC-biased to  $V_{CC}$  - 0.87V (see Figure 3). External capacitors are required to AC-couple the data signals. Pattern-dependent jitter is minimized by using coupling capacitor values large enough to pass the lowest frequencies of interest (consecutive ones and zeros) with the given input resistance.

Typically,  $0.1\mu F$  coupling capacitors yield a -3dB frequency of 354Hz. Capacitor tolerance and input resis-

tance variation  $(3.3 k\Omega$  to  $6.4 k\Omega)$  must be considered to accurately calculate the -3dB frequency. Capacitor values should be chosen that set the -3dB frequency at least a factor of 10 below the lowest frequency of interest. A capacitor value of  $0.1 \mu F$  is recommended.

#### Gain Stage and Offset Correction

The limiting amplifier provides approximately 74dB ( $R_{TH}=100\Omega$ ) of gain. This large gain makes the amplifier susceptible to small DC offsets in the signal path. To correct DC offsets, the amplifier has an internal feedback loop that acts as a DC autozero circuit. By correcting the DC offsets, the limiting amplifier improves receiver sensitivity and power-detector accuracy.

Figure 2. Functional Diagram

The external autozero capacitor ( $C_{AZ}$ ), in parallel with internal capacitance ( $C_{INT}$ ), determines the time constant of the DC offset correction loop. With  $C_{AZ}=0.1\mu F$  (recommended), the -3dB frequency cutoff of the signal path is typically 0.5kHz.

#### Power Detector and LOS Indicators

The external resistor R<sub>TH</sub> sets the gain of the first limiting stage. This gain setting controls the threshold at which the power detector indicates an LOS condition. Power detection is accomplished by rectifying and low-pass filtering the data signal, then comparing it to the programmed threshold voltage. A hysteresis of 2dB prevents the LOS output from chattering when the input signal is near the threshold.

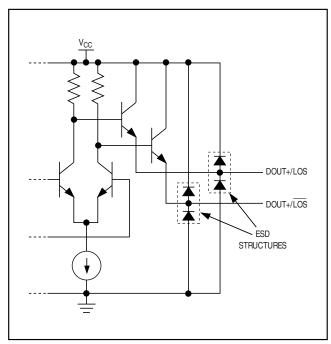

#### **PECL Output Buffer**

The data outputs (DOUT+, DOUT-) and the loss-of-signal outputs (LOS+, LOS-) are PECL outputs. The equivalent PECL output circuit is shown in Figure 4.

# Applications Information

**Programming LOS Assert/Deassert Levels**The appropriate value of R<sub>TH</sub> is determined by using the Loss-Of-Signal Threshold vs. R<sub>TH</sub> graph in the *Typical Operating Characteristics*.

#### LOS Time Constant

The lowpass filter of the power detector comprises a  $20k\Omega$  on-chip resistor (RSD) and an external capacitor (CSD). The CSD capacitor value determines the power-

Figure 3. Equivalent Data Input Circuit

detector time constant, which determines the LOS assert/deassert time. With  $C_{SD}=1nF$  the assert/deassert time is in the range of 2.3µs to 80µs. This provides a long enough time constant to avoid false triggering due to variations in mark density.

#### Disable Function

When the DIS input is forced high, the disable function is enabled, which holds DOUT+ low and DOUT- high. The disable function is used to prevent the data outputs from toggling due to noise when no signal is present. The LOS output can be connected to the DIS input for automatic squelch.

### **PECL Output Terminations**

The proper termination for a PECL output is  $50\Omega$  to (V<sub>CC</sub> - 2V), but other standard termination techniques can be used. For more information on PECL terminations and how to interface with other logic families, refer to Maxim Application Note *HFAN-01.0: Introduction to LVDS, PECL, and CML*.

### Layout Considerations

For best performance, use good high-frequency layout techniques. Filter power supplies, keep ground connections short, and use multiple vias where possible. Power-supply decoupling should be placed close to the V<sub>CC</sub> pins. Minimize the distance from the preamplifier and use controlled-impedance transmission lines to interface with the outputs when possible.

Figure 4. Equivalent PECL Output Circuit

Chip Information

TRANSISTOR COUNT: 1026 PROCESS: Silicon bipolar

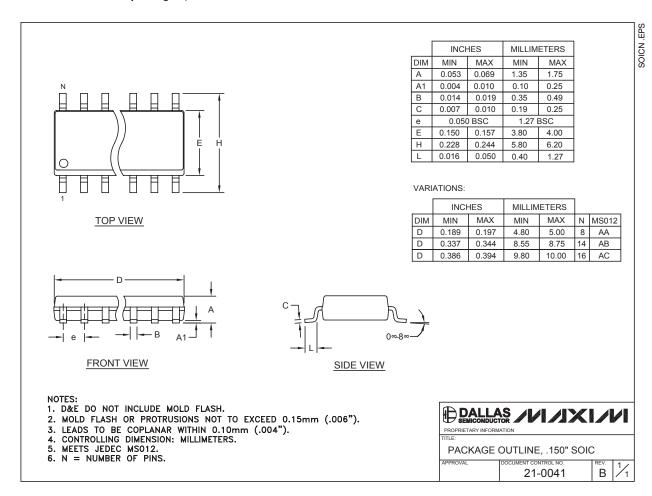

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

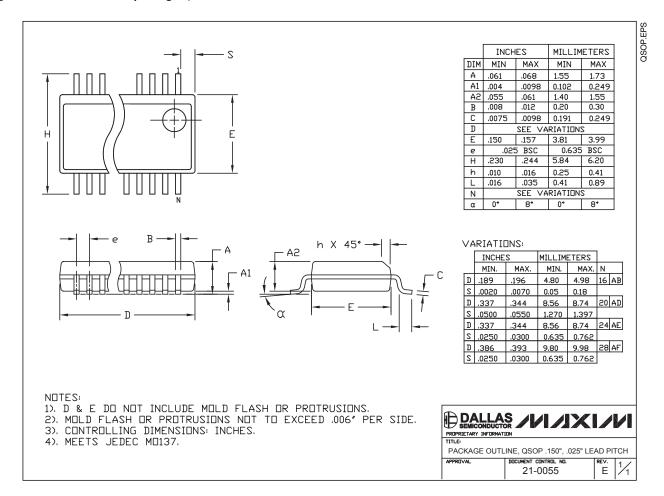

Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.