# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **General Description**

The MAX3671 is a low-jitter frequency synthesizer that accepts two reference clock inputs and generates nine phase-aligned outputs. The device features 40kHz jitter transfer bandwidth, 0.3ps<sub>RMS</sub> (12kHz to 20MHz) integrated phase jitter, and best-in-class power-supply noise rejection (PSNR), making it ideal for jitter clean-up, frequency translation, and clock distribution in Gigabit Ethernet applications.

The MAX3671 operates from a single +3.3V supply and typically consumes 400mW. The IC is available in an 8mm x 8mm, 56-pin TQFN package, and operates from -40°C to +85°C.

#### **Applications**

Gigabit Ethernet Routers and Switches

Frequency Translation

Jitter Cleanup

Clock Distribution

# Pin Configuration and Typical Application Circuits appear at end of data sheet.

- Two Reference Clock Inputs: LVPECL

- Nine Phase-Aligned Clock Outputs: LVPECL

- Input Frequencies: 62.5MHz,125MHz, 250MHz, 312.5MHz

- Output Frequencies: 62.5MHz, 125MHz, 156.25MHz, 250MHz, 312.5MHz

- ◆ Low-Jitter Generation: 0.3ps<sub>RMS</sub> (12kHz to 20MHz)

- Clock Failure Indicator for Both Reference Clocks

- External Feedback Provides Zero-Delay Capability

- Low Output Skew: 20ps Typical

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX3671ETN+ | -40°C to +85°C | 56 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

# MAX367

**Features**

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage Range (V<sub>CC</sub>, VCC\_VCO).....-0.3V to +4.0V LVPECL Output Current (OUTA[3:0], OUTA[3:0], OUTB[4:0], OUTB[4:0]) .....-56mA

All Other Pins.....-0.3V to  $(V_{CC} + 0.3V)$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +3.0V to +3.6V, T<sub>A</sub> = -40°C to +85°C, C<sub>PLL</sub> = 0.1 $\mu$ F, C<sub>REG</sub> = 0.22 $\mu$ F. Typical values are at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                             | SYMBOL        | CONDITIONS                                       | MIN                   | ТҮР                       | MAX                      | UNITS |

|-------------------------------------------------------|---------------|--------------------------------------------------|-----------------------|---------------------------|--------------------------|-------|

| Supply Current                                        | Icc           | LVPECL outputs unterminated                      |                       | 120                       | 175                      | mA    |

| POWER-ON RESET                                        |               |                                                  |                       |                           |                          |       |

| V <sub>CC</sub> Rising                                |               | (Note 1)                                         |                       | 2.55                      |                          | V     |

| V <sub>CC</sub> Falling                               |               | (Note 1)                                         |                       | 2.45                      |                          | V     |

| LVCMOS/LVTTL INPUTS (MR, SE                           | EL_CLK, PLL   | _BYPASS, FB_SEL)                                 |                       |                           |                          |       |

| Input High Voltage                                    | VIH           |                                                  | 2.0                   |                           |                          | V     |

| Input Low Voltage                                     | VIL           |                                                  |                       |                           | 0.8                      | V     |

| Input High Current                                    | Ιн            | $V_{IN} = V_{CC}$                                |                       |                           | 75                       | μA    |

| Input Low Current                                     | ١L            | $V_{IN} = GND$                                   | -75                   |                           |                          | μA    |

| LVCMOS/LVTTL OUTPUTS (IN0F                            | AIL, IN1FAIL, | LOCK)                                            |                       |                           |                          |       |

| Output High Voltage                                   | Voh           | I <sub>OH</sub> = -8mA                           | 2.4                   |                           |                          | V     |

| Output Low Voltage                                    | VOL           | $I_{OL} = +8mA$                                  |                       |                           | 0.4                      | V     |

| LVPECL INPUTS (REFCLK0, REI                           | FCLK0, REFC   | LK1, REFCLK1, FB_IN, FB_IN) (Note 2)             |                       |                           |                          |       |

| Input High Voltage                                    | VIH           |                                                  |                       |                           | V <sub>CC</sub> -<br>0.7 | V     |

| Input Low Voltage                                     | VIL           |                                                  | V <sub>CC</sub> - 2.0 |                           |                          | V     |

| Input Bias Voltage                                    | Vсмі          |                                                  | V <sub>CC</sub> - 1.8 | V <sub>CC</sub> -<br>1.34 |                          | V     |

| Differential-Input Swing                              |               |                                                  | 0.15                  |                           | 1.9                      | VP-P  |

| Differential-Input Impedance                          |               |                                                  |                       | > 40                      |                          | kΩ    |

| Common-Mode Input Impedance                           |               |                                                  |                       | > 14                      |                          | kΩ    |

| Input Capacitance                                     |               |                                                  |                       | 1.5                       |                          | pF    |

| Input Current                                         |               | $V_{IH} = V_{CC} - 0.7V, V_{IL} = V_{CC} - 2.0V$ | -100                  |                           | +100                     | μA    |

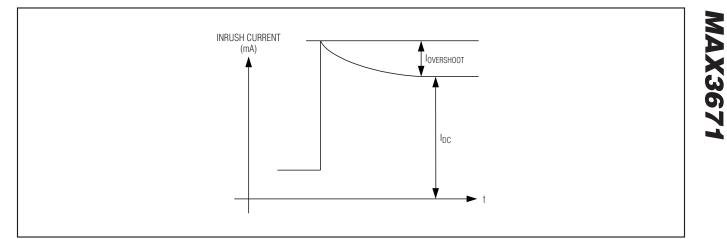

| Input Inrush Current When Power is Off (Steady State) | IDC           | (Notes 3, 4)                                     |                       | 8                         |                          | mA    |

| Input Inrush Current Overshoot<br>When Power is Off   | IOVERSHOOT    | (Notes 3, 4)                                     |                       | 6                         |                          | mA    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, C_{PLL} = 0.1\mu\text{F}, C_{REG} = 0.22\mu\text{F}.$  Typical values are at  $V_{CC} = +3.3V, T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                                                                                                | SYMBOL                          | CONDITIONS                                             | MIN                       | ТҮР                       | MAX                       | UNITS             |

|----------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------------------|

| REFERENCE CLOCK INPUTS (R                                                                                | EFCLK0, RE                      | FCLK0, REFCLK1, REFCLK1)                               | -                         |                           |                           | •                 |

| Reference Clock Frequency                                                                                | fref                            |                                                        |                           | Table 1                   |                           | MHz               |

| Reference Clock Frequency<br>Tolerance                                                                   |                                 |                                                        | -200                      |                           | +200                      | ppm               |

| Reference Clock Duty Cycle                                                                               |                                 |                                                        | 40                        |                           | 60                        | %                 |

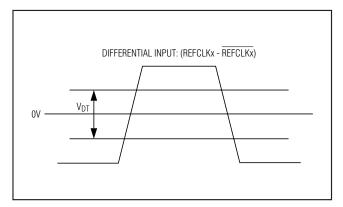

| Reference Clock Amplitude<br>Detection Assert Threshold                                                  | V <sub>DT</sub>                 | Differential swing (Notes 5, 6)                        |                           | 200                       |                           | mV <sub>P-P</sub> |

| LVPECL OUTPUTS (OUTA[3:0], 0                                                                             | DUTA[3:0], OL                   | JTB[4:0], OUTB[4:0]) (Note 7)                          | •                         |                           |                           | •                 |

| Output High Voltage                                                                                      | Voh                             |                                                        | V <sub>CC</sub> -<br>1.13 | V <sub>CC</sub> -<br>0.98 | V <sub>CC</sub> -<br>0.83 | V                 |

| Output Low Voltage                                                                                       | VOL                             |                                                        | V <sub>CC</sub> -<br>1.85 | V <sub>CC</sub> -<br>1.70 | V <sub>CC</sub> -<br>1.55 | V                 |

| Differential-Output Swing                                                                                |                                 |                                                        | 1.1                       | 1.45                      | 1.8                       | VP-P              |

| Output Current When Disabled                                                                             |                                 | $V_{\rm O} = V_{\rm CC} - 2.0V$ to $V_{\rm CC} - 0.7V$ |                           |                           | 130                       | μA                |

| Output Frequency                                                                                         | four                            |                                                        |                           | Tables<br>2, 3            |                           | MHz               |

| Output Rise/Fall Time                                                                                    | t <sub>R</sub> , t <sub>F</sub> | 20% to 80% (Note 8)                                    | 150                       |                           | 500                       | ps                |

| Outout Duty Ovala                                                                                        |                                 | PLL_BYPASS = 0                                         | 48                        |                           | 52                        | - %               |

| Output Duty Cycle                                                                                        |                                 | PLL_BYPASS = 1 (Note 9)                                | 45                        |                           | 55                        |                   |

| Output-to-Output Skew                                                                                    | tskew                           | Within output bank                                     |                           | 20                        |                           | - ps              |

|                                                                                                          | USINEW                          | All outputs                                            |                           | 40                        |                           |                   |

| OTHER AC ELECTRICAL SPECI                                                                                | FICATIONS                       |                                                        |                           |                           |                           |                   |

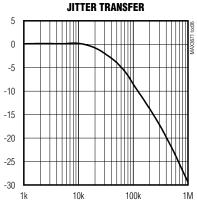

| PLL Jitter Transfer Bandwidth                                                                            |                                 |                                                        |                           | 40                        |                           | kHz               |

| Jitter Peaking                                                                                           |                                 |                                                        |                           | 0.1                       |                           | dB                |

| PFD Compare Frequency                                                                                    |                                 |                                                        |                           | 62.5                      |                           | MHz               |

| VCO Center Frequency                                                                                     |                                 |                                                        |                           | 2.5                       |                           | GHz               |

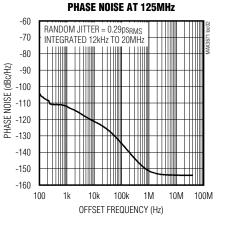

| Random Jitter Generation                                                                                 |                                 | Integrated 12kHz to 20MHz (Notes 5, 8)                 |                           | 0.3                       | 1.0                       | psRMS             |

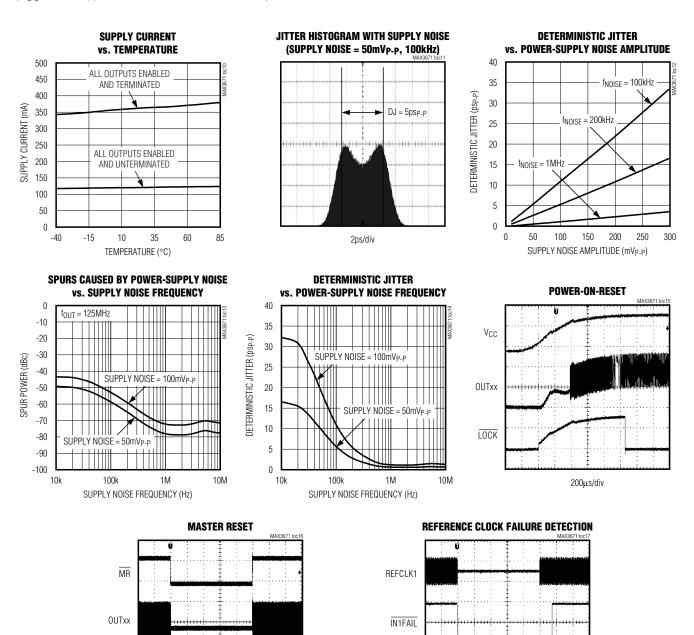

| Determinisitic Jitter Caused by<br>Power-Supply Noise                                                    |                                 | (Note 10)                                              |                           | 5                         |                           | psp-p             |

| Frequency Difference Between<br>Reference Clock and VCO<br>Within Which the PLL is<br>Considered in Lock |                                 |                                                        |                           | 500                       |                           | ppm               |

| Frequency Difference Between<br>Reference Clock and VCO at<br>Which the PLL is Considered<br>Out-of-Lock |                                 |                                                        |                           | 800                       |                           | ppm               |

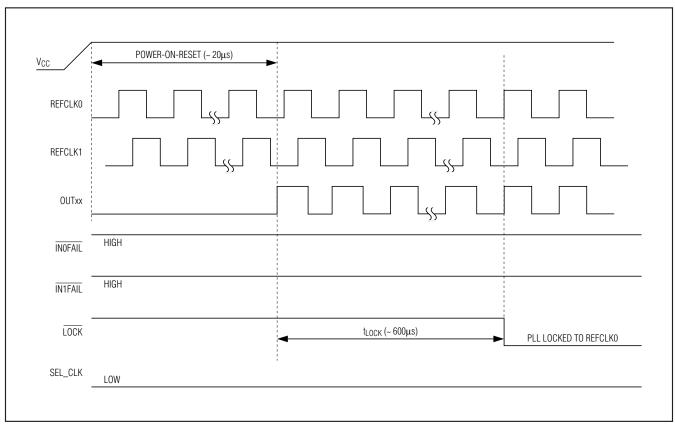

| PLL Lock Time                                                                                            | tLOCK                           | Figure 2                                               |                           | 600                       |                           | μs                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +3.0V to +3.6V, T<sub>A</sub> = -40°C to +85°C, C<sub>PLL</sub> = 0.1µF, C<sub>REG</sub> = 0.22µF. Typical values are at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                     | SYMBOL | CONDITIONS               | MIN  | ТҮР | MAX  | UNITS |

|-----------------------------------------------|--------|--------------------------|------|-----|------|-------|

| Master Reset (MR) Minimum<br>Pulse Width      |        |                          |      | 100 |      | ns    |

| Propagation Delay from Input to FB_IN         |        | FB_SEL = 1 (Notes 8, 11) | -120 |     | +120 | ps    |

| Propagation Delay from Input to<br>Any Output |        | PLL_BYPASS = 1           |      | 1.0 |      | ns    |

**Note 1:** During the power-on-reset time, the LVPECL outputs are held to logic-low (OUTxx = low,  $\overline{OUTxx}$  = high). See the *Power-On-Reset (POR)* section for more information.

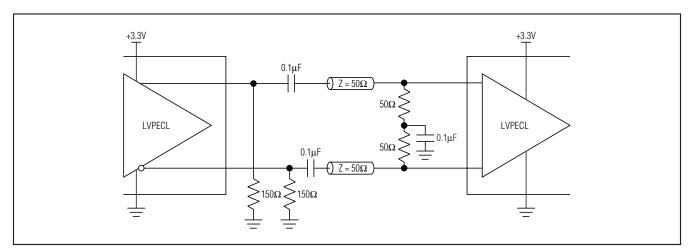

**Note 2:** LVPECL inputs can be AC- or DC-coupled.

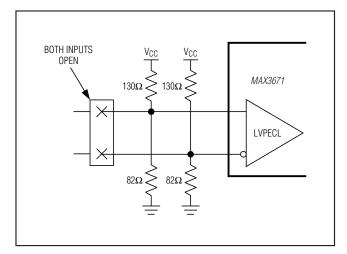

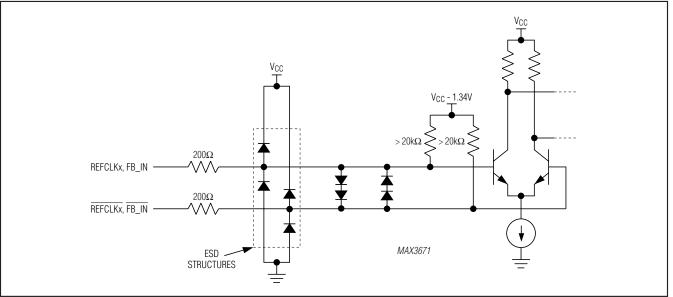

**Note 3:** For hot-pluggable purposes, the device can receive LVPECL inputs when no supply voltage is applied. Measured with V<sub>CC</sub> pins connected to GND. See Figure 1.

Note 4: Measured with LVPECL input (VIH, VIL) as specified.

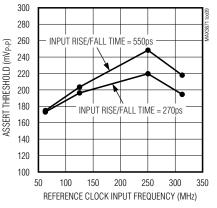

Note 5: Measured using reference clock input with 550ps rise/fall time (20% to 80%).

Note 6: When input differential swing is below the specified threshold, a clock failure is declared. See Figure 4.

**Note 7:** LVPECL outputs terminated  $50\Omega$  to V<sub>TT</sub> = V<sub>CC</sub> - 2V.

Note 8: Guaranteed by design and characterization.

**Note 9:** Measured with 50% duty cycle at reference clock input.

Note 10: Measured with  $50mV_{P-P}$  sinusoidal noise on the power supply,  $f_{NOISE} = 100kHz$ .

**Note 11:** Measured with  $f_{REFCLKx} = f_{FB_IN}$  and matched slew rates.

Figure 1. LVPECL Input Inrush Current

Figure 2. Power-Up, PLL Locks to REFCLK0

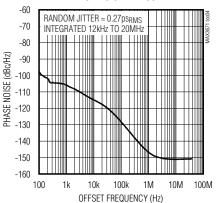

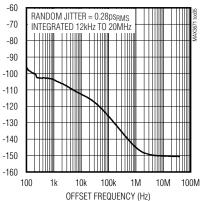

PHASE NOISE (dBc/Hz)

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

**MAX3671**

**PHASE NOISE AT 62.5MHz** -60 RANDOM JITTER = 0.41ps<sub>RMS</sub> -70 INTEGRATED 12kHz TO 20MHz -80 -90 -100 -110 -110 -120 -130 -140 -150 -160 100 10M 1k 10k 100k 1M 100M OFFSET FREQUENCY (Hz)

#### PHASE NOISE AT 156.25MHz -60 RANDOM JITTER = 0.28ps<sub>RMS</sub> -70 INTEGRATED 12kHz TO 20MHz -80 -90 -100 -110 -110 -120 -130 -140 -150 -160 100 100M 1k 10k 100k 1M 10M OFFSET FREQUENCY (Hz)

**PHASE NOISE AT 250MHz**

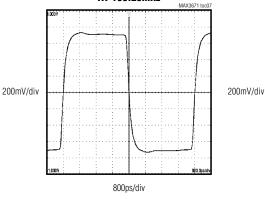

DIFFERENTIAL OUTPUT WAVEFORM AT 156.25MHz

**DIFFERENTIAL OUTPUT WAVEFORM**

AT 312.5MHz

400ps/div

MAX3671 toc0

JITTER TRANSFER (dB)

JITTER FREQUENCY (Hz)

REFERENCE CLOCK AMPLITUDE DETECTION ASSERT THRESHOLD vs. INPUT FREQUENCY

#### **Typical Operating Characteristics**

6

#### **\_Typical Operating Characteristics (continued)**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

LOCK

40µs/div

LOCK

2ms/div

**MAX367**

#### **Pin Description**

| PIN                          | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                            | INOFAIL         | REFCLK0 Failure Indicator, LVCMOS/LVTTL Output. Low indicates REFCLK0 fails the clock qualification. Once a failed clock is detected, the indicator status is latched and updated every 128 PFD cycles (~ 2µs).                                                                                                                                                                                                                                                                             |  |  |

| 2                            | RSVD1           | Reserved. Leave pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 3                            | RSVD2           | Reserved. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4                            | REFCLK0         | Reference Clock Input 0, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 5                            | <b>REFCLK0</b>  | neierence clock input 0, Dinerential EVI LCE                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 6                            | DM              | Four-Level Control Input for Reference Clock Input Divider. See Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 7, 22, 30, 41,<br>49, 52     | V <sub>CC</sub> | Power Supply. Connect to +3.3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 8, 14, 23, 29,<br>42, 48, 53 | GND             | Supply Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 9                            | MR              | Master Reset, LVCMOS/LVTTL Input. Connect this pin high or leave open for normal operation. Has internal 90k $\Omega$ pullup to V <sub>CC</sub> . Connect low to reset the device. A reset is not required at power-up. If the output divider settings are changed on the fly, a reset is required to phase align the outputs. This input has a 100ns minimum pulse width and is asynchronous to the reference clock. While in reset, all clock outputs are held to logic-low. See Table 6. |  |  |

| 10                           | REFCLK1         | Reference Clock Input 1, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 11                           | REFCLK1         | neierence clock input 1, binerential EVI LCE                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 12                           | SEL_CLK         | Reference Clock Select, LVCMOS/LVTTL Input. Connect low or leave open to select REFCLK0 as the reference clock. Has internal $90k\Omega$ pulldown to GND. Connect high to select REFCLK1 as the reference clock.                                                                                                                                                                                                                                                                            |  |  |

| 13                           | VCC_VCO         | Power Supply for VCO. Connect to +3.3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

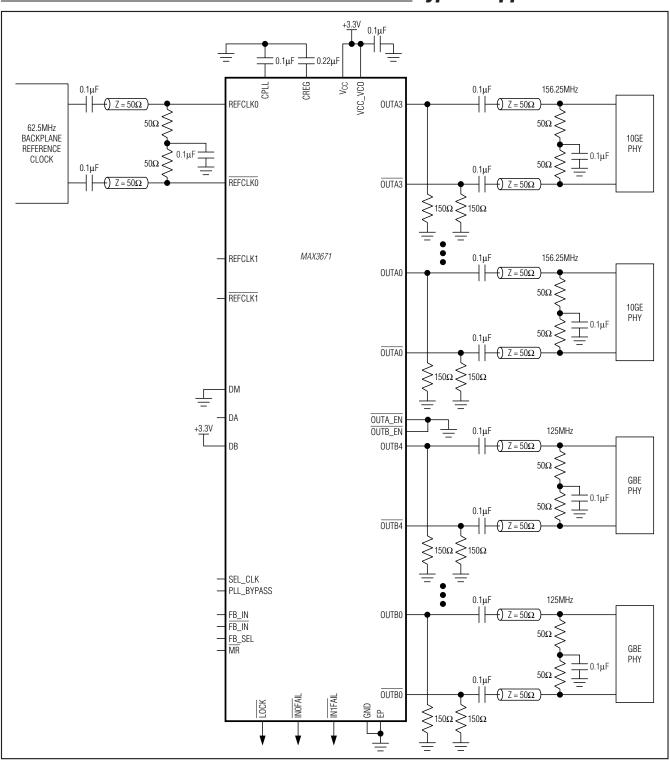

| 15                           | CPLL            | Connection for PLL Filter Capacitor. Connect a 0.1µF capacitor between this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 16                           | CREG            | Connection for VCO Regulator Capacitor. Connect a 0.22µF capacitor between this pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 17                           | FB_SEL          | External Feedback Select, LVCMOS/LVTTL Input. Connect high to select external feedback for zero-delay buffer configuration. Connect low or leave open for internal feedback. Has internal 90k $\Omega$ pulldown to GND.                                                                                                                                                                                                                                                                     |  |  |

| 18                           | FB_IN           | External Feedback Clock Input, Differential LVPECL. Used for zero-delay buffer                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 19                           | FB_IN           | configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 20                           | OUTB0           | Clock Output BO, Differential LV/DECL                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 21                           | OUTB0           | Clock Output B0, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 24                           | OUTB1           | Clock Output B1, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 25                           | OUTB1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 26                           | OUTB2           | Cleak Output D0 Differential LV/DECL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 27                           | OUTB2           | Clock Output B2, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 28                           | DB              | Four-Level Control Input for B-Group Output Divider. See Table 3.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 31                           | OUTB3           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 32                           | OUTB3           | Clock Output B3, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 33                           | OUTB4           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 34                           | OUTB4           | Clock Output B4, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 35                           | OUTB_EN         | Three-Level Control Input for B-Group Output Enable. See Table 5.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 36                           | OUTA_EN         | Three-Level Control Input for A-Group Output Enable. See Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

#### **Pin Description (continued)**

| PIN | NAME           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 37  | OUTA3          | Cleak Output AD Differential LVDECI                                                                                                                                                                                                                                                                                                                                                                             |  |

| 38  | OUTA3          | Clock Output A3, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                            |  |

| 39  | OUTA2          | Clock Output AD Differential LV/PECI                                                                                                                                                                                                                                                                                                                                                                            |  |

| 40  | OUTA2          | Clock Output A2, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                            |  |

| 43  | DA             | Four-Level Control Input for A-Group Output Divider. See Table 2.                                                                                                                                                                                                                                                                                                                                               |  |

| 44  | OUTA1          | Clock Output A1, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                            |  |

| 45  | OUTA1          |                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 46  | OUTAO          | Clock Output A0, Differential LVPECL                                                                                                                                                                                                                                                                                                                                                                            |  |

| 47  | OUTAO          |                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 50  | PLL_BYPASS     | PLL Bypass Control, LVCMOS/LVTTL Input. Connect low or open for normal operation. Has internal 90k $\Omega$ pulldown to GND. Connect high to bypass the PLL, connecting the selected reference clock directly to the clock outputs. In this mode, the clock qualification function is not valid. To reduce spurious jitter in bypass mode, the internal VCO should be disabled by shorting the CREG pin to GND. |  |

| 51  | RSVD3          | Reserved. Connect to V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                          |  |

| 54  | RSVD4          | Reserved. Leave pin open.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 55  | LOCK           | PLL Lock Indicator, LVCMOS/LVTTL Output. Low indicates PLL is locked.                                                                                                                                                                                                                                                                                                                                           |  |

| 56  | <b>IN1FAIL</b> | REFCLK1 Failure Indicator, LVCMOS/LVTTL Output. Low indicates REFCLK1 fails the clock qualification. Once a failed clock is detected, the indicator status is latched and updated every 128 PFD cycles (~ $2\mu$ s).                                                                                                                                                                                            |  |

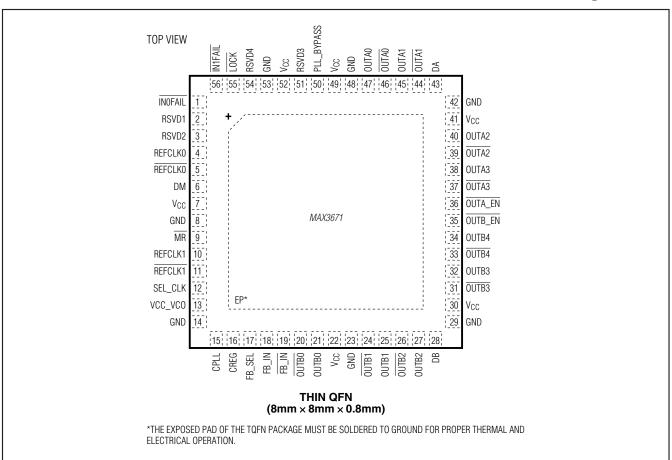

|     | EP             | Exposed Pad. Connect to supply ground for proper electrical and thermal performance.                                                                                                                                                                                                                                                                                                                            |  |

#### **Detailed Description**

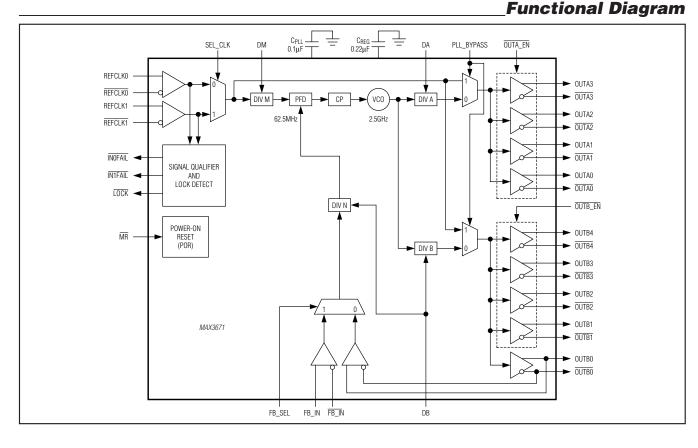

The MAX3671 integrates two differential LVPECL reference inputs with a 2:1 mux, a PLL with configurable dividers, nine differential LVPECL clock outputs, and a selectable external feedback input for zero-delay buffer applications (see the *Functional Diagram*).

The two reference clock inputs are continuously monitored for clock failure by the internal PLL and associated logic. If the primary clock fails, the user can switch over to the secondary clock using the 2:1 mux.

The PLL accepts reference input frequencies of 62.5, 125, 250, or 312.5MHz and generates output frequencies of 62.5, 125, 156.25, 250, or 312.5MHz. The nine clock outputs are organized into two groups (A and B). Each group has a configurable frequency divider and output-enable control.

#### Phase-Locked Loop (PLL)

The PLL contains a phase-frequency detector (PFD), charge pump (CP) with a lowpass filter, and voltage-controlled oscillator (VCO). The PFD compares the

divided reference frequency to the divided VCO output at 62.5MHz, and generates a control signal to keep the VCO phase and frequency locked to the selected reference clock. Using a high-frequency VCO (2.5GHz) and low-loop bandwidth (40kHz), the MAX3671 attenuates reference clock jitter while maintaining lock and generates low-jitter clock outputs at multiple frequencies. Typical jitter generation is 0.3psRMS (integrated 12kHz to 20MHz).

To minimize supply noise-induced jitter, the VCO supply (VCC\_VCO) is isolated from the core logic and output buffer supplies. Additionally, the MAX3671 uses an internal low-dropout (LDO) regulator to attenuate noise from the power supply. This allows the device to achieve excellent power-supply noise rejection, significantly reducing the impact on jitter generation.

#### **Clock Failure Conditions**

The MAX3671 clock failure detection is performed using the combination of amplitude qualification and PLL frequency and phase-error qualification. The failure status is indicated for REFCLK0 and REFCLK1 at

INOFAIL and IN1FAIL, respectively. Once an indicator is asserted low, it is latched and updated every 128 PFD cycles (~ 2µs).

It should be noted that when the PLL is locked to a reference clock, the clock failure indicator for the other reference clock is only valid for amplitude qualification and frequency qualification.

#### Amplitude Qualification

A reference clock input fails amplitude qualification if any of the following conditions occur:

- Either one or both inputs (REFCLKx, REFCLKx) are shorted to V<sub>CC</sub> or GND.

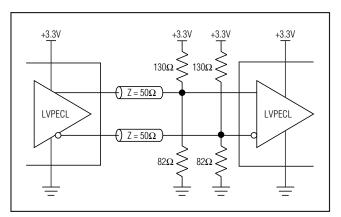

- Both inputs (REFCLKx, REFCLKx) are disconnected from the source and have 130 $\Omega$  to V<sub>CC</sub> and 82 $\Omega$  to GND at each input. See Figure 3.

- Input reference clock differential swing is below the clock failure assert threshold as specified in the *Electrical Characteristics*. See Figure 4.

The response time for these conditions is typically between 50ns and 300ns.

#### Phase Qualification

A reference clock input fails phase qualification when the phase error at the PFD output exceeds the error window (0.75ns typical) for more than five of eight PFD cycles. A reference clock input is qualified when phase error at the PFD output is within the phase-error window for eight consecutive PFD cycles. Note that phase qualification only applies to the reference input currently being used by the PLL.

#### Frequency Qualification

A reference clock input becomes frequency qualified if the input frequency is within  $\pm 2.4\%$  of the nominal frequency. The reference input becomes frequency disqualified if the input frequency moves away from the nominal frequency by more than  $\pm 8\%$ .

Figure 3. Positions for Open-Circuit Detection

Figure 4. Input Amplitude Detection Threshold

# Table 1. Divider M Configuration for InputFrequencies

| CONNECTION FROM DM PIN | INPUT FREQUENCY (MHz) |

|------------------------|-----------------------|

| GND                    | 62.5                  |

| Vcc                    | 125                   |

| Open                   | 250                   |

| 10kΩ to GND            | 312.5                 |

# Table 2. Divider A Configuration forA-Group Output Frequencies

| CONNECTION FROM DA PIN | OUTPUT FREQUENCY AT<br>OUTA[3:0] (MHz) |

|------------------------|----------------------------------------|

| GND                    | 62.5                                   |

| Vcc                    | 125                                    |

| Open                   | 156.25                                 |

| 10k $\Omega$ to GND    | 312.5                                  |

# Table 3. Divider B Configuration forB-Group Output Frequencies

| CONNECTION FROM DB PIN | OUTPUT FREQUENCY AT<br>OUTB[4:0] (MHz) |

|------------------------|----------------------------------------|

| GND                    | 62.5                                   |

| Vcc                    | 125                                    |

| Open                   | 250                                    |

| 10kΩ to GND            | 312.5                                  |

#### Table 4. OUTA[3:0] Enable Control

#### **PLL Out-of-Lock Condition**

If the frequency difference between the reference clock input and the VCO at the PFD input becomes within 500ppm, the PLL is considered to be in lock ( $\overline{LOCK} = 0$ ). When the frequency difference between the reference clock input and the VCO at the PFD input becomes greater than 800ppm, the PLL is considered out-of-lock. It should be noted that the LOCK indicator is not part of the frequency qualification used for the INxFAIL indicators.

#### **Input and Output Frequencies**

The MAX3671 input and output dividers are configured using four-level control inputs DM, DA, and DB. Each divider is independent and can have a unique setting. The input connection and associated frequencies are listed in Tables 1, 2, and 3.

#### **Output-Enable Controls**

Each <u>output group</u> (<u>A and B</u>) has a three-level control input <u>OUTA\_EN</u> and <u>OUTB\_EN</u>. See Tables 4 and 5 for configuration settings. When clock outputs are disabled, they are high impedance. Unused enabled outputs should be left open.

#### **Power-On-Reset (POR)**

At power-on, an internal signal is generated to hold the MAX3671 in a reset state. This internal reset time is about 20 $\mu$ s after V<sub>CC</sub> reaches 3.0V (Figure 2). During the POR time, the outputs are held to logic-low (OUTxx = low and OUTxx = high). See Table 6 for output signal status during POR. After this internal reset time, the PLL starts to lock to the reference clock selected by SEL\_CLK.

| CONNECTION FROM OUTA_EN PIN | A-GROUP OUTPUT ENABLED     | A-GROUP OUTPUT DISABLED TO HIGH<br>IMPEDANCE |  |  |

|-----------------------------|----------------------------|----------------------------------------------|--|--|

| GND                         | OUTA0, OUTA1, OUTA2, OUTA3 | —                                            |  |  |

| V <sub>CC</sub> *           |                            | OUTA0, OUTA1, OUTA2, OUTA3                   |  |  |

| Open                        | OUTA0, OUTA1               | OUTA2, OUTA3                                 |  |  |

|                             |                            |                                              |  |  |

\*Connecting both OUTA\_EN and OUTB\_EN to V<sub>CC</sub> enables a factory test mode and forces all indicators to GND. This is not a valid mode of operation.

#### Table 5. OUTB[4:0] Enable Control

| CONNECTION FROM OUTB_EN PIN | B-GROUP OUTPUT ENABLED            | B-GROUP OUTPUT DISABLED TO HIGH<br>IMPEDANCE |

|-----------------------------|-----------------------------------|----------------------------------------------|

| GND                         | OUTB0, OUTB1, OUTB2, OUTB3, OUTB4 | —                                            |

| V <sub>CC</sub> *           | OUTB0                             | OUTB1, OUTB2, OUTB3, OUTB4                   |

| Open                        | OUTB0, OUTB1, OUTB2               | OUTB3, OUTB4                                 |

\*Connecting both OUTA\_EN and OUTB\_EN to V<sub>CC</sub> enables a factory test mode and forces all indicators to GND. This is not a valid mode of operation.

#### **Master Reset**

After power-up, an external master reset ( $\overline{MR}$ ) can be provided to reset the internal dividers. This input requires a minimum reset pulse width of 100ns (active low) and is asynchronous to the reference clock. While  $\overline{MR}$  is low, all clock outputs are held to logic-low (OUTxx = low,  $\overline{OUTxx}$  = high). See Table 6 for the output signal status during master reset. When the master reset input is deasserted ( $\overline{MR}$  = 1), the PLL starts to lock to the reference clock selected by SEL CLK.

Master reset is only needed for applications where divider configurations are changed on the fly and the clock outputs need to maintain phase alignment. A master reset is not required at power-up.

**External Feedback for Zero-Delay Buffer** The MAX3671 can be operated with either internal or external PLL feedback path, controlled by the FB\_SEL input. Connecting FB\_SEL to GND selects internal feedback. For applications where a known phase relationship between the reference clock input and the external feedback input (FB\_IN, FB\_IN) are needed for phase synchronization, connect FB\_SEL to V<sub>CC</sub> for zero-delay buffer configuration and provide external feedback to the FB\_IN input.

#### PLL Bypass Mode

PLL bypass mode is provided for test purposes. In PLL bypass mode (PLL\_BYPASS = 1), the selected reference clock is connected to the LVPECL clock outputs directly. The output clock frequency is the same as the input clock frequency and the clock qualification function is not valid. To reduce spurious jitter in bypass mode, the internal VCO should be disabled by shorting the CREG pin to GND.

#### Applications Information

#### Interfacing with LVPECL Inputs

Figure 5 shows the equivalent LVPECL input circuit for REFCLK0, REFCLK1, and FB\_IN. These inputs are internally biased to allow AC- or DC-coupling and have > 40k $\Omega$  differential input impedance. When AC-coupled, these inputs can accept LVDS, CML, and LVPECL signals. Unused reference clock inputs should be left open.

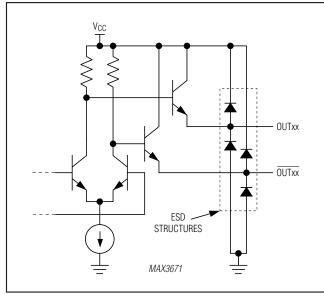

#### Interfacing with LVPECL Outputs

Figure 6 shows the equivalent LVPECL output circuit. These outputs are designed to drive a pair of  $50\Omega$  transmission lines terminated with  $50\Omega$  to V<sub>TT</sub> = V<sub>CC</sub> - 2V. If a separate termination voltage (V<sub>TT</sub>) is not available, other termination methods can be used such as those shown in Figures 7 and 8. Unused outputs, enabled or disabled, can be left open or properly terminated. For more information on LVPECL terminations and how to interface with other logic families, refer to Application Note 291: *HFAN-01.0: Introduction to LVDS, PECL, and CML.*

#### **Layout Considerations**

The clock inputs and outputs are critical paths for the MAX3671, and care should be taken to minimize discontinuities on the transmission lines. Maintain  $100\Omega$  differential (or  $50\Omega$  single-ended) impedance in and out of the MAX3671. Avoid using vias and sharp corners. Termination networks should be placed as close as possible to receiving clock inputs. Provide space between differential output pairs to reduce crosstalk, especially if the A and B group outputs are operating at different frequencies.

| OUTPUT         | DURING POWER-ON-RESET<br>(FOR ~ 20μs AFTER V <sub>CC</sub> > 3.0V) | DURING MASTER RESET<br>(MR = 0) | NOTES                                                    |

|----------------|--------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|

| INOFAIL        | 1                                                                  |                                 | Forced high regardless of reference input qualification. |

| <b>IN1FAIL</b> | 1                                                                  |                                 | Forced high regardless of reference input qualification. |

| LOCK           | 1                                                                  |                                 | PLL out-of-lock.                                         |

| OUTA[3:0]      | Logic-Low                                                          |                                 | —                                                        |

| OUTB[4:0]      | Logic-Low                                                          |                                 |                                                          |

**Power Supply and Ground Connections**

The MAX3671 has seven supply connection pins; installation of a bypass capacitor at each supply pin is recommended. All seven supply connections should be driven from the same source to eliminate the possibility of independent power-supply sequencing. Excessive supply noise can result in increased jitter.

The 56-pin TQFN package features an exposed pad (EP), which provides a low-resistance thermal path for heat removal from the IC and must be connected to the circuit board ground plane for proper operation.

Figure 5. Equivalent LVPECL Input Circuit

Figure 6. Equivalent LVPECL Output Circuit

Figure 7. Thevenin Equivalent LVPECL Termination

Figure 8. AC-Coupled LVPECL Termination

#### Pin Configuration

#### **Typical Application Circuits**

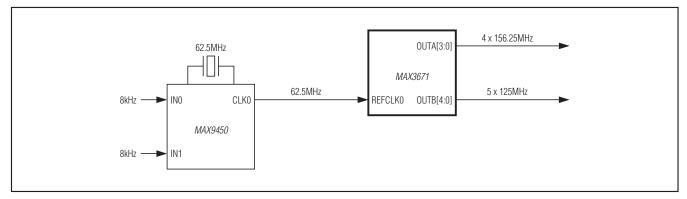

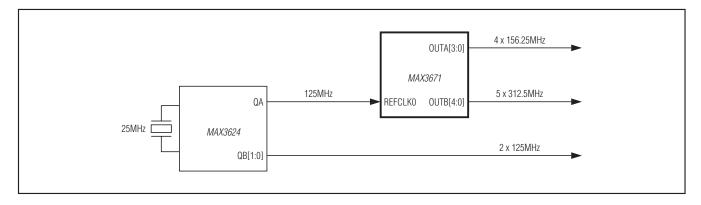

#### **Typical Application Circuits (continued)**

**Chip Information**

PROCESS: BICMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to http://www.microsemi.com

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 56 TQFN-EP   | T5688+3      | <u>21-0135</u> |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.